A nsga-ii-based power and area optimization method for incompletely determined reed-muller circuits

A technology for area optimization and power consumption, applied in exclusive-or circuits, logic circuits with logic functions, etc., can solve problems such as poor performance, inability to solve non-convex Pareto, and simultaneous optimization of power consumption and area of seldom RM logic circuits, etc. problem, to achieve the effect of good power consumption and area performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

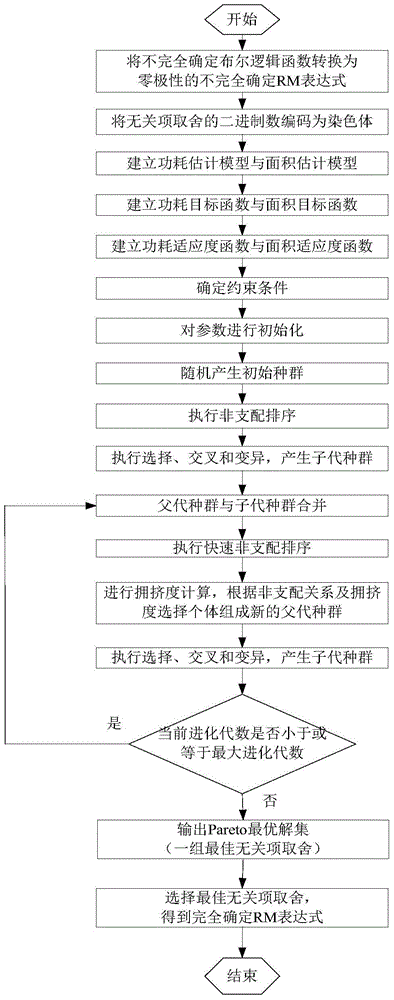

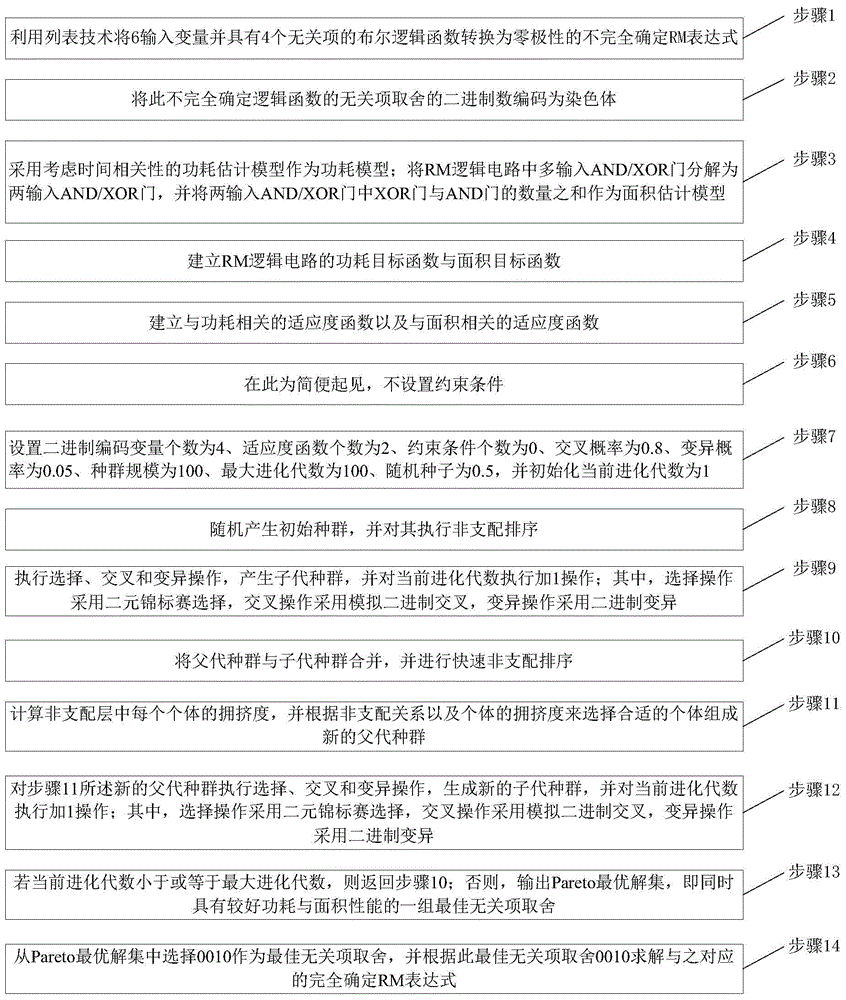

[0052] figure 1 It is a flow chart of the NSGA-II-based method for optimizing the power consumption and area of an incompletely determined Reed-Muller circuit in the present invention. Such as figure 1 As shown, the method includes:

[0053] Step 1, convert the incompletely deterministic Boolean logic function into an incompletely deterministic RM expression of zero polarity by using the list technique;

[0054] Step 2, encode the binary numbers of the irrelevant items that do not completely determine the Boolean logic function into chromosomes;

[0055] Step 3, according to the characteristics of the RM logic circuit, respectively establish a power consumption estimation model and an area estimation model;

[0056] Step 4, according to the determined power consumption estimation model a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More