Metastable state eliminating circuit used for TDC

A technology to eliminate circuits and metastability, applied in the direction of electrical components, automatic power control, etc., can solve problems such as sampling result error, TDC count deviation, metastability, etc., to eliminate timing errors and improve reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Below in conjunction with accompanying drawing and embodiment, describe technical solution of the present invention in detail:

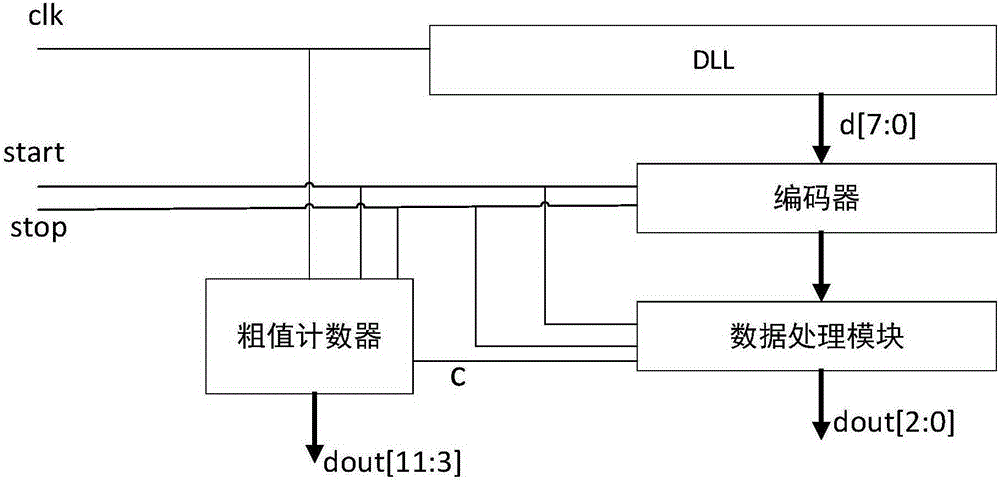

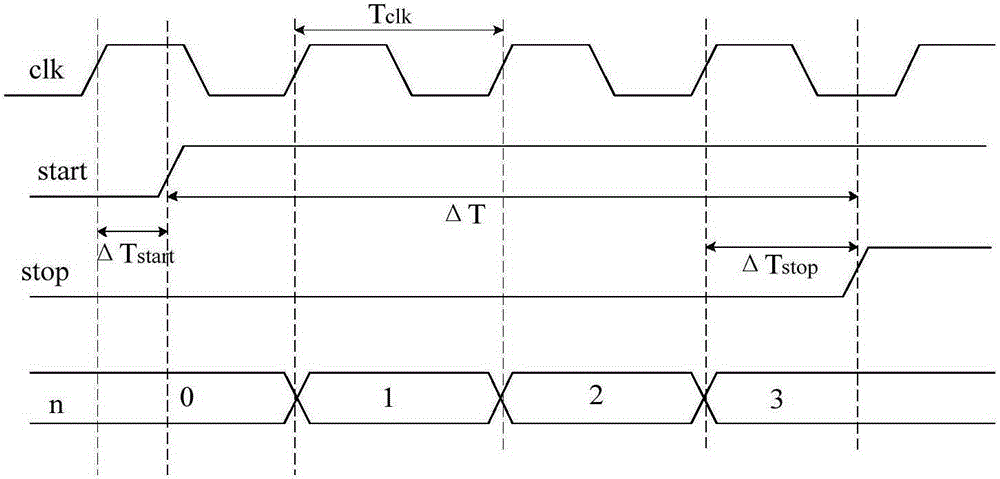

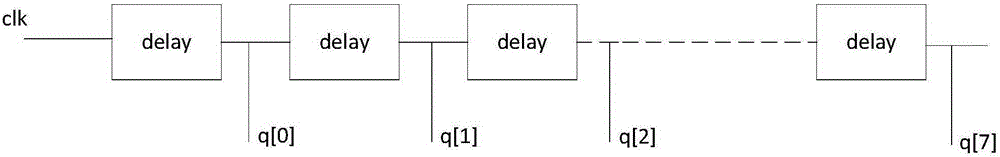

[0024] In order to eliminate the timing error caused by metastable state when the traditional TDC adopts DLL and counter to quantify the time interval, the invention adds a metastable state elimination logic circuit. The TDC after eliminating the metastable state is the same as the typical TDC accuracy, the only difference is that when the start is at Figure 4 ①②When sampling the position, the typical TDC may not be able to sample correctly, so that the quantization result has a clock cycle deviation from the correct result, which is a very serious deviation. However, the circuit after adding the metastable state elimination logic will have a deviation of one clock period in the quantization result of the DLL after sampling incorrectly. At the same time, it will also give the counter a signal start_clk, so that the count n will also have a de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More