Method for forming semiconductor structure

A semiconductor and wet etching technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as difficulty in adjusting the performance of transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

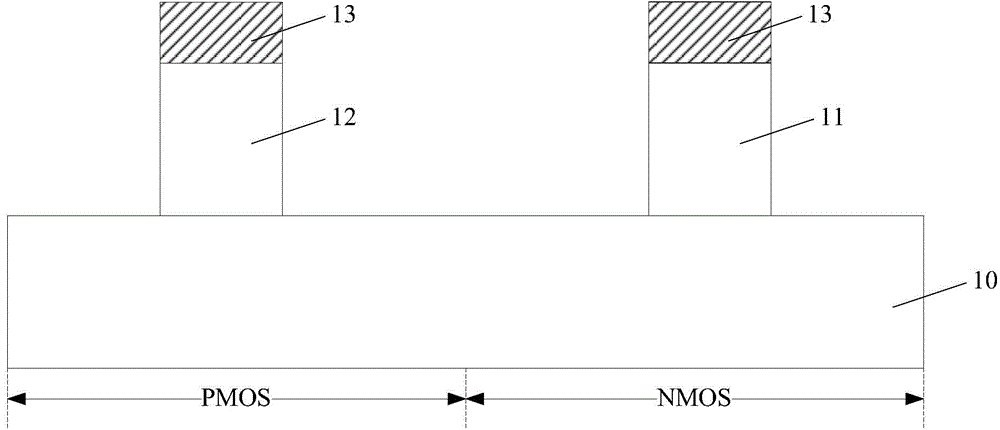

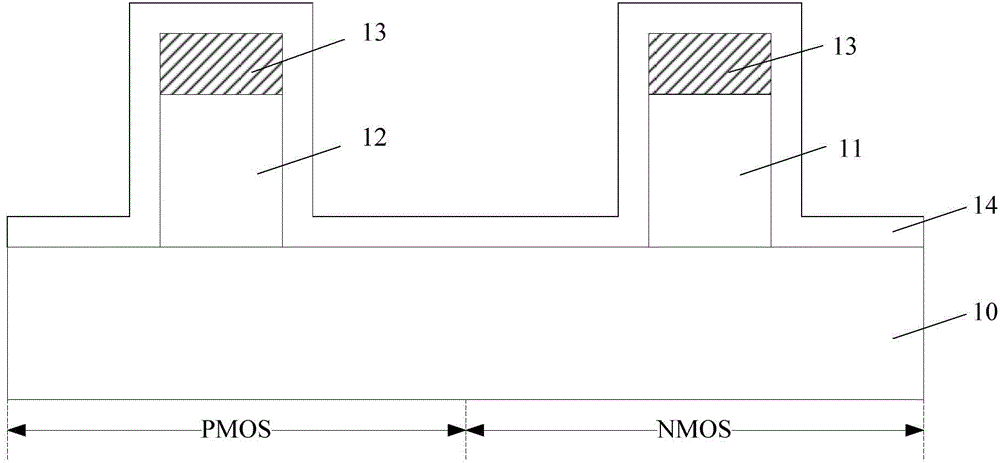

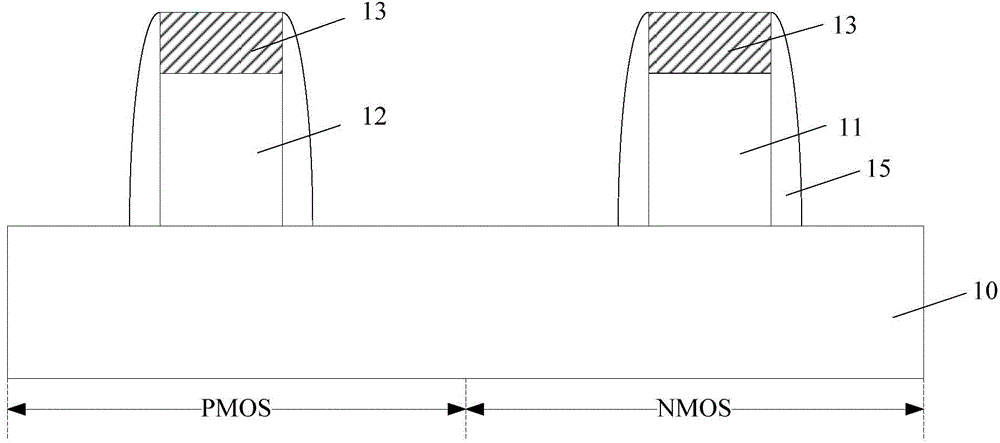

[0037] As mentioned in the background art, in the prior art, the sidewalls on the gate sidewall surfaces of different transistors are usually formed at the same time, so that the thickness of the gate sidewalls of different transistors is the same, and it is impossible to make a judgment on the performance of different transistors through the thickness of the sidewalls. Adjustment. In order to accurately adjust the performance of different transistors, it is necessary to form sidewalls with different thicknesses for different transistors to meet the requirements of device design. For example, since the diffusion rate of the dopant ions in the source and drain of the PMOS transistor is greater than the diffusion rate of the dopant ions in the source and drain of the NMOS transistor, in order to prevent the source and drain of the PMOS transistor from punching through, it is necessary to make the gate of the PMOS transistor The thickness of the pole sidewall is greater than the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More