Semiconductor Wafer Bump Structure

A bump structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc. Problems such as delamination between the tops of wiring metal layers to reduce wafer warpage, avoid electrical performance failures, and avoid semiconductor device failures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain related inventions, rather than to limit the invention. It should also be noted that, for ease of description, only parts related to the invention are shown in the drawings.

[0015] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other. The present application will be described in detail below with reference to the accompanying drawings and embodiments.

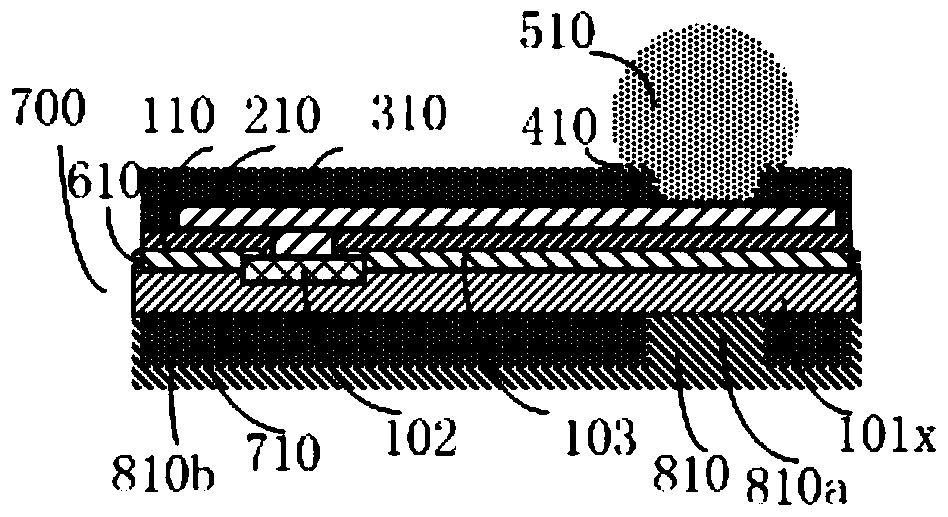

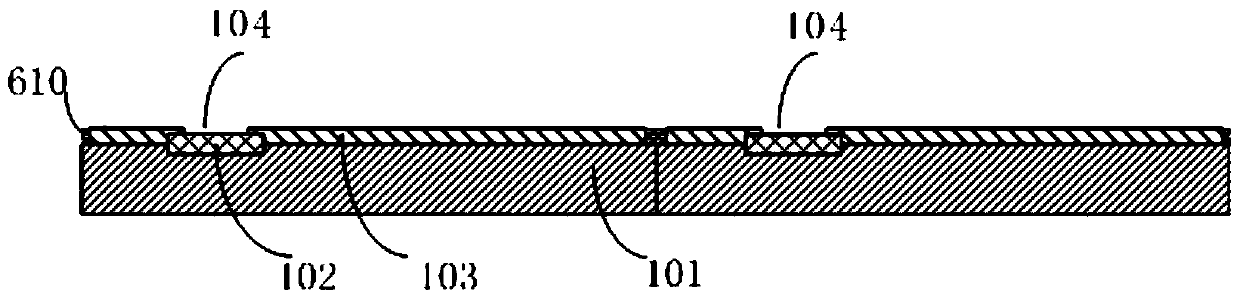

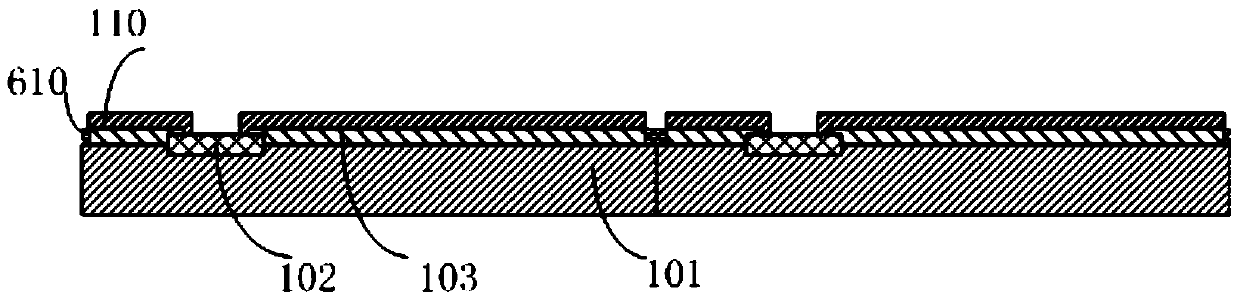

[0016] refer to figure 1 , the semiconductor wafer bump structure of the embodiment of the present invention includes:

[0017] Wafer 101X;

[0018] A recreated passivation layer formed on the upper surface of the wafer 101X;

[0019] A polymer material layer 710 formed on the lower surface of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More