Semiconductor chip packaging structure and packaging method thereof

A chip packaging structure and packaging method technology, applied in semiconductor devices, electric solid state devices, radiation control devices, etc., can solve problems such as affecting the quality of finished chips, delamination cracking of support structure 101, etc., to solve delamination cracking and reduce impact. force effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

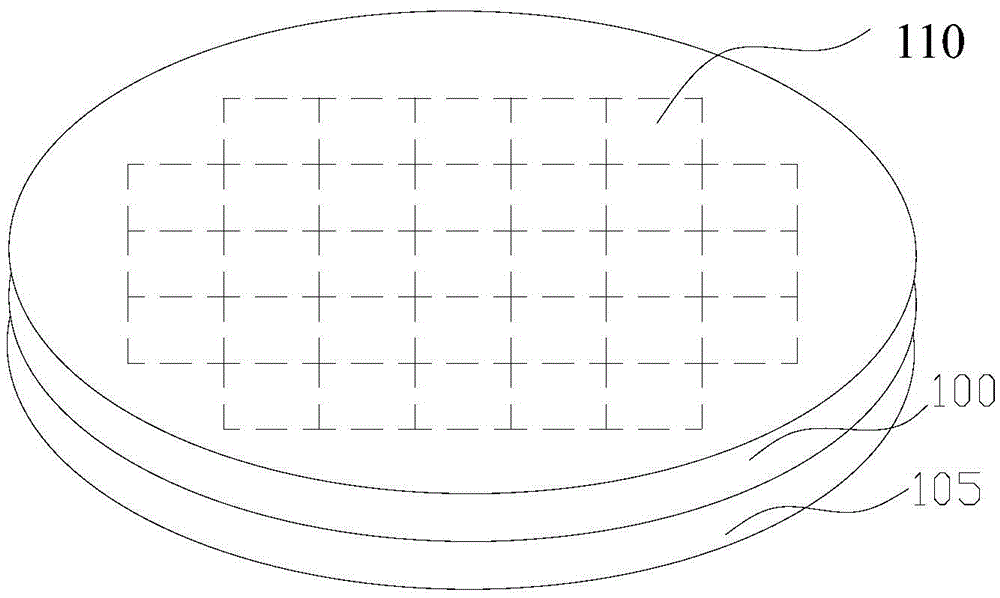

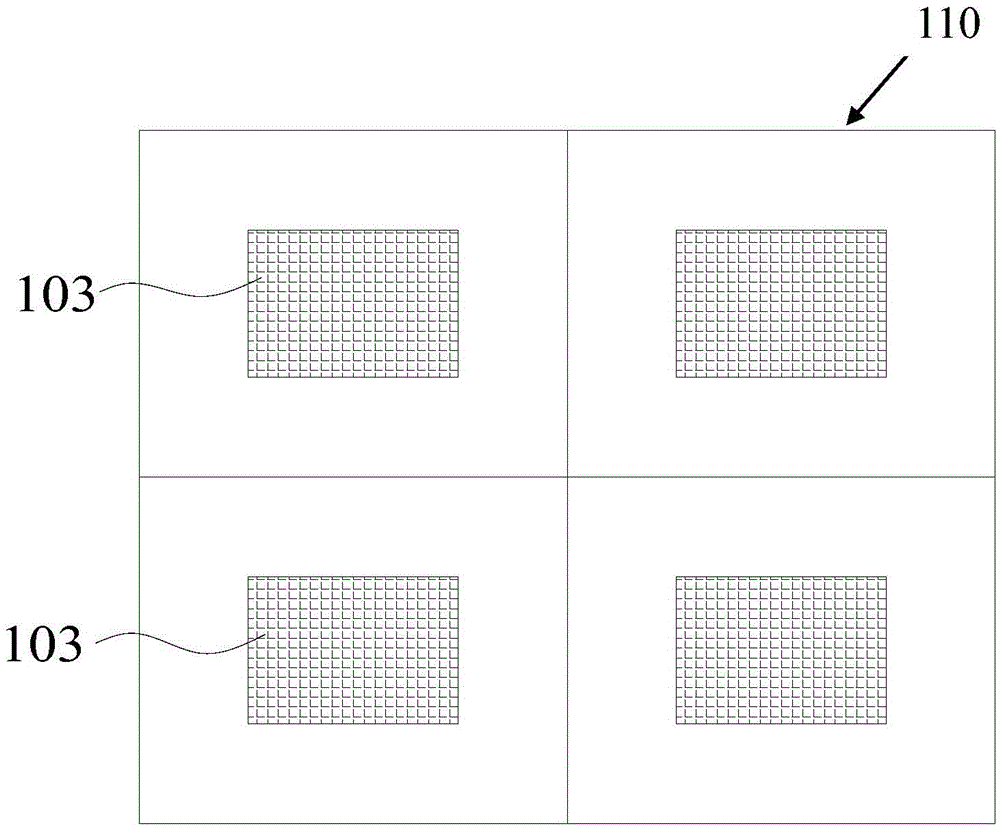

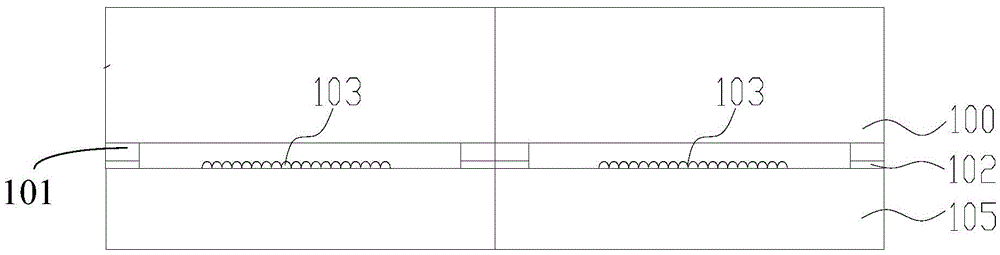

[0029] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

[0030] It should be noted that the purpose of providing these drawings is to facilitate the understanding of the embodiments of the present invention, and should not be interpreted as undue limitations on the present invention. For clarity, the dimensions shown in the figures are not drawn to scale and may be enlarged, reduced or otherwise changed. In addition, the three-dimensional space dimensions of length, width and depth should be included in actual production.

[0031] The preferred embodiment of the present invention takes an image sensor chip as an example. Of course, the present invention is not li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More