AES decryption and decryption method and circuit for FPGA with limited IO resource

An encryption, decryption, resource technology, applied in the field of communication, can solve problems such as too many pins, cannot meet AES encryption and decryption, and increase device cost, so as to achieve the effect of improving utilization rate, strong program portability, and saving IO resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

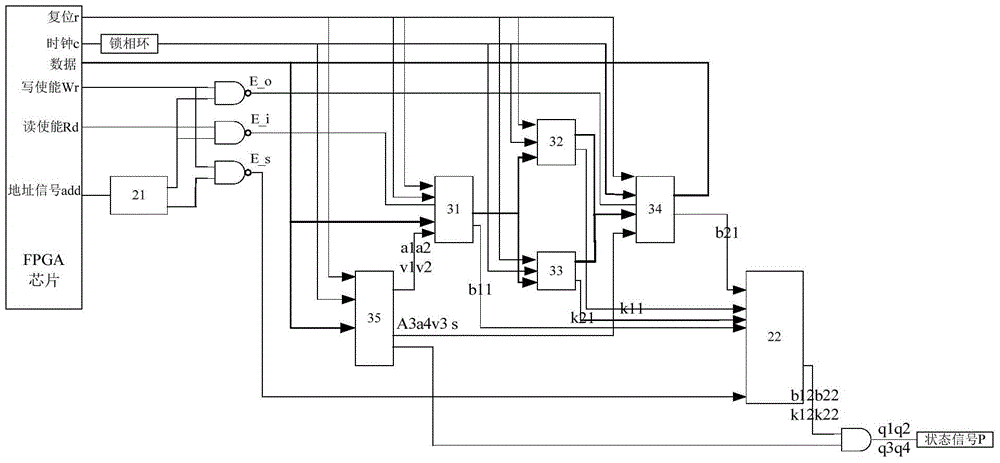

Image

Examples

Embodiment

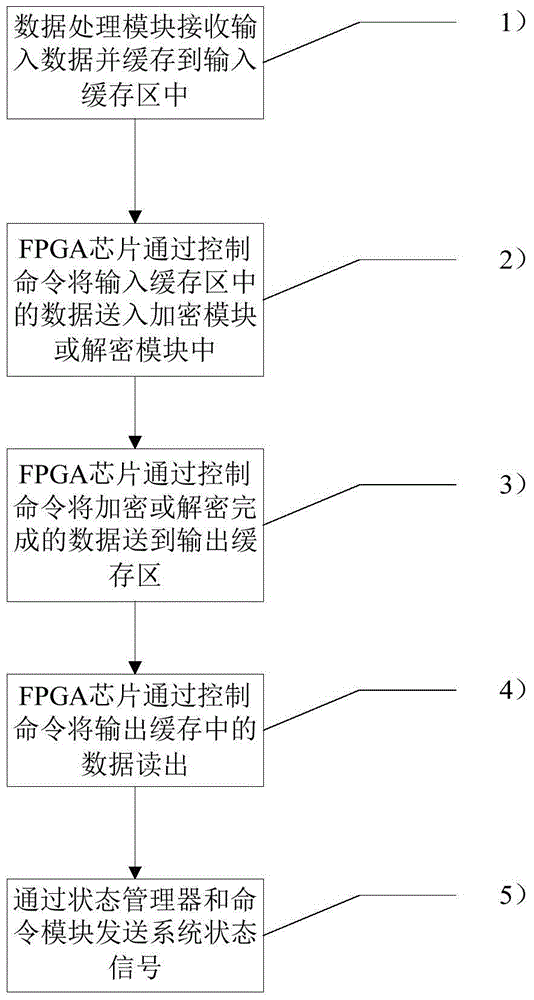

[0059] Such as figure 2 As shown, an AES encryption and decryption method suitable for FPGAs with limited IO resources includes the following steps:

[0060] 1) The data processing module receives the input data and caches it in the input buffer area, specifically including the following steps;

[0061] 11) Determine whether the reset signal r is 1, if so, reset all registers, and return to step 11); if not, proceed to step 12);

[0062] 12) Determine whether the write address initialization signal a1 is 1, if so, reset the input cache write address pointer, and return to step 11); if not, proceed to step 13);

[0063] 13) Determine whether the input buffer enable signal E_i is on a falling edge, if so, write the received data into the input buffer, and the address pointer is incremented by 1; if not, return to step 11);

[0064] 2) The FPGA chip sends the data in the input buffer area to the encryption unit or the decryption unit through a control command, specifically inc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More