Method and device for verification of layout comparison principle diagram of discrete devices

A discrete device and verification method technology, applied in the direction of instruments, electrical digital data processing, special data processing applications, etc., can solve the problems of high error rate and low efficiency of circuit diagrams, and achieve improved efficiency, improved layout accuracy, and fast batch LVS Verify the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

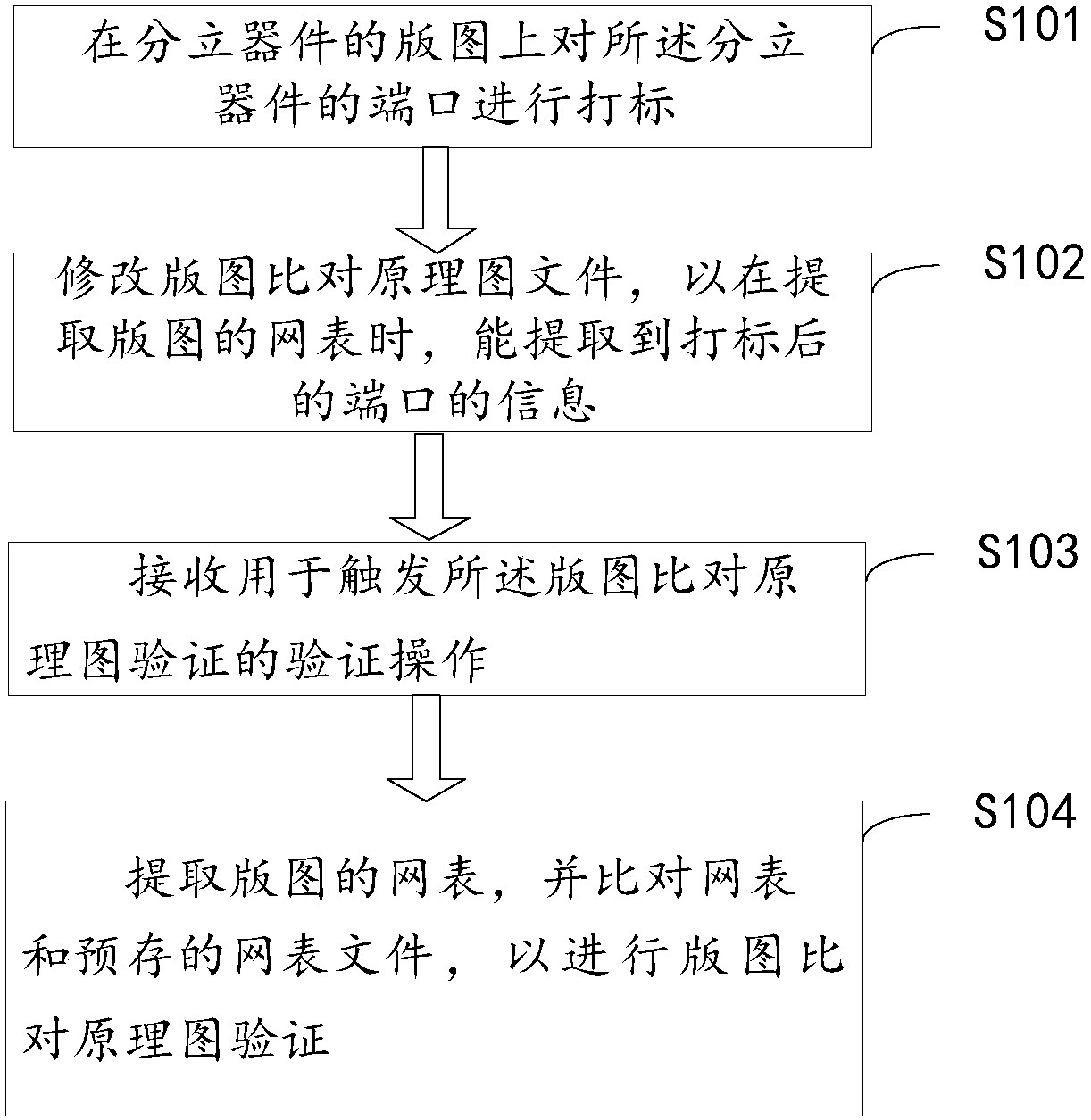

[0044] In this embodiment, a verification method of layout comparison and schematic diagram of discrete devices is provided, please refer to figure 1 , figure 1 It is a flow chart of the method for verifying the schematic diagram of the layout of the discrete device in the embodiment of the present application, such as figure 1 As shown, the method includes:

[0045] Step S101, marking the ports of the discrete device on the layout of the discrete device;

[0046] Step S102, modifying the layout comparison schematic file, so that when extracting the netlist of the layout of the discrete device, the information of the marked port can be extracted;

[0047] Step S103, receiving a verification operation for triggering verification of the layout comparison schematic diagram;

[0048] Step S104, extracting the netlist of the layout, and comparing the netlist with a pre-stored netlist file to perform layout comparison schematic verification; the netlist file includes the port and...

Embodiment 2

[0102] In this embodiment, a layout comparison schematic verification device for discrete devices is provided, such as Figure 4 As shown, the device includes:

[0103] A marking module 401, configured to mark ports of the discrete device on the layout of the discrete device;

[0104] A modification module 402, configured to modify the layout comparison schematic file, so that when extracting the netlist of the layout of the discrete device, the information of the marked port can be extracted;

[0105] A receiving module 403, configured to receive a verification operation for triggering the verification of the layout comparison schematic diagram;

[0106] The verification module 404 is used to extract the netlist of the layout, and compare the netlist and the pre-stored netlist file, so as to verify the schematic diagram of the layout comparison; the netlist file includes the discrete device to be verified port and process size information.

[0107] In the implementation of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More