Interlayer dielectric layer forming method and semiconductor device forming method

A technology of interlayer dielectric layer and dielectric layer, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems that the quality of the interlayer dielectric layer cannot be guaranteed, the performance of the device is affected, and holes cannot be completely eliminated.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

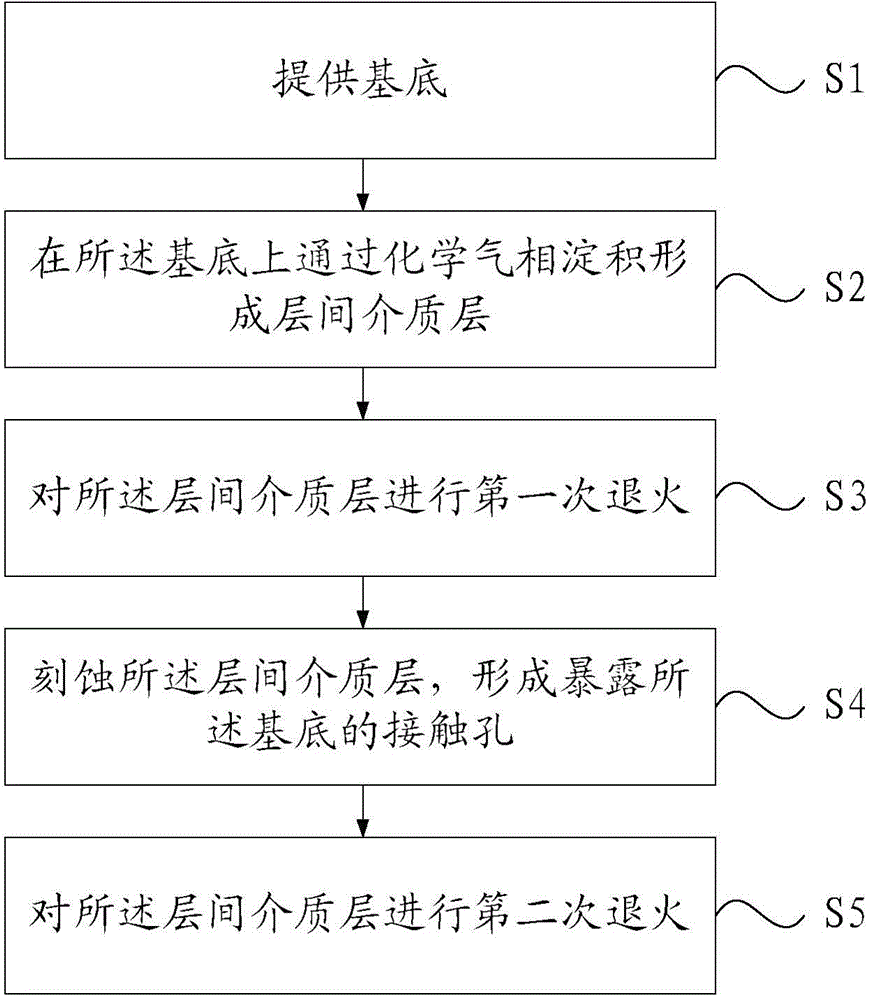

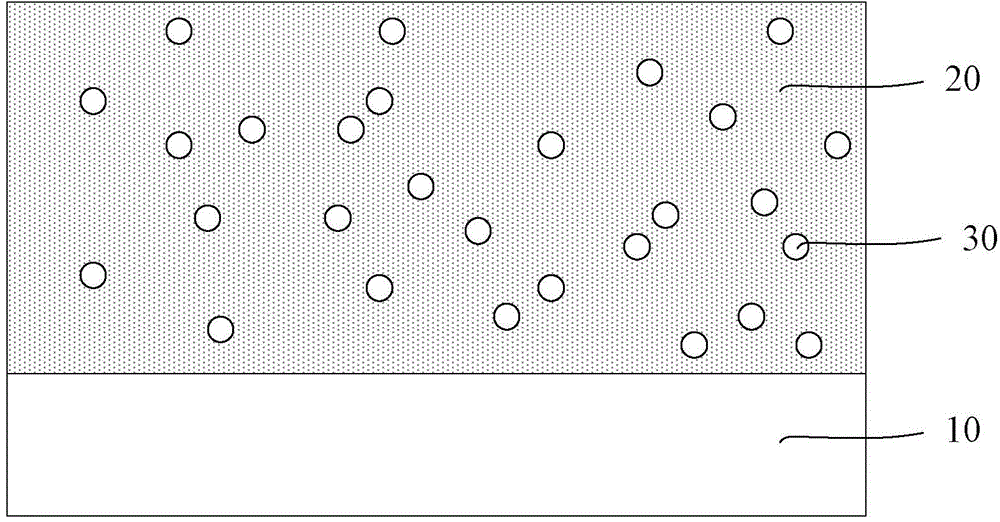

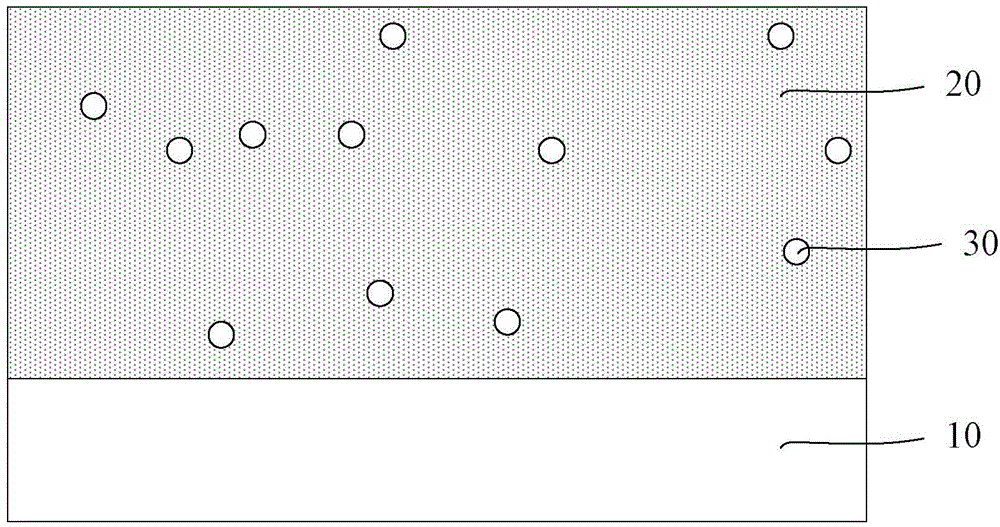

[0030] As mentioned in the background art, the quality of the current interlayer dielectric layer cannot meet the requirements. The inventors of the present application have found through long-term research that fluid chemical vapor deposition (FCVD) has been widely used in the formation of interlayer dielectric layers due to its advantages of strong hole filling. After the interlayer dielectric layer is formed by fluid chemical vapor deposition, an annealing process is usually required to remove holes that may appear in the interlayer dielectric layer during the formation process, improve the quality of the interlayer dielectric layer, and then perform an annealing process on the interlayer dielectric layer A subsequent etching process is performed. However, when the thickness of the interlayer dielectric layer is larger, more holes will be formed in the interlayer dielectric layer. Since some holes are far away from the surface of the interlayer dielectric layer, the common...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More