Method for forming gate channel and corresponding semiconductor structure

A semiconductor and channel technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of gate patterns that cannot be accurately aligned and alignment marks that cannot be measured, and achieve protection Effects that are not damaged

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In the following description, numerous specific details are given in order to provide a more thorough understanding of the present invention. Of course, the present invention can also have other embodiments besides these detailed descriptions.

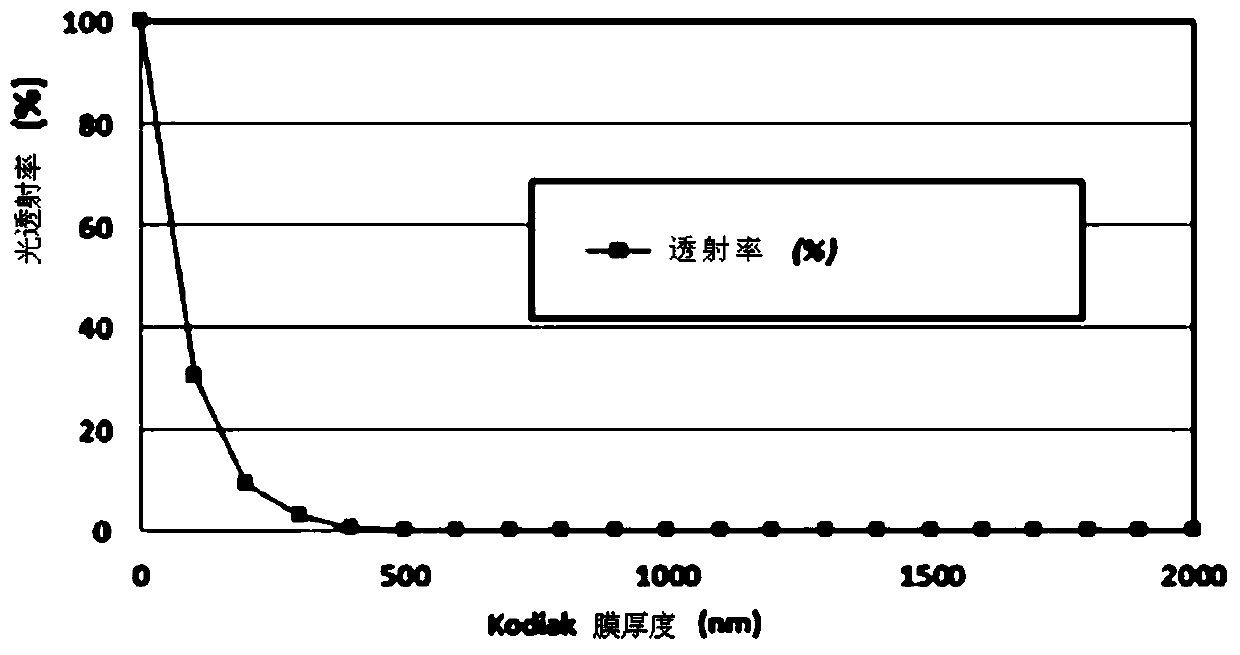

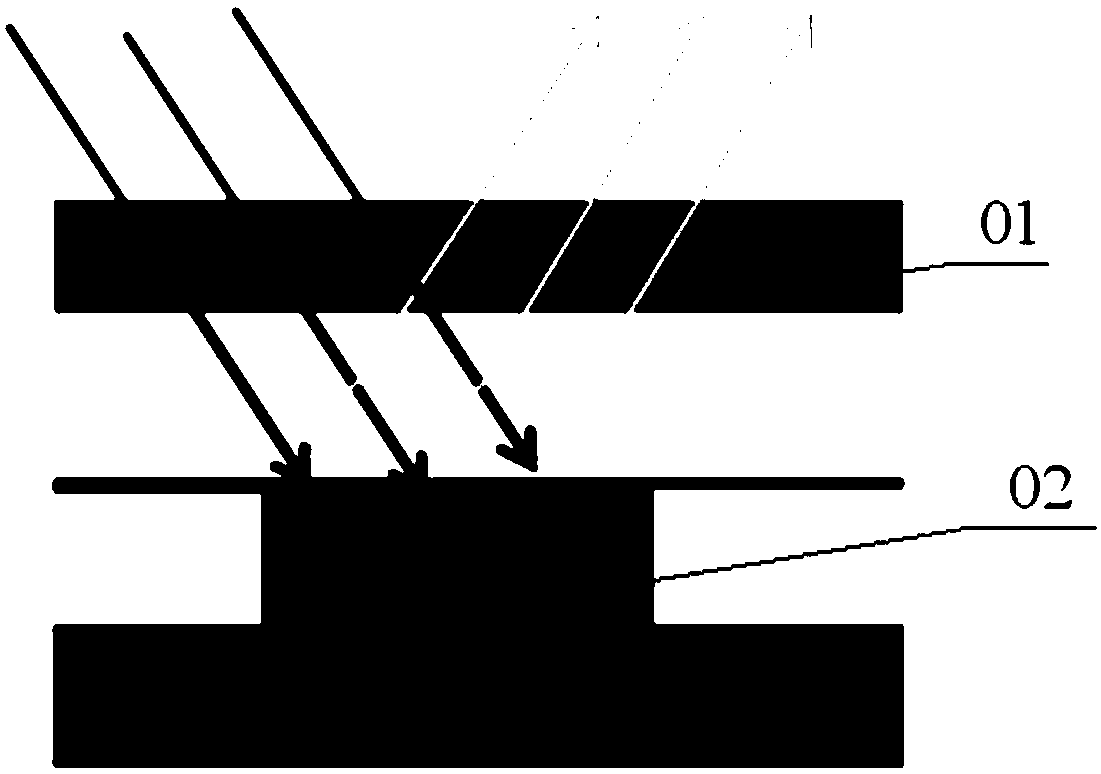

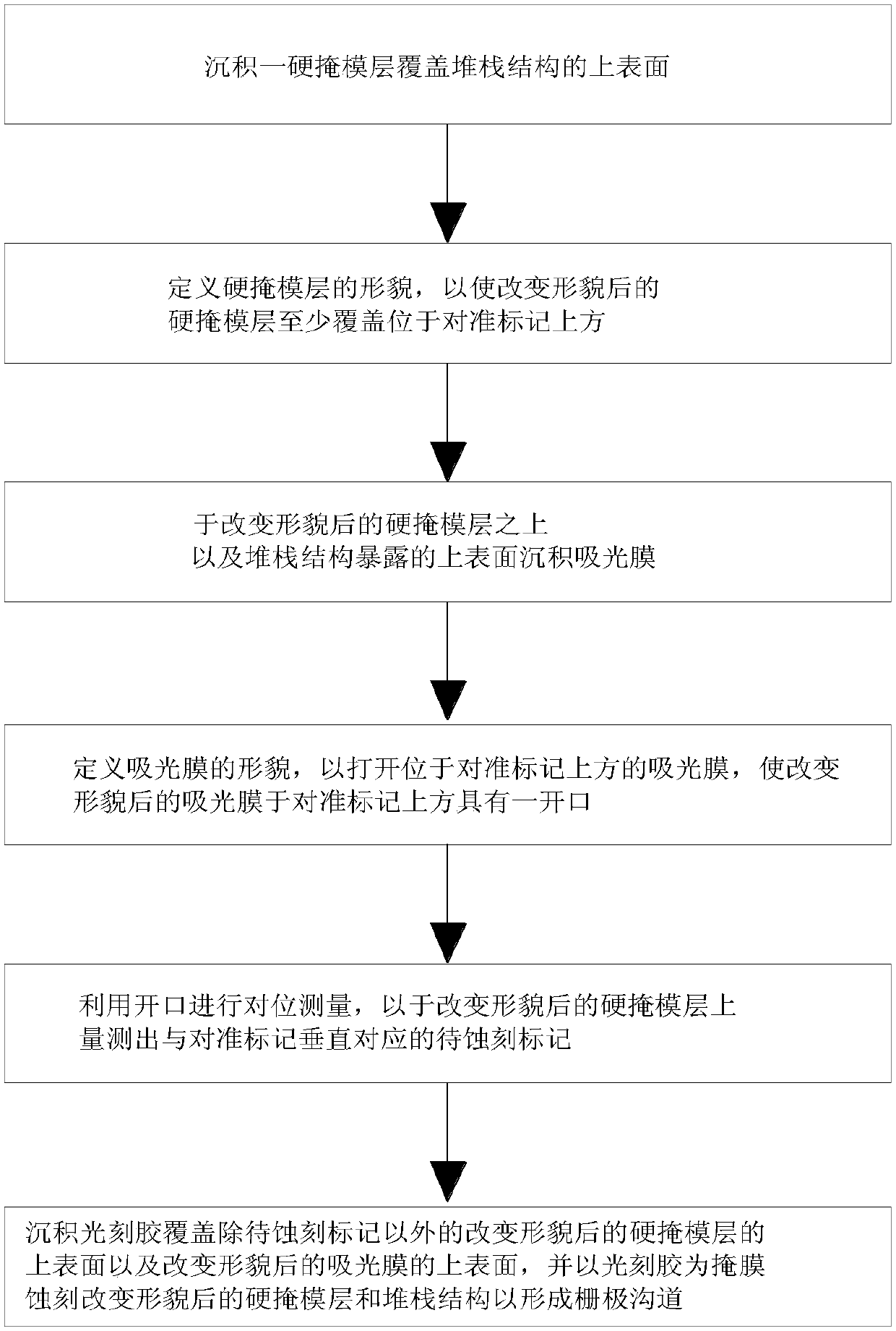

[0042] The method for forming a gate channel of the present invention is mainly applied to a stack structure in which an alignment mark (or called an overlay mark) is pre-embedded, such as image 3 As shown, it includes: depositing a hard mask layer first, and etching so that the hard mask layer covers at least the alignment marks; then depositing a light-absorbing film, and etching so that the light-absorbing film has an opening above the alignment marks; and then performing Alignment measurement, marking the gate channel corresponding to the mark to be etched on the hard mask layer; and then etching according to the mark to be etched to form the gate channel.

[0043] The steps of the method for forming a gate channel of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com