Real-time flat-field correction method of area array camera based on FPGA

A flat-field correction and area array camera technology, applied in the field of image algorithms, can solve problems such as difficult to achieve, limited internal resources, unable to meet the requirements of high-resolution image storage resources, etc., to achieve the effect of high output image quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] A preferred embodiment of the present invention will be described in detail below with reference to the accompanying drawings.

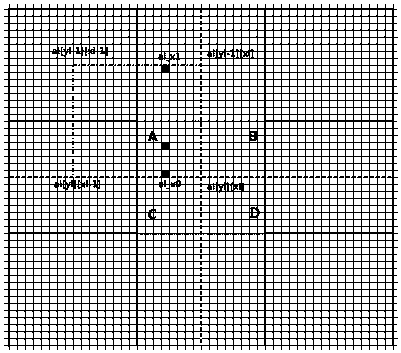

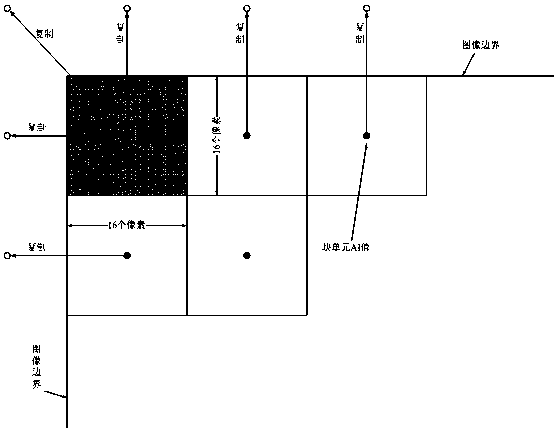

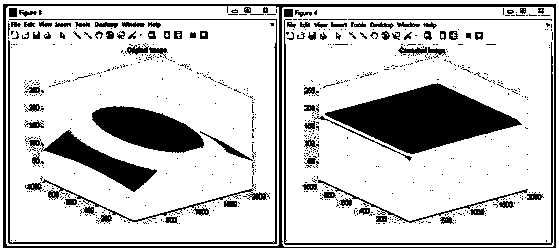

[0034] The FFC algorithm is mainly used to correct the response inconsistency and non-ideal errors of the sensor array. The basic algorithm is as follows: Yi=Xi*ai, where Yi is the corrected data, and Xi is the original data output by the sensor. Due to the high resolution of the area array camera, if the single-point FFC operation is performed directly, it is necessary to maintain an ai array of the same size as the image resolution, which consumes too much resources, and it is not feasible to implement it directly in the FPGA, and the algorithm needs to be optimized. The primary purpose of optimization is to reduce the consumption of storage resources by the algorithm. In order to reduce the demand for storage resources, a block-based calculation method can be used. In this embodiment, a 16x16 pixel block is used as the basic unit to perform ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More