Patents

Literature

50 results about "Real time algorithm" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

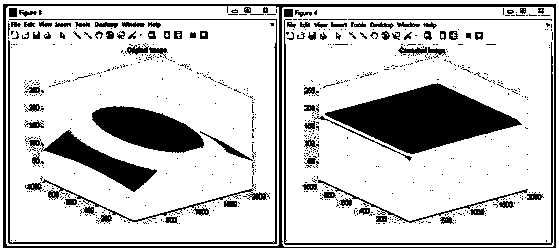

Parking lot detection method

InactiveCN107886080AAdapt to scene changesMeet real-timeImage enhancementImage analysisReal time algorithmComputer science

The invention discloses a parking lot detection method, which comprises the following steps that: (1) obtaining information around a vehicle as input; (2) carrying out mark point detection on the input obtained in the (1); and (3) through the mark point obtained in (2), realizing parking lot deduction. An experiment verifies that the algorithm disclosed by the invention can accurately judge a parking lot position in a round-looking image and can conform to real-time algorithm efficiency. The method has the function that a key step in the automatic parking scene of an automatic driving field gives the accurate position of the parking lot in a vehicle coordinate system. A purpose that the position of the parking lot can be detected through the own camera of the vehicle on the basis of no additional infrastructures is realized.

Owner:TONGJI UNIV

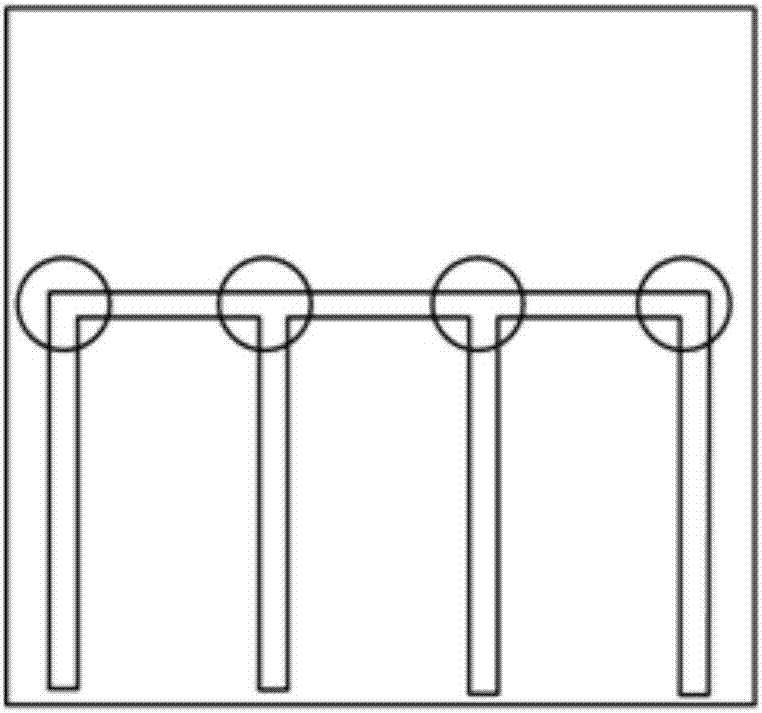

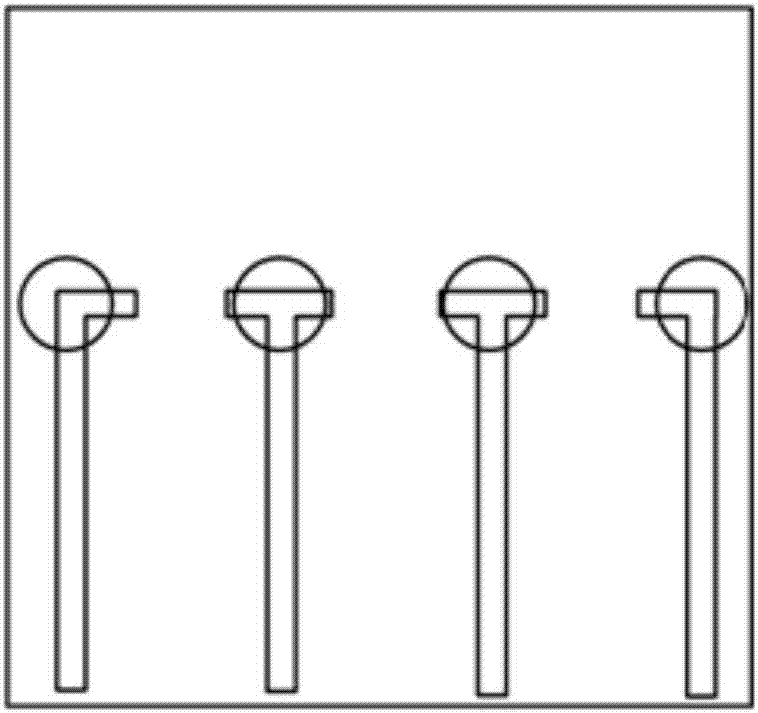

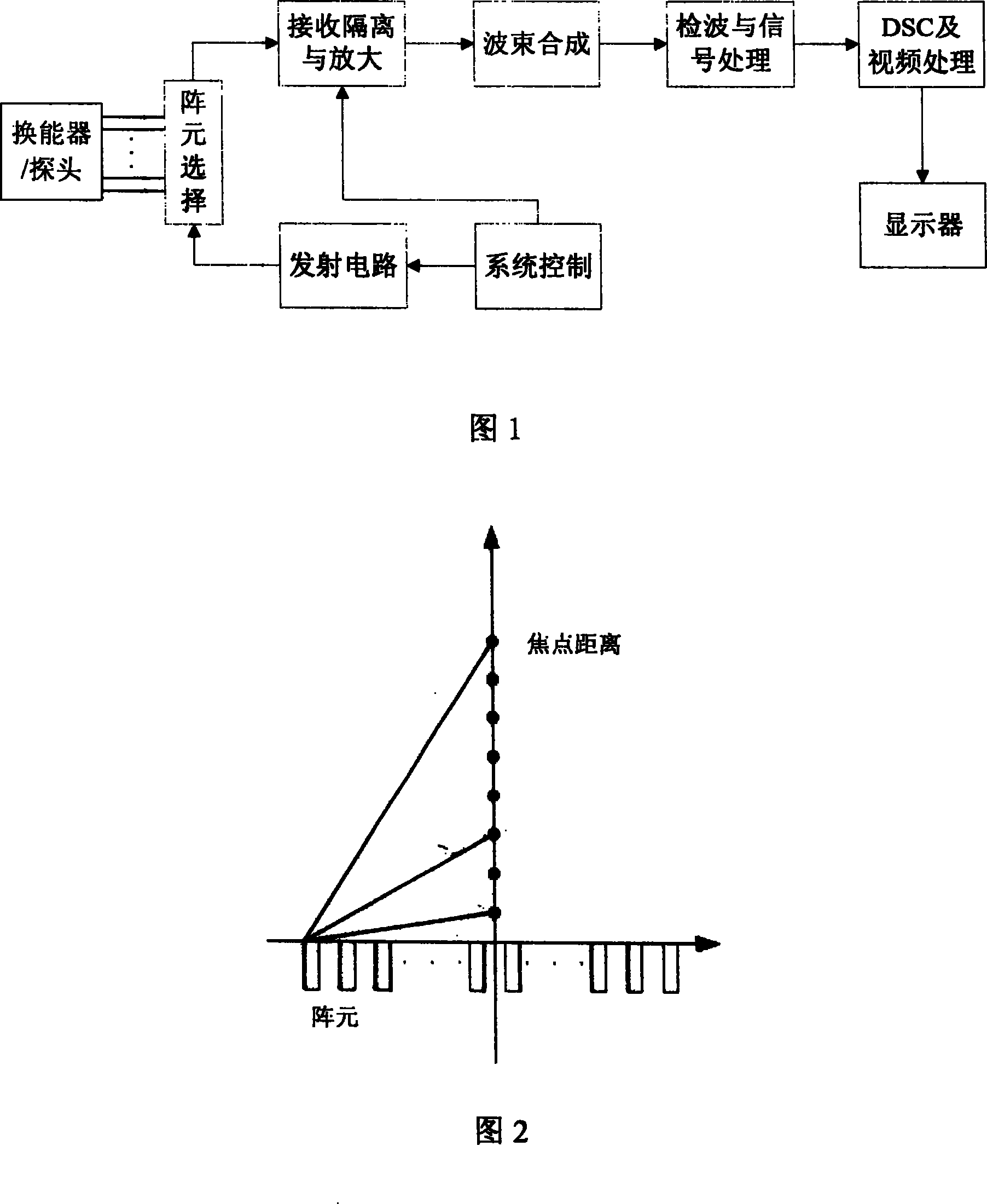

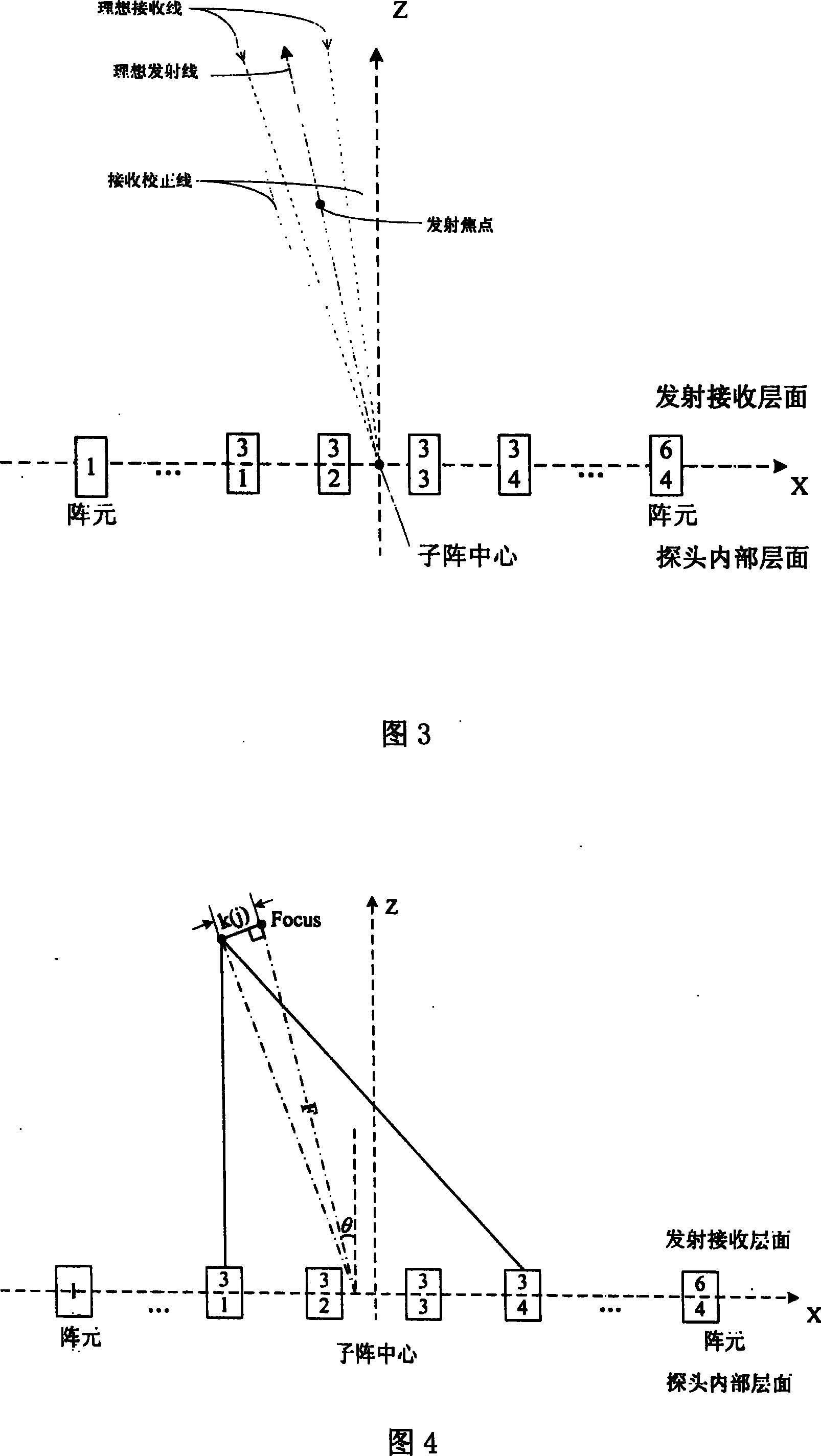

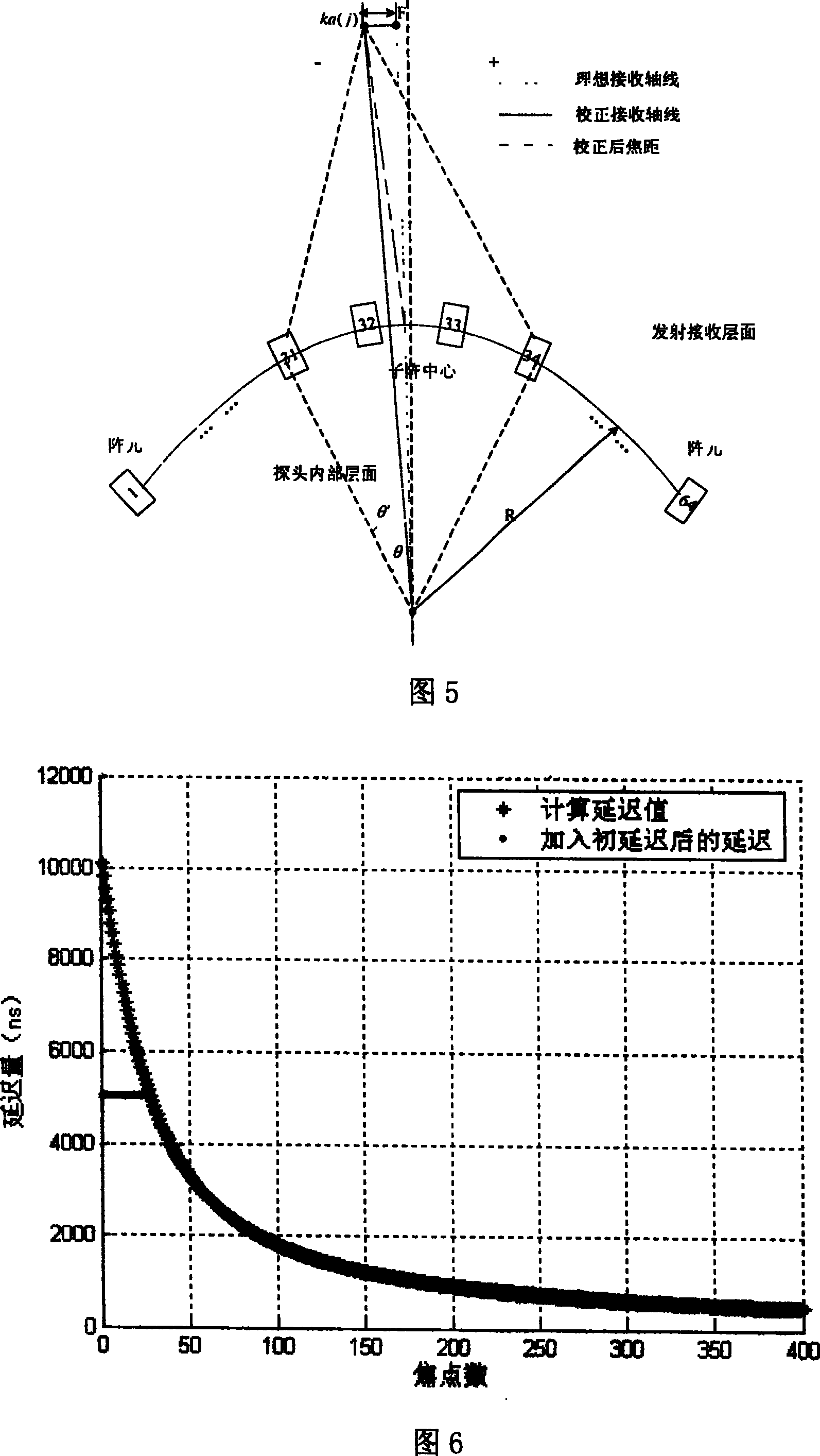

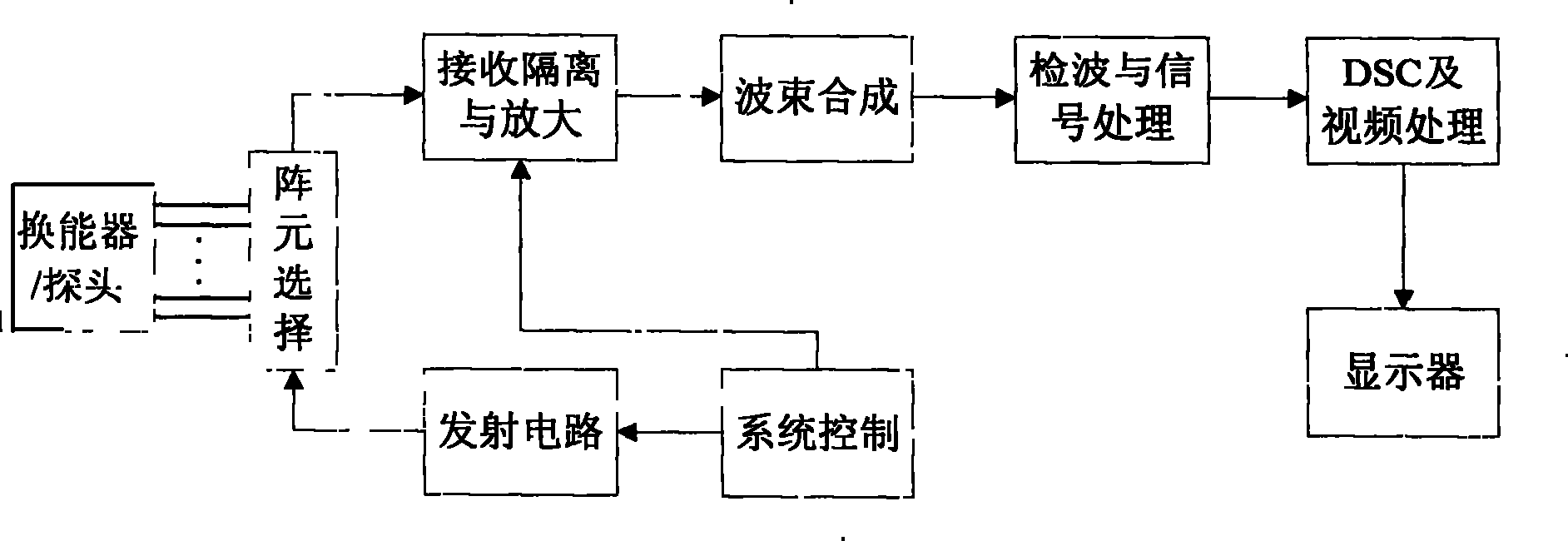

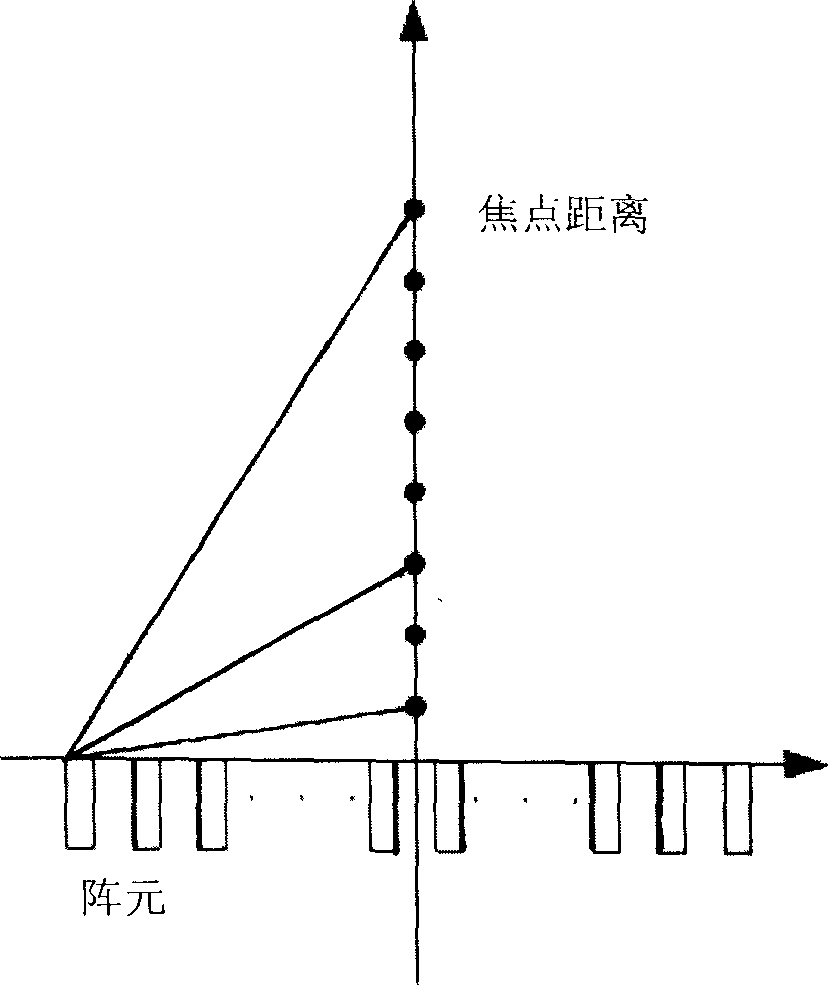

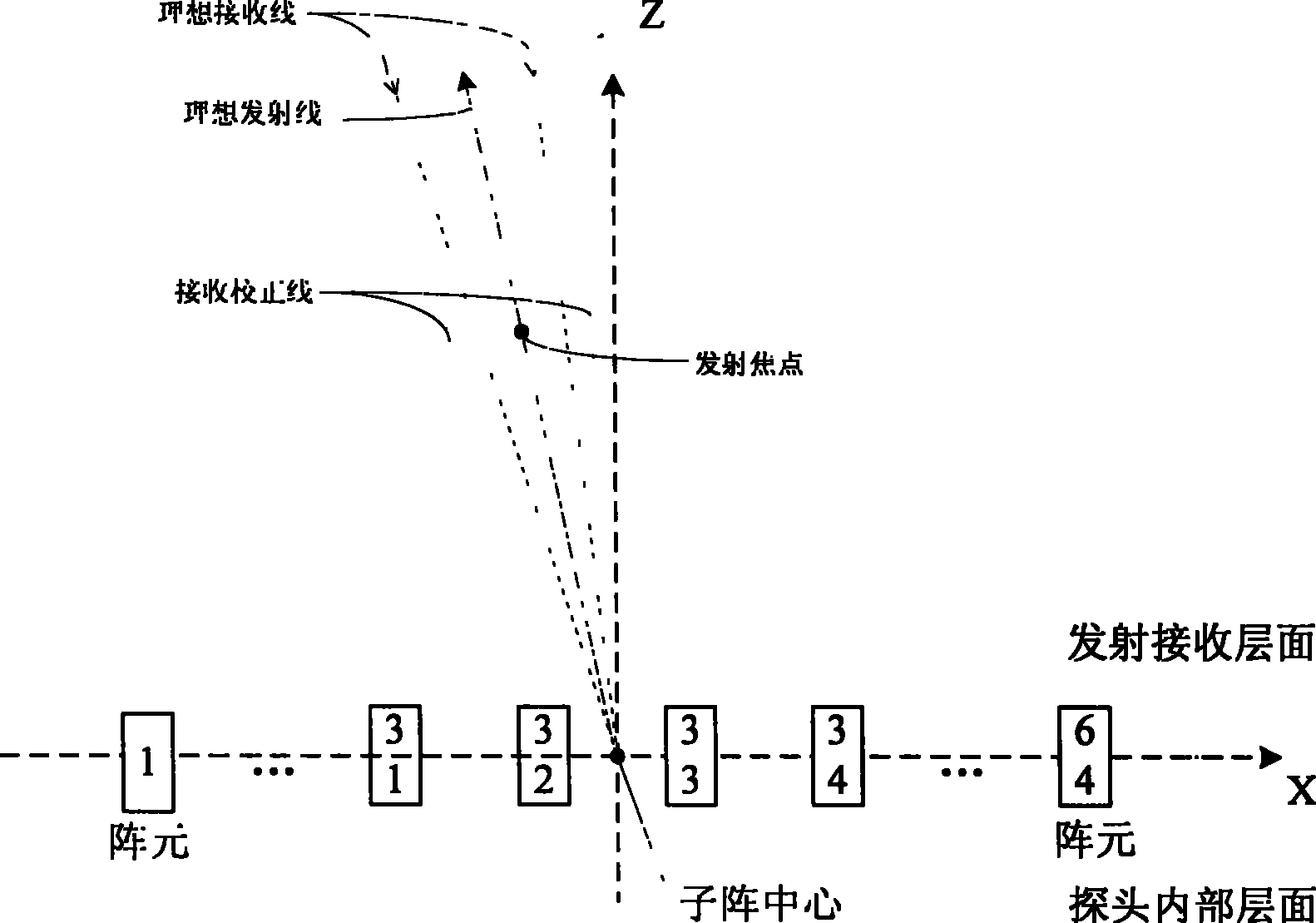

Ultrasonic beam synthetic focusing parameter real-time algorithm and device thereof

ActiveCN101097256AReduce the impactAchieving multi-beam correctionSound producing devicesAcoustic wave reradiationReal time algorithmUltrasonic beam

The invention relates to a kind of method and device to calculate synthesized focusing parameter of supersonic wave beam, and it sets the initial parameter, and adds 2*c2*n+2*tD*n to first intermediate variable sum to calculate the new value of first intermediate variable, and calculate the second intermediate variable sum_a: sum_a=sum-2*T-2*tD+1, and compares the absolute value of first intermediate variable sum and second intermediate variable sum_a, if |sum_a|<|sum|, it will iterative compute the focus matrix delay inequality tD, and the value of first intermediate variable sum is set to be the second intermediate variable sum_a, and the focus bite is 0 or 1 according to the comparing result and output. It just needs to load the limited initial parameter to obtain the ideal focusing parameters by the iterative computation. It fits for linear array, phased array and protrusion array. And it fits for multiple-beam, and supports the multiple-beam to receive the focusing calibration. It can realize in FPGA, and can be used in system with random channels and focuses.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD

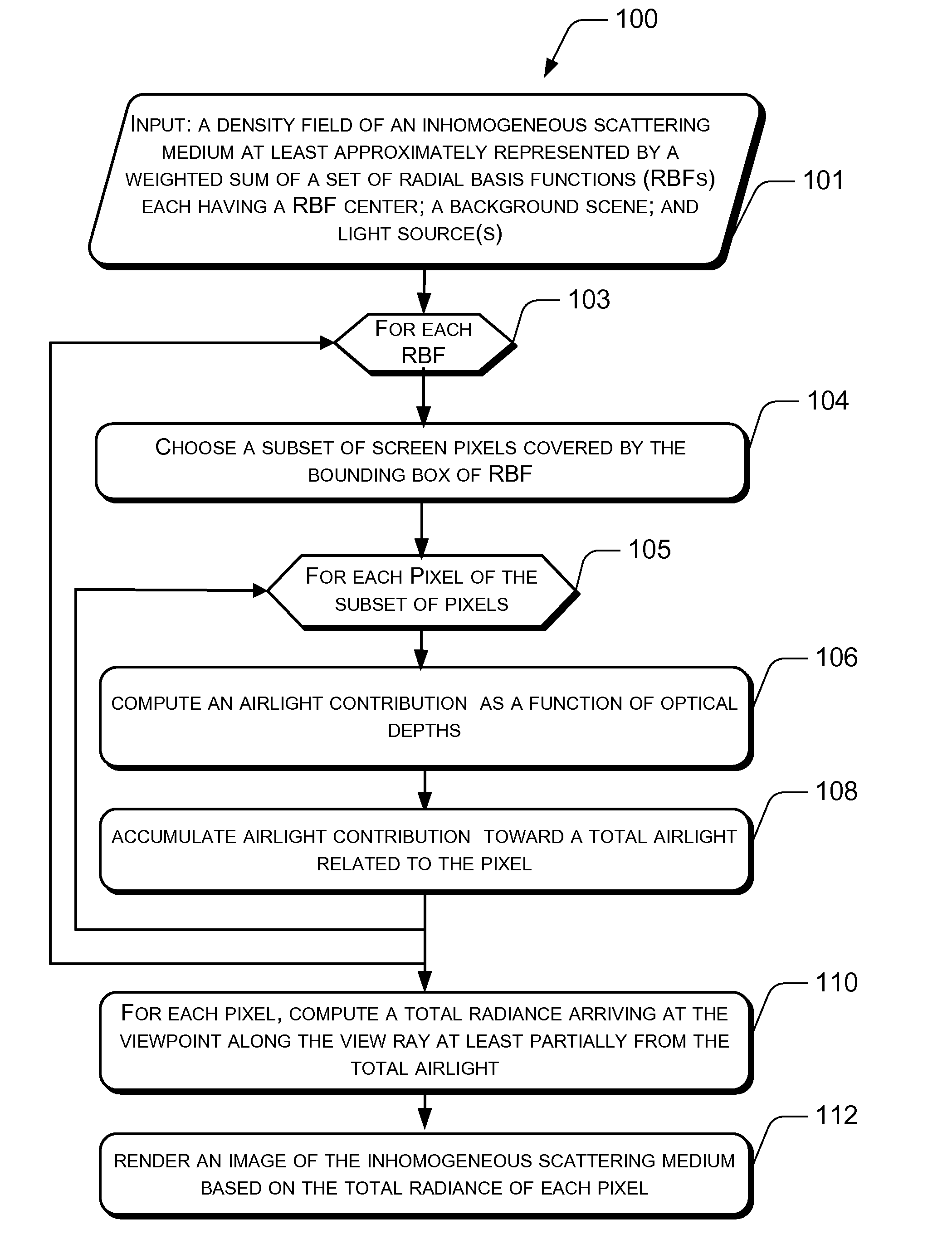

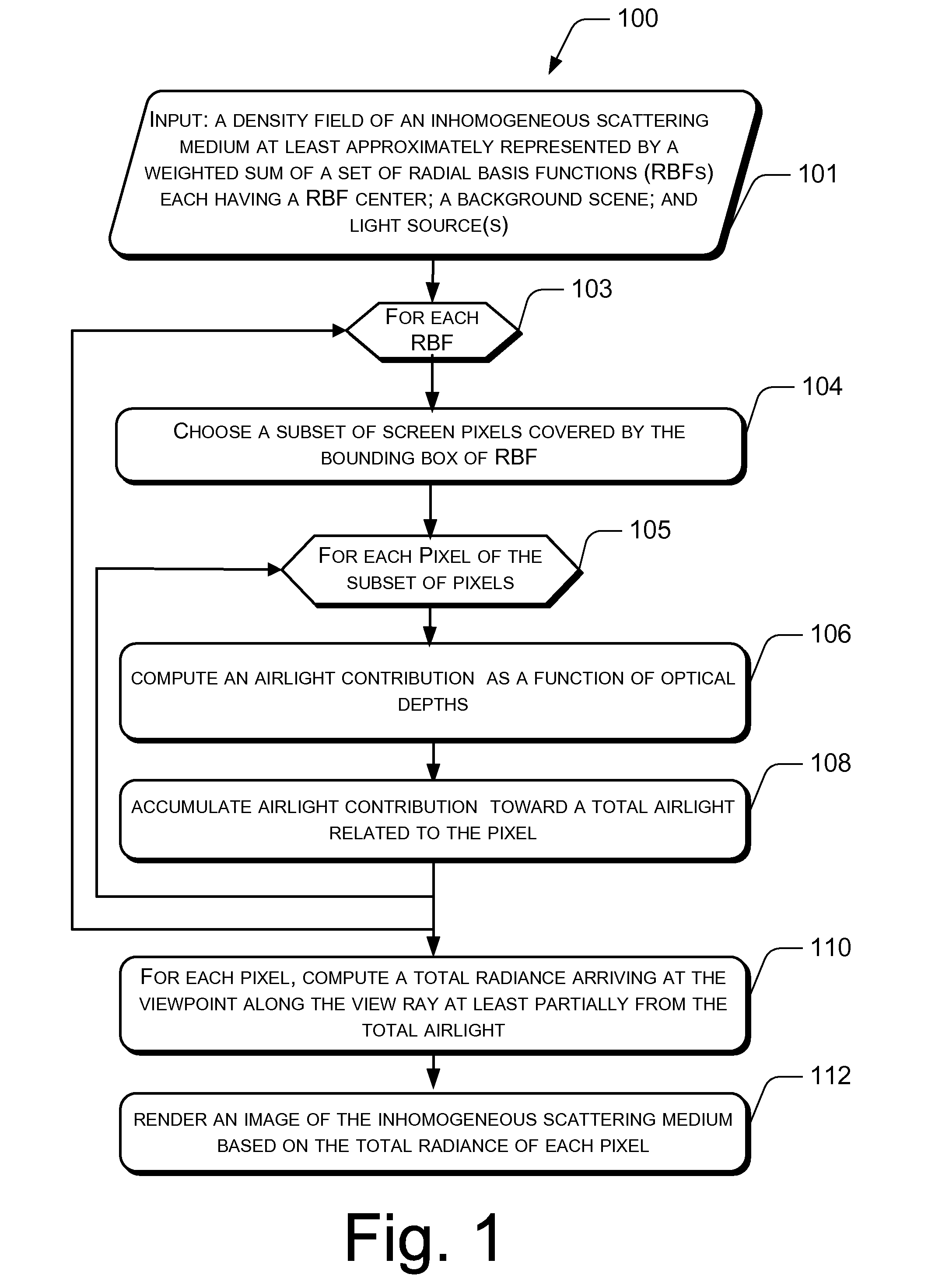

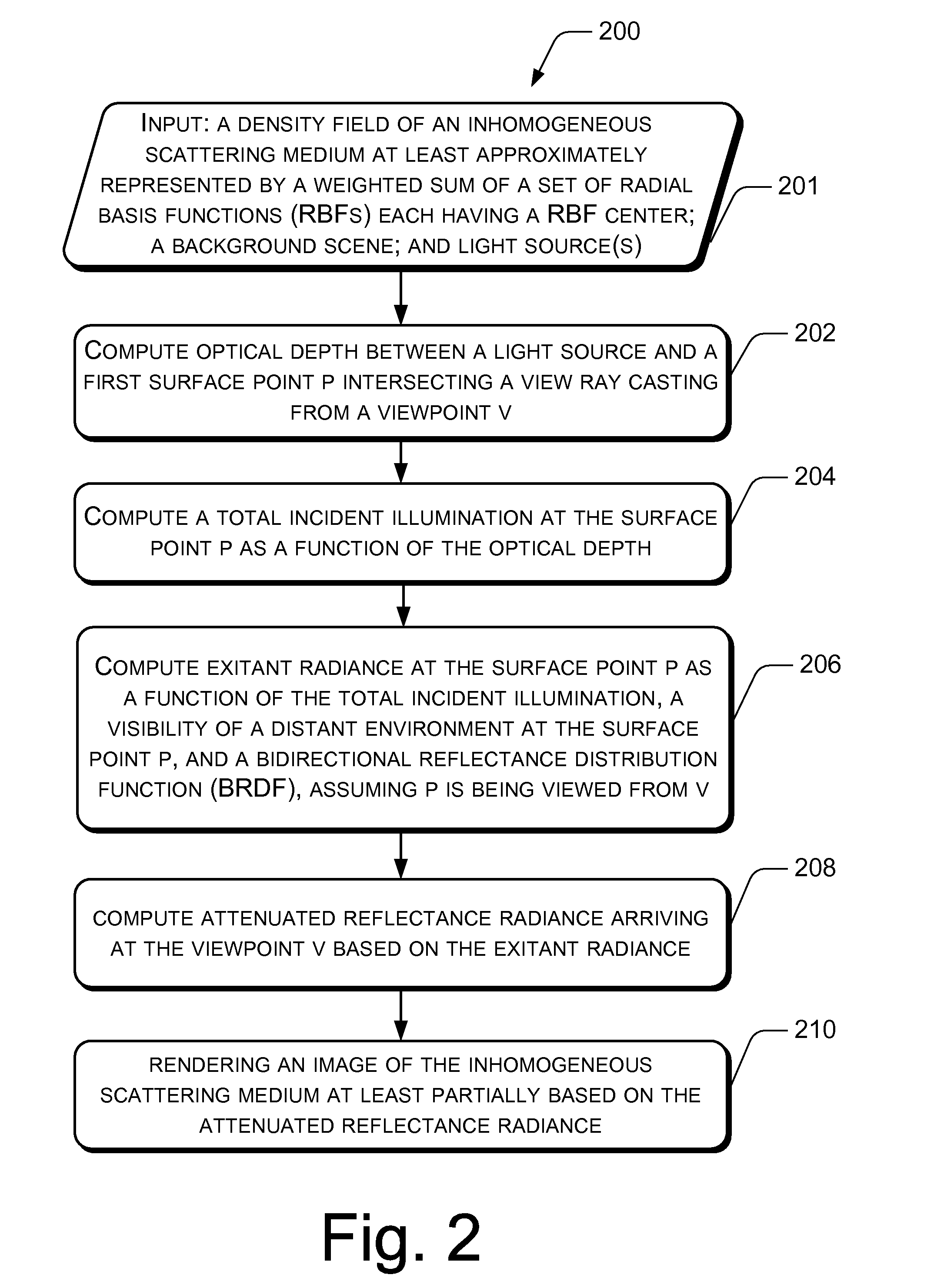

Real-Time Rendering of Light-Scattering Media

InactiveUS20090006051A1Simple optical depth averagingAnalogue computers for heat flow3D-image renderingShadowingsPoint light

A real-time algorithm for rendering an inhomogeneous scattering medium such as fog is described. An input media animation is represented as a sequence of density fields, each of which is decomposed into a weighted sum of a set of radial basis functions (RBFs) such as Gaussians. The algorithm computes airlight and surface reflectance of the inhomogeneous scattering medium. Several approximations are taken which lead to analytical solutions of quantities such as an optical depth integrations and single scattering integrations, and a reduced number of integrations that need to be calculated. The resultant algorithm is able to render inhomogeneous media including their shadowing and scattering effects in real time. The algorithm may be adopted for a variety of light sources including point lights and environmental lights.

Owner:MICROSOFT TECH LICENSING LLC

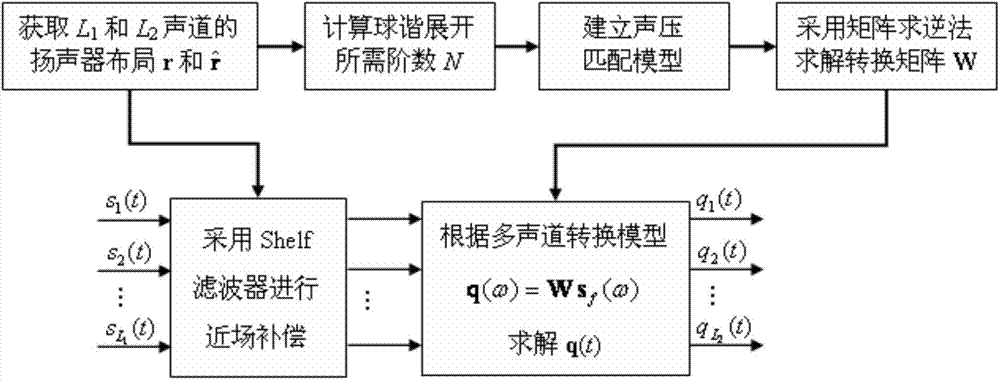

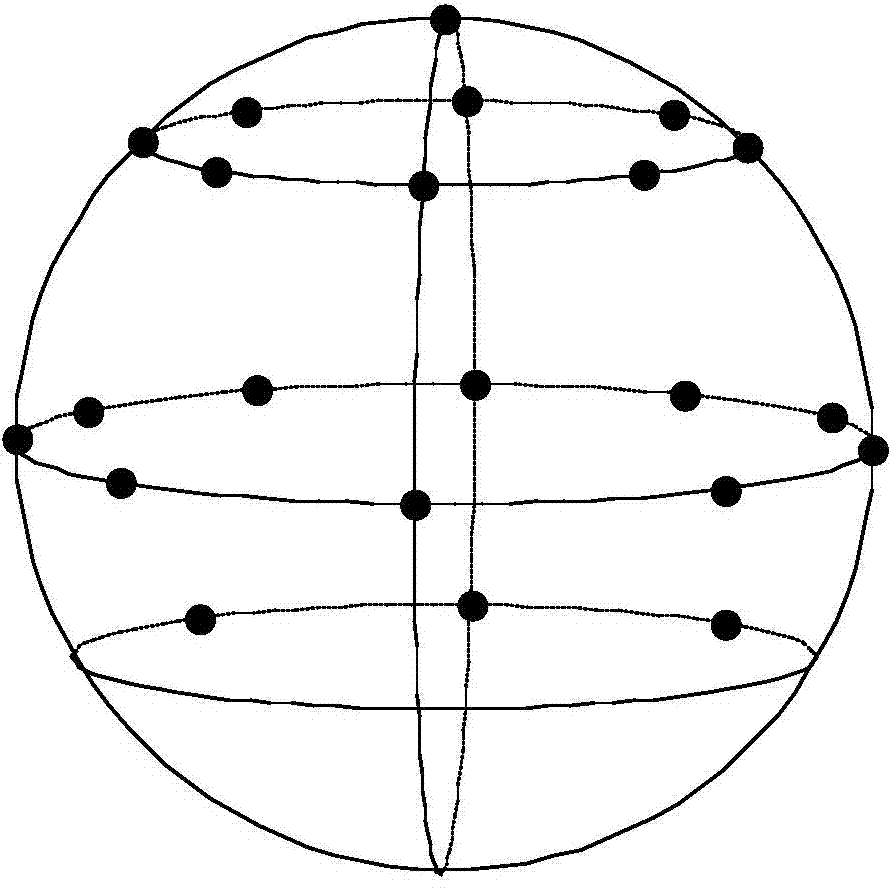

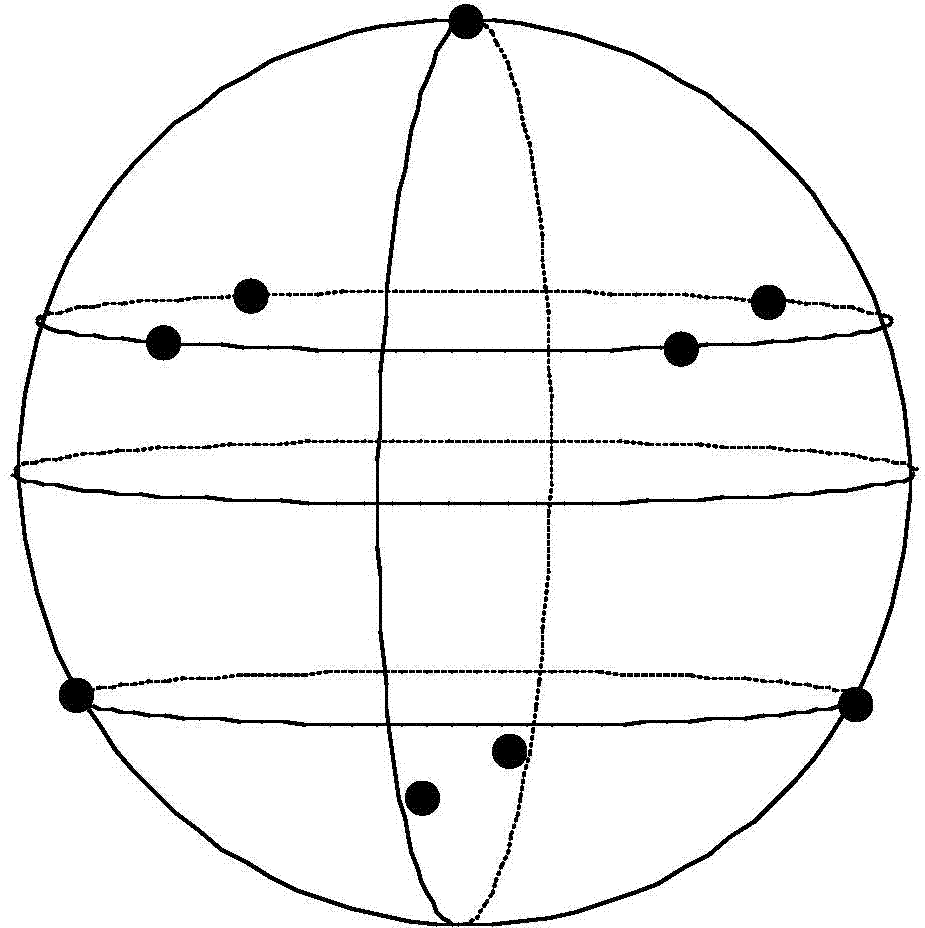

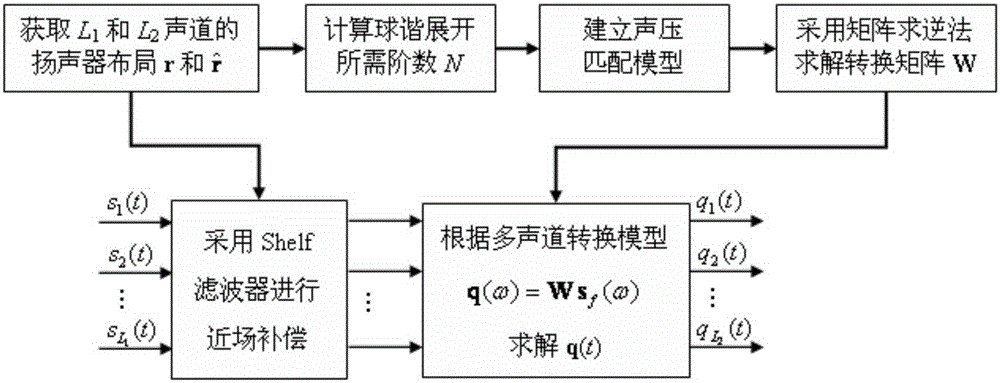

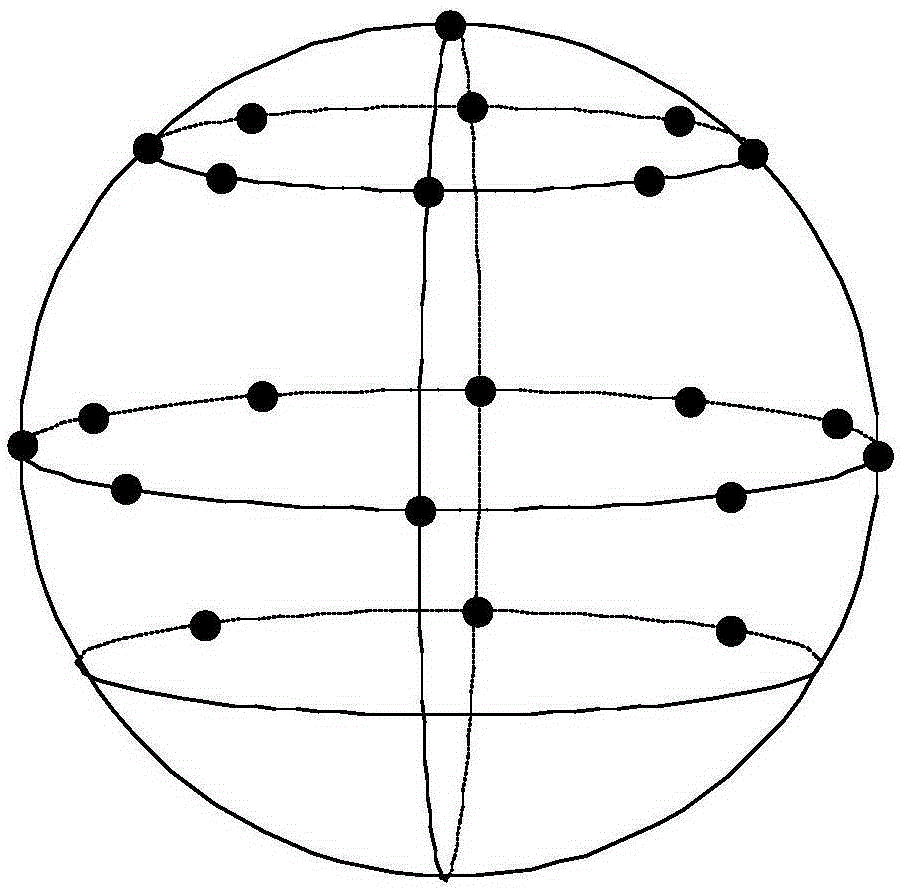

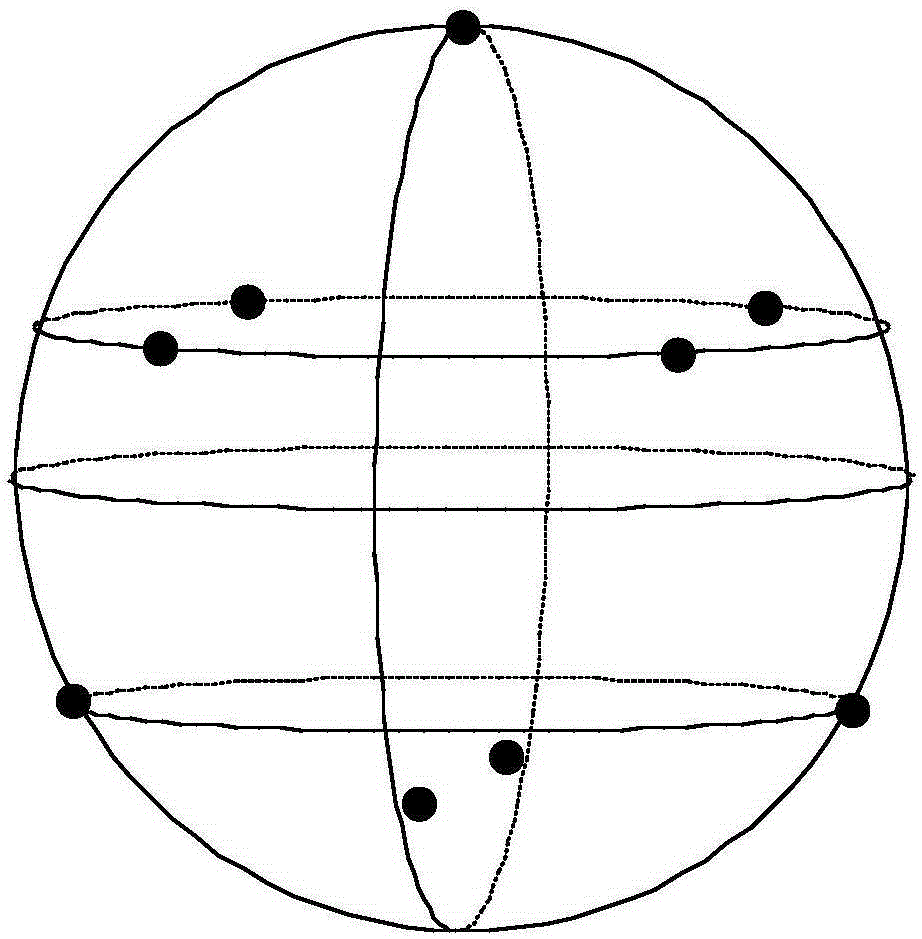

Multi-channel conversion method based on spherical harmonic expansion

InactiveCN103888889APerfect theoretical basisReduce computational complexityStereophonic systemsReal time algorithmSpherical harmonics

The invention provides a multi-channel conversion method based on spherical harmonic expansion. The multi-channel conversion method is mainly used for converting an L1-path multi-channel loudspeaker system into an L2-path multi-channel loudspeaker system. Based on the linear superposition theory of a sound field, spherical harmonics with corresponding orders are adopted according to different numbers of channels for calculating the sound field of the loudspeaker system which is not converted and the sound field of the loudspeaker system which is obtained after conversation, and gain coefficients of each loudspeaker of the loudspeaker system obtained after conversation are calculated under the situation that the spherical harmonic expansion sound field of the loudspeaker system which is not converted and the spherical harmonic expansion sound field of the loudspeaker system which is obtained after conversation are the same under the certain order. According to the multi-channel conversion method based on spherical harmonic expansion, the real-time algorithm complexity is low, the sound field of an original reproducing system in a listening area can be recovered on the system obtained after conversation, the method can be used for streamline compression and hybrid technology of a multi-channel three-dimensional audio system, effective compatibility of various loudspeaker reproduction systems can be achieved, and the transmission bandwidth is reduced.

Owner:BEIJING UNIV OF TECH

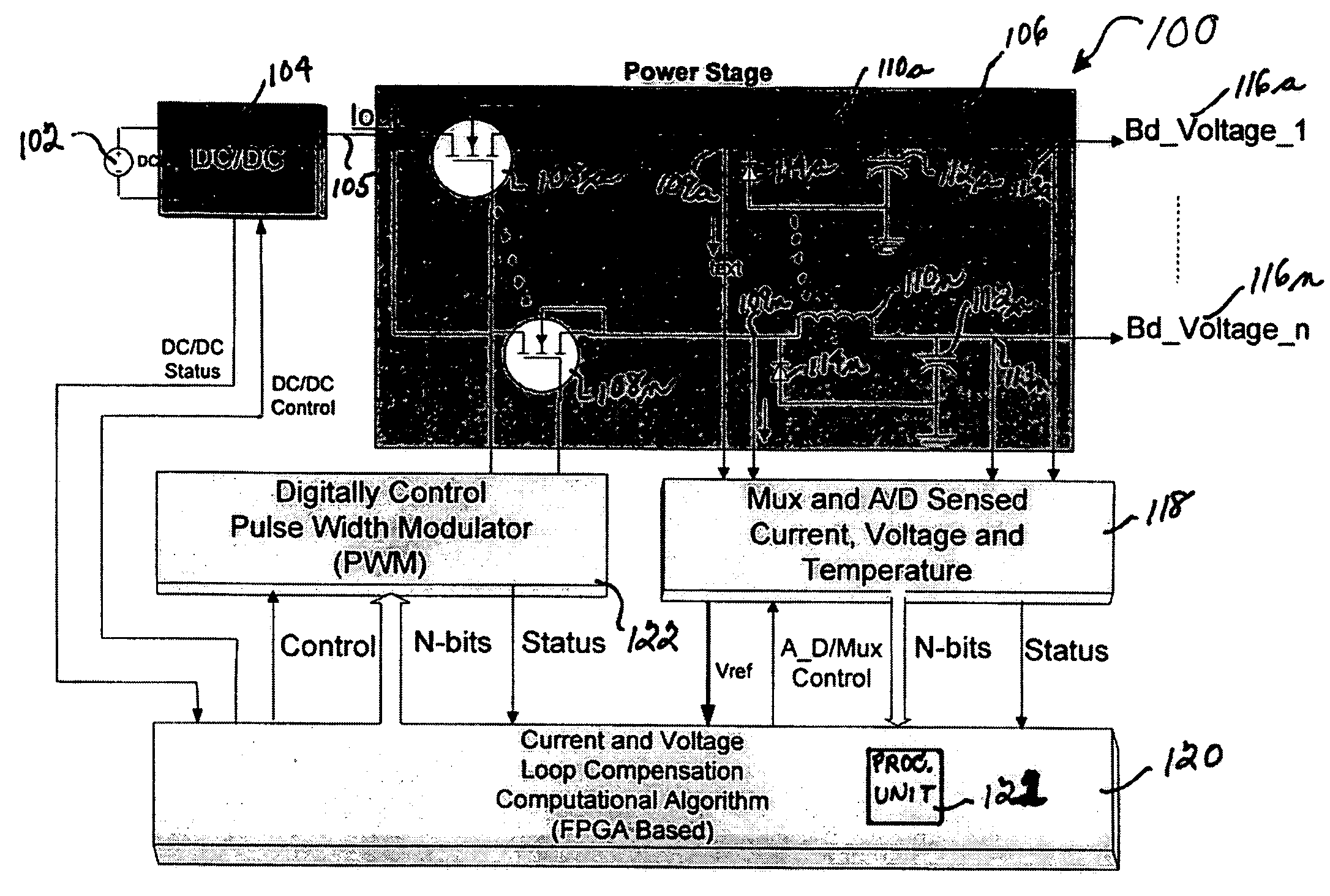

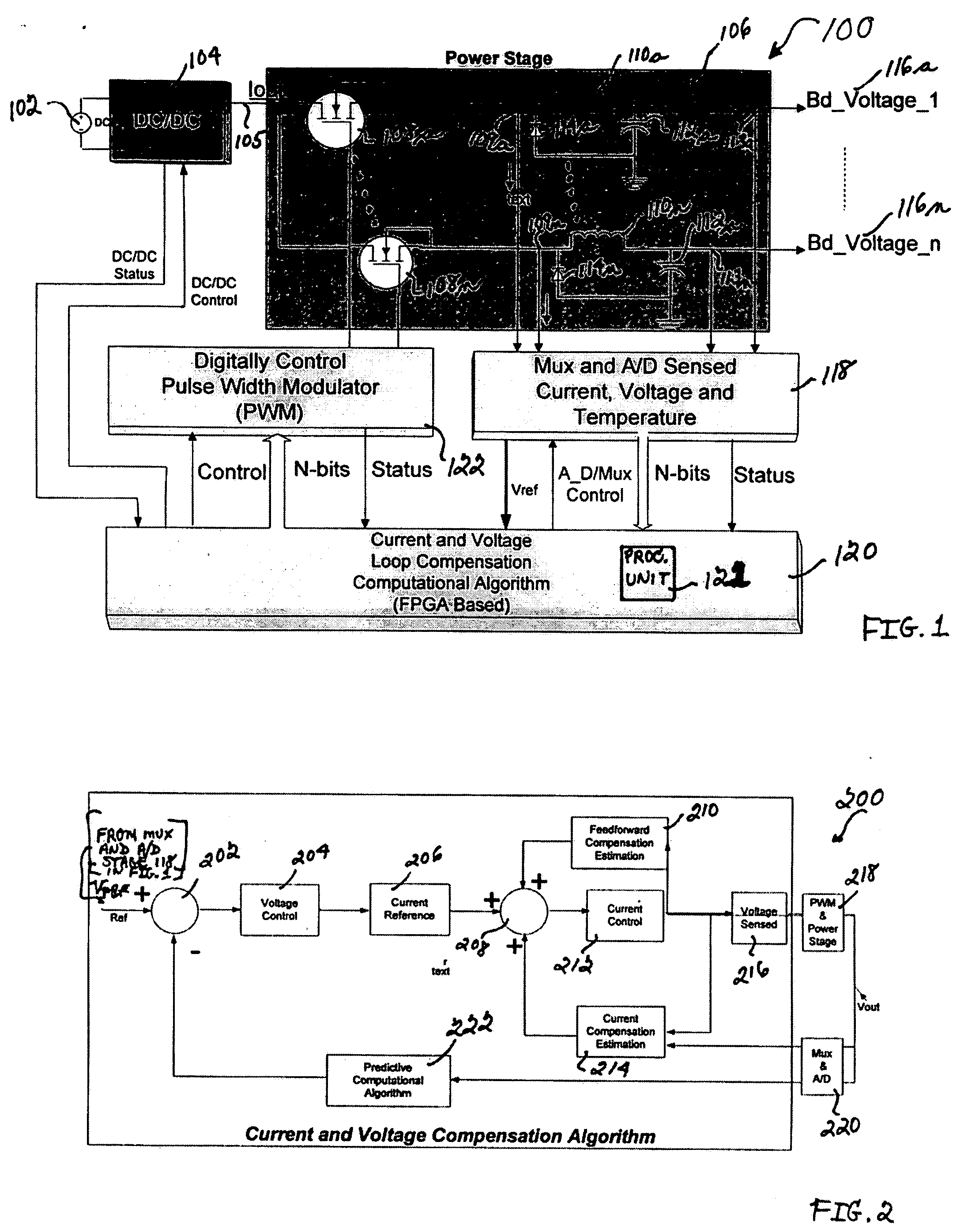

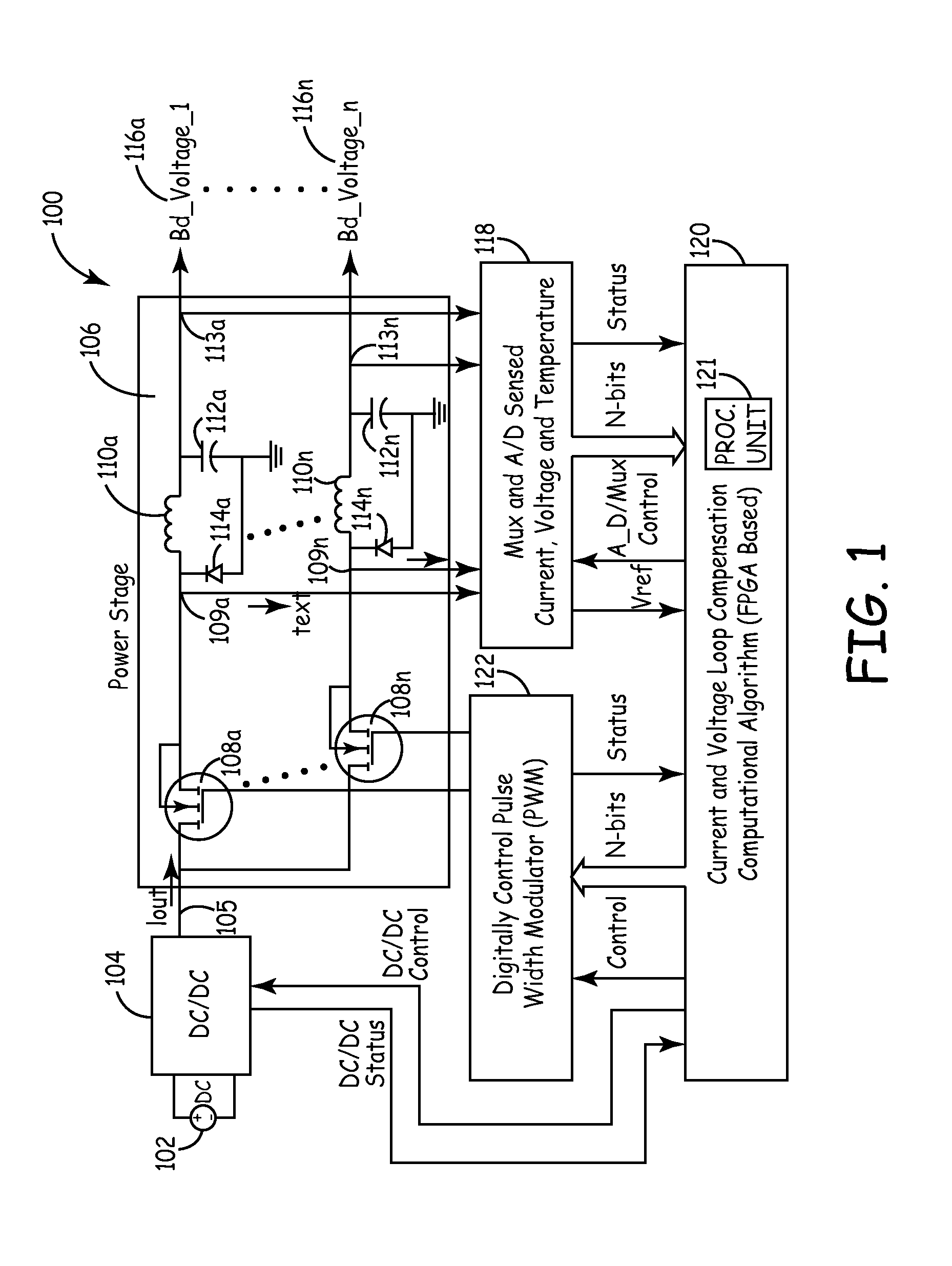

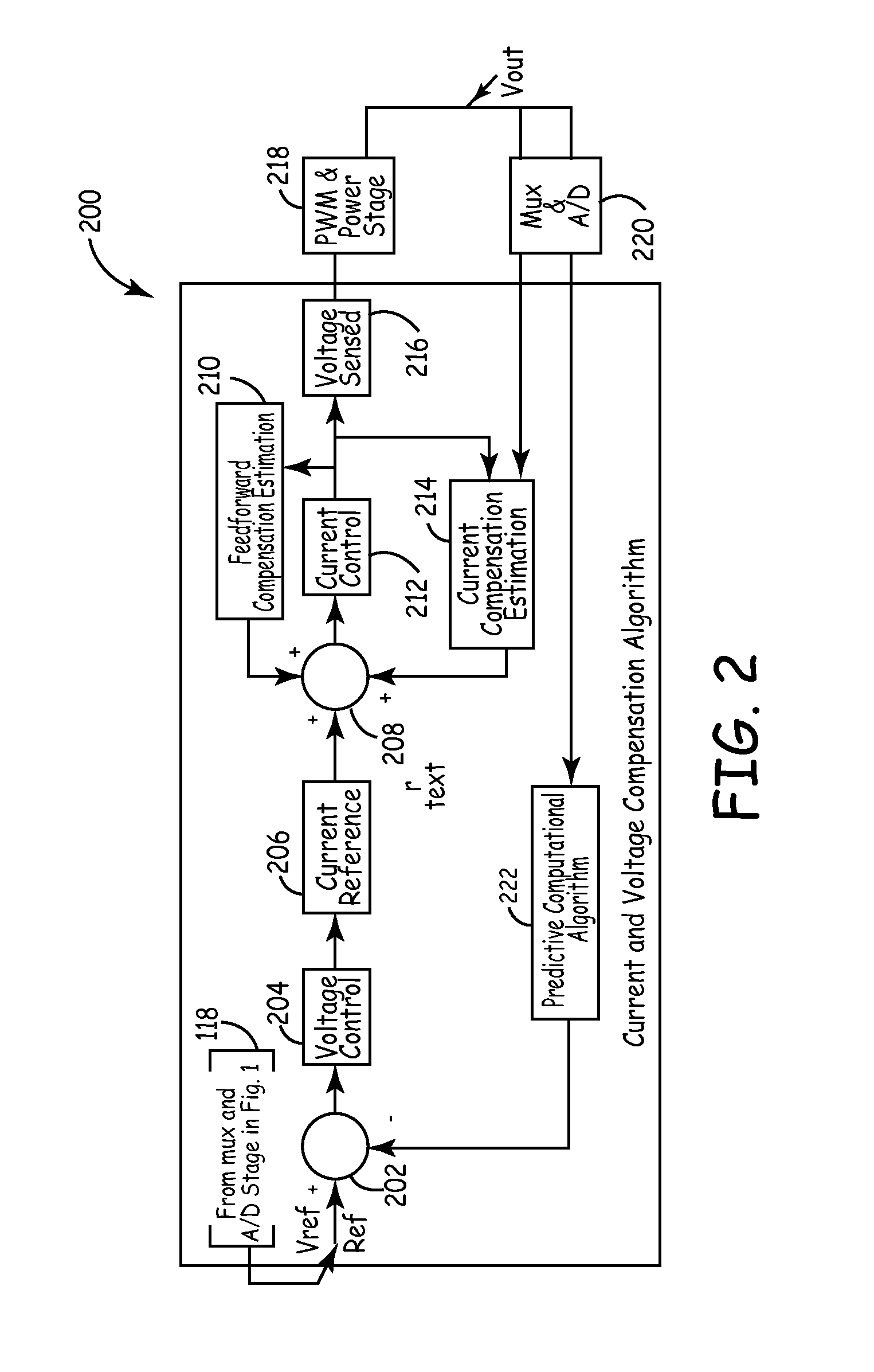

Adaptive digital power control system

InactiveUS20070010917A1Reduce voltageHigh currentMechanical power/torque controlLevel controlLow voltageControl signal

An adaptive digital power control system is disclosed, which implements a digitally controlled, near real-time algorithm to accommodate multiple loop current mode controls for low voltage, high performance computing system power needs. For example, an adaptive digital power control system that is implemented with an FPGA to generate low voltages for high performance computing systems is disclosed, which includes a current and voltage loop compensation algorithm that enables the adaptive digital power control system to dynamically compensate for high current transients and EMI-related noise. The current and voltage loop compensation algorithm uses a combination of linear predictive coding and Kalman filtering techniques to provide dynamic current and voltage compensation, and implement a feed-forward technique using knowledge of the power system's output parameters to adequately adapt to the system's compensation needs. More specifically, an adaptive digital power control system is disclosed, which includes a power stage for generating a plurality of low voltages, a multiplexer and A / D converter stage for receiving and converting the plurality of low voltages and a plurality of associated currents to a plurality of digital voltage and current signals, a current and voltage compensation algorithm stage for receiving the plurality of digital voltage and current signals and generating a plurality of digital voltage and current compensation control signals using linear predictive coding, Kalman filtering and feed-forward estimation techniques, and a digitally controlled pulse width modulator stage for receiving the plurality of digital voltage and current compensation control signals and controlling the duty cycles of a plurality of transistor switching devices in the power stage. Thus, the adaptive digital power control system can dynamically compensate for high current transients and EMI-related noise generated in low voltage power systems for high performance computing systems.

Owner:HONEYWELL INT INC

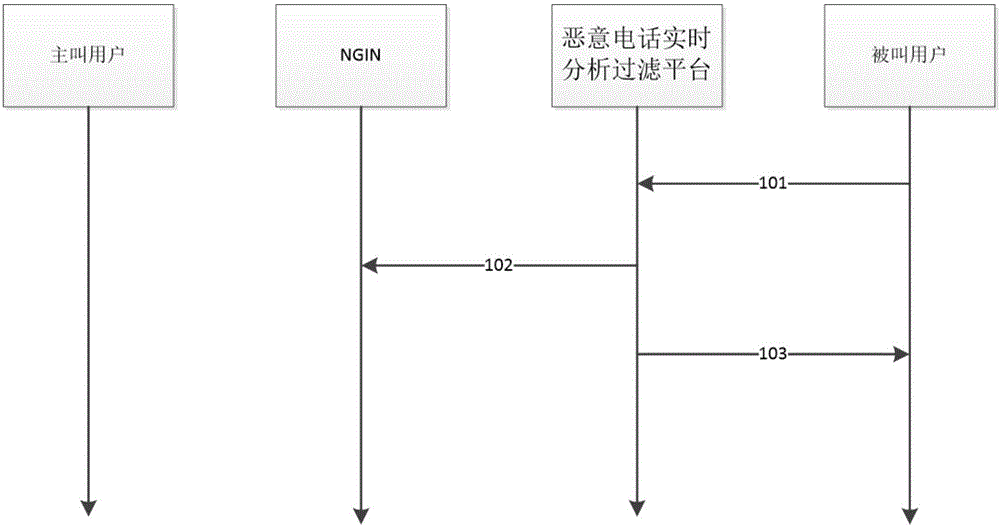

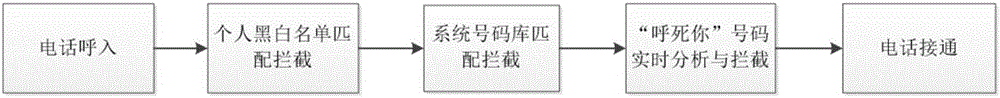

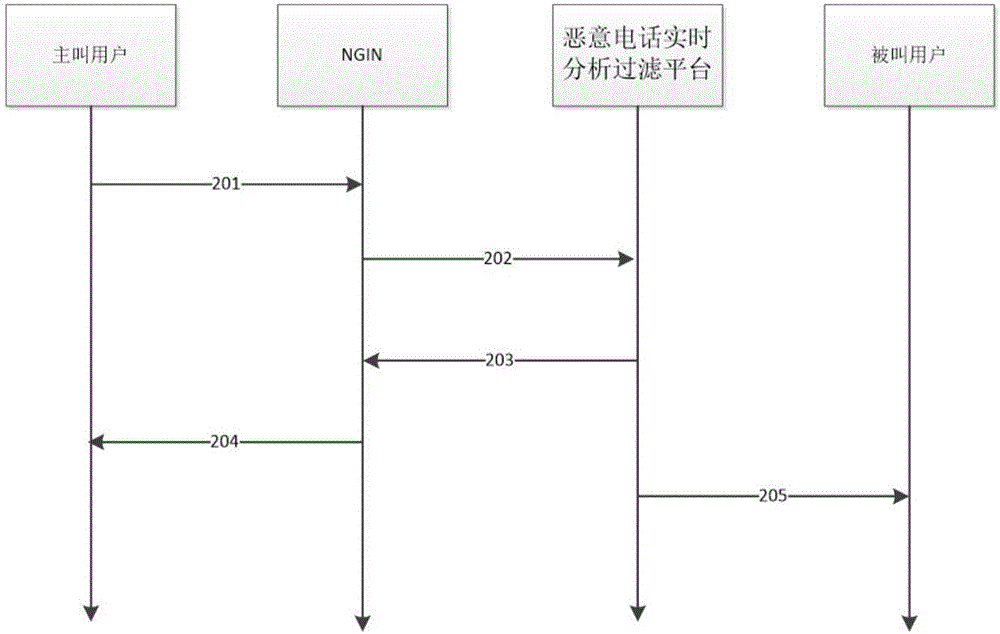

Method and system for realizing filtering of malicious calls through real-time algorithm

ActiveCN106506769ARelieve the stress of analyzing interceptsHigh efficiency in filtering malicious callsSubstation equipmentAutomatic exchangesReal time algorithmReal time analysis

The invention belongs to the technical field of mobile telephone communication, and particularly relates to a method for realizing filtering of malicious calls through a real-time algorithm. The method comprises the following steps that: a calling number initiates a call to a called number already applying for malicious call protection; the calling number and the called number are transmitted to a real-time malicious call analyzing and filtering platform; the real-time malicious call analyzing and filtering platform matches the calling number and the called number with a number library, and judges whether to intercept the calling number or not by using the real-time algorithm; and if the calling number is not intercepted, the calling number is put through. The invention also discloses a malicious call filtering system. The malicious call filtering system comprises a malicious call intercepting assembly module, a support platform module, an algorithm model module and an external connection interface module. In the method, the malicious call protection is applied through the called number, the calling number and the called number are transmitted to the real-time malicious call analyzing and filtering platform, the calling number and the called number are matched with the number library for interception, and whether to intercept the non-intercepted calling number or not is judged by the real-time algorithm, so that filtering of the malicious calls is realized, and the trouble of a called user is avoided.

Owner:ZHEJIANG PONSHINE INFORMATION TECH CO LTD

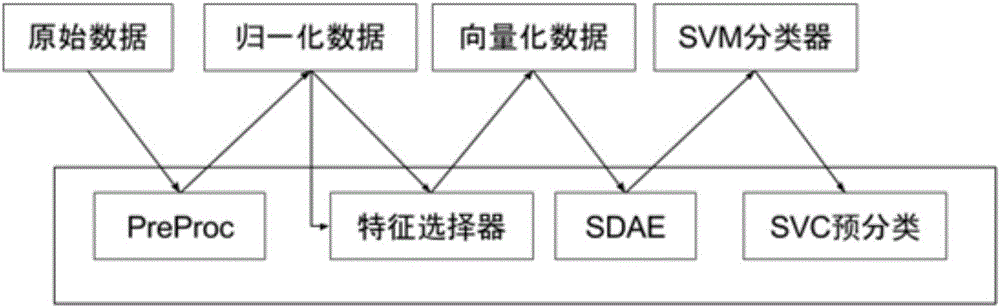

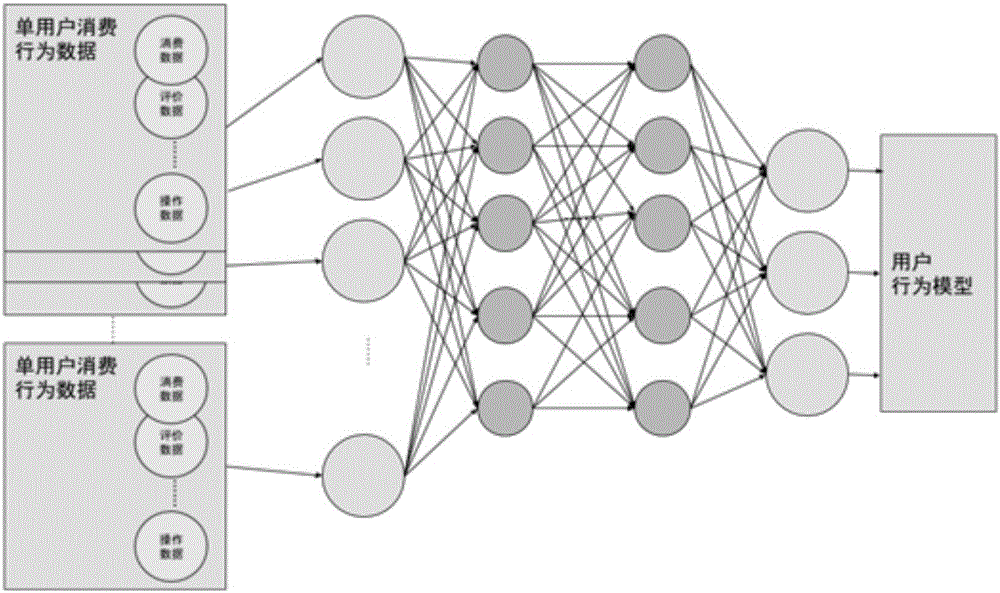

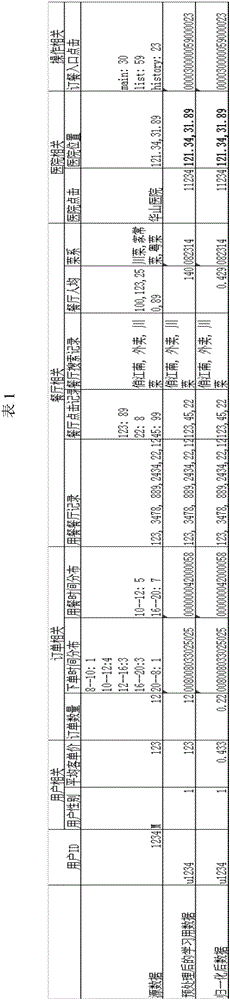

Home page recommendation algorithm based on user eating behavior modeling

InactiveCN106157114AImprove referral conversion rateReduce maintenance costsAdvertisementsBuying/selling/leasing transactionsReal time algorithmHome page

The invention discloses a home page recommendation algorithm based on user eating behavior modeling. The method comprises: step one, all application operation behavior data of a user are obtained by means of application terminal point burying; step two, a clustering analysis is carried out on all user data by using an SVM to form a pre classification unit; step three, it is assumed that user behaviors in each classification in the pre classification unit are similar, modeling is carried out on users of each classification, all user data in the classification are learned by using a neural network for a user behavior model in each classification, and repeated iteration is carried out to obtain an optimal solution; and step four, latest behavior data of the users are substituted into the obtained models and recommendation information of the users is obtained in real time. According to the invention, difficulties of relative solidification and difficulty improvement of recommendation conversion rate in the prior art can be solved. On the basis of SVM pre classification, a classification user model is determined and dynamic recommendation is carried out based on the real-time algorithm model; and the maintenance cost is lowered and the home page recommendation conversion rate is improved.

Owner:商宴通(上海)网络科技有限公司

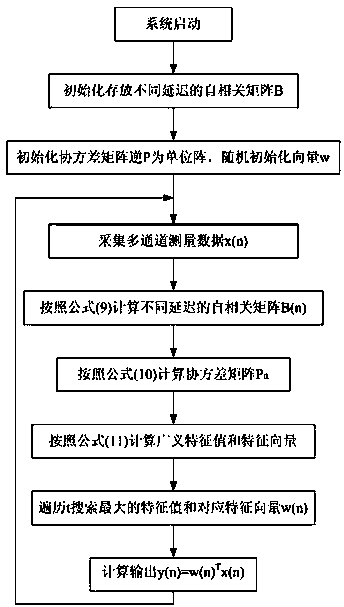

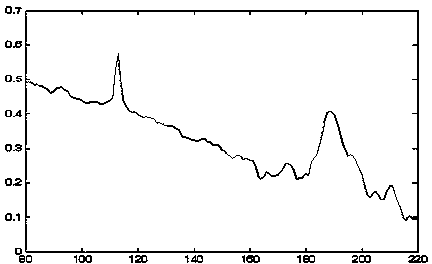

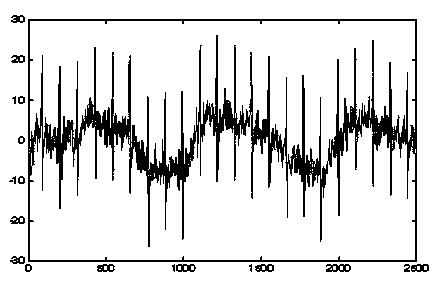

Fetal electrocardiosignal self-adaptive blind extraction method based on generalized eigenvalue maximization

InactiveCN103637796AReduce computationSimple calculationDiagnostic recording/measuringSensorsFeature vectorReal time algorithm

The invention provides a fetal electrocardiosignal self-adaptive blind extraction method based on generalized eigenvalue maximization. The method comprises the following steps: collecting and acquiring blended data including a maternal and fetal electrophysiological signal; based on the self-adaptive real-time algorithm, calculating the covariance matrix characteristic value and characteristic vector of different delayed autocorrelation matrixes within the set period range; selecting the characteristic vector corresponding to the maximum eigenvalue as the blind separation vector so as to extract a fetal electrocardiosignal. The fetal electrocardiosignal self-adaptive blind extraction method utilizes the second-order statistics property of the signal to minimize the noise-to-signal ratio. The second-order statistic method is simple in calculation and small in operation, can still realize effective calculation when the rank of the autocorrelation matrix of the observation vector is close to zero, and can expand to real-time on-line algorithm more conveniently to facilitate product development.

Owner:SHANGHAI MARITIME UNIVERSITY

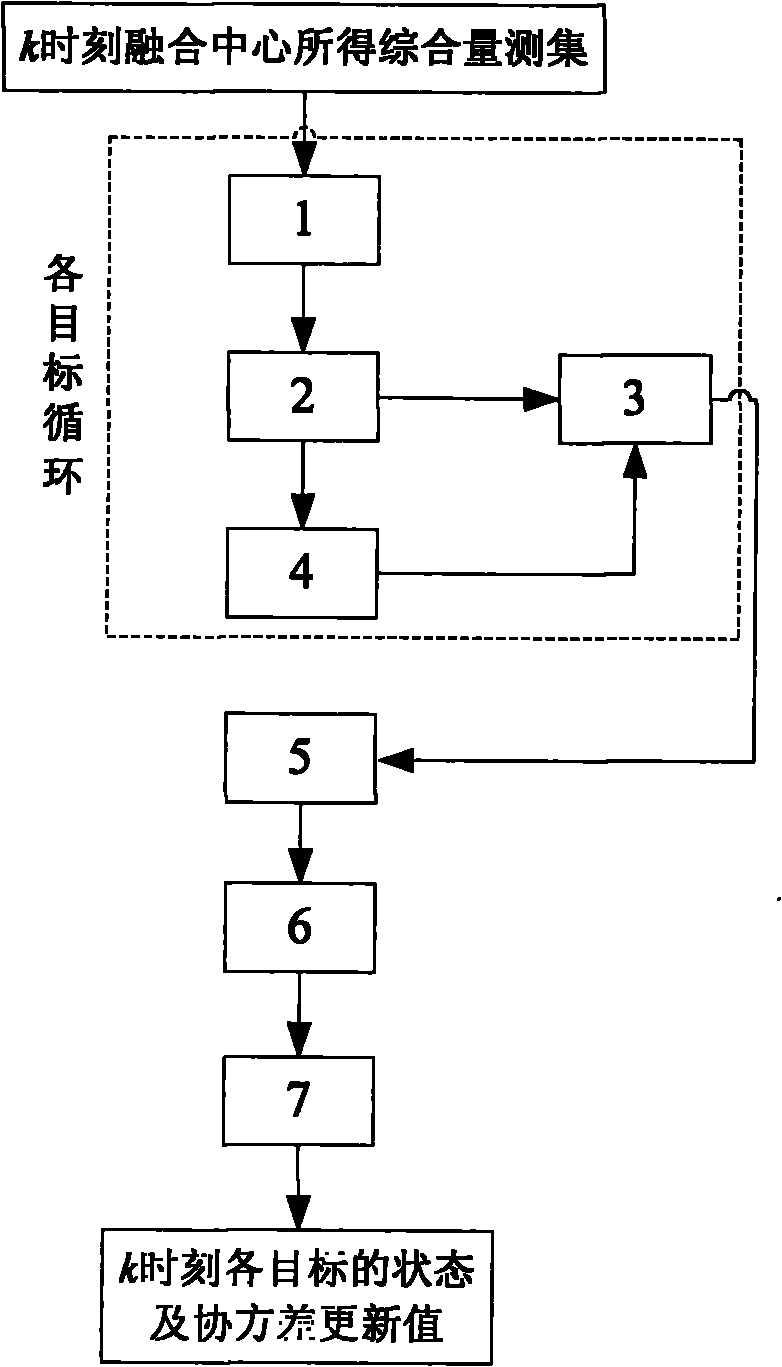

Centralized type multi-source generalized correlation tracker based on data compression

InactiveCN101984362AAvoid problemsImprove tracking accuracyCode conversionRadio wave reradiation/reflectionData compressionReal time algorithm

The invention discloses a centralized type multi-source generalized correlation tracker based on data compression. The technique of the invention belongs to the field of radar data processing. The multiple targets tracking technique in clutter is an important problem difficult to be solved in the field of target tracking. The traditional multi-source multi-target tracking method is difficult to meet the system demand in the actual occasion having certain demands on both real-time algorithm and tracking precision. Through the method of the invention, multiple measurements corresponding to the same target are compressed into an equivalent measurement based on a plot trace merging method in data compression, interconnection hypothesises are generated according to the equivalent measurements and the remained measurements after compressing data, the score of each interconnection hypothesis is calculated according to a score function recursion formula of multi-source generalized correlation algorithm and the blending center state evaluation is realized by choosing the interconnection hypothesis having highest score. The tracker has better tracking precision and real-time property when tracking multiple targets in clutter. The tracker has high application value and can be applied to various centralized type multi-source information bending system.

Owner:NAVAL AERONAUTICAL & ASTRONAUTICAL UNIV PLA

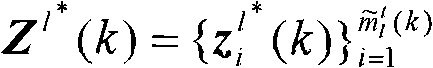

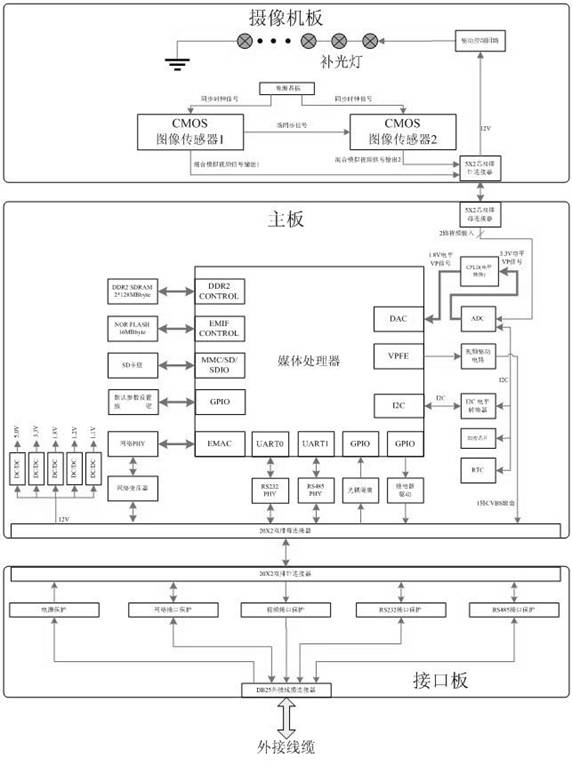

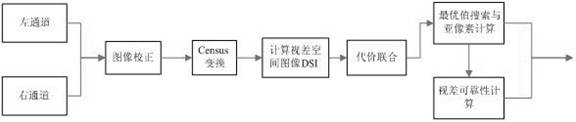

Depth information acquisition method based on binocular framework

InactiveCN102447933AAccurate processingImprove accuracySteroscopic systemsReal time algorithmComputer graphics (images)

The invention relates to a depth information acquisition method based on a binocular framework, which comprises the following steps of: by utilizing the frame synchronous input and output interface of a camera chip, outputting a sampling signal from a left passage into a right passage for the frame synchronism of the left passage and the right passage; adopting Census transformation result as a characteristic to avoid the problem of inconsistent brightness of the left passage and a right passage; by the arrangement of a reasonable algorithm to enable the real-rime to be realized on an embedded platform; giving out depth information reliability by the algorithm so as to provide richer information for the following processing; and adopting the embedded platform to enable a camera structure to be small and further to be conveniently installed.

Owner:ZHEJIANG ICARE VISION TECH

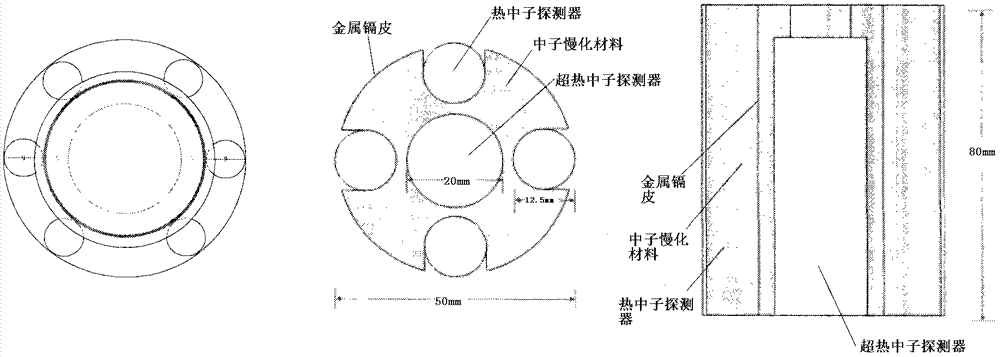

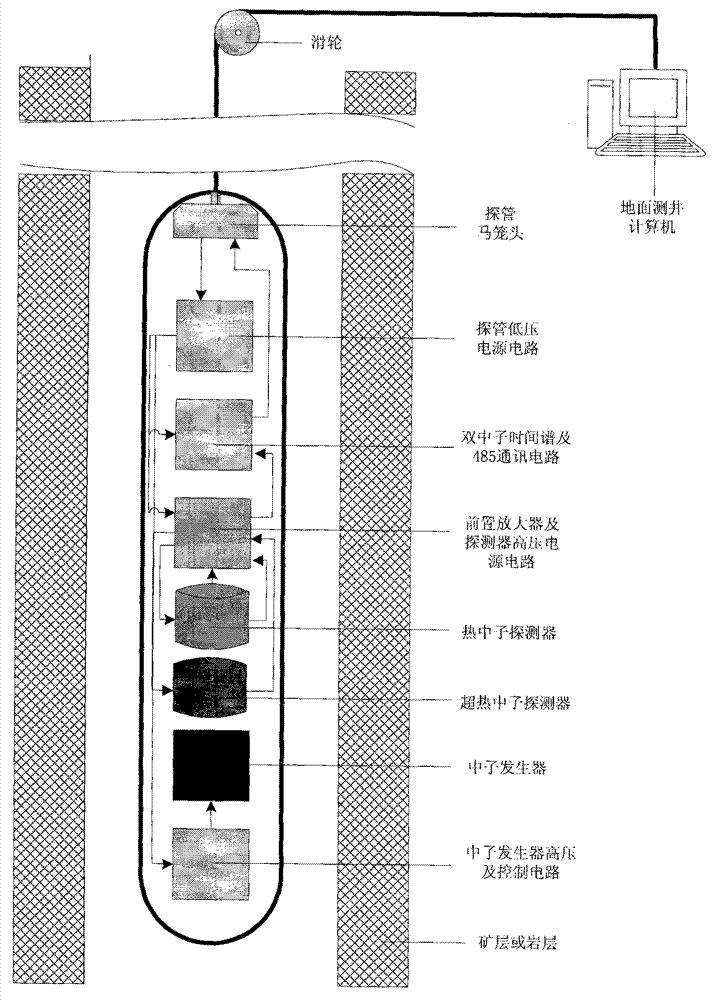

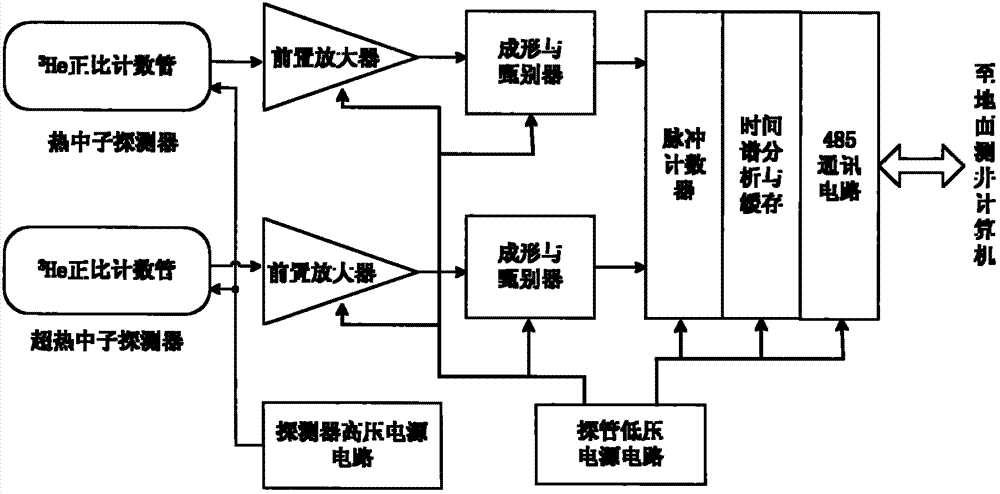

Prompt uranium fission neutron logging technique based on epithermal neutron and thermal neutron ratio

ActiveCN103711479ARealize loggingBorehole/well accessoriesNuclear radiation detectionReal time algorithmSecondary neutron

The invention discloses a prompt uranium fission neutron logging technique based on the epithermal neutron and thermal neutron ratio. The technique is specifically characterized in that in boreholes, fast neutrons, also called virgin neutrons, are transmitted to formation rock by means of pulsing; the virgin neutrons are successively moderated by in-well medium into epithermal neutrons and thermal neutrons; the thermal neutrons induce 235U fission to radiate prompt uranium fission neutrons, also called secondary neutrons; the secondary neutrons are successively moderated into epithermal neutrons and thermal neutrons, inducing 235U fission again; from any moment t after the virgin neutrons are moderated into the thermal neutrons, the total nE(t) of existing epithermal neutrons in the formation rock is in direct proportion to the total nT(t) of existing thermal neutrons and uranium content qu, namely nE(t)<nT(t) qu. By using a bi-neutron detector and a dual-time detector disposed in the invention to measure time spectra of the epithermal and thermal neutrons and defining an attenuation ratio of the epithermal neutrons to the thermal neutrons as 'E / T', from a moment, when the virgin neutrons are moderated into the thermal neutrons, to any moment, a uranium quantitative real-time algorithm based on saturated seams is constructed.

Owner:EAST CHINA UNIV OF TECH

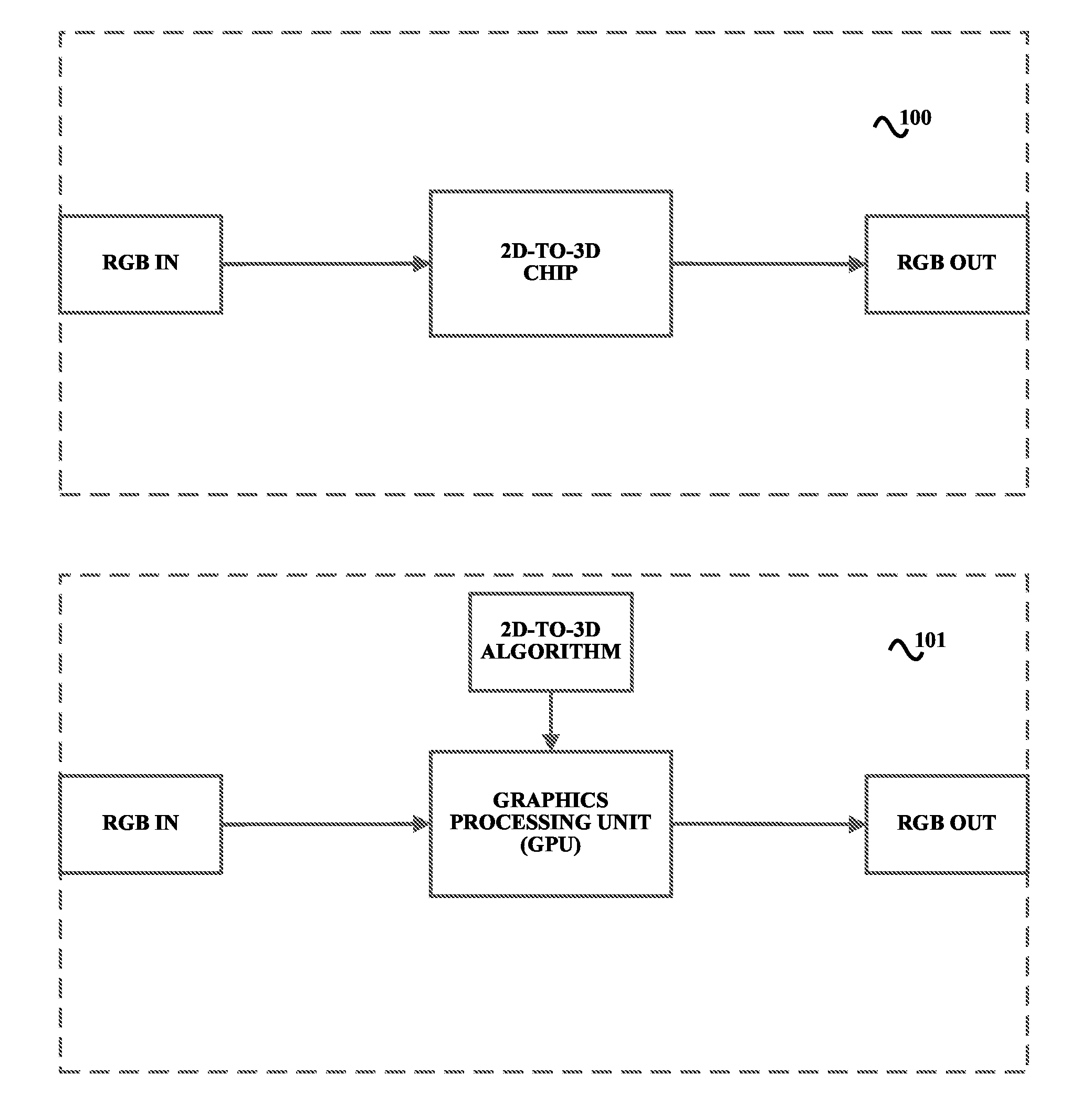

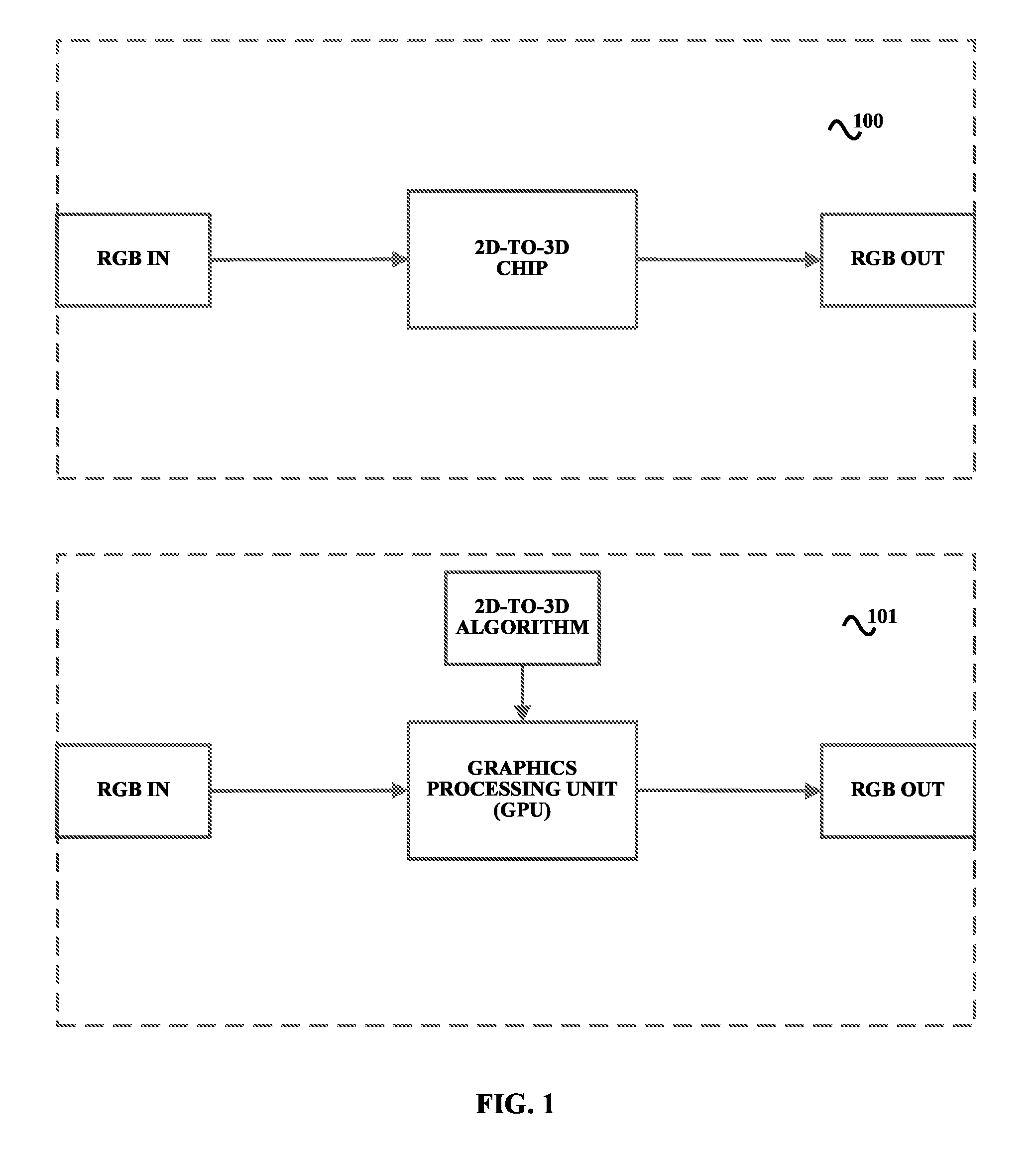

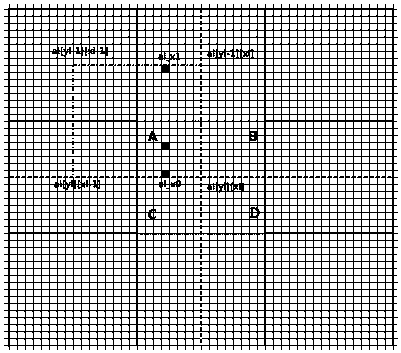

Method for automated realtime conversion of 2D RGB images and video to red-cyan stereoscopic anaglyph 3D

ActiveUS9131209B1High optical clarityHighly parallelizableImage analysisSteroscopic systemsRgb imageDisplay device

In the 2D-to-3D conversion method presented, a series of fast-executing 2D image- or pixel-processing operations are used to transform flat 2D RGB images and video into Red-Cyan Stereoscopic 3D Anaglyph images and video. The output of this process is viewable in stereoscopic 3D on any color screen or display device, using passive red-cyan lensed Anaglyph 3D glasses. The method presented is designed to be deployed as both a hardware “2D-to-3D conversion chip”, and as a short, fast, highly parallelizable realtime algorithm running on programmable graphics hardware like a GPU. The method presented upgrades 2D visual content to stereoscopic 3D, improves the lighting, contrast and color of the content, and also increases its optical sharpness by as much as 200%. Both the left-eye and right-eye image created by the method are “synthetic”—digitally generated. The method produces fairly accurate colors, despite 3D glasses with colored lenses being used.

Owner:DEMIRBAHACEK OVER

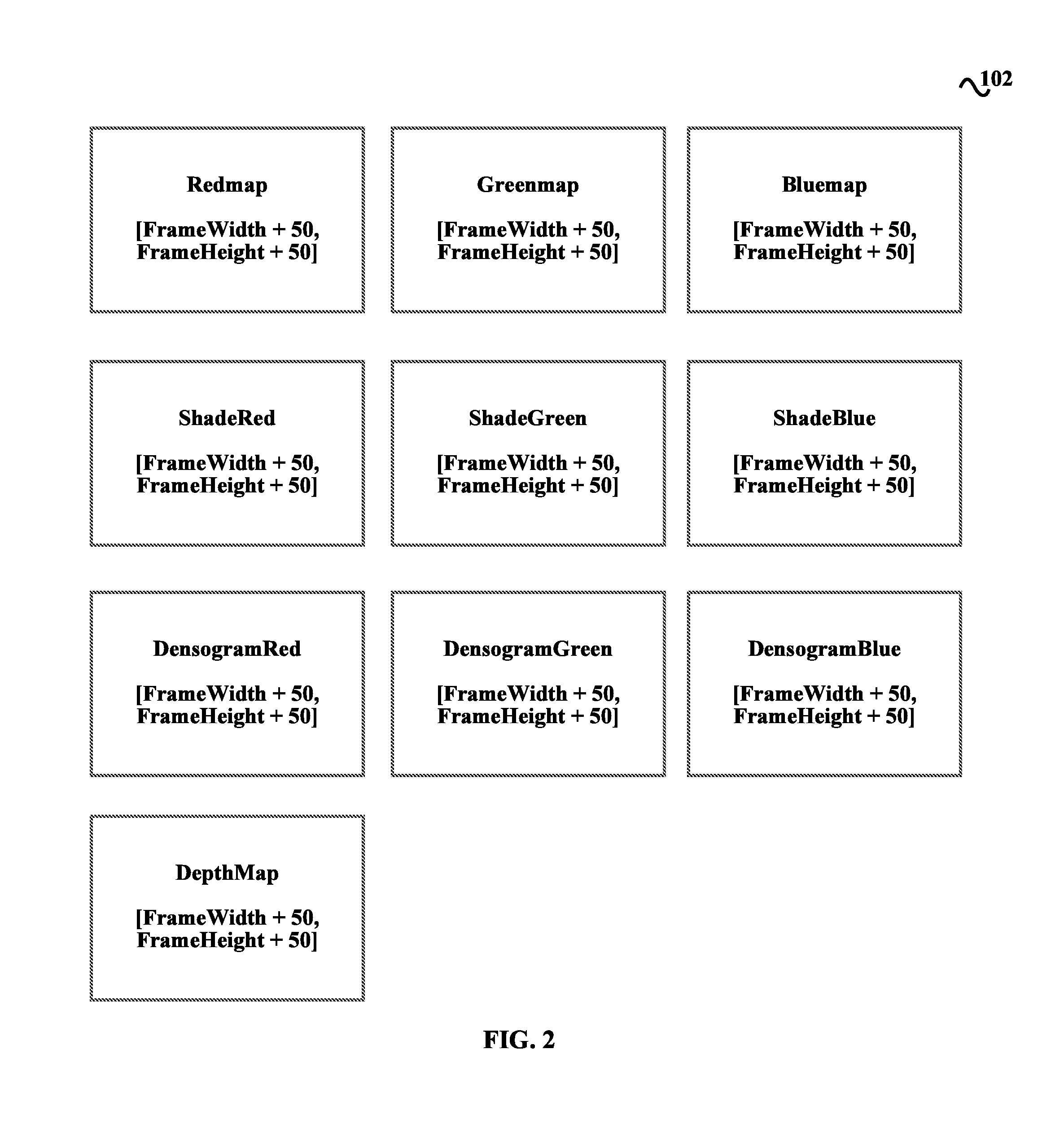

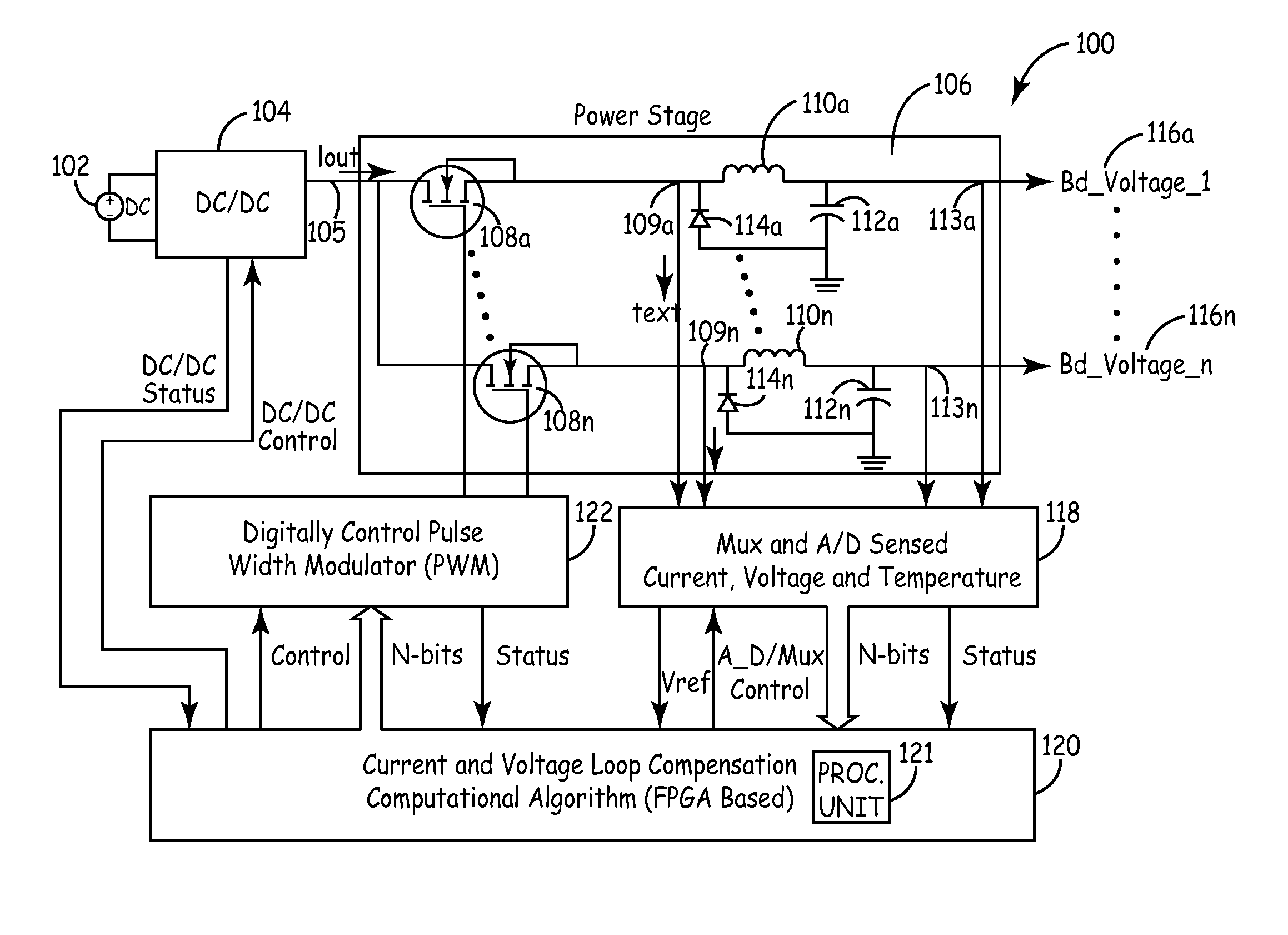

Adaptive digital power control system

InactiveUS7415622B2Reduce voltageHigh currentVolume/mass flow measurementDc-dc conversionCurrent mode controlControl signal

An adaptive digital power control system is disclosed, which implements a digitally controlled, near real-time algorithm to accommodate multiple loop current mode controls for low voltage, high performance computing system power needs. For example, an adaptive digital power control system that is implemented with an FPGA to generate low voltages for high performance computing systems is disclosed, which includes a current and voltage loop compensation algorithm that enables the adaptive digital power control system to dynamically compensate for high current transients and EMI-related noise. The current and voltage loop compensation algorithm uses a combination of linear predictive coding and Kalman filtering techniques to provide dynamic current and voltage compensation, and implement a feed-forward technique using knowledge of the power system's output parameters to adequately adapt to the system's compensation needs. More specifically, an adaptive digital power control system is disclosed, which includes a power stage for generating a plurality of low voltages, a multiplexer and A / D converter stage for receiving and converting the plurality of low voltages and a plurality of associated currents to a plurality of digital voltage and current signals, a current and voltage compensation algorithm stage for receiving the plurality of digital voltage and current signals and generating a plurality of digital voltage and current compensation control signals using linear predictive coding, Kalman filtering and feed-forward estimation techniques, and a digitally controlled pulse width modulator stage for receiving the plurality of digital voltage and current compensation control signals and controlling the duty cycles of a plurality of transistor switching devices in the power stage. Thus, the adaptive digital power control system can dynamically compensate for high current transients and EMI-related noise generated in low voltage power systems for high performance computing systems.

Owner:HONEYWELL INT INC

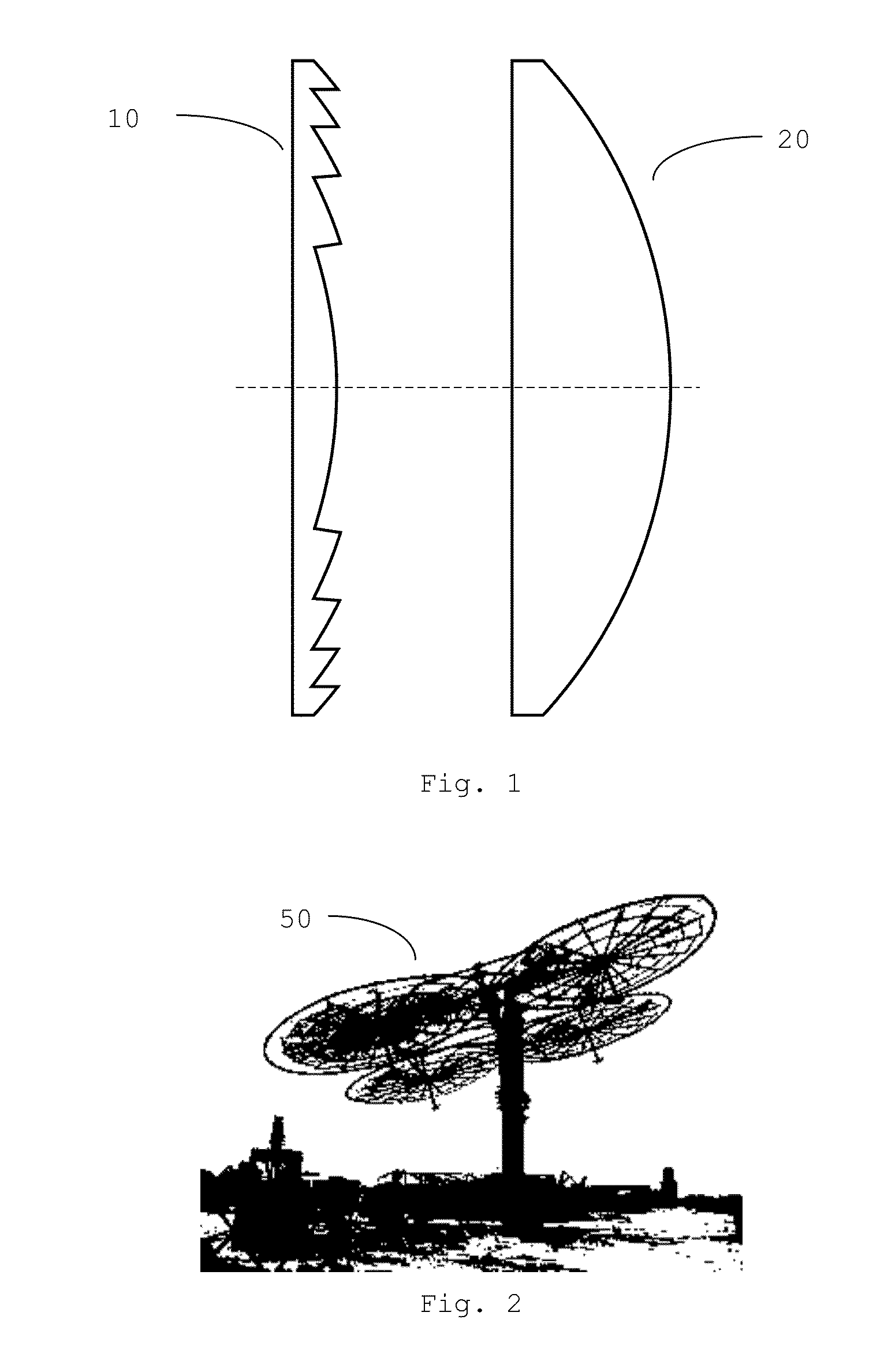

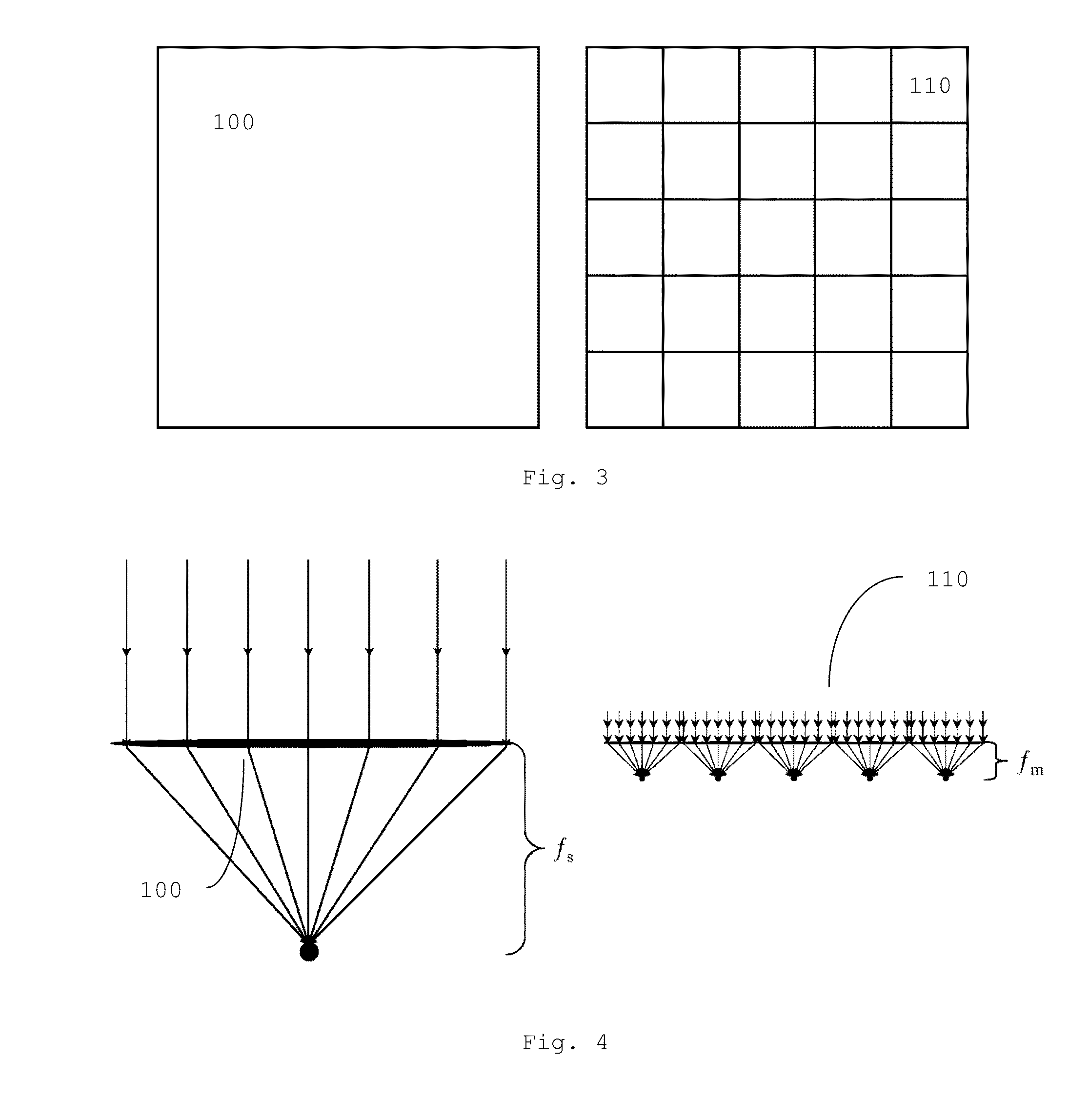

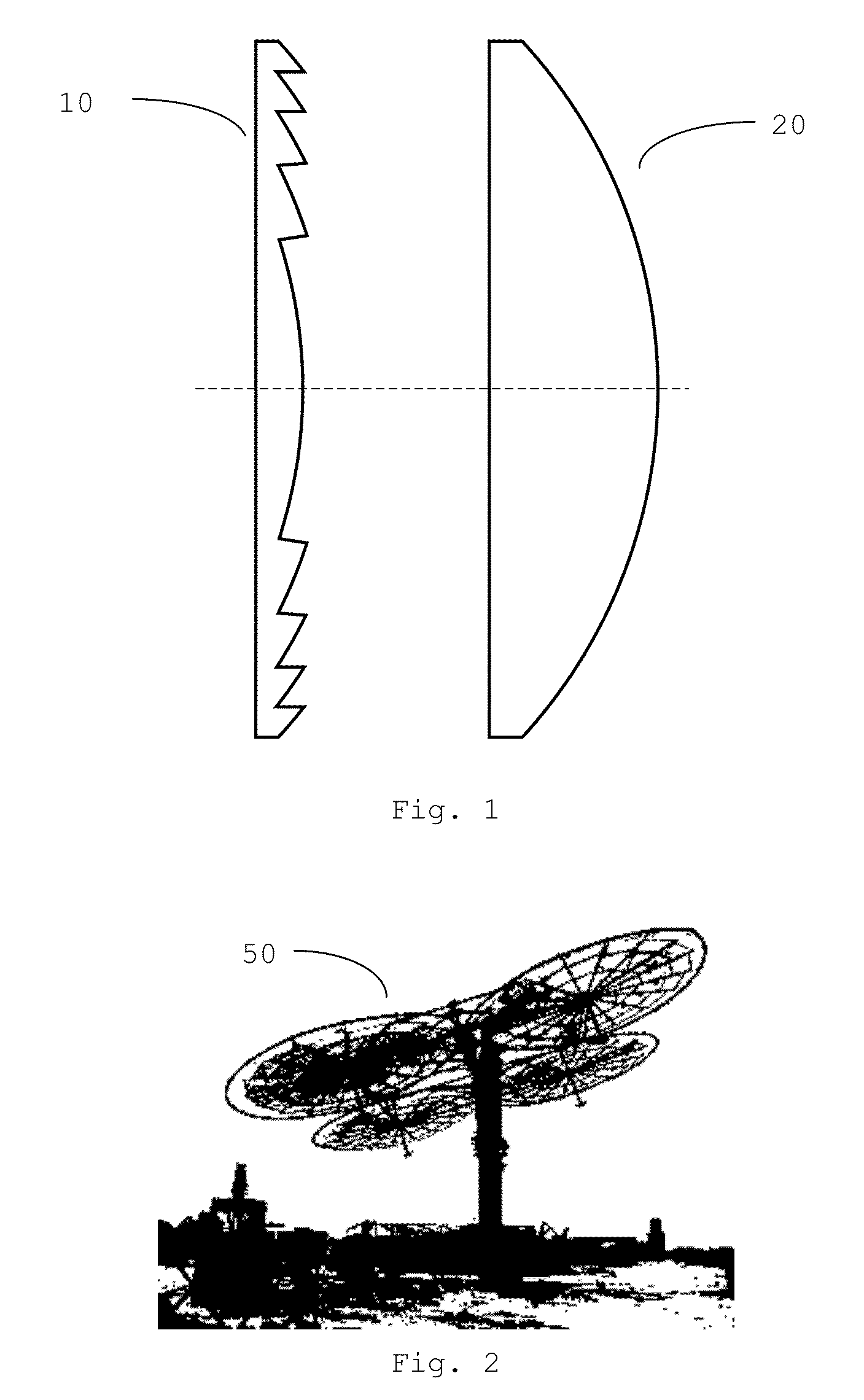

Method and apparatus for electricity production by means of solar thermal transformation

ActiveUS20130255256A1Short focal lengthMounting is very lowSolar heating energyFrom solar energyAbove groundEnergy absorption

We present an improved system for solar energy collection and electricity generation, comprising a solar collector apparatus, said apparatus comprising an array of square Fresnel lenses arranged in rows with modular energy absorption devices located below, wherein the array is mounted on arms at a low height above ground, the rows of said array are rotatable horizontally about their lengthwise axis, and the array is mounted on a rotatable baseThe system further comprises transportable insulated storage tanks containing a storage medium, Stirling engines and generators. The solar collection apparatus heats the storage medium, the storage medium supplies the Stirling engines with heat, and each engine is coupled to a generator.In a preferred embodiment, the system additionally comprises embedded controllers using real-time algorithms providing smart on-the-fly management of the system.

Owner:LOGOTHETIS GEORGIOS

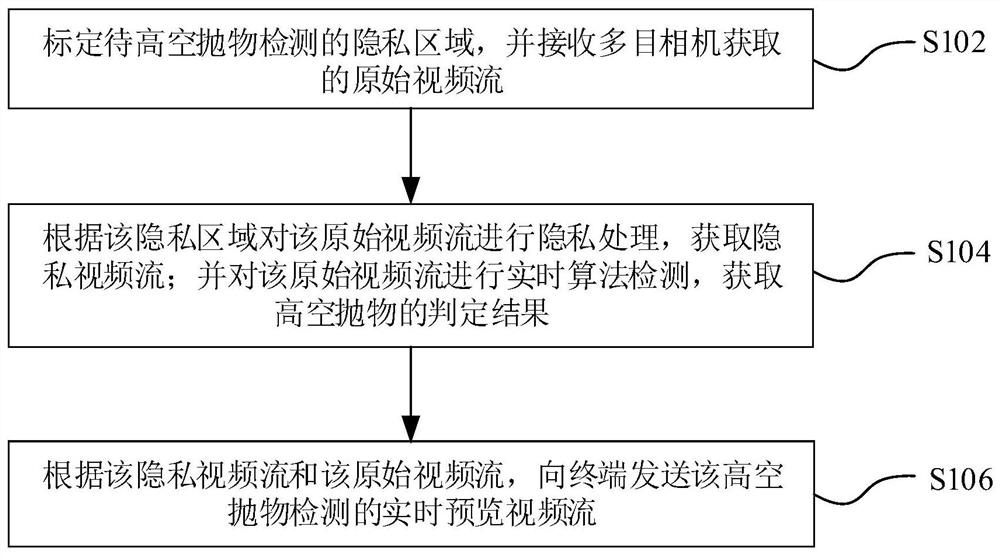

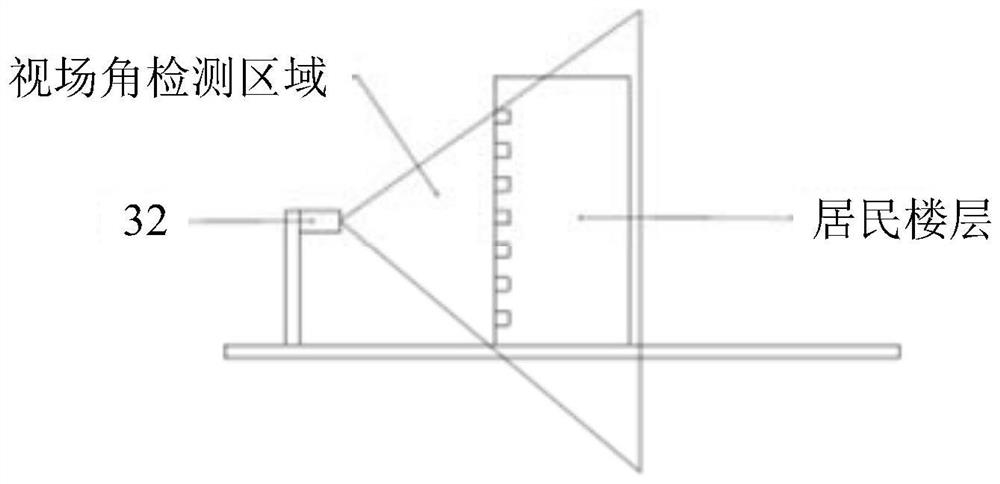

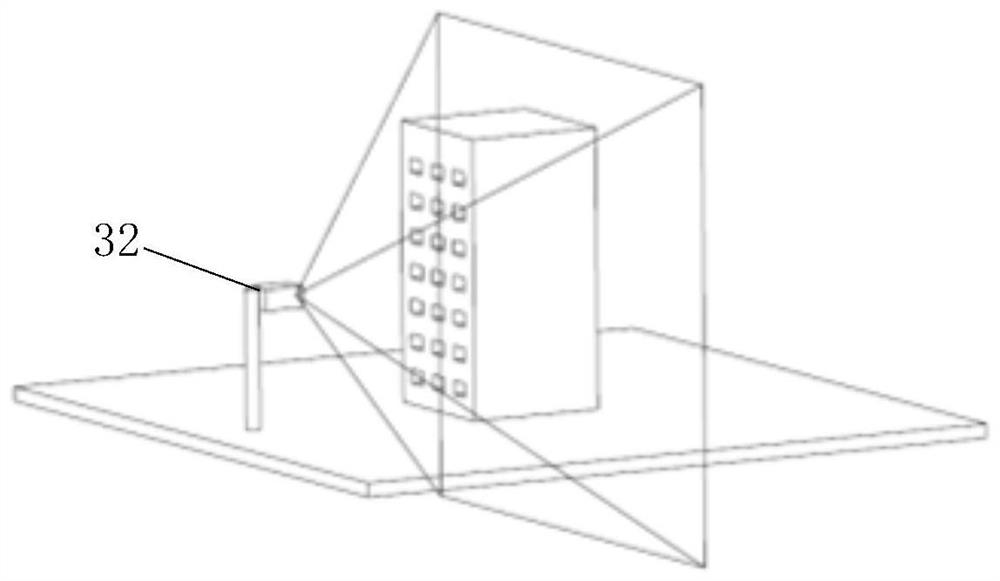

High-rise littering detection method and system, computer equipment and storage medium

ActiveCN111654664AFix security issuesSolve the costCharacter and pattern recognitionClosed circuit television systemsReal time algorithmView camera

The invention discloses a high-rise littering detection method and system, computer equipment and a storage medium, and the method comprises the steps: calibrating a privacy region to be subjected tohigh-rise littering detection, and receiving an original video stream obtained by a multi-view camera; performing privacy processing on the original video stream according to the privacy region to obtain a privacy video stream; performing real-time algorithm detection on the original video stream to obtain a judgment result of the high-rise littering; and according to the private video stream andthe original video stream, sending the real-time preview video stream of the high-rise littering detection to a terminal. Thus, the method solves the problems of low privacy security and high cost inthe high-rise littering detection method.

Owner:ZHEJIANG DAHUA TECH CO LTD

A Multi-channel Conversion Method Based on Spherical Harmonic Expansion

InactiveCN103888889BPerfect theoretical basisReduce computational complexityStereophonic systemsReal time algorithmVocal tract

The invention provides a multi-channel conversion method based on spherical harmonic expansion. The multi-channel conversion method is mainly used for converting an L1-path multi-channel loudspeaker system into an L2-path multi-channel loudspeaker system. Based on the linear superposition theory of a sound field, spherical harmonics with corresponding orders are adopted according to different numbers of channels for calculating the sound field of the loudspeaker system which is not converted and the sound field of the loudspeaker system which is obtained after conversation, and gain coefficients of each loudspeaker of the loudspeaker system obtained after conversation are calculated under the situation that the spherical harmonic expansion sound field of the loudspeaker system which is not converted and the spherical harmonic expansion sound field of the loudspeaker system which is obtained after conversation are the same under the certain order. According to the multi-channel conversion method based on spherical harmonic expansion, the real-time algorithm complexity is low, the sound field of an original reproducing system in a listening area can be recovered on the system obtained after conversation, the method can be used for streamline compression and hybrid technology of a multi-channel three-dimensional audio system, effective compatibility of various loudspeaker reproduction systems can be achieved, and the transmission bandwidth is reduced.

Owner:BEIJING UNIV OF TECH

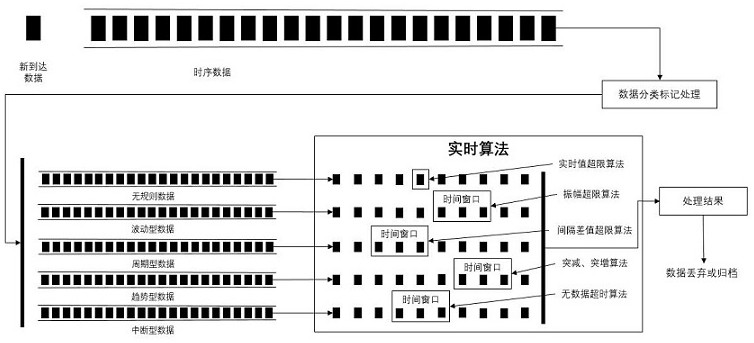

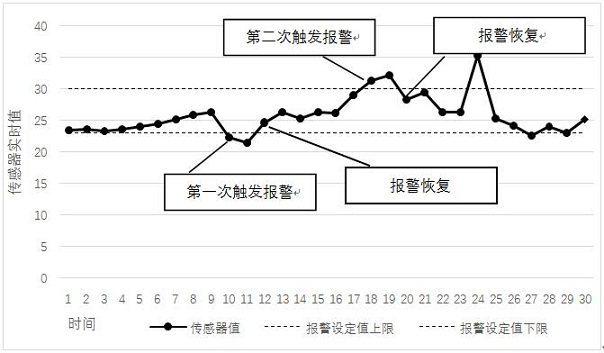

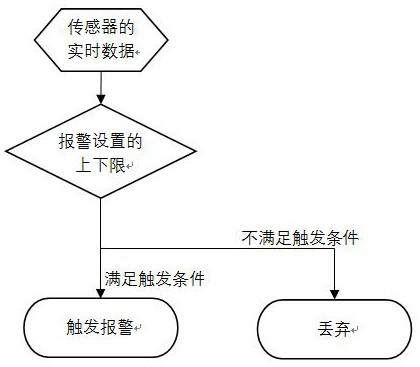

Internet-of-things data real-time analysis method and system and computer readable storage medium

ActiveCN113568960AImprove accuracyEasy to useRelational databasesSpecial data processing applicationsReal time analysisThe Internet

The invention discloses an Internet-of-things data real-time analysis method and system and a computer readable storage medium, and the method comprises the following steps: S1, collecting the remote measurement data of the Internet of Things in real time, and carrying out the real-time sampling of the remote measurement data according to a time window; S2, dividing the sampling data into a plurality of classified data according to the data type, and marking the plurality of classified data to obtain marked data; S3, establishing a matching relationship between each piece of marked data and a real-time algorithm through a matching method; and S4, analyzing data in the marked data by using a real-time algorithm, and outputting the data if a preset condition is met, otherwise, discarding the data. According to the Internet-of-things data real-time analysis method and system and the computer readable storage medium, the Internet-of-things time series data is analyzed and processed, real-time sampling is performed according to a time window, data mining is performed according to a rule, therefore, the data accuracy is improved, and the problems that the result of Internet-of-things telemetry data mining analysis is not accurate enough and the timeliness is low are solved.

Owner:NANJING TAIJIESAI INTELLIGENT TECH CO LTD

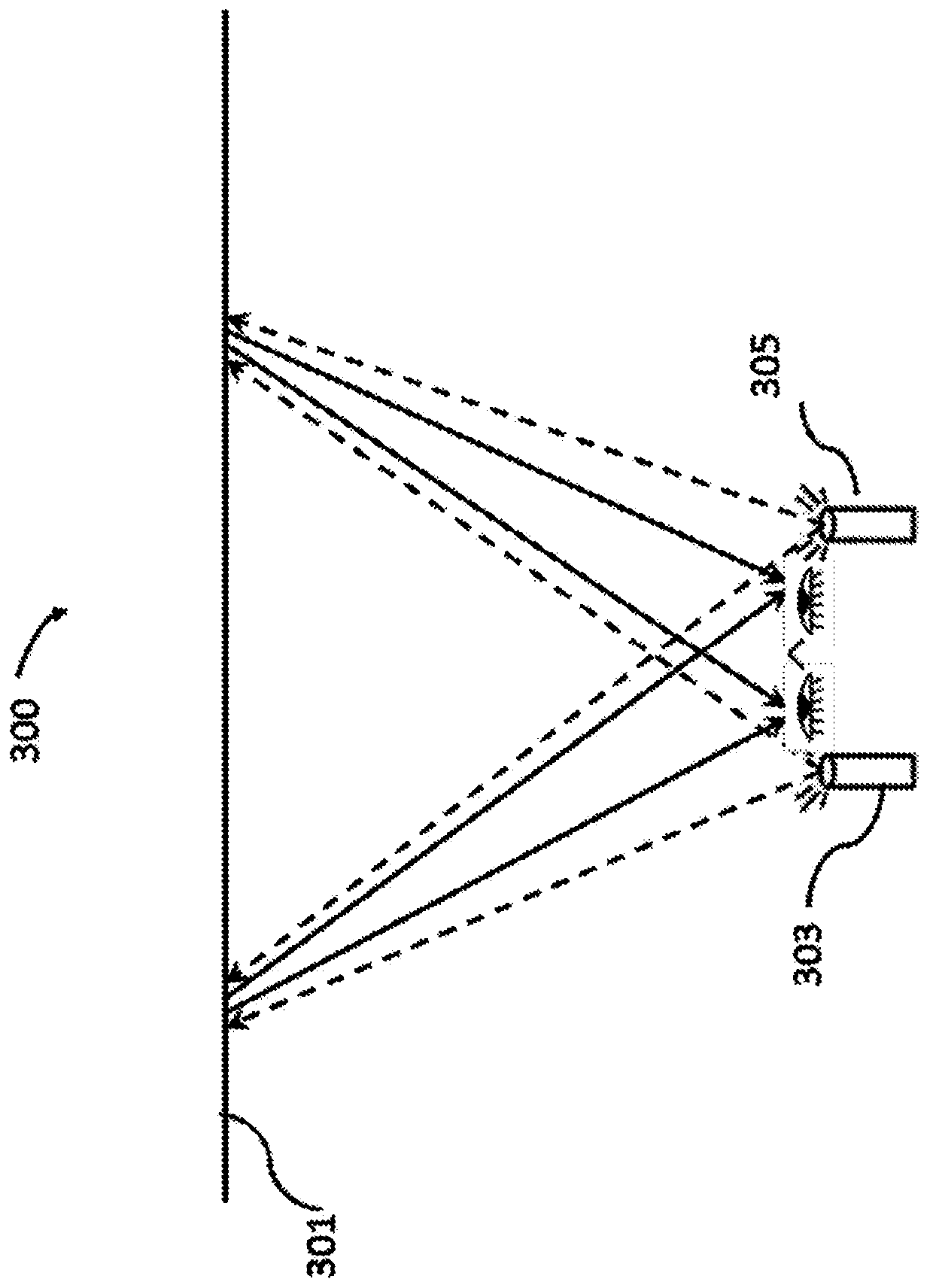

Real time algorithmic calibration and compensation of virtual and augmented reality systems and optimized semi-transparent and transparent retroreflective display systems and methods

ActiveCN109804297AInput/output processes for data processing3D-image renderingReal time algorithmOptical transparency

The present disclosure provides systems and methods to enable significant improvements in display systems utilizing projectors and a retro -reflective (RR) screen through use of transparent or semi-transparent RR material. An aspect of the present disclosure provides methods for optimization of optical properties of the RR material to achieve desired optical transparency parameters. Another aspectof the present disclosure provides methods for specific use cases for flexible, transparent and semi-transparent RR display systems.

Owner:MIRRAVIZ

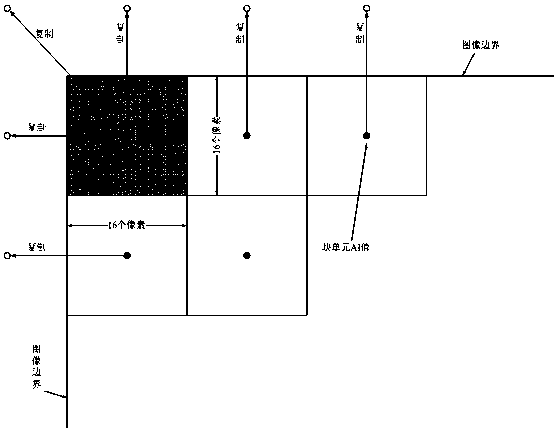

Real-time flat-field correction method of area array camera based on FPGA

ActiveCN106204492BOptimizing Parallel ComputingReal-time correctionImage enhancementImage analysisCorrection algorithmSensor array

This invention combines the parallel computing characteristics of FPGA and takes into account the limited resources in FPGA, and proposes an optimized real-time flat field correction method for area array cameras that can be implemented based on FPGA. It uses a block-based computing method to perform block operations on the sensor array. , combined with the interpolation algorithm on the basis of blocks, to reduce resource consumption and perform operations on each point at the same time. The invention provides the possibility to implement a real-time FFC correction algorithm for high-resolution and high-frame-rate lower-array cameras, and provides higher output image quality for high-resolution and high-frame-rate applications. By using optimization algorithms, PRNU and vignetting effects were successfully corrected in real time while meeting the requirements of high resolution and high frame rate.

Owner:HEFEI I TEK OPTOELECTRONICS CO LTD

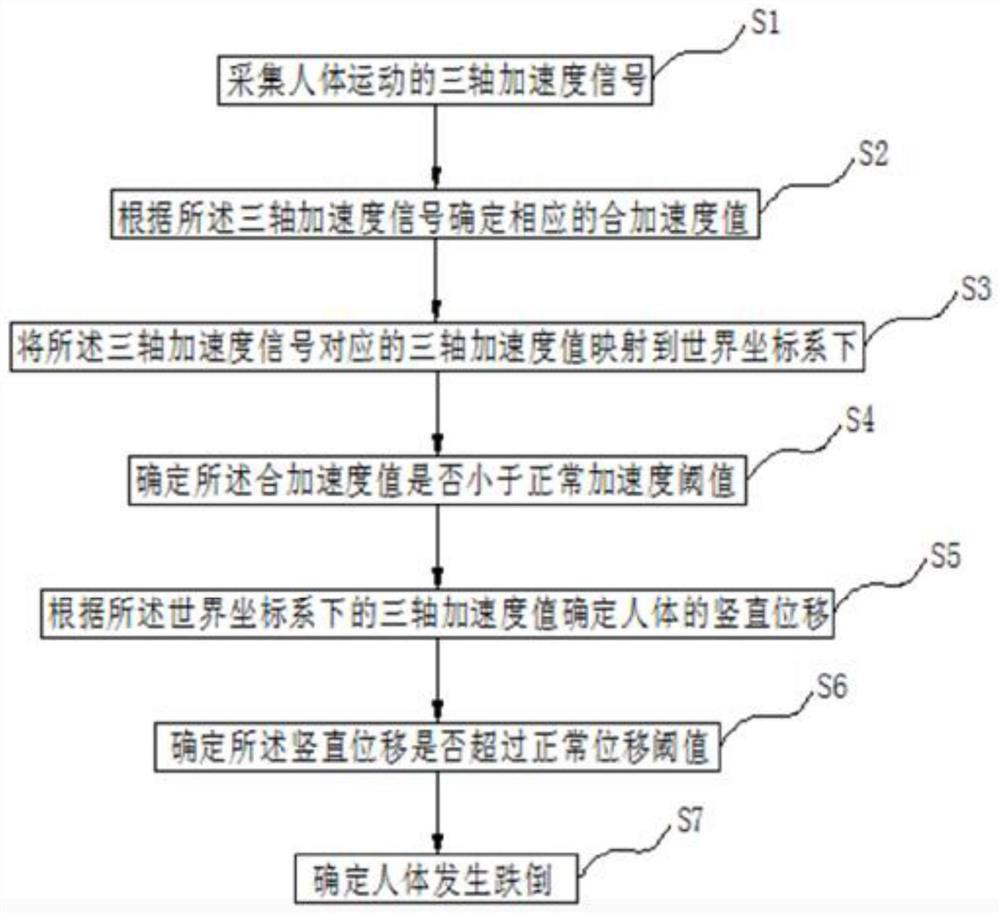

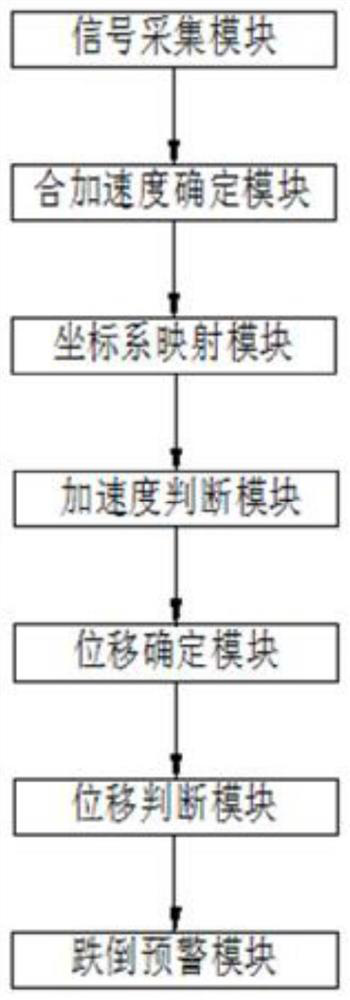

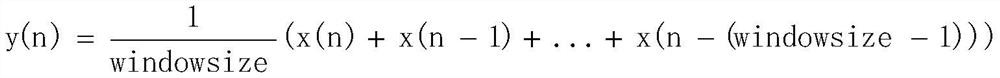

Fall early warning method, system and device and computer storage medium

PendingCN114469074AReduce fall prediction false alarm rateImprove accuracyDiagnostic recording/measuringSensorsReal time algorithmHuman body

The invention discloses a fall early warning method, system and device and a computer storage medium, and the method comprises the steps: carrying out the filtering of a human body acceleration signal collected by an attitude sensor, carrying out the solving of a mapping matrix according to a mapping relation between a body coordinate system and a world coordinate system, and the Euler angles of three axes, and carrying out the early warning of fall. The resultant acceleration is obtained through the three-axis original acceleration signals to judge whether the human body weightlessness and the weightlessness degree, a threshold value is set to judge whether the human body weightlessness is normal or not, and then whether the human body is about to fall or not is judged so as to trigger a fall early warning signal. According to the fall early warning method, a large number of actions similar to fall behaviors in life can be effectively filtered out, so that the fall prediction false alarm rate is reduced, the accuracy is improved, and through real-time algorithm analysis and processing, good prediction can be realized before fall, and a fall early warning signal is sent out to inform an execution mechanism to perform timely fall protection and rescue.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI +2

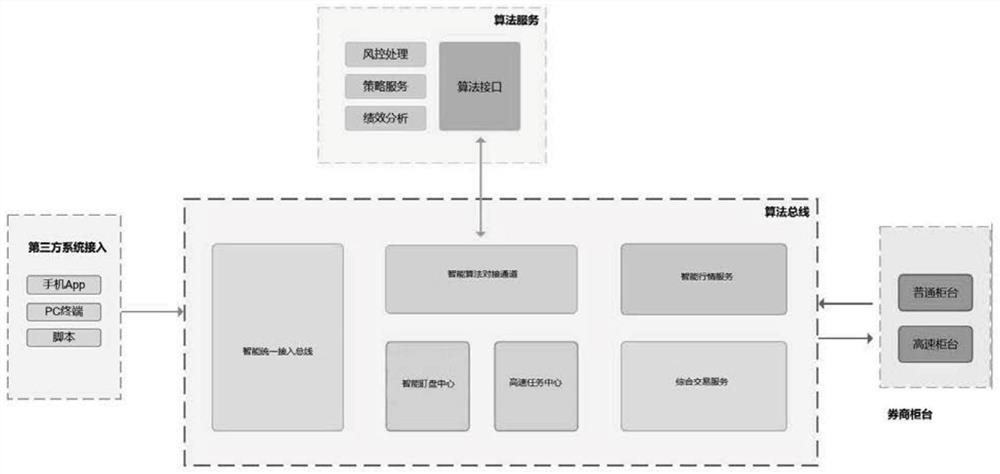

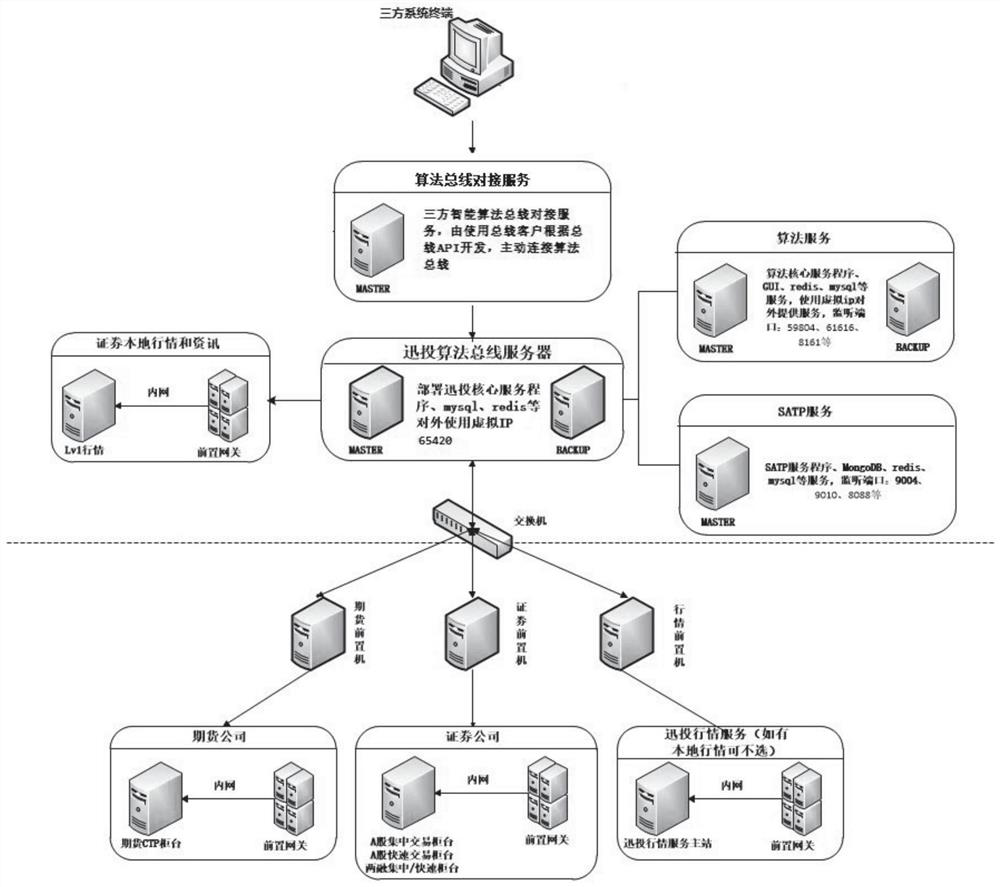

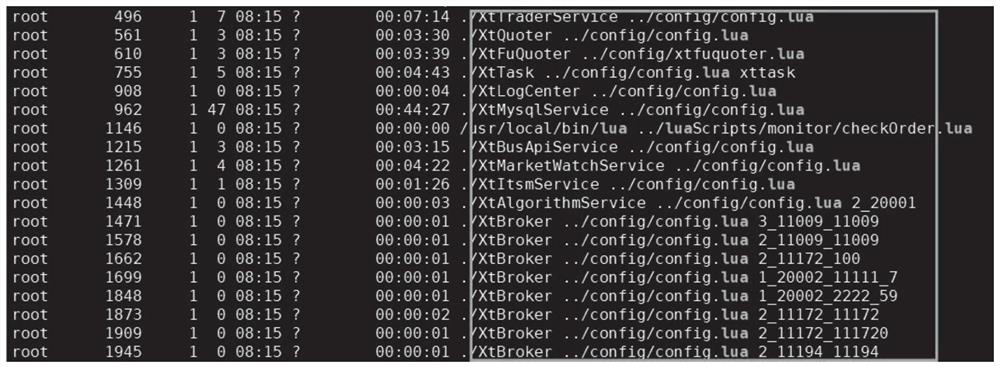

Real-time algorithm transaction bus system in securities algorithm transaction process

The invention discloses a real-time algorithm transaction bus system in a securities algorithm transaction process. The system comprises a securities algorithm transaction data processing interface module and a securities transaction data algorithm bus module, and the securities algorithm transaction data processing interface module is in communication connection with the securities transaction data algorithm bus module. The invention has a normative and stable algorithm investment transaction interface and rich algorithm investment transaction functions, can quickly and stably butt and expandmore three-party algorithms, can comprehensively meet transaction execution requirements of most institution customers, can help institutions and high-end personal investors to remarkably reduce impact cost, reduces occurrence of abnormal transactions, and can help brokers to quickly build their own investment transaction systems; the invention can be connected with Shenzhen and Shanghai real-time quotations or lightweight quotations, can be quickly accessed to broker counter systems, and solves the problems that it is difficult to form a technical barrier capable of adapting to multiple environments and deployment is not flexible enough under the technical barriers of existing domestic investment transaction system suppliers.

Owner:北京睿智融科控股股份有限公司

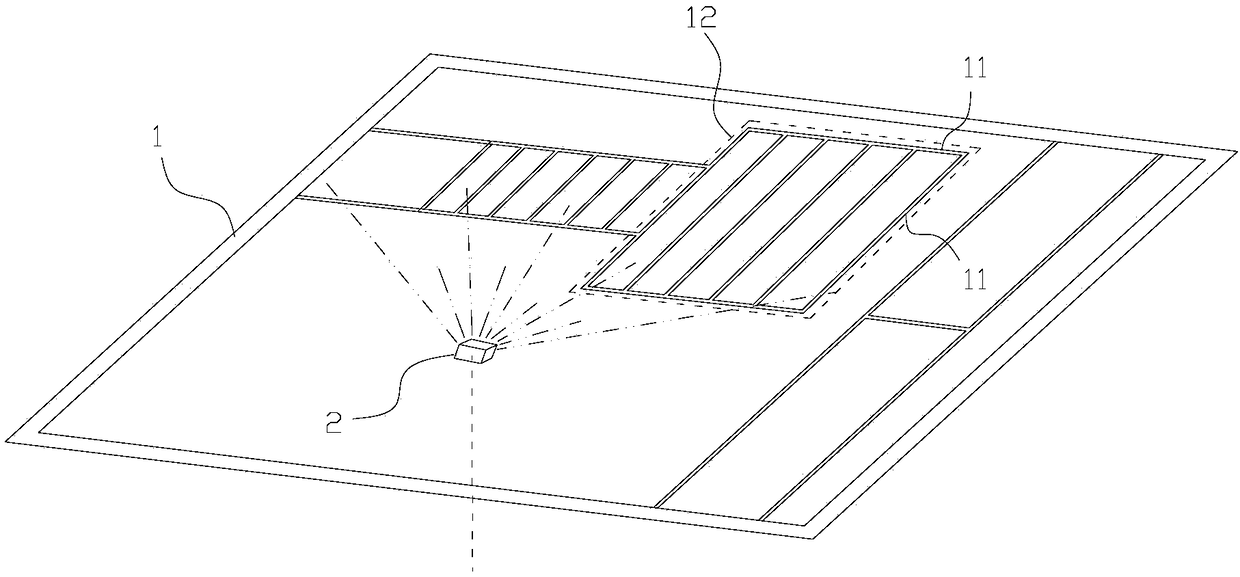

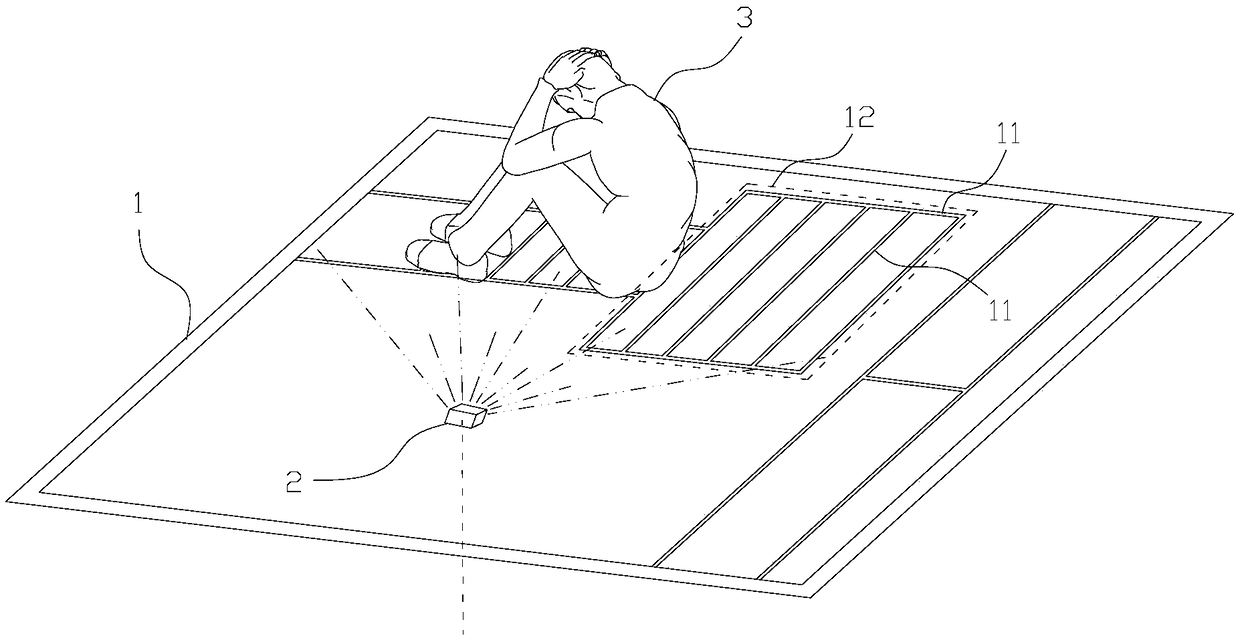

Optical calibration and measurement methods for sit-up tests

InactiveCN109200563AGood testing experienceGuaranteed test efficiencyGymnastic exercisingReal-time testingWidth ratio

The invention relates to an optical calibration and measurement method for sit-up tests, comprising the following steps: S1, a plurality of mark lines with different reflectance from a background areaare arranged in the test area and a plurality of quadrilaterals are formed, and with preset length-width ratio of each quadrilateral in the area where the body is located being different from other quadrilateral; S2, when no one is present, the standard test area image is captured by the camera, and the body standard image area is delimited and processed by the algorithm to obtain the standard algorithm graph; S3, a real-time test area image of a test area with a test person is captured, a real-time image area of a body in the real-time test area is found, and the real-time algorithm graph isprocessed to obtain the real-time algorithm graph; S4 AND operation is performed on that real-time algorithm graph and the standard algorithm graph to obtain the effective algorithm graph, and judging and count the sit-up motion of the tester according to the changes of the mark lines in the effective algorithm graph. The method has good test experience, and the test efficiency and the test precision can be guaranteed.

Owner:SHENZHEN TAISHAN SPORTS TECH CO LTD

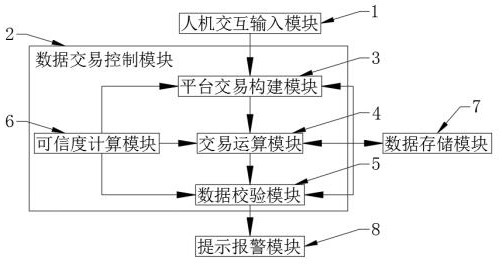

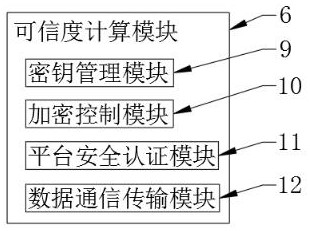

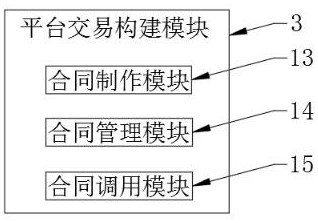

Real-time algorithm transaction system in digital RMB transaction process

PendingCN113673992AReduce lossesSafety of tradementProtocol authorisationReal time algorithmAlgorithm

The invention discloses a real-time algorithm transaction system in a digital RMB transaction process. According to the system, a data transaction control module is bidirectionally and electrically connected with a data storage module; the data transaction control module comprises a platform transaction construction module which is in electrical input connection with a man-machine interaction input module, and is in electrical output connection with a transaction operation module; the transaction operation module is in the electrical output connection with a data verification module; the data verification module is in the electrical output connection with a prompt alarm module; the platform transaction construction module, the transaction operation module and the data verification module are all in the electrical input connection with a credibility calculation module; and the platform transaction construction module, the transaction operation module and the data verification module are all bidirectionally and electrically connected with the data storage module. Therefore, transactions can be carried out more safely and reliably, the real-time performance of the transactions is ensured, a plurality of future transactions are prevented from being signed due to loss of digital signatures, and the loss after the digital signatures are lost is greatly reduced.

Owner:SUZHOU UNIV

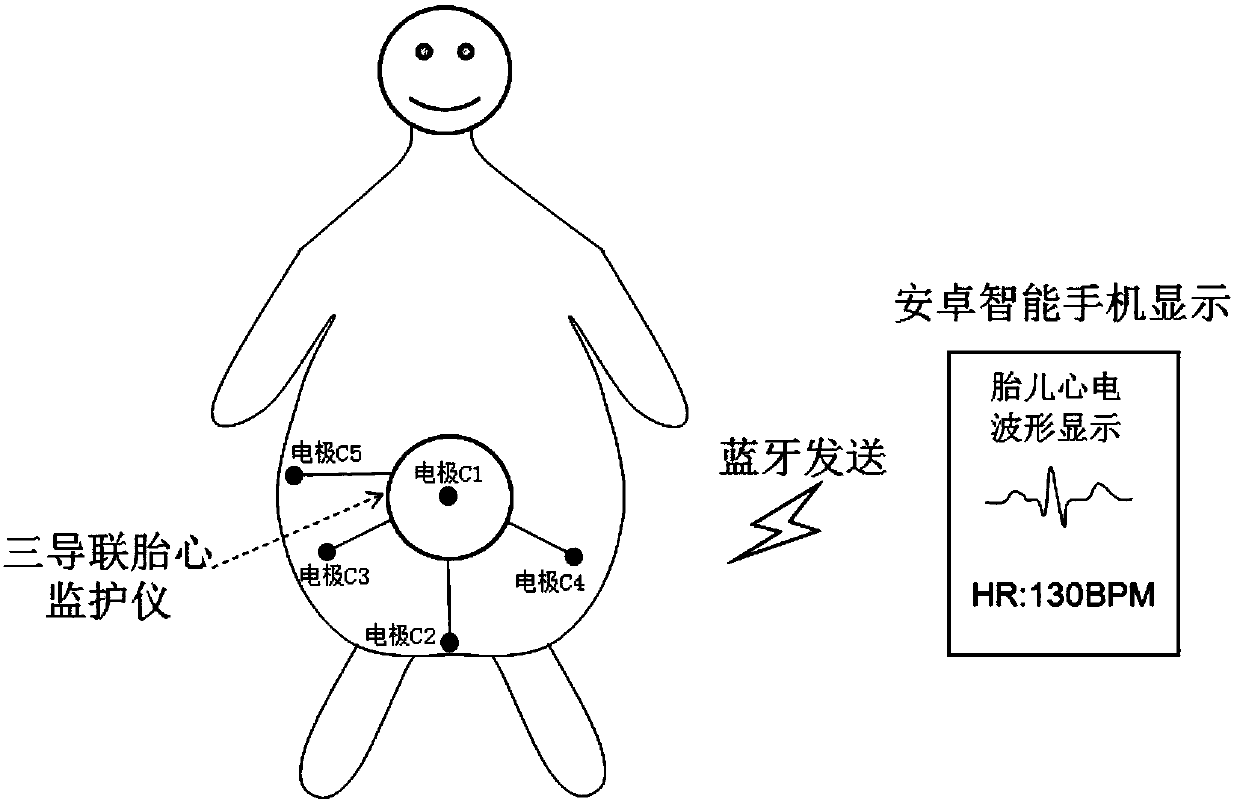

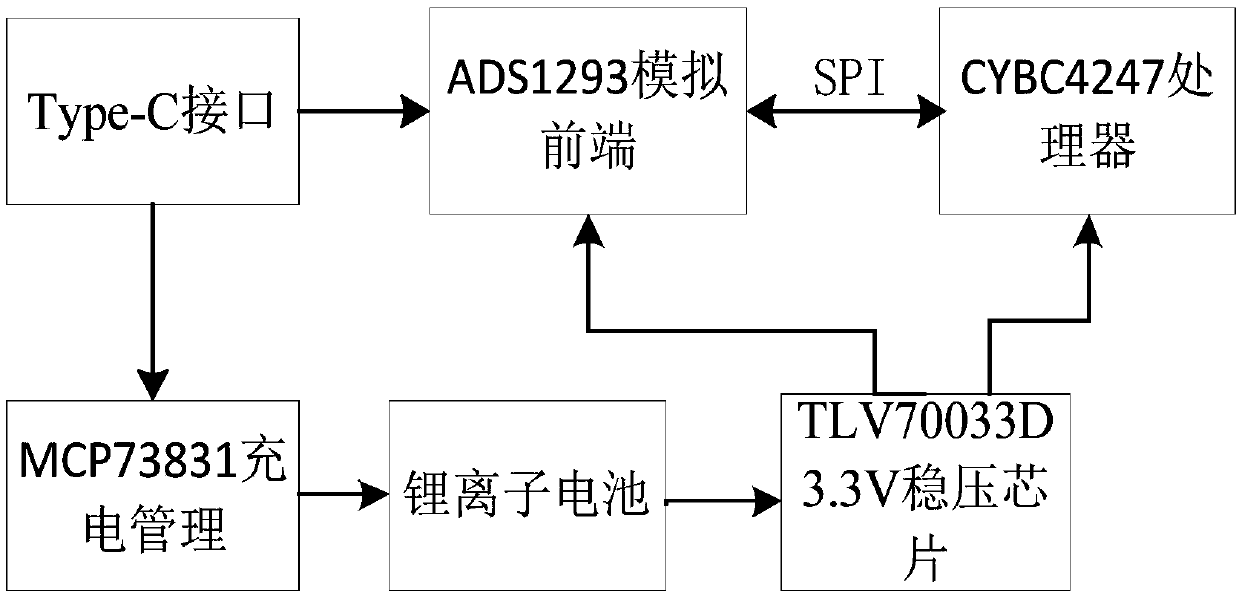

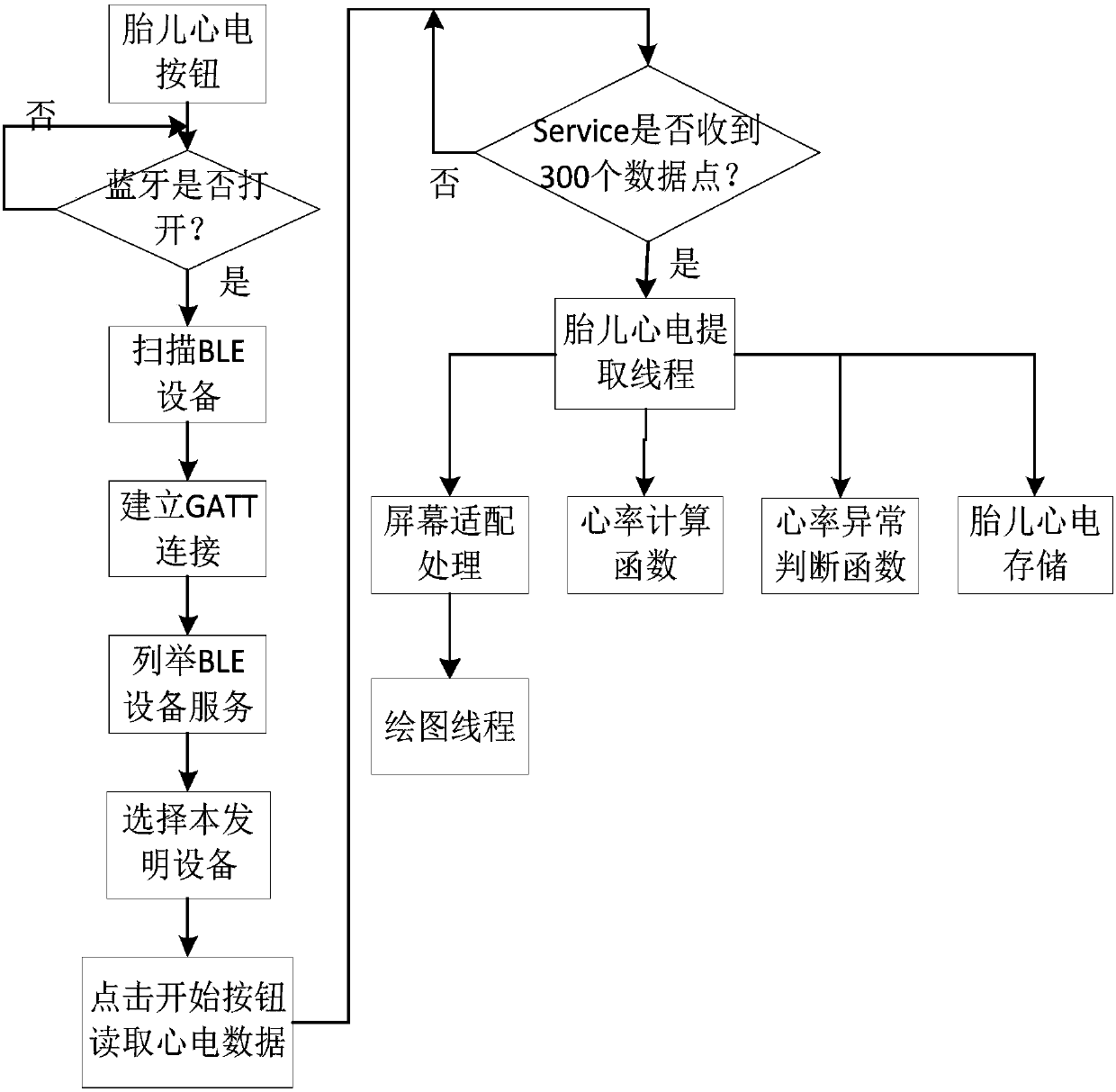

Fetal electrocardiogram monitoring system based on Android smartphone

The invention provides a fetal electrocardiogram monitoring system based on an Android smartphone so as to achieve home monitoring of the fetal electrocardiogram. The system is composed of a pregnantwoman abdomen three-lead electrocardiogram collector, a fetal electrocardiogram real-time algorithm and Android smartphone software. The circuit of the pregnant woman abdomen three-lead electrocardiogram collector is mainly composed of a low-power-consumption Bluetooth processor Cypress CY8C4247 and a three-lead analog front end ADS1293, and pregnant woman abdomen three-lead electrocardiogram signals are collected by the 24-bit ADS1293, transmitted to the processor CY8C4247 through SPI communication to be processed and then wirelessly sent to the Android smartphone through Bluetooth. The functions of the Android smartphone software include BLE service acquisition, communication connection, Service provision, broadcasting, thread establishment and drawing canvas design, heart rate calculation, electrocardiogram abnormity warning and the like. The fetal electrocardiogram detection algorithm is a fast ICA algorithm with optimized parameters.

Owner:BEIJING UNIV OF TECH

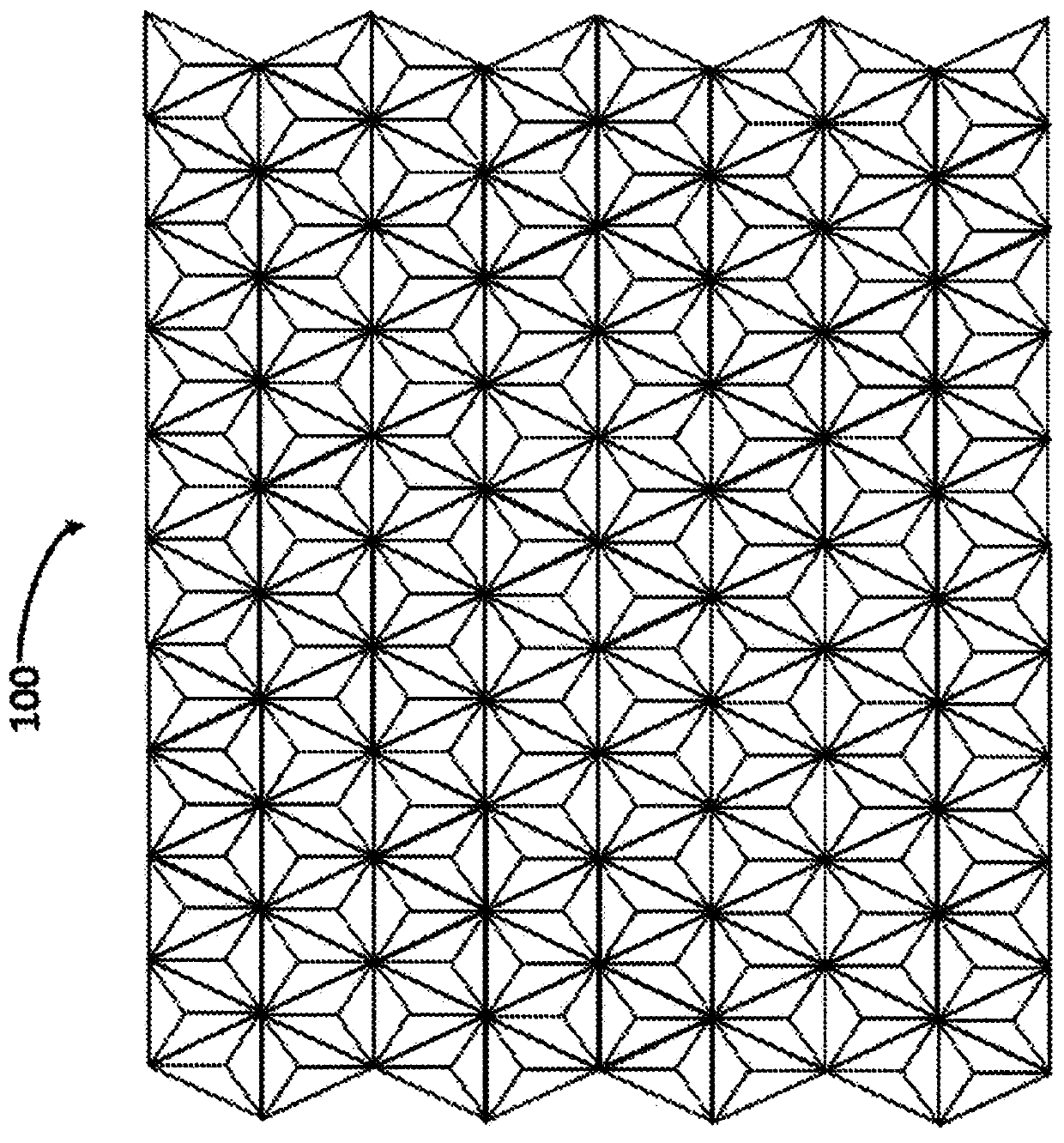

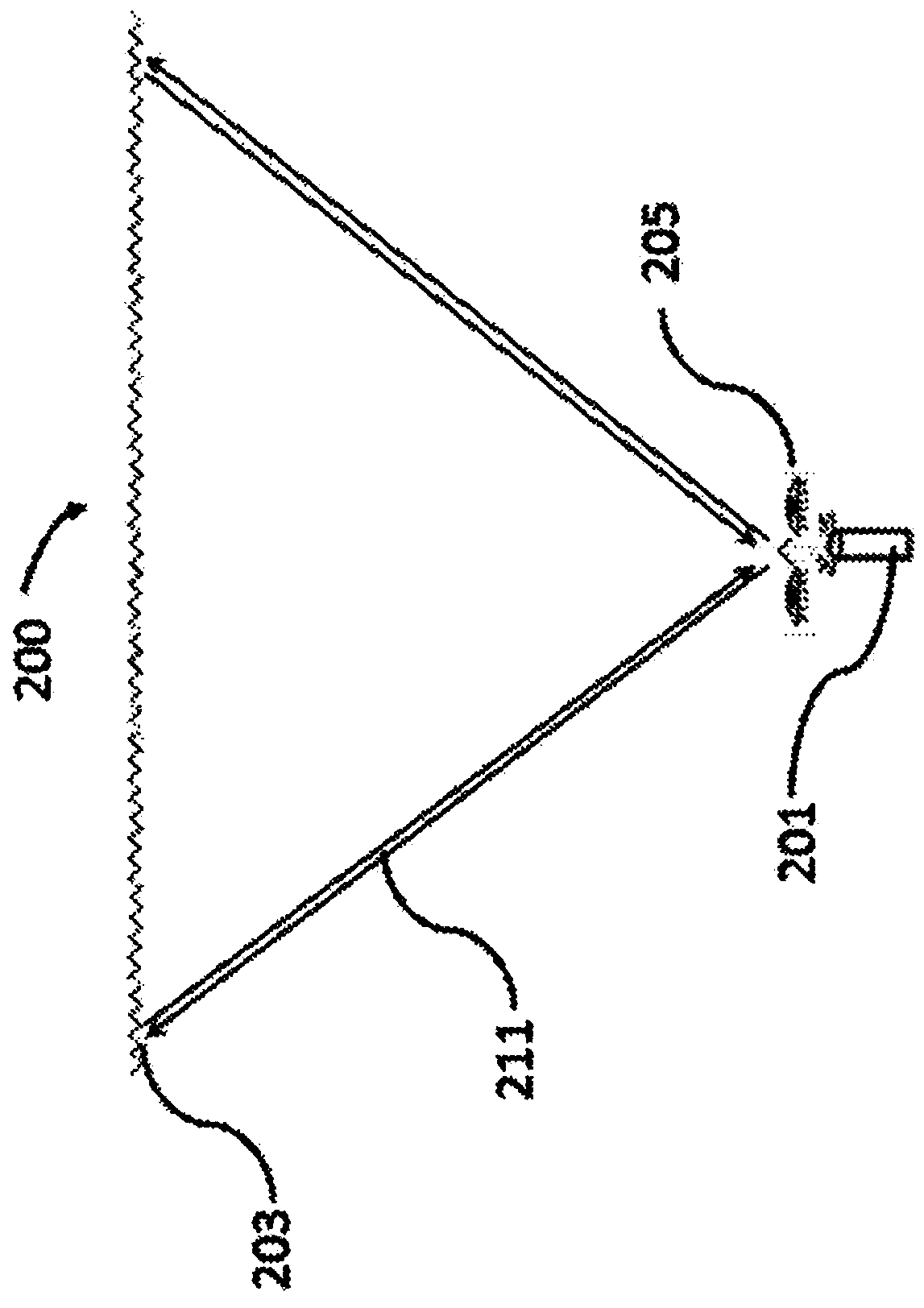

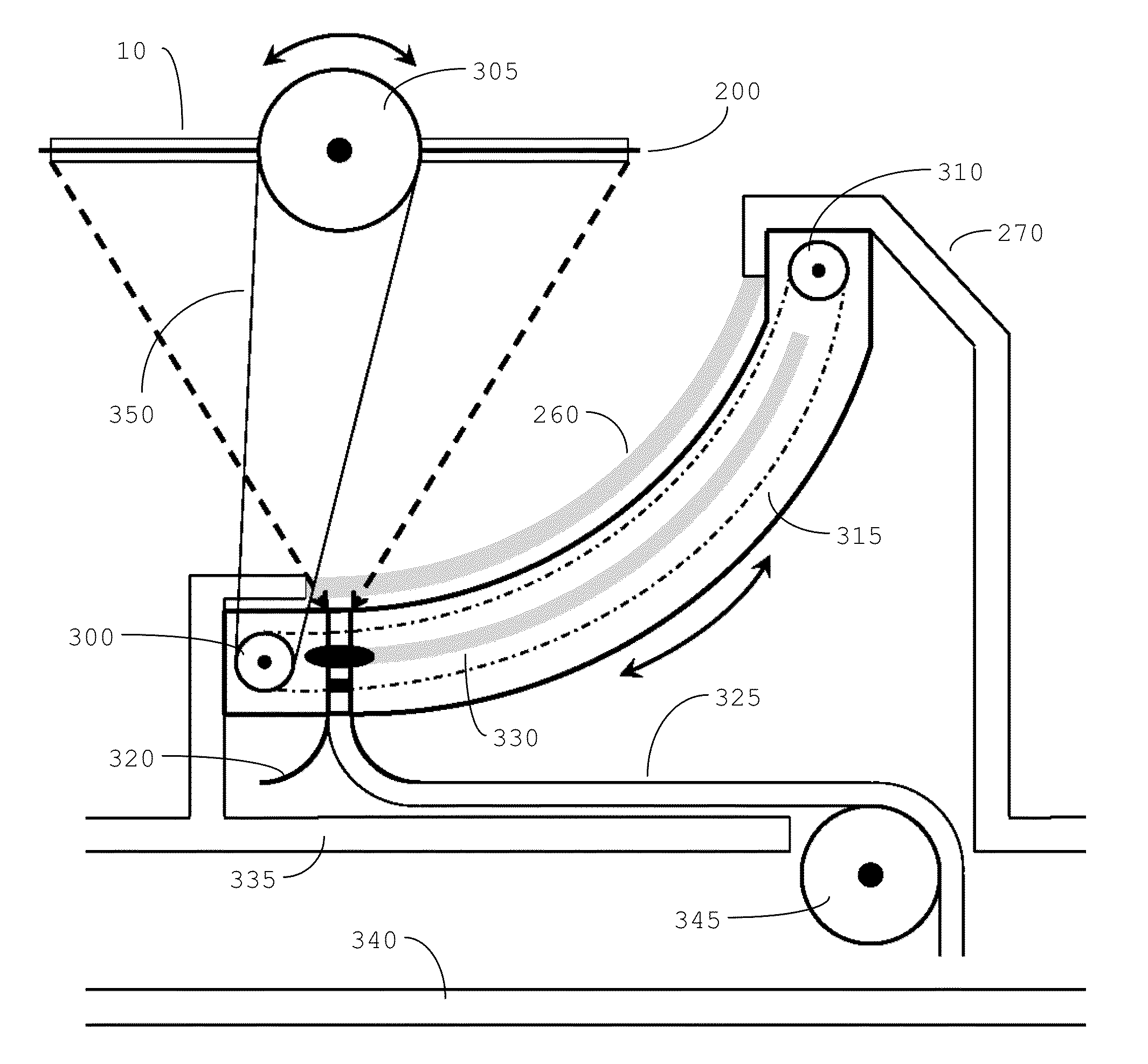

Method and apparatus for electricity production by means of solar thermal transformation

InactiveUS9086059B2Short focal lengthMounting is very lowSolar heating energyFrom solar energyAbove groundEnergy absorption

We present an improved system for solar energy collection and electricity generation, comprising a solar collector apparatus, said apparatus comprising an array of square Fresnel lenses arranged in rows with modular energy absorption devices located below, wherein the array is mounted on arms at a low height above ground, the rows of said array are rotatable horizontally about their lengthwise axis, and the array is mounted on a rotatable baseThe system further comprises transportable insulated storage tanks containing a storage medium, Stirling engines and generators. The solar collection apparatus heats the storage medium, the storage medium supplies the Stirling engines with heat, and each engine is coupled to a generator.In a preferred embodiment, the system additionally comprises embedded controllers using real-time algorithms providing smart on-the-fly management of the system.

Owner:LOGOTHETIS GEORGIOS

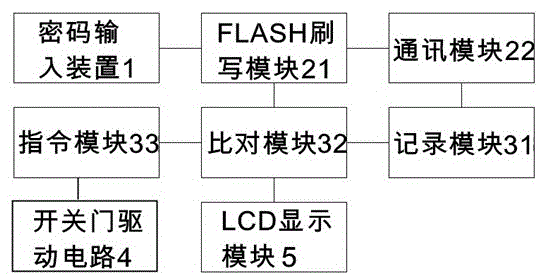

Electronic lock with function of preventing cracked unlocking by detaching connecting wire

InactiveCN106296912APrevent cracking and unlockingImprove securityPower-operated mechanismIndividual entry/exit registersInput deviceReal time algorithm

The invention discloses an electronic lock with a function of preventing cracked unlocking by detaching a connecting wire. The electronic lock comprises a password input device, a singlechip microcomputer, a central monitoring system and a door opening / closing driving circuit, wherein the singlechip microcomputer comprises a FLASH module and a communication module; the central monitoring system is a microcomputer which comprises a recording module, a comparison module and an instruction module; the password input device is used for inputting unlocking information into the electronic lock; the FLASH module is connected with the password input module and can be used for asynchronously updating an encryption algorithm and performing real-time algorithm encryption on the inputted unlocking information; the recording module is used for recording preset unlocking information; the communication module is connected with the FLASH module and the recording module and is used for performing real-time algorithm encryption on the preset unlocking information; the comparison module is connected with the recording module and the FLASH module and is used for comparing the preset unlocking information subjected to the real-time algorithm encryption with the inputted unlocking information subjected to the real-time algorithm encryption; the instruction module is connected with the comparison module and the door opening / closing driving circuit and is used for instructing the door opening / closing driving circuit to work after correct comparison of the comparison module. The electronic lock can be used for effectively preventing the cracked unlocking by detaching the connecting wire, is higher in safety performance and has good practicality.

Owner:苏州微柚物联科技有限公司

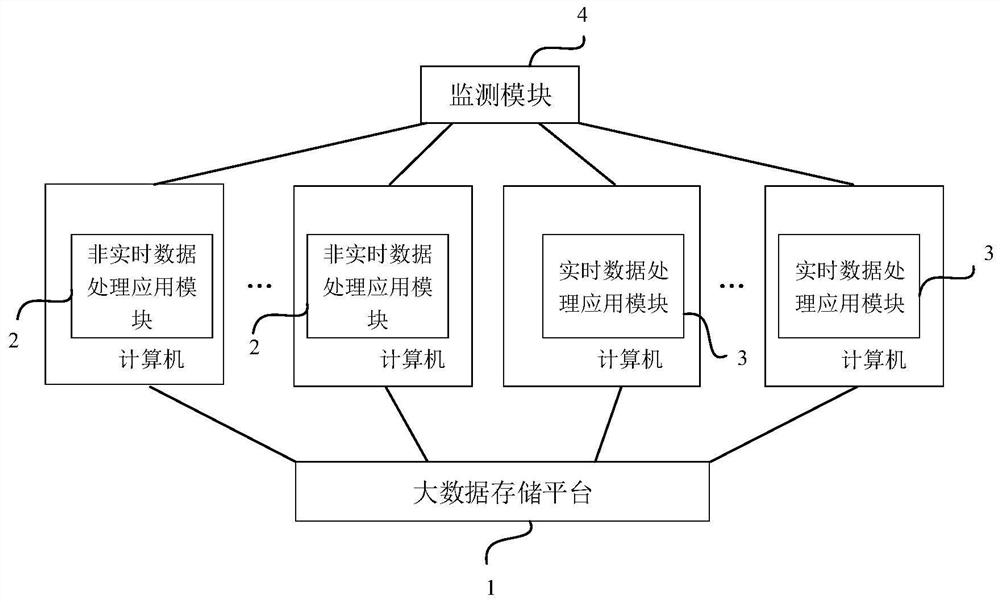

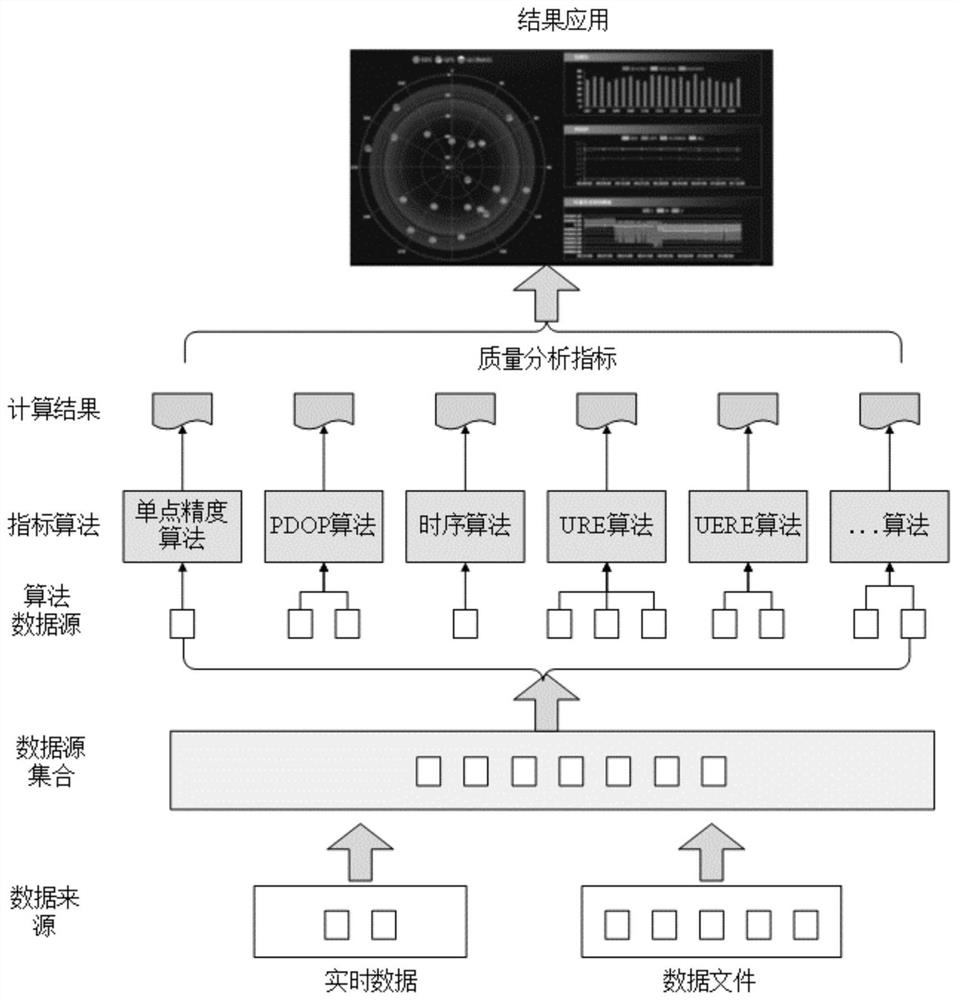

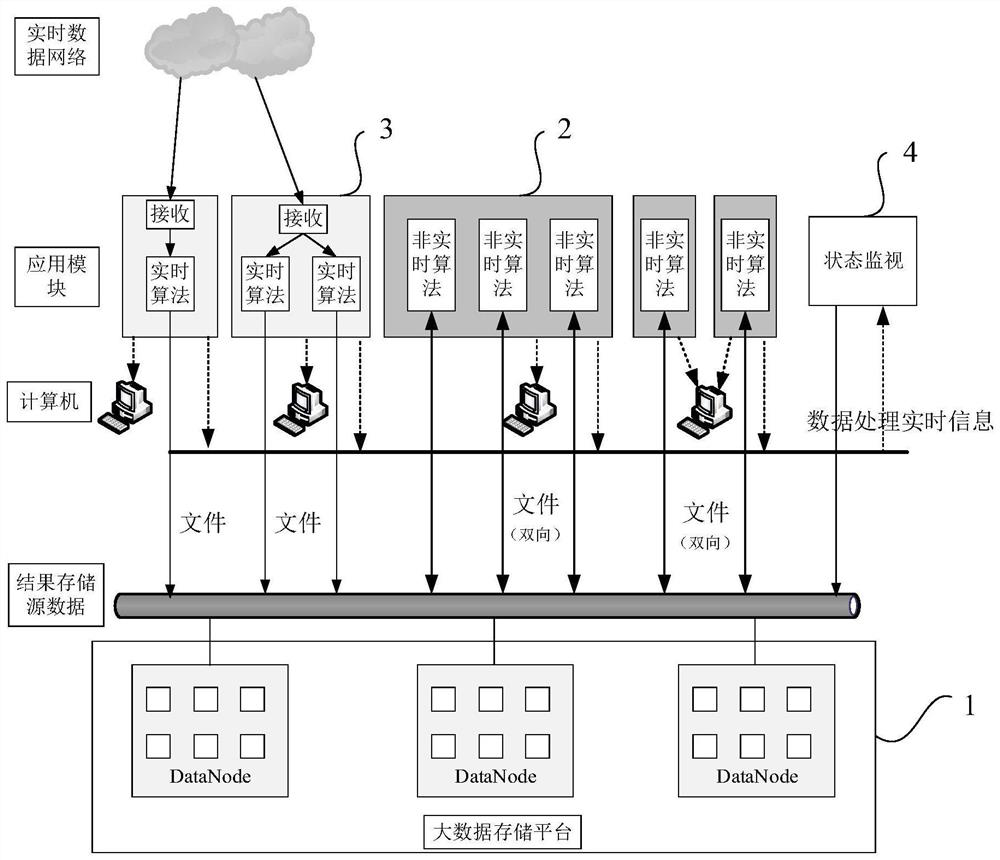

Satellite data distributed processing system and method based on big data storage platform

ActiveCN114416815ALow costEasy to implementDatabase distribution/replicationSpecial data processing applicationsReal time algorithmSatellite data

The invention discloses a satellite data distributed processing system and method based on a big data storage platform, and the system comprises the big data storage platform, a plurality of non-real-time data processing application modules, a plurality of real-time data processing application modules, and a monitoring module. The big data storage platform is used for receiving and storing various types of original data for satellite data processing from each observation station; each non-real-time data processing application module is at least integrated with one piece of satellite index non-real-time algorithm software, and the plurality of non-real-time data processing application modules are respectively arranged on a plurality of computers; each real-time data processing application module is at least integrated with one piece of satellite index real-time algorithm software, and the plurality of real-time data processing application modules are respectively arranged on a plurality of computers; the monitoring module is connected to each computer. Based on the big data storage platform, data processing calculation is carried out in a distributed mode, and the performance requirements for computers and application software are lowered.

Owner:NAT TIME SERVICE CENT CHINESE ACAD OF SCI

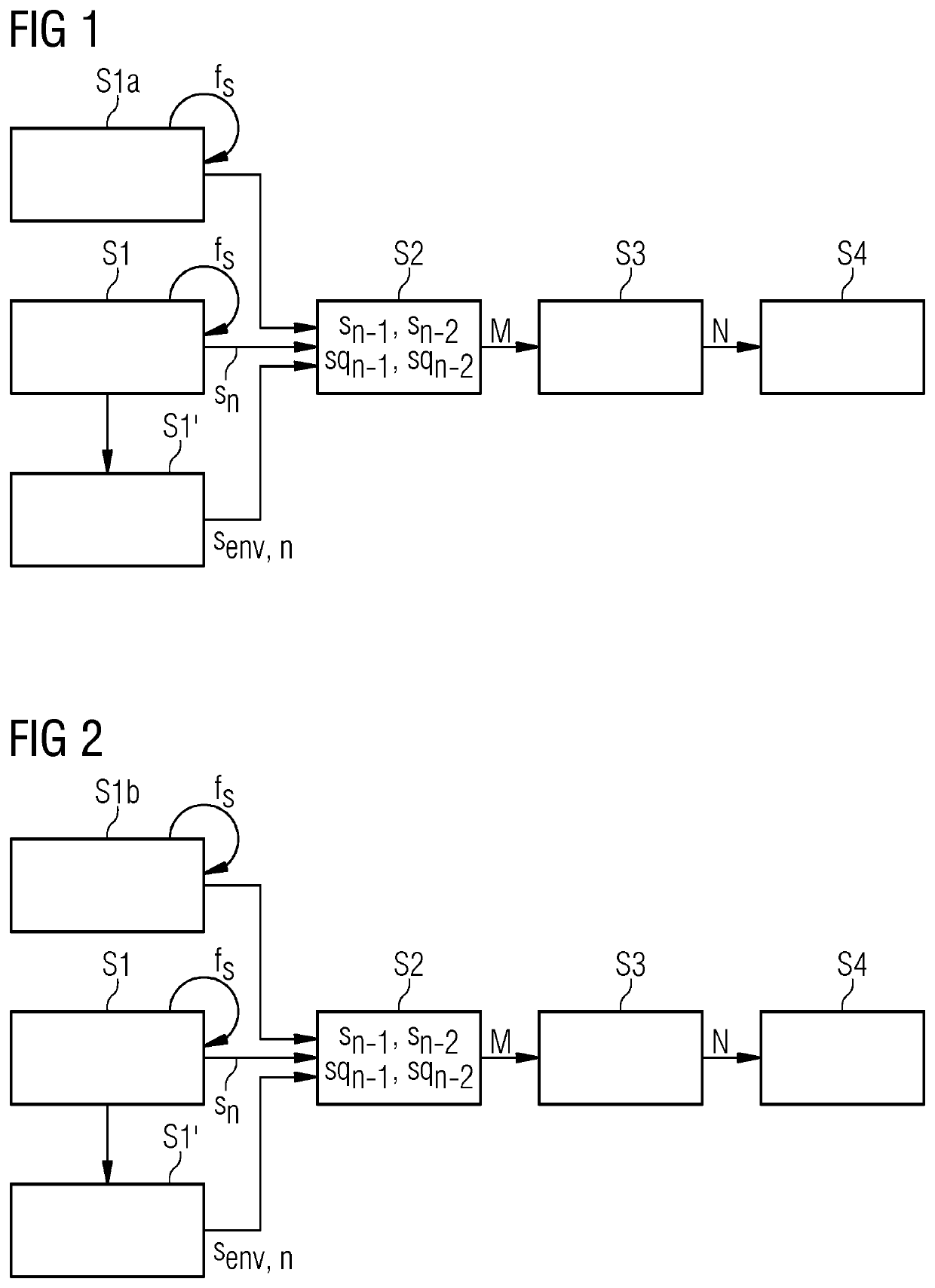

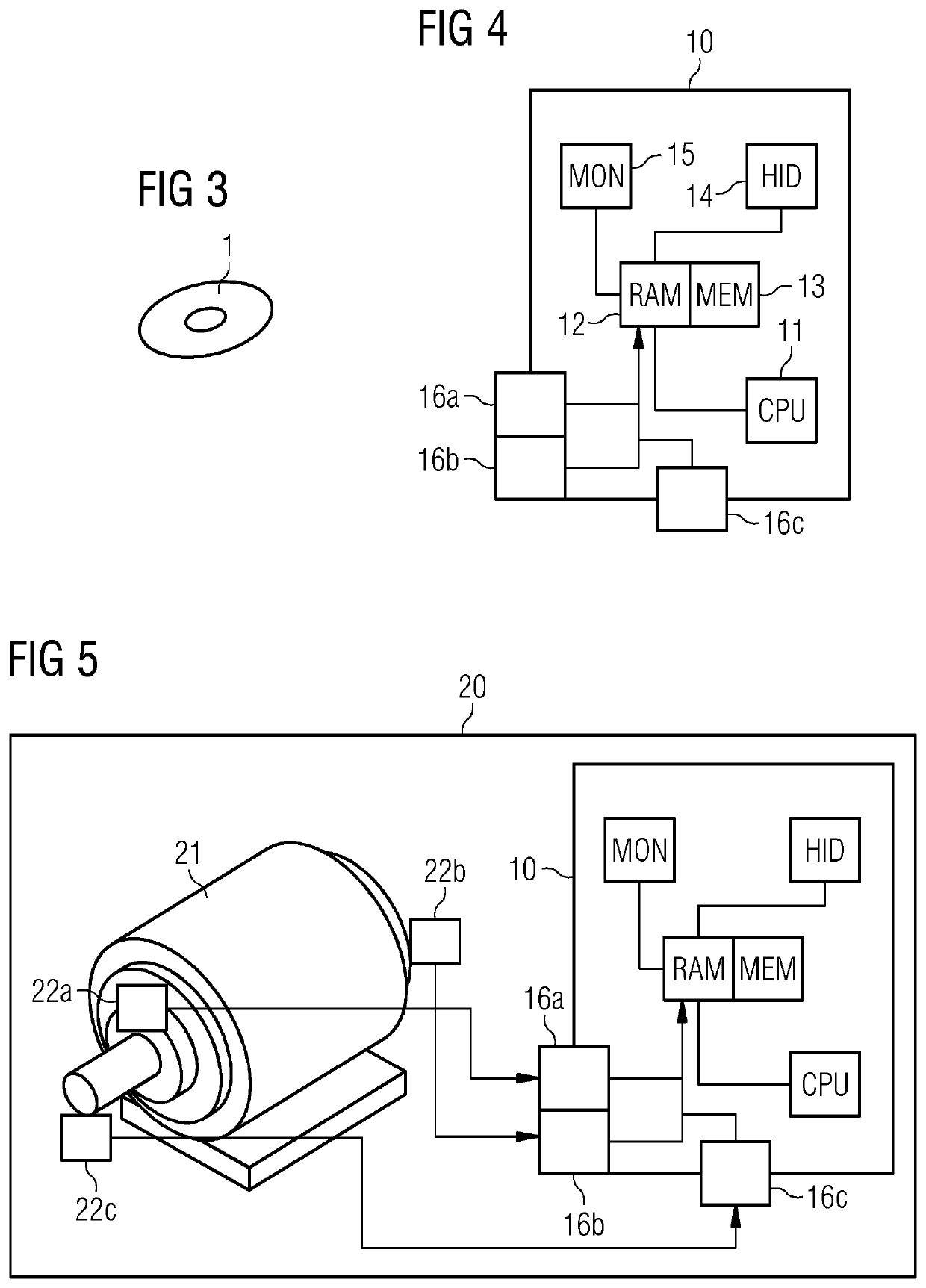

Smart motor data analytics with real-time algorithm

ActiveUS20220357194A1Avoid a lotReduce data processing costsVibration measurement in solidsMachine part testingData processing systemReal time algorithm

A computer-implemented method of Condition Monitoring (CM) for rotating machines like motors, a corresponding computer program, computer-readable medium and data processing system for CM for rotating machines as well as a system including the data processing system for CM for rotating machines. M accumulator variables are updated in real-time based on L samples including a current sample sn and at least one preceding sample Sn−1 of input data. Based on the M accumulator variables N spectral features are computed in real-time. A condition of the rotating machine is determined based on the N spectral features.

Owner:SIEMENS AG

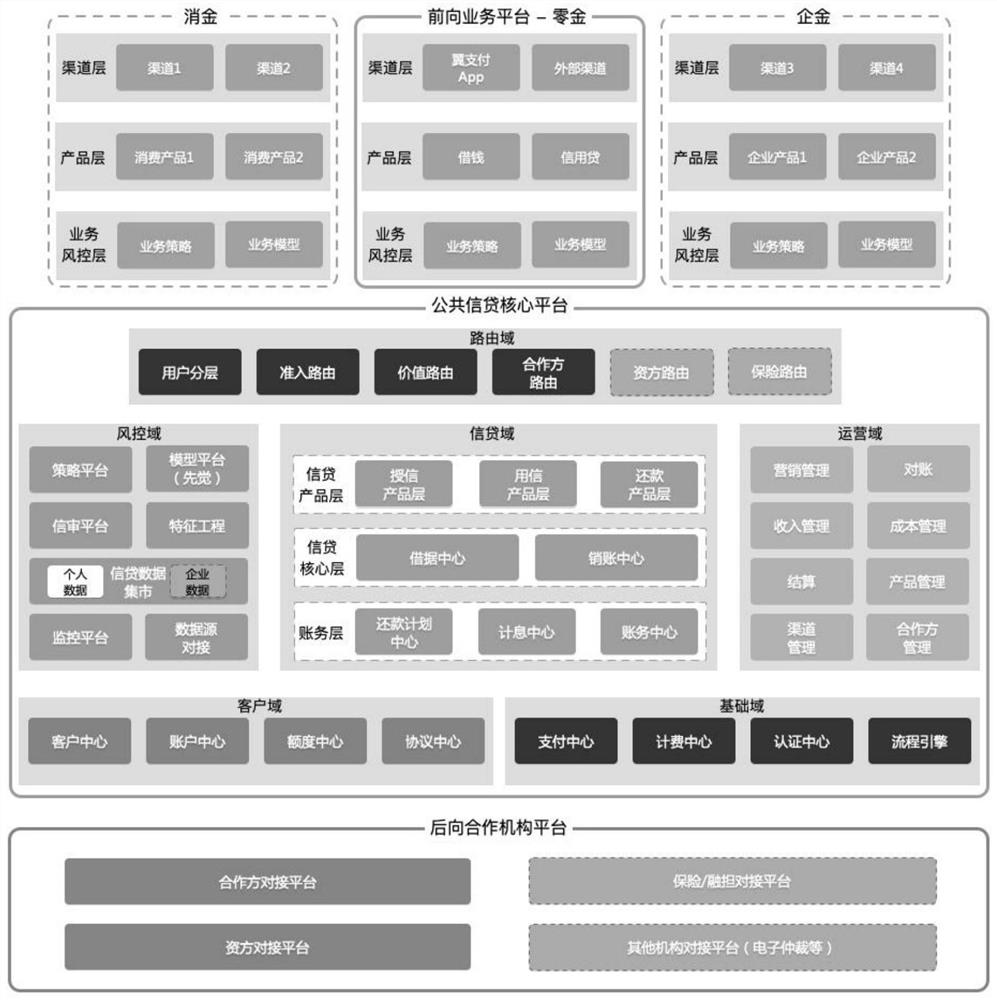

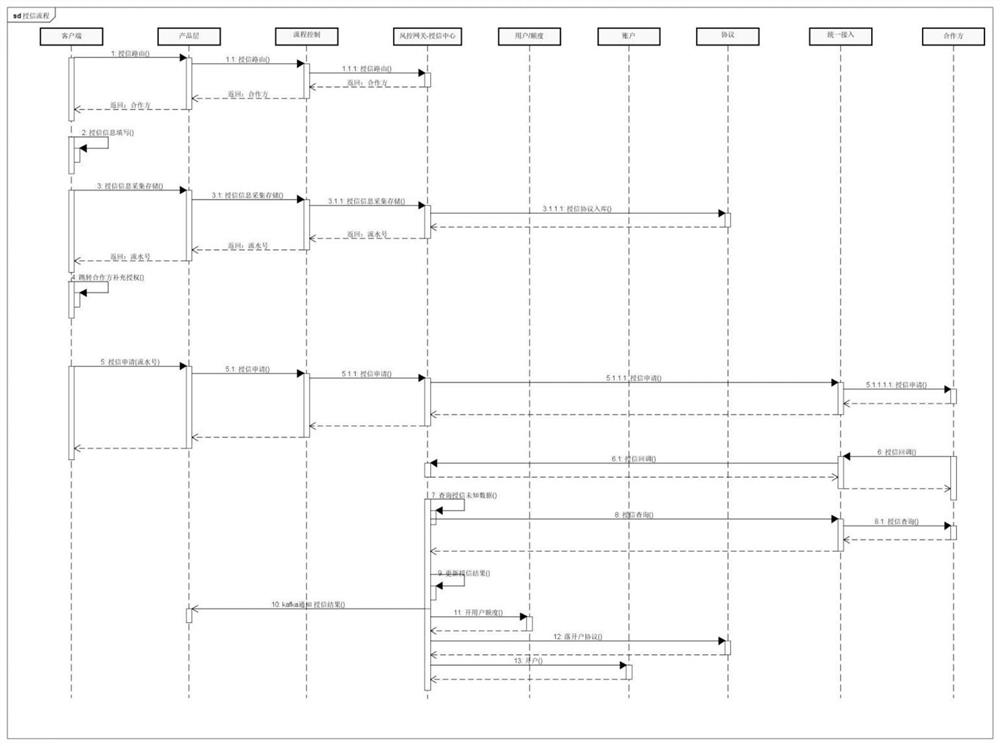

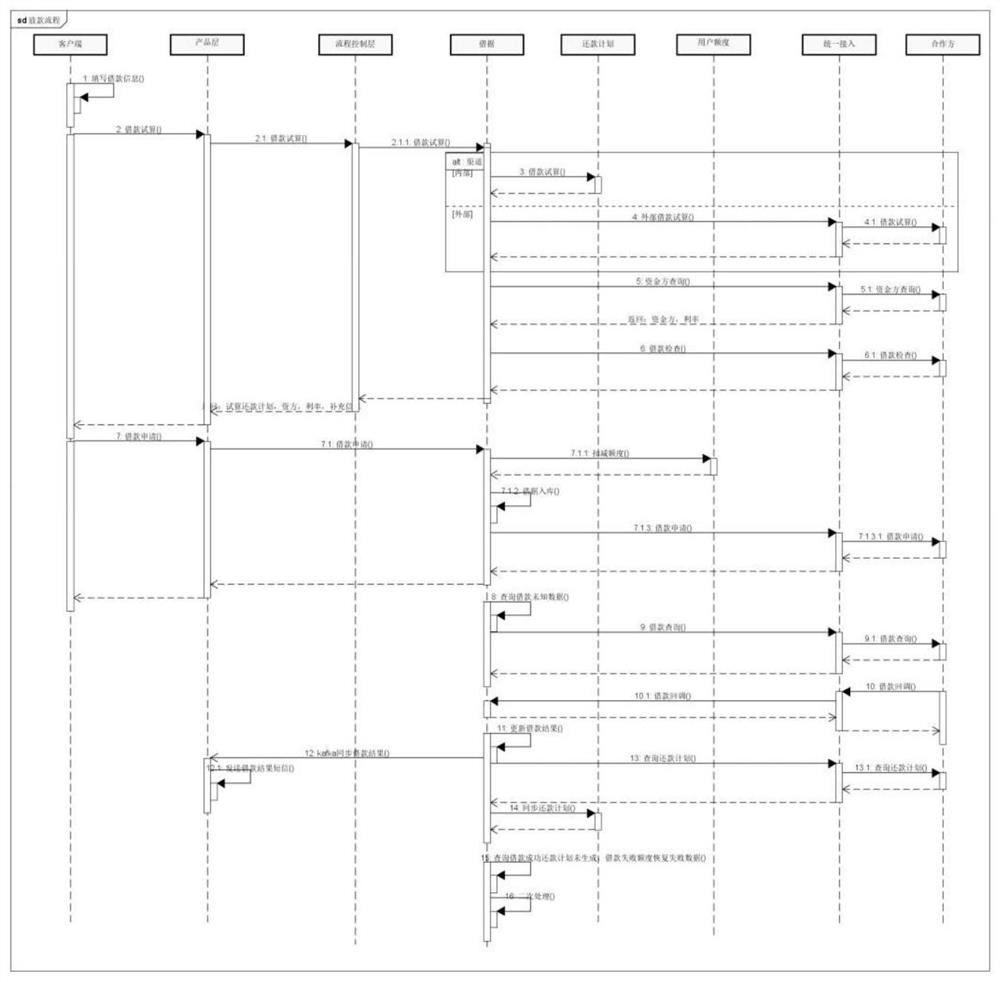

Method and system for complex credit matching platform

PendingCN112288387AImprove liquidityImprove big data risk control capabilitiesFinanceOffice automationOperations researchStatic data

The invention discloses a method and system for a complex credit matching platform. The system is composed of a product domain system, a routing domain system, a risk control domain system, a credit domain system, an operation domain system, a client domain system and a basic domain system. Financial diversion service and financial science and technology service with intelligent risk control as the core are provided, the user operation and flow conversion capacity and big data risk control capacity of a cooperative financial institution are improved, and meanwhile a high-flow platform is helped to improve the flow change capacity. A user can complete credit granting service acceptance of all fund parties after completing information acquisition in the system. The system completes user portraying, rating and other work based on static data and dynamic data of a client, does not need to perform any processing offline, greatly reduces the offline labor cost, and meanwhile, a user calculates and provides related qualification party platform quotas meeting user requirements according to a real-time algorithm in different payment scenes.

Owner:TIANYI ELECTRONICS COMMERCE

Ultrasonic beam synthetic focusing parameter real-time algorithm and device thereof

ActiveCN101097256BAchieving multi-beam correctionUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsReal time algorithmUltrasonic beam

The invention relates to a kind of method and device to calculate synthesized focusing parameter of supersonic wave beam, and it sets the initial parameter, and adds 2*c2*n+2*tD*n to first intermediate variable sum to calculate the new value of first intermediate variable, and calculate the second intermediate variable sum_a: sum_a=sum-2*T-2*tD+1, and compares the absolute value of first intermediate variable sum and second intermediate variable sum_a, if |sum_a|<|sum|, it will iterative compute the focus matrix delay inequality tD, and the value of first intermediate variable sum is set to be the second intermediate variable sum_a, and the focus bite is 0 or 1 according to the comparing result and output. It just needs to load the limited initial parameter to obtain the ideal focusing parameters by the iterative computation. It fits for linear array, phased array and protrusion array. And it fits for multiple-beam, and supports the multiple-beam to receive the focusing calibration. It can realize in FPGA, and can be used in system with random channels and focuses.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD