A high-performance DSP memory access pipeline circuit and its realization method

A pipeline, high-performance technology, applied in the direction of electrical digital data processing, instruments, calculations, etc., can solve the problems of small SRAM, missing, unfavorable multi-core shared data storage, etc., and achieve the effect of large data throughput efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

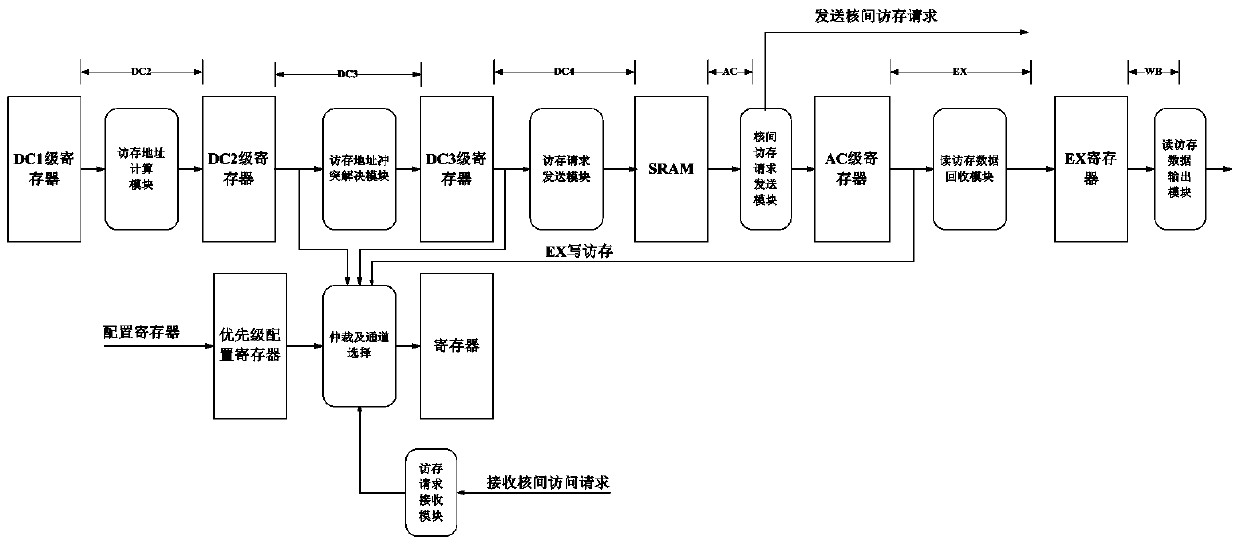

[0029] Such as figure 1 As shown, a high-performance DSP memory access pipeline circuit includes a memory access address calculation module, which is used to generate multiple effective addresses according to the form of memory access instructions; a memory access address conflict resolution module, which is used to judge memory access conflicts of multiple addresses and determine the address launch sequence; the memory access request sending module is used to send the memory access request for accessing the adjacent core to the adjacent core; the memory access request receiving module is used to receive the memory access request sent by the adjacent core; the inter-core access The memory request sending module is used to detect the inter-core memory access request and send it out; the read memory data recovery module is used to splice the data returned by multiple read addresses that have conflicts after multiple cycles. The recovery process is memory access The reverse proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More