Method for preventing growth of redundant SiGe in shoulder part of grid

A redundant and shoulder technology, which is applied in SRAM process manufacturing to prevent the growth of SiGe redundant on gate shoulders. In the field of 28nm integrated circuits, it can solve problems such as limited film thickness, process influence, and SRAM has no function.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

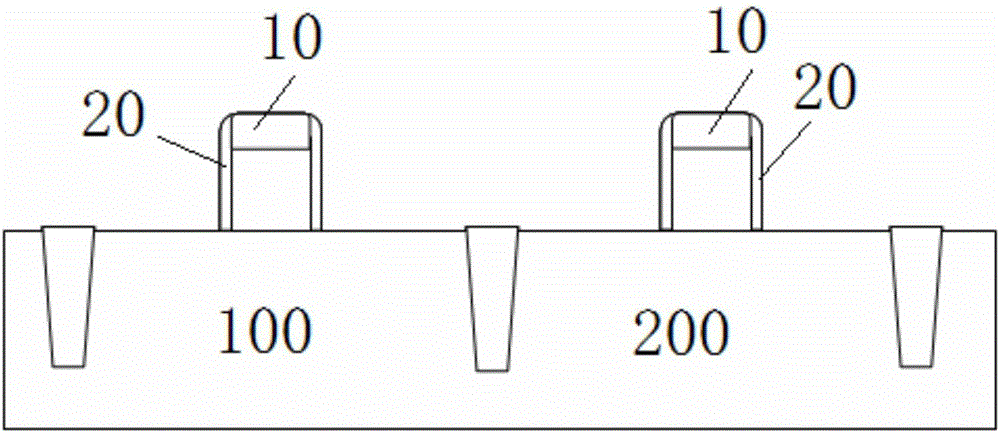

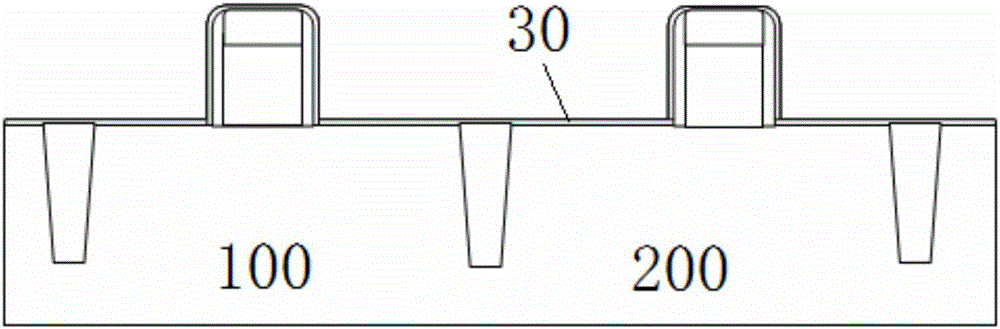

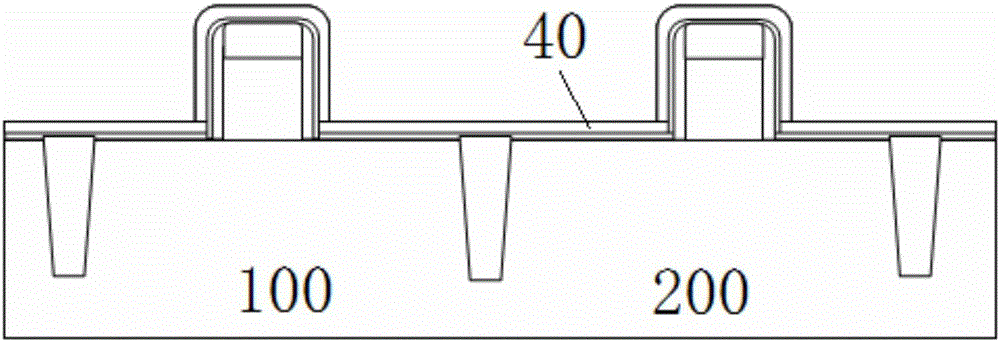

[0032] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0033] In view of the above-mentioned technical problems in the prior art, the present invention adds a second sidewall process in the process to increase the protection of the gate, so as to prevent the first There is too much loss in the sidewall of the channel, and excess germanium and silicon are grown on the gate shoulder. Through the above method, the present invention avoids the generation of redundant silicon germanium on the PMOS gate shoulder, and increases the process control capability.

[0034] Figure 8 A flow chart of a method for preventing redundant SiGe growth on a gate shoulder according to a preferred embodiment of the present invention is schematically shown.

[0035] Specifically, such as Figure 8 As shown, according to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More