High-density circuit chip packaging process

A chip packaging, high-density technology, used in circuits, printed circuits, printed circuit manufacturing, etc., can solve the problems of limiting the density of chip lines, no problems with this process, and inability to dense lines, and achieve the effect of flexible design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be described in detail below in conjunction with specific embodiments.

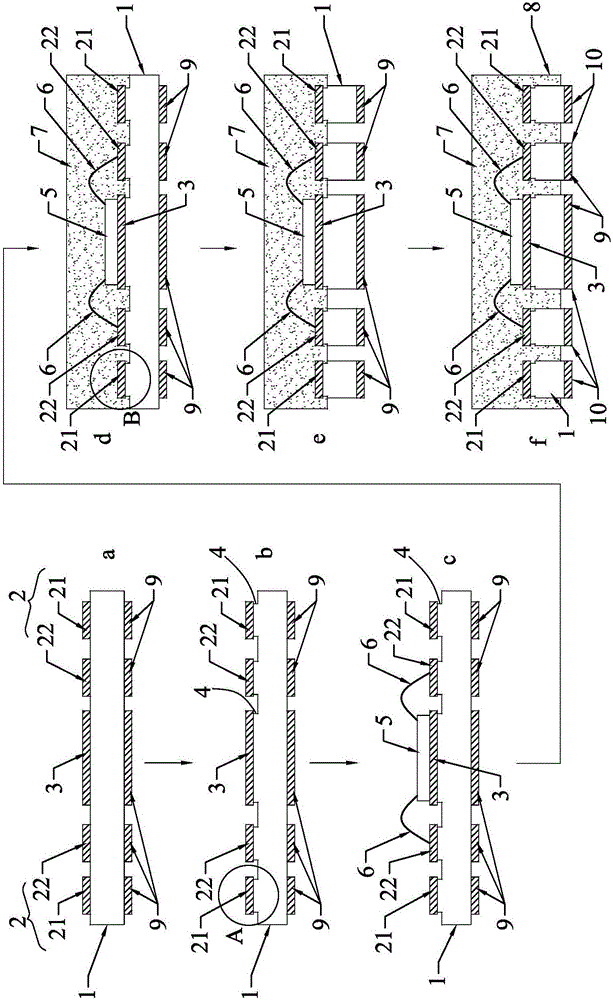

[0026] Such as figure 1 As shown, the high-density circuit chip packaging process of this embodiment includes the following steps:

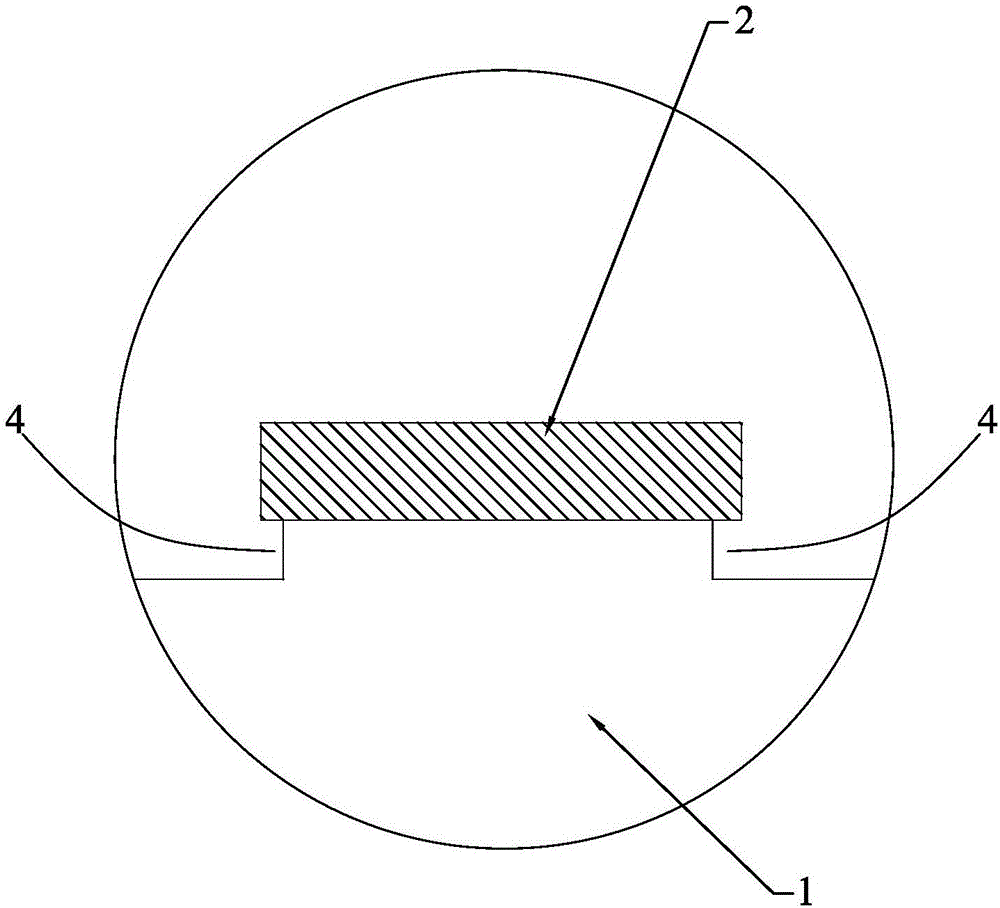

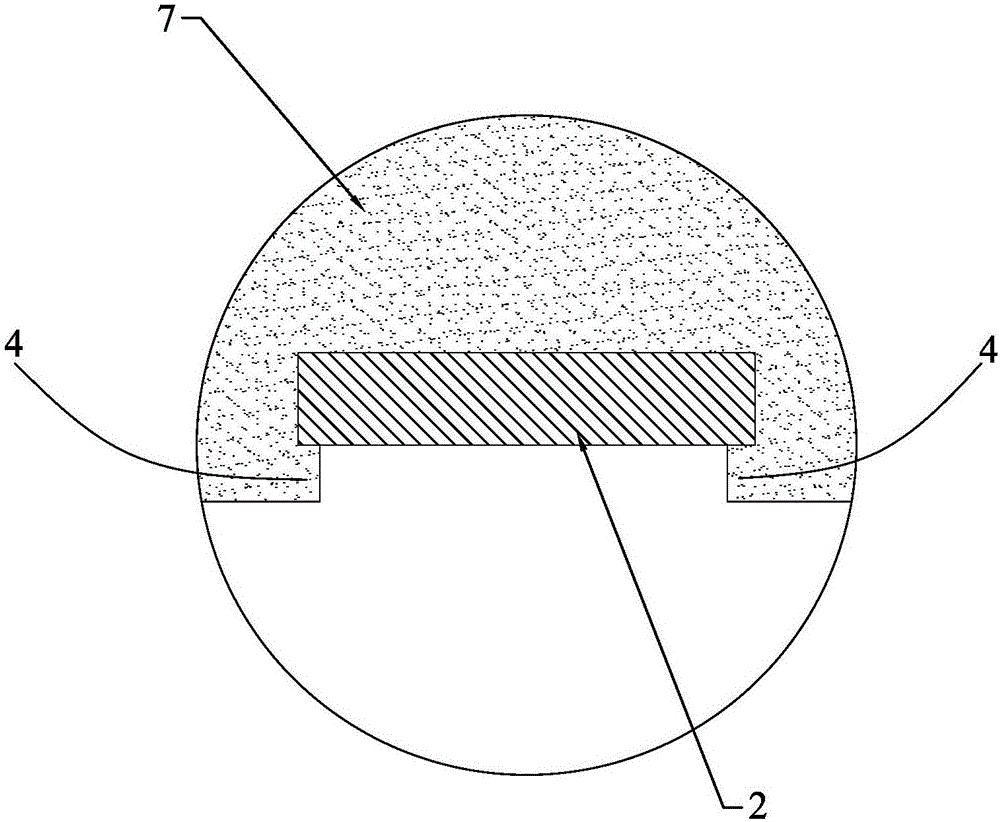

[0027] Electroplating: electroplating on the front of the copper substrate 1 according to the pattern of the circuit 2 of the chip to form an electroplating layer as the circuit 2 . Line 2 see Figure 4 , the line 2 includes a wire 21 (different from the wire 6 welded), a welding wire welding position 22 and an outer pin connection position 23, the welding wire welding position 22 is used for welding the wire 6, and the outer pin connection position 23 is used for connecting the outer pin 10, It should be noted, figure 1 In order to briefly show the process, the representation of the line 2 and its relationship with the outer pin 10 is not necessarily complete. For details of the line 2, see Figure 4 , the bottom of the outer pin connec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More