Method and system for automatically realizing channel switching of JTAG link

A channel switching, link technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

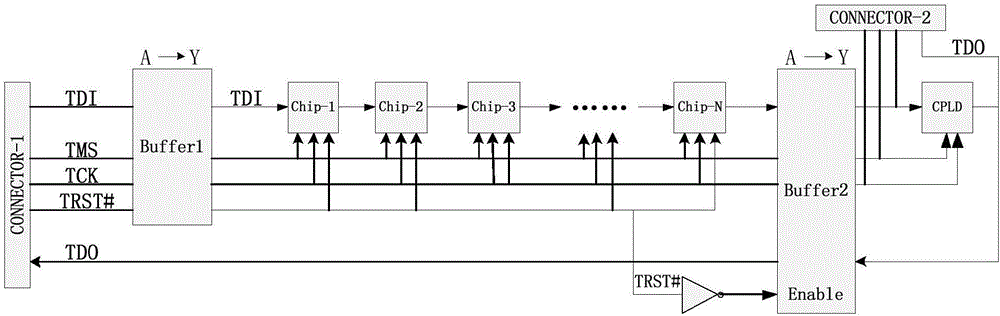

[0026] In view of the deficiencies in the prior art, the inventor of this case was able to propose the technical solution of the present invention after long-term research and extensive practice. The technical solution, its implementation process and principle will be further explained as follows.

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

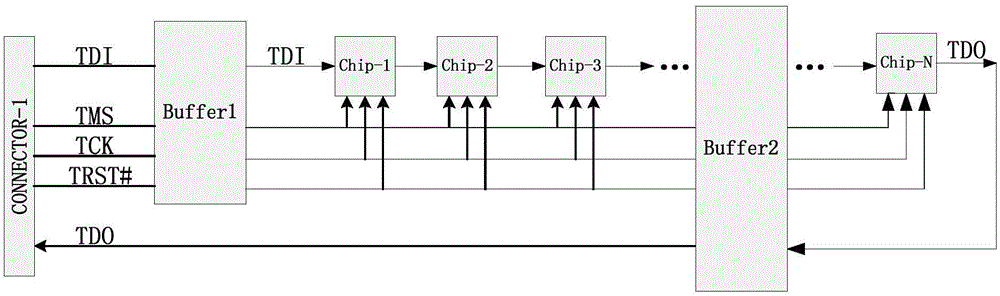

[0028] Figure 1a It is a schematic diagram of the JTAG link in the prior art, including the first connector, buffer buffer1, chipset chip-1, chip-2...chip-N and buffer buffer2, and the JTAG pins are connected between each component connected. Among them, the JTAG pins include:

[0029] TCK is the te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More