Programmable logic device configuration method and device

A technology of programming logic and configuration method, which is applied in the field of digital electronics, can solve the problem that the critical path cannot accurately control the utilization rate of large PLD resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] Embodiment 1 of the present invention provides a method for implementing the configuration process of programmable logic devices based on the Valence language, so as to achieve the purpose of configuring and debugging PLDs, and the configuration process is efficient and convenient, which is conducive to the development and testing of PLD logic functions by designers , is conducive to promoting the development of PLD technology.

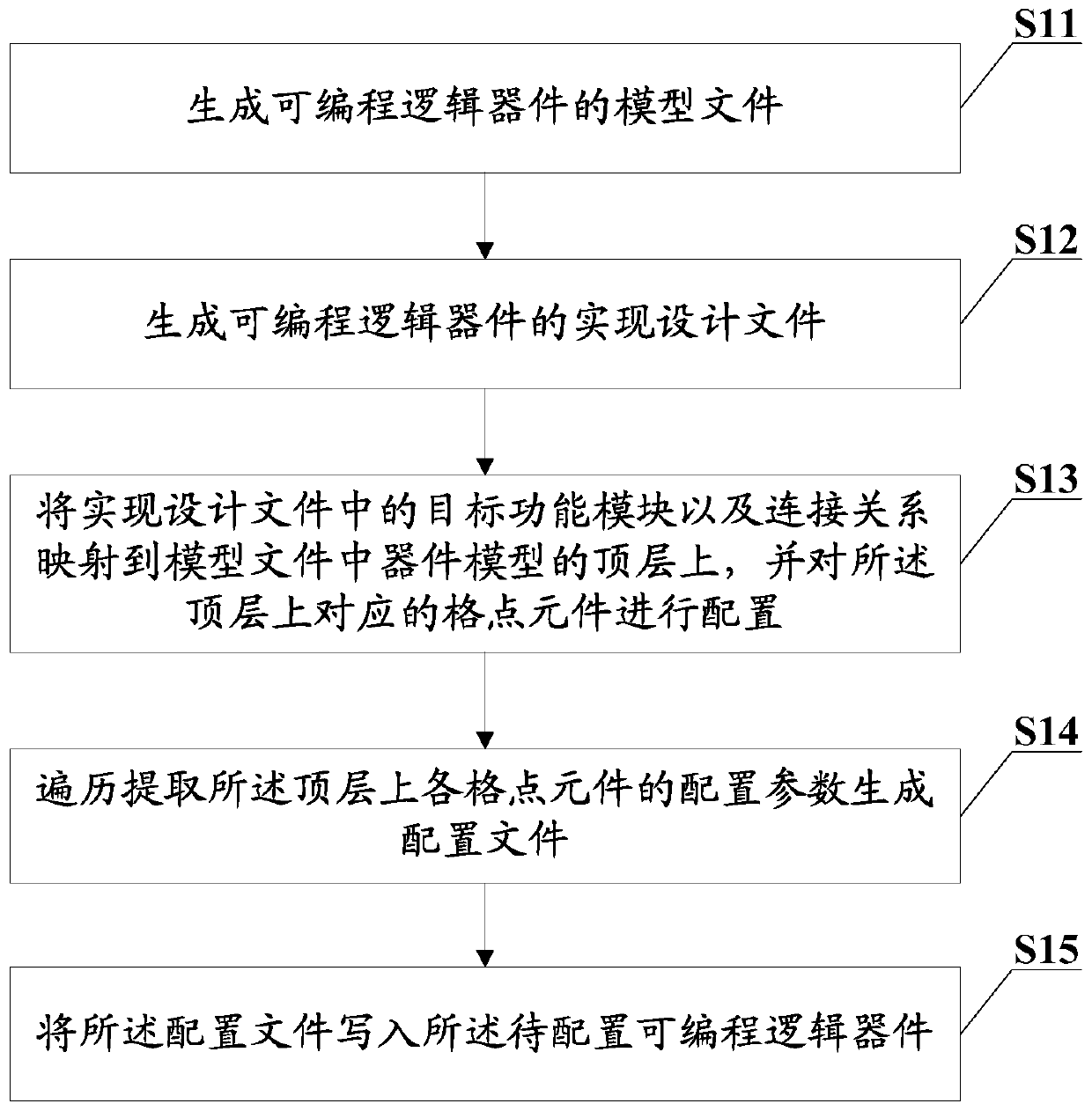

[0046] See figure 1 , figure 1 A schematic flowchart of a PLD configuration method provided in Embodiment 1 of the present invention, including:

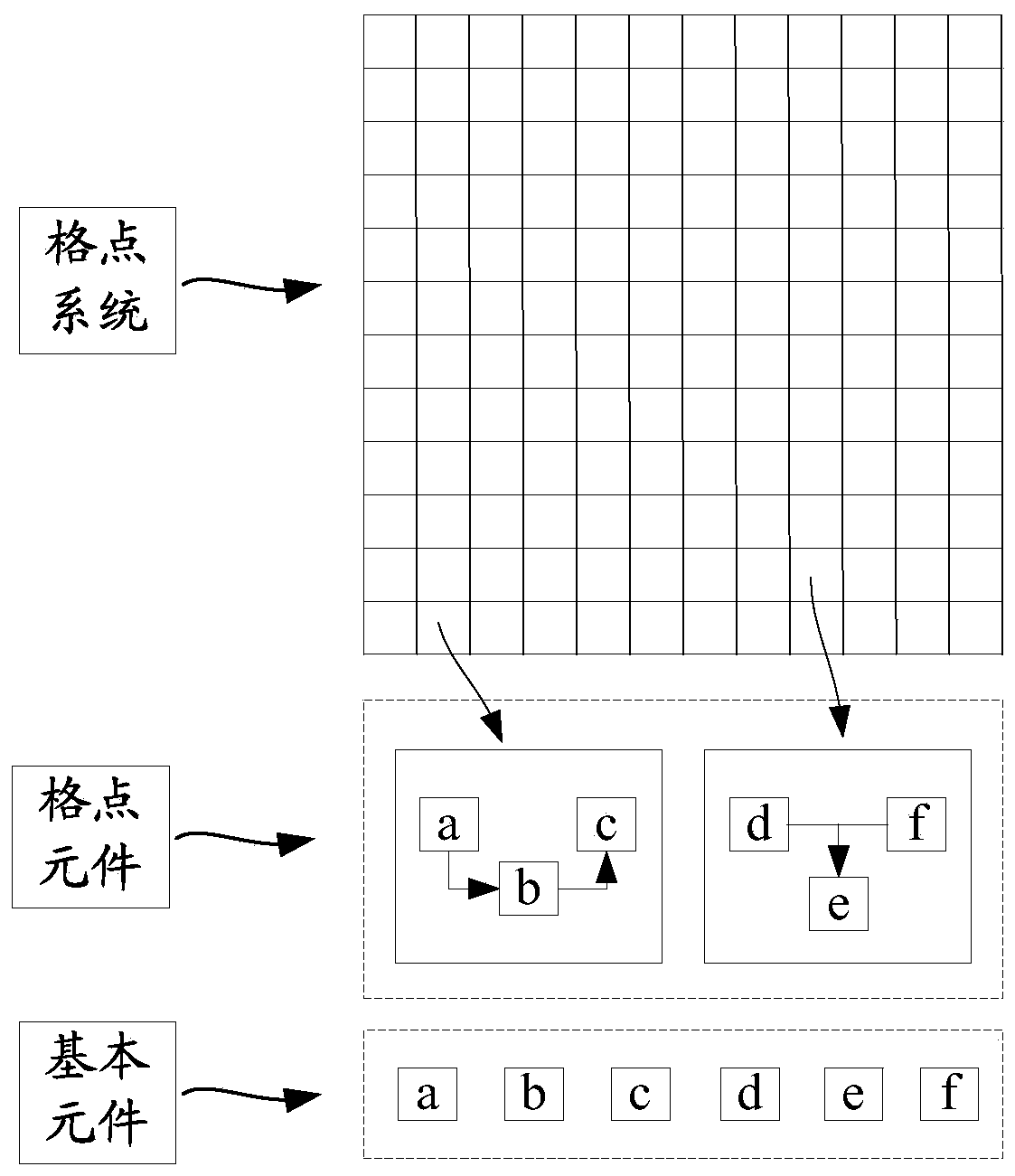

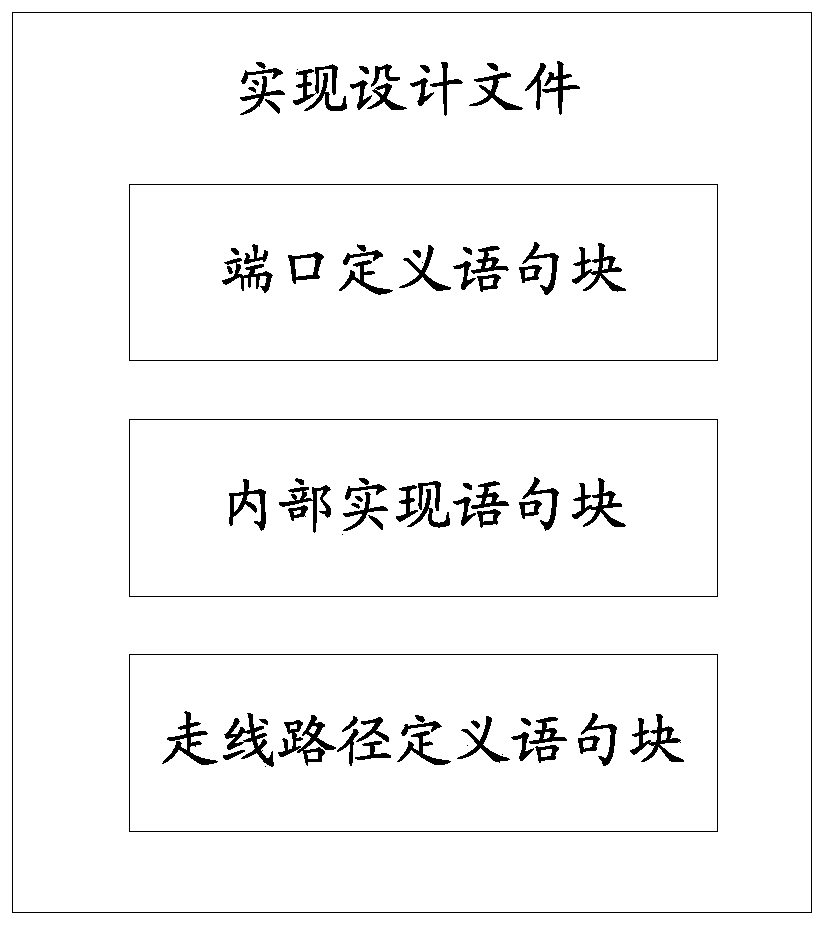

[0047] S11: Generate a PLD model file, which contains a device model and an operator model; the device model includes a PLD basic element at the bottom layer, a grid element at the middle layer, and a grid system at the top layer, the grid point The element is composed of at least one basic element, and the lattice system is composed of at least one lattice element; the operator model includes func...

Embodiment 2

[0078] An embodiment of the present invention provides a device for configuring a programmable logic device, which is used to implement the method for configuring a programmable logic device described in the first embodiment. Please refer to Figure 5 , Figure 5 It is a schematic structural diagram of a programmable logic device configuration device provided in Embodiment 2 of the present invention. The programmable logic device configuration device 5 includes: a model generation module 51, a design generation module 52, and a processing module 53, wherein:

[0079] Model generation module 51, is used for generating PLD model file, contains device model and operator model in the described PLD model file; Described device model comprises the PLD basic element that is positioned at bottom layer, the grid point element of middle layer and the grid point system of top layer , the grid element is composed of at least one basic element, and the grid system is composed of at least ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More