Linear interpolation method and apparatus for fixed interpolation multiple of digital signal

A digital signal, linear interpolation technology, applied in electrical digital data processing, measurement devices, digital variable display and other directions, can solve the problems of large computational load, high circuit implementation cost, consumption of FPGA resources, etc., to achieve fast parallel operation, real-time Good performance and the effect of reducing FPGA resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0078] The linear interpolation method of the fixed interpolation multiple provided by the embodiment of the present application includes:

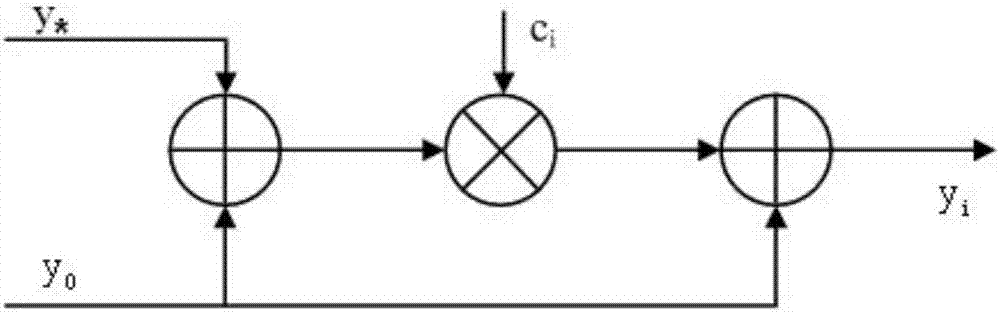

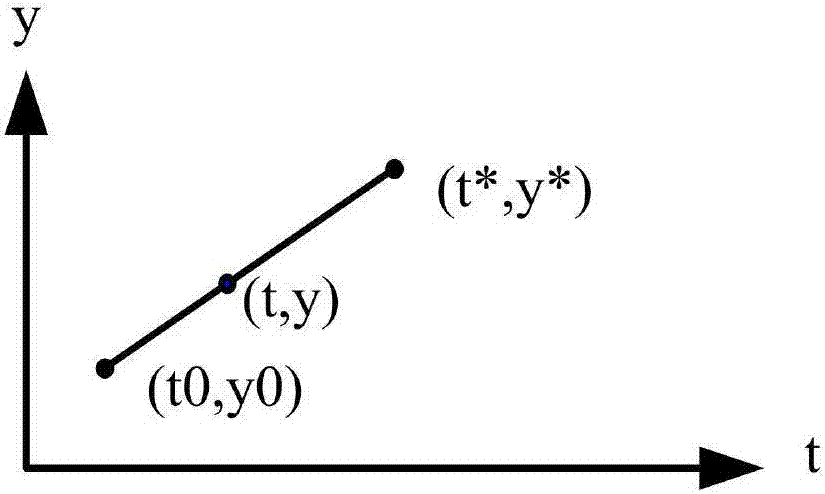

[0079]Step 100, the original data y of the digital signal to be processed 0 、y * Perform addition to get Δy=y * -y 0 .

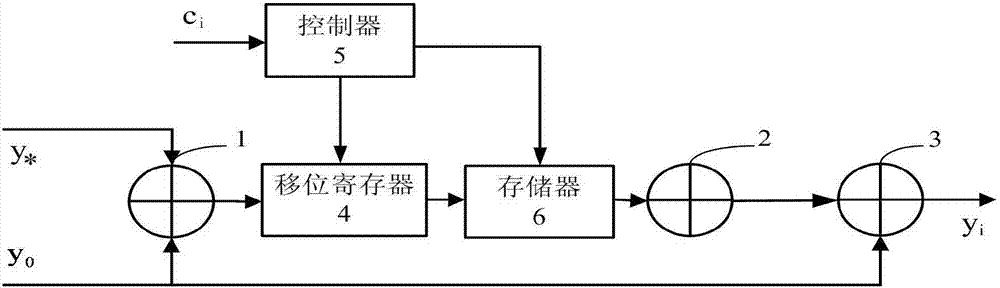

[0080] Step 101, generate the interpolation multiple data c of the digital signal to be processed by the fixed interpolation multiple to be interpolated i , according to c i value, the controller 5 controls the shift register 4 to perform a corresponding shift operation on Δy, each shift generates a shifted data in sequence, and stores the shifted data in the memory 6 .

[0081] For example, for 8bit data, if a linear interpolation of 20 times is performed, like Figure 7 As shown, calculate the first interpolated value y 1 hour, The shift register 4 carries out a 4-bit shift and a 6-bit shift to Δy to generate shift data (Δy>>4) and (Δy>>6) respectively, which are stored in the memory 6; and so on, according...

Embodiment 2

[0091] The linear interpolation method with a fixed interpolation multiple provided in the embodiment of the present application includes:

[0092] Step 200, the original data y of the digital signal to be processed 0 、y * Perform addition to get Δy=y * -y 0 .

[0093] Step 201, generate the interpolation multiple data c of the digital signal to be processed by the fixed interpolation multiple to be interpolated i , the shift register 4 performs an n-bit shift operation on Δy, generates corresponding shift data for each bit shift, and stores the shift data in the memory 6, n+1 is the bit width of the digital signal to be processed, n = 2 η -1, n is a positive integer greater than or equal to 3.

[0094] For example, for 8bit data, if a linear interpolation of 20 times is performed, such as Figure 8 As shown, the shift register 4 shifts Δy by 7 bits, and generates corresponding shift data for each bit shifted, and shifts the shift data (Δy>>0) to (Δy>>7 ) are all store...

Embodiment 3

[0105] The linear interpolation method with a fixed interpolation multiple provided in the embodiment of the present application includes:

[0106] Step 300, the original data y of the digital signal to be processed 0 、y * Perform addition to get Δy=y * -y 0 .

[0107] Step 301, generate the interpolation multiple data c of the digital signal to be processed by the fixed interpolation multiple to be interpolated i , according to c i The controller 5 controls different shift registers to perform corresponding shift operations on Δy at the same time.

[0108] For example, for 8bit data, if a linear interpolation of 20 times is performed, like Figure 9 As shown, calculate the first interpolated value y 1 hour, The shift register 44 shifts Δy by 4 bits to obtain shifted data (Δy>>4), and at the same time, the shift register 46 shifts 6 bits to Δy to obtain shifted data (Δy>>6); accordingly By analogy, according to c 1 ~ c 19 , perform the corresponding shift operati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com