A method for realizing an SoC verification interaction mechanism

A mechanism and interactive interface technology, applied in the field of interactive mechanism of SoC verification, can solve the problems of poor versatility, portability, inconvenient use, etc., and achieve the effect of solving the inconvenience of use and meeting the verification requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

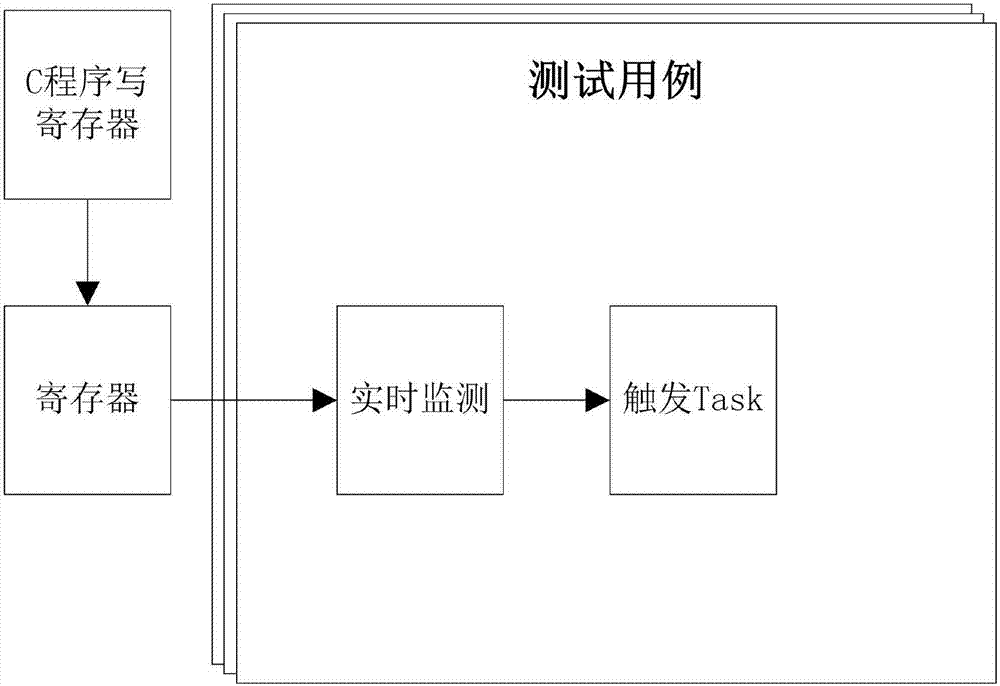

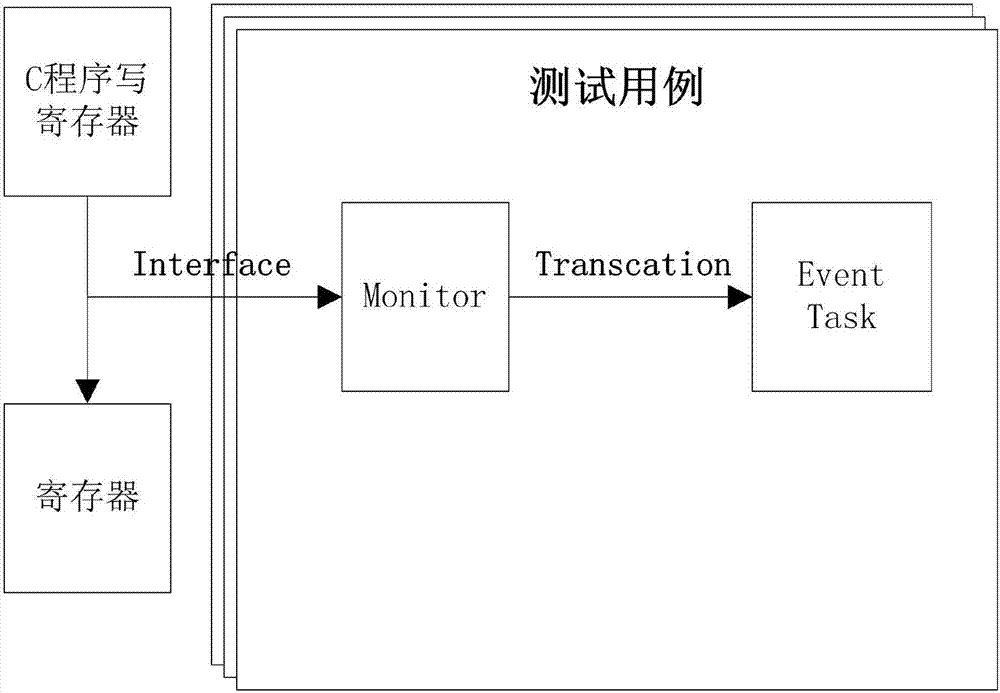

[0012] If you want to implement a C program to control SystemVerilog to execute a certain function. The traditional verification interaction mechanism first uses a C program to write a value to a specific register, and then uses the SystemVerilog language in the verification platform to monitor the value in this register in real time. Once it is found that the C program has changed it to an agreed value, it will Trigger SystemVerilog to execute a specific function....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More