Zynq-7000-based scratch-pad memory single event upset protection method

An on-chip memory, anti-single event technology, applied in the direction of instrumentation, response error generation, hardware redundancy for data error detection, etc., can solve reliability problems, do not have error correction capabilities, and do not meet the needs of spaceborne systems Anti-single event flipping and other issues to achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described below in conjunction with the accompanying drawings.

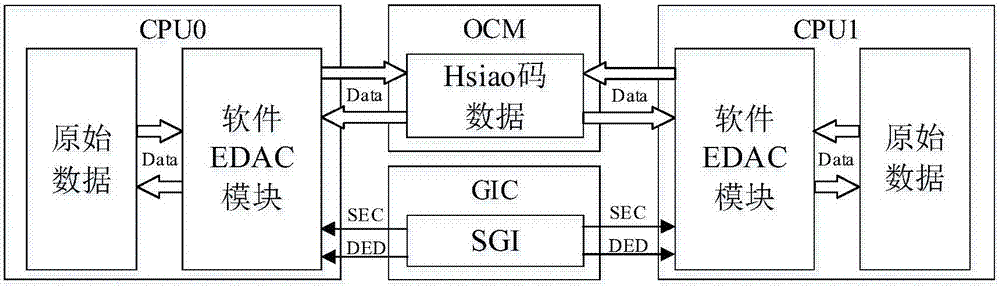

[0028] A Zynq-7000-based on-chip memory anti-single event flipping protection method, using the resource characteristics of the dual-core ARM processor and software generate interrupt (Software Generate Interrupt, SGI) in the Zynq-7000 chip, using the software EDAC method to achieve OCM data fault tolerance , to ensure the reliability of dual-core communication, its functional block diagram is as follows figure 1 shown.

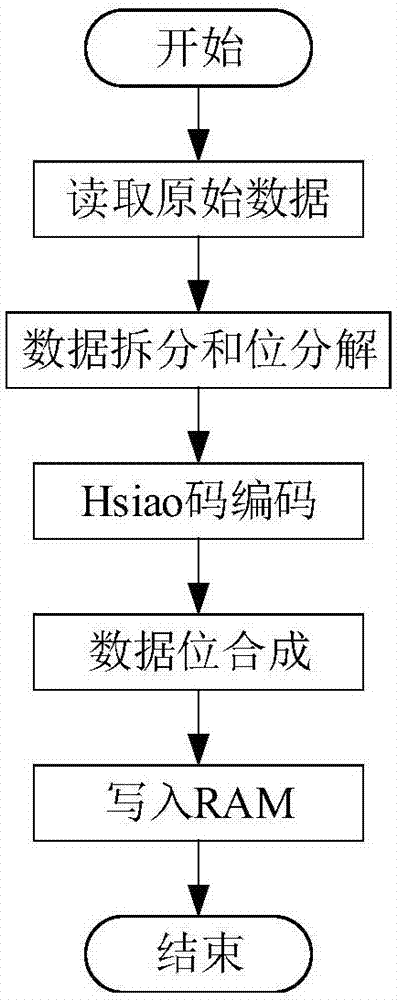

[0029] exist figure 1Among them, the original data in CPU0 or CPU1 is encoded by the software EDAC module and written into OCM; the Hsiao code data in OCM is decoded by the software EDAC module and read by CPU0 or CPU1; when the data read detects When a unit error or a double bit error occurs, SGI generates a software interrupt to write back dual-core synchronous data or notify CPU0 and CPU1 for processing. The main steps are as follows:

[0030] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More