Configurable low-speed PAD and BMC chip possessing intelligent reconfigurable interface

A BMC chip, low-speed technology, applied in the field of IP core design, which can solve the problems of unusable special interfaces, unrealizable peripherals, and unusable new peripherals.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

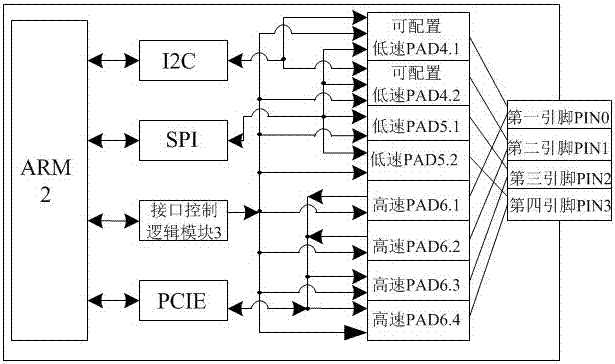

[0124] Embodiment 1, BMC chip with intelligent reconfigurable interface, choose to use I2C interface:

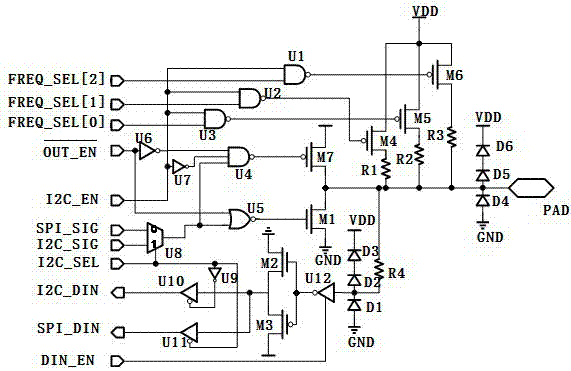

[0125] ARM configuration control information, choose to use the I2C interface, the interface control logic module outputs control signals to the configurable low-speed PAD according to the ARM configuration control information, disables the high-speed PAD, configures the PAD to use the I2C function, and outputs signals: OUT_EN = 0, I2C_EN = 1 , I2C_SEL = 1, DIN_EN = 1.

[0126] When the low-speed PAD output data can be configured, select I2C_SIG to M7 and M1 CMOS tubes. When I2C_SIG is 0, M7 is off, M1 is on, and outputs a low level to the PAD pin; when I2C_SIG is 1, M7 is off, and M1 is off. If any bit of FREQ_SEL[2:0] is valid, it is not required outside the chip Pull-up resistor, just use a pull-up resistor, and the output high point is flat to the PAD pin.

[0127] When the low-speed PAD input data can be configured, DIN_EN = 1, select the PAD signal to M2 and M3 CMOS ...

Embodiment 2

[0128] Embodiment 2, the BMC chip of the intelligent reconfigurable interface, selects to use the SPI interface:

[0129] ARM configuration control information, choose to use the SPI interface, the interface control logic module outputs control signals to the configurable low-speed PAD according to the ARM configuration control information, disables the high-speed PAD, configures the PAD to use the SPI function, and outputs signals: OUT_EN = 0, I2C_EN = 0 , I2C_SEL = 0, DIN_EN = 1.

[0130] When the low-speed PAD output data can be configured, select SPI_SIG to M7 and M1 CMOS transistors. When I2C_SIG is 0, M7 is off, M1 is on, and outputs a low level to the PAD pin; when I2C_SIG is 1, M7 is on, M1 is off, and outputs a high level to the PAD.

[0131] When the low-speed PAD input data can be configured, DIN_EN = 1, select the PAD signal to M2 and M3 CMOS transistors, and then select the data to SPI_DIN according to I2C_SEL = 0.

Embodiment 3

[0132] Embodiment 3, the BMC chip of the intelligent reconfigurable interface, chooses to use the PCIE interface:

[0133] ARM configuration control information, choose to use the PCIE interface, the interface control logic module outputs control signals to the configurable low-speed PAD according to the ARM configuration control information, output signal: OUT_EN = 0, DIN_EN = 0, FREQ_SEL[2:0] = 0, disabled When using the transmission function, the use of pull-up resistors is prohibited; at the same time, high-speed PAD is enabled, and high-speed differential signals pass through the high-speed PAD to the PCIE module.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More