Serial interface universal verification platform and method based on SV language

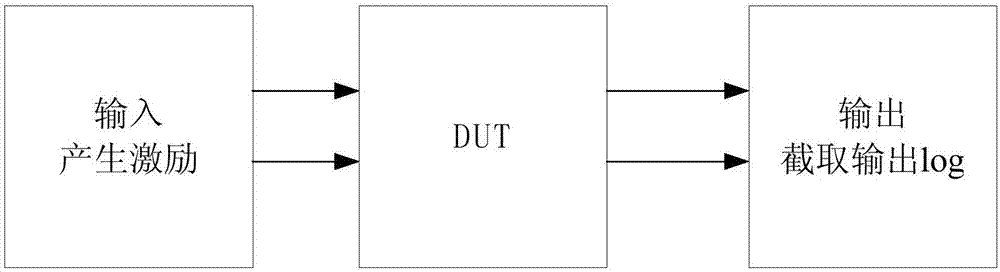

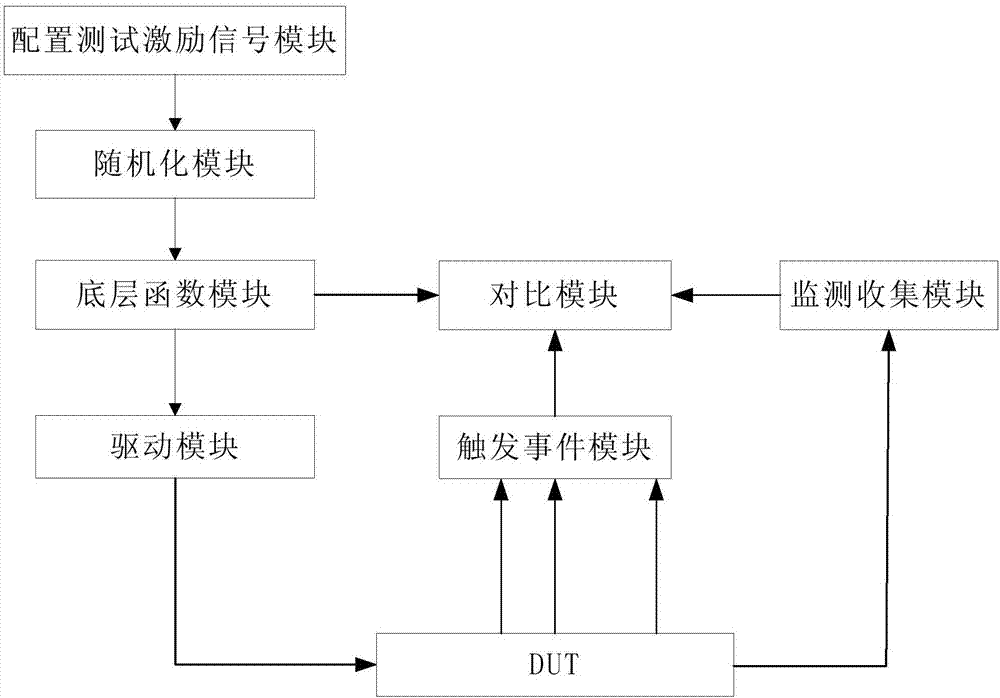

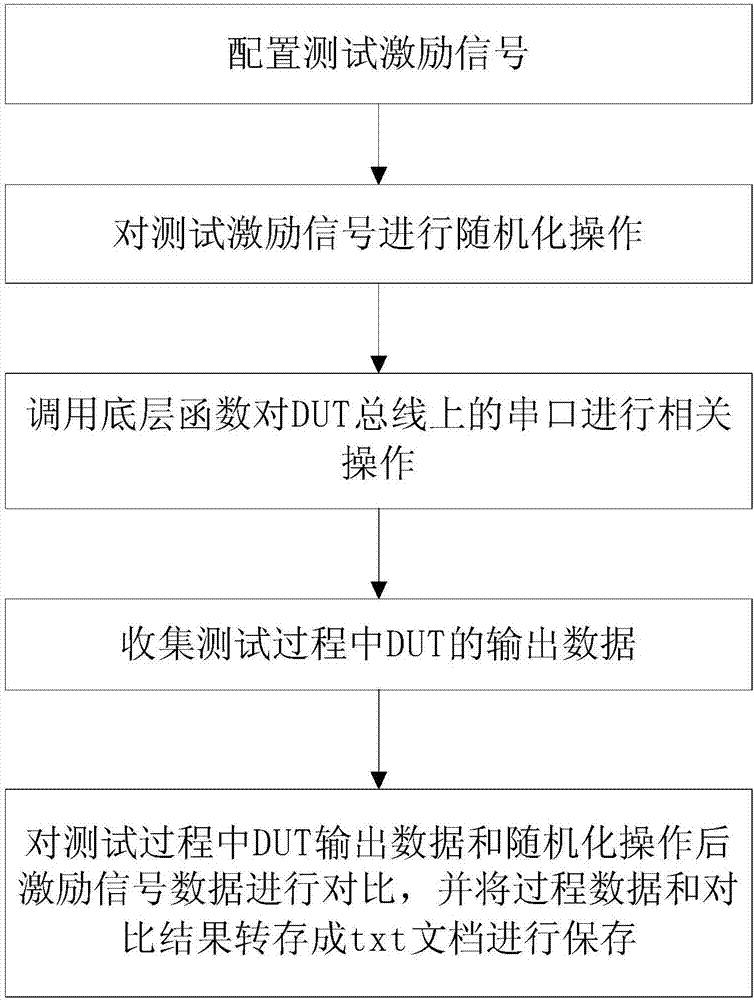

A general verification method and general verification technology, applied in the field of chip design, can solve problems such as difficult to simulate IP working environment, difficult to simulate continuous and complete actions, and lack of portability, so as to achieve reusability and improve efficiency As well as the accuracy of the assessment, the effect of saving verification time and effort

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to clearly illustrate the technical characteristics of the present solution, the present invention will be described in detail below through specific implementations and in conjunction with the accompanying drawings. The following disclosure provides many different embodiments or examples for implementing different structures of the present invention. In order to simplify the disclosure of the present invention, the components and settings of specific examples are described below. In addition, the present invention may repeat reference numbers and / or letters in different examples. This repetition is for the purpose of simplification and clarity, and does not in itself indicate the relationship between the various embodiments and / or settings discussed. It should be noted that the components illustrated in the drawings are not necessarily drawn to scale. The present invention omits descriptions of well-known components and processing techniques and processes to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More