Peripheral circuit structure of array substrate

A peripheral circuit and array substrate technology, applied in the field of peripheral circuit structure, can solve serious problems, adverse effects of HVA process, RC delay, etc., to achieve the effect of improving yield, improving curing effect, and reducing RC load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

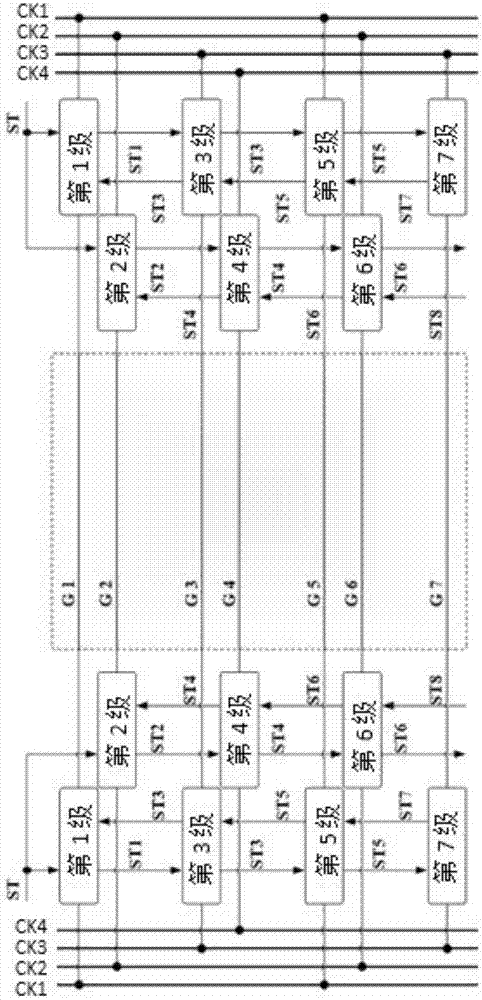

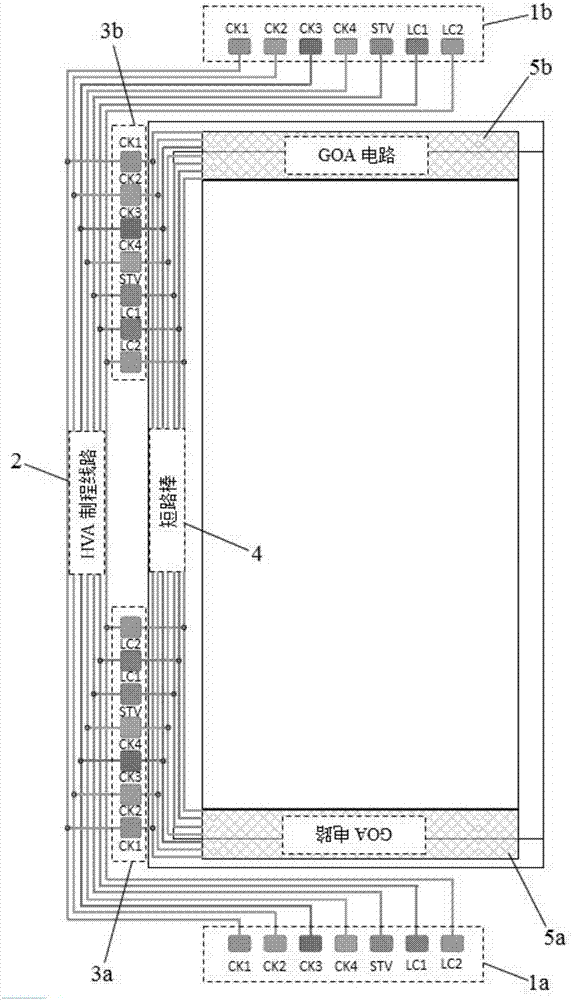

[0038] This embodiment provides a peripheral circuit structure of an array substrate, refer to Figure 4 and Figure 5 , the array substrate 10 includes a display area 11 and a fan-out area 12 located at the edge of the display area 11 , and the peripheral circuit structure is arranged on the fan-out area 12 .

[0039] Specifically, the peripheral circuit structure includes: first GOA circuit 20a and first array test pad 30a electrically connected to each other, second GOA circuit 20b and second array test pad 30b electrically connected to each other, HVA process Line 40. The first array of test pads 30a is connected to the HVA process line 40 through a first connection line 50a, and the second array of test pads 30b is connected to the HVA process line 40 through a second connection line 50b. In this embodiment, the first GOA circuit 20a and the second GOA circuit 20b are respectively located on the first side 11a and the second side 11b opposite to the display area 11, and...

Embodiment 2

[0047] The difference between this embodiment and embodiment 1 is that, refer to Figure 10 and Figure 11 , the circuit breaking point 80 is set on the HVA process line 40, the HVA process line 40 is divided into a first line segment 40a and a second line segment 40b insulated from each other to form the circuit break point 80, the The welding point 81 is arranged above the circuit breaking point 80 , and after the welding process is performed at the welding point 81 , the first line section 40 a and the second line section 40 b are electrically connected to each other. In this embodiment, the first array test pad 30a is electrically connected to the first line segment 40a, and the second array test pad 30b is electrically connected to the second line segment 40b. The specific connection The structure can refer to the embodiment 1 Figure 7 structure shown. Other circuit structures in this embodiment are the same as those in Embodiment 1, and will not be repeated here.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More