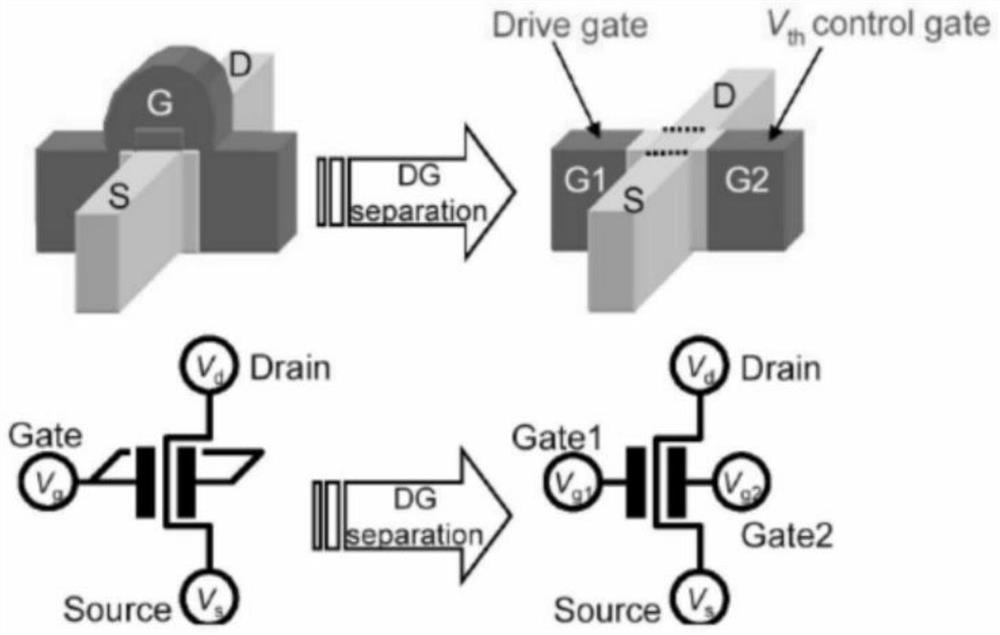

Method and structure for forming a double-gate fin field effect transistor

A field-effect transistor and double-gate technology, which is applied in the field of formation method and structure of double-gate fin field-effect transistors, can solve problems such as the difference between the upper and lower parts of the fin, and high leakage, so as to reduce leakage, improve device performance, and change threshold voltage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The invention provides a double-gate fin field effect transistor and a forming method thereof.

[0054] In the following, the present invention will be described in detail and specifically through specific examples, so as to better understand the present invention, but the following examples do not limit the scope of the present invention.

[0055] Such as Figure 9 As shown in the flow chart of the present invention, a method for forming a double-gate fin field effect transistor in a preferred embodiment of the present invention includes the following steps:

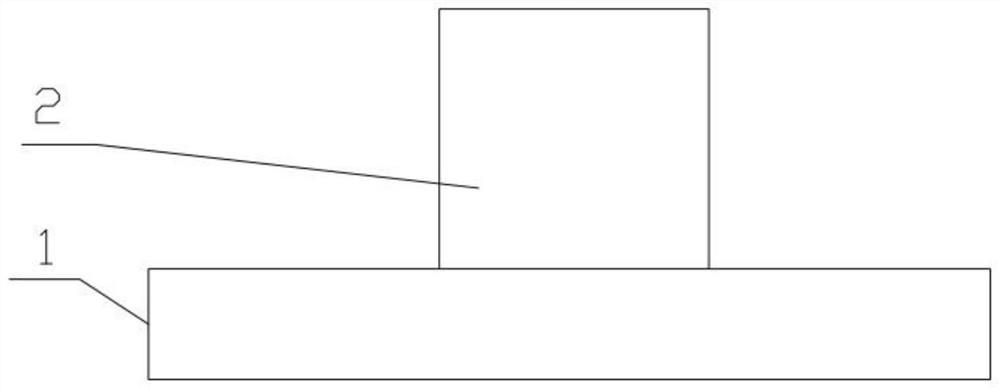

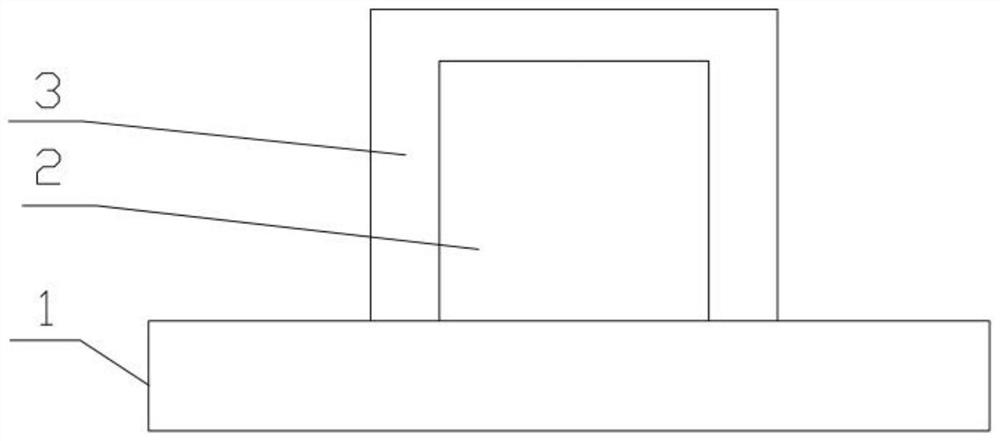

[0056] Such as figure 2 As shown, S1 provides a semiconductor substrate (not shown), on which a buried oxide layer 1 is formed;

[0057] S2 forming a first semiconductor layer (not shown) on the buried oxide layer 1, and patterning the first semiconductor layer to form a semiconductor fin layer 2;

[0058] The method for forming the semiconductor fin layer 2 is to first deposit a first semiconductor layer on ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More