Low power consumption compact digital decimation filter for CMOS image sensor

A technology for extracting filters and image sensors, applied in image communication, color TV components, TV system components, etc., can solve the problems of optimizing the number of transistors and power consumption, so as to reduce the number of transistors and facilitate low-cost Effect of low power consumption design and quantity reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The following will be combined with Figure 1-Figure 7 The present invention is described in detail, and the technical solutions in the embodiments of the present invention are clearly and completely described. Apparently, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

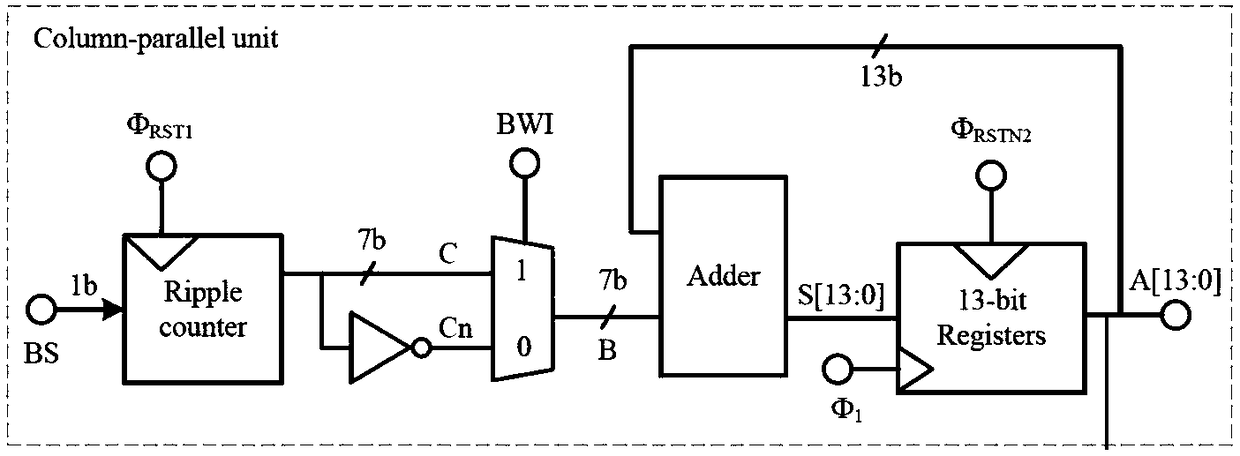

[0031] The present invention provides a kind of low power consumption compact digital decimation filter for CMOS image sensor by improving here, as Figure 2-Figure 7 As shown, it can be implemented as follows;

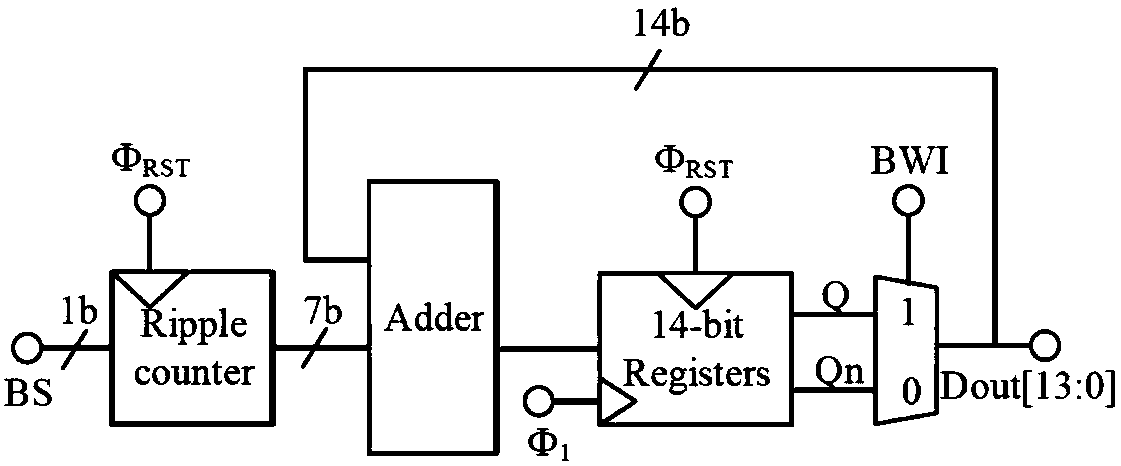

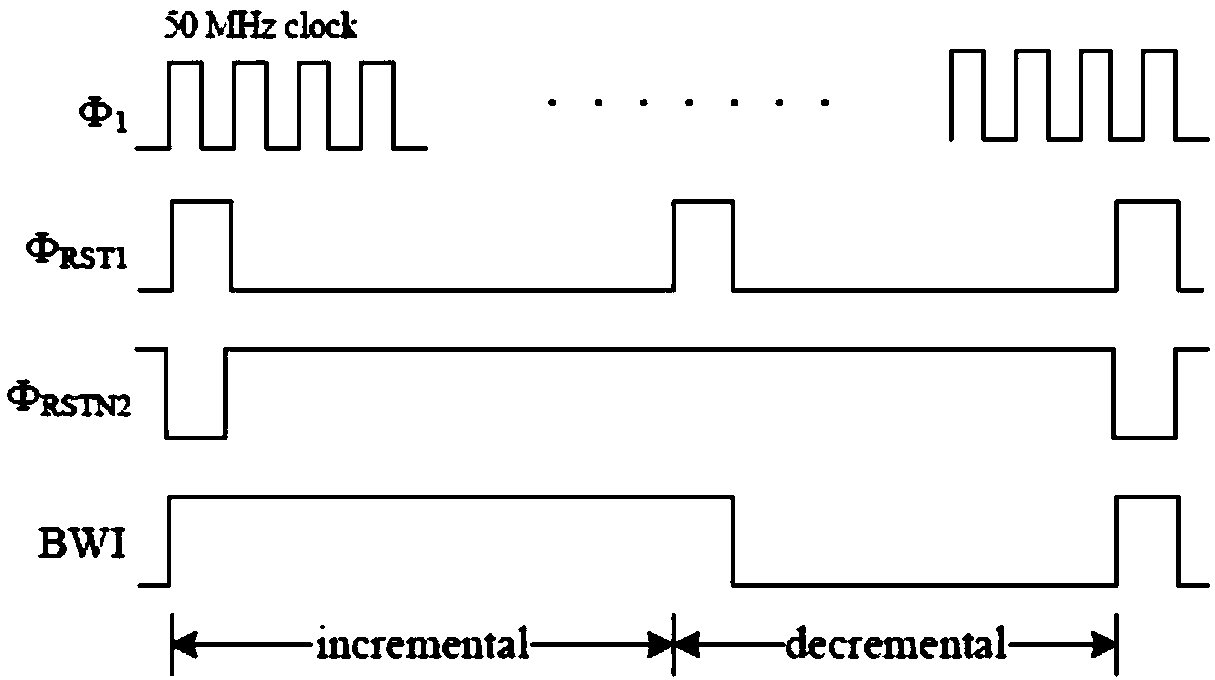

[0032] The overall design of the present invention is as figure 2 As shown, the present invention mainly proposes a special structure, that is, the pre-BWI, which realizes the reduction of the number of transistors and the reducti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More