Method and system for locating winding congestion in chip design

A chip design and winding technology, applied in CAD circuit design, calculation, special data processing applications, etc., can solve problems such as affecting chip function, delaying chip tape-out, reducing chip competitiveness, etc., to improve design efficiency and reduce code. Effects of modification risk and extensive verification work to ensure physical achievability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The technical solutions of the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings of the present invention.

[0042] The method and system for locating winding congestion in chip design disclosed by the present invention can quickly discover and locate the underlying sub-module in the chip where winding congestion occurs, and is especially suitable for the RTL design stage of the chip.

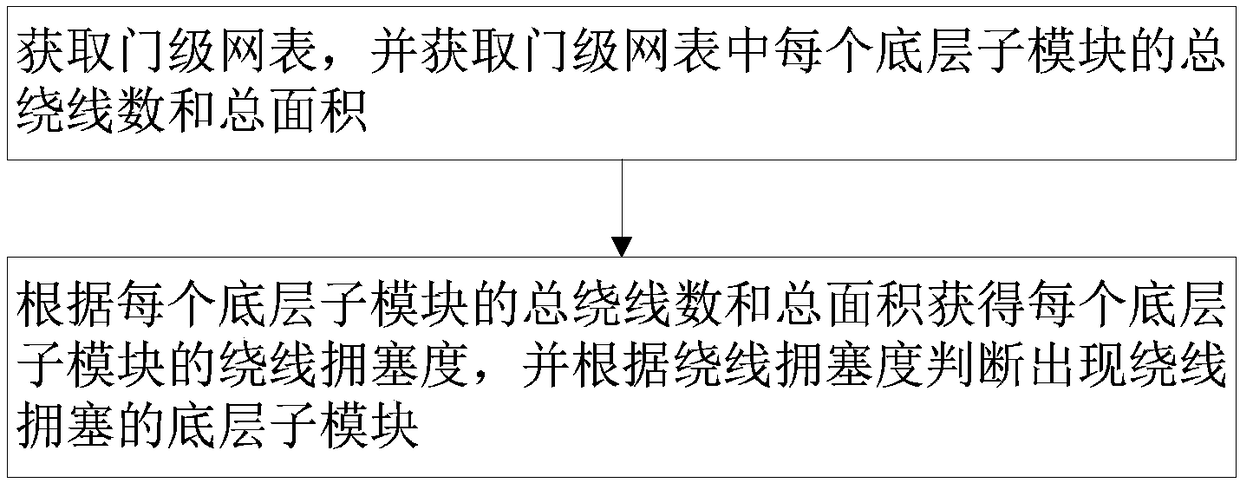

[0043] Such as figure 1 As shown, a method for locating winding congestion in a chip design according to the present invention includes the following steps:

[0044] S1, obtain the gate-level netlist, and obtain the total number of windings and the total area of each underlying sub-module in the gate-level netlist;

[0045] Specifically, the gate-level netlist can be obtained through the logic synthesis tool Design Complier, which converts the circuit described in the RTL (Register Transfer Level, register...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More