LED (light-emitting diode) chip and preparation method thereof

A technology of LED chip and epitaxial layer, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of poor adhesion of N-type epitaxial layer, reduce luminous intensity and efficiency, and affect the firmness of wafer bonding, etc., to achieve Not easy to peel off, improve luminous intensity and efficiency, low cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

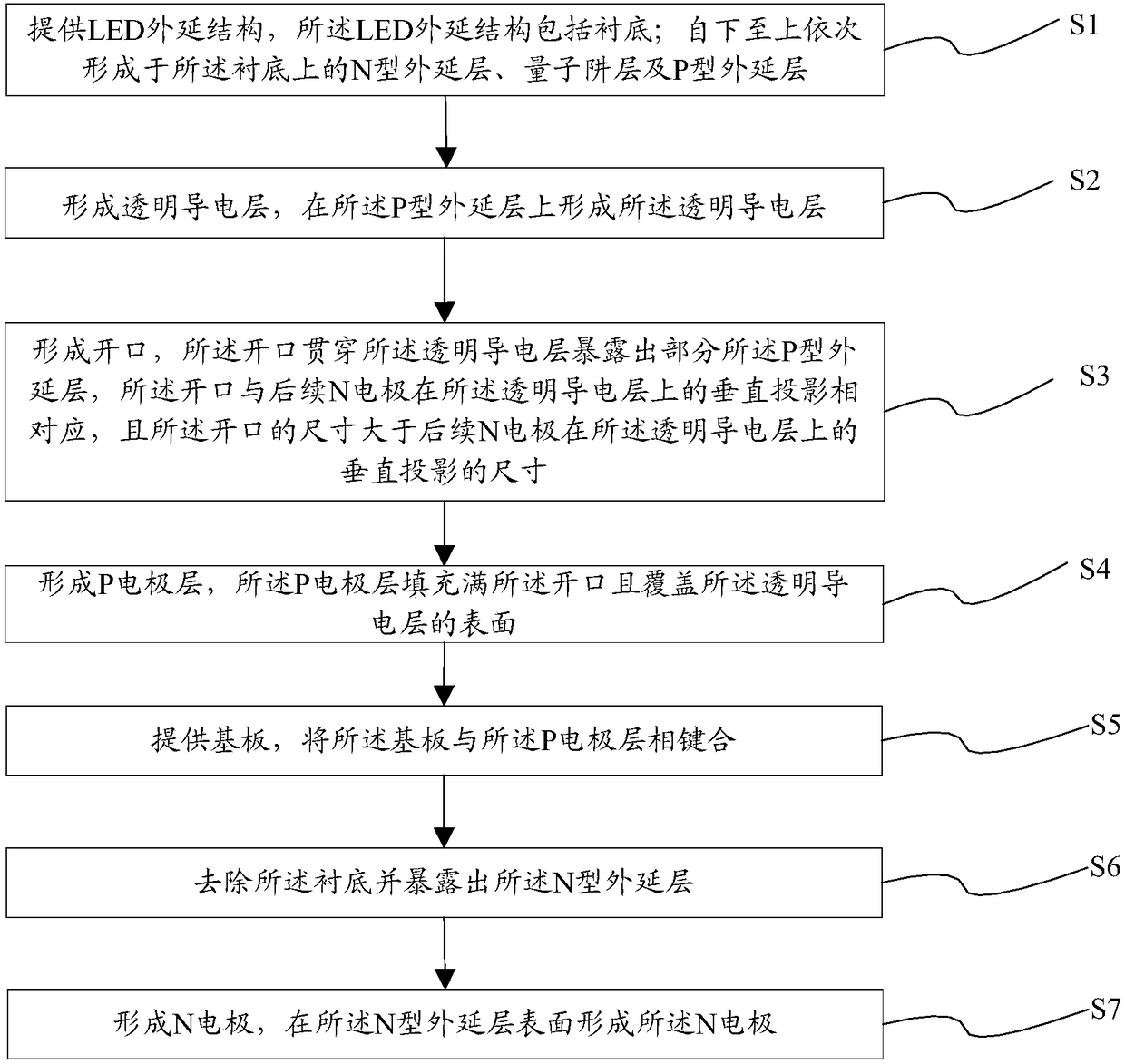

[0040] The core idea of the present invention is that the present invention provides a method for preparing an LED chip, such as figure 1 Shown, described preparation method comprises the following steps:

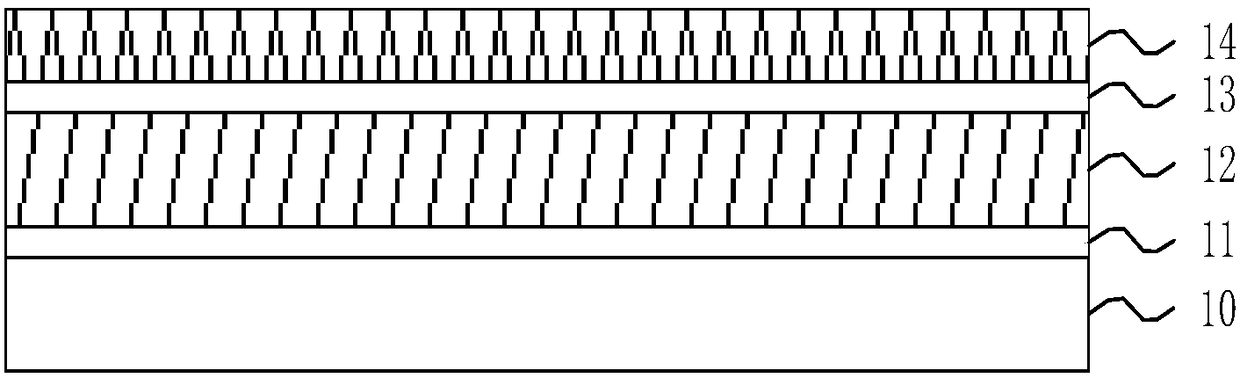

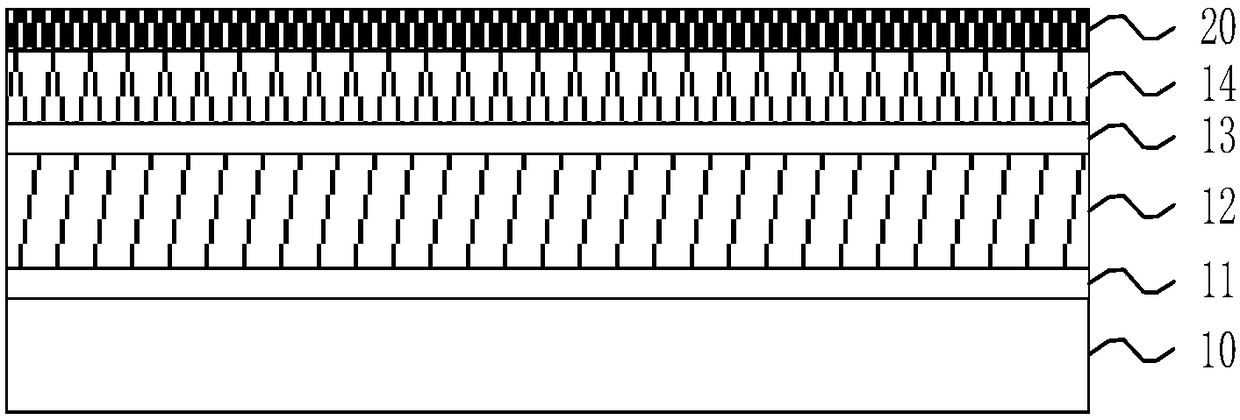

[0041] Step S1, providing an LED epitaxial structure, the LED epitaxial structure includes a substrate; an N-type epitaxial layer, a quantum well layer, and a P-type epitaxial layer are sequentially formed on the substrate from bottom to top;

[0042] Step S2, forming a transparent conductive layer, forming the transparent conductive layer on the P-type epitaxial layer;

[0043] Step S3, forming an opening, the opening penetrates through the transparent conductive layer to expose part of the P-type epitaxial layer, the opening corresponds to the vertical projection of the subsequent N electrode on the transparent conductive layer, and the opening The size is larger than the size of the vertical projection of the subsequent N electrode on the transparent conductive layer;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More