Awaking method and device of FPGA (Field Programmable Gate Array) chip

A chip and wake-up circuit technology, applied to program control devices, program control design, instruments, etc., can solve the problems of system power failure, FPGA chip cannot be processed, FPGA chip cannot be woken up from standby, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

[0033] An embodiment of the present invention provides a wake-up circuit for an FPGA chip. The wake-up circuit can be applied to an electronic device including an FPGA chip, such as a display, a TV, a notebook computer, a smart phone, a smart watch, a tablet computer, and the like.

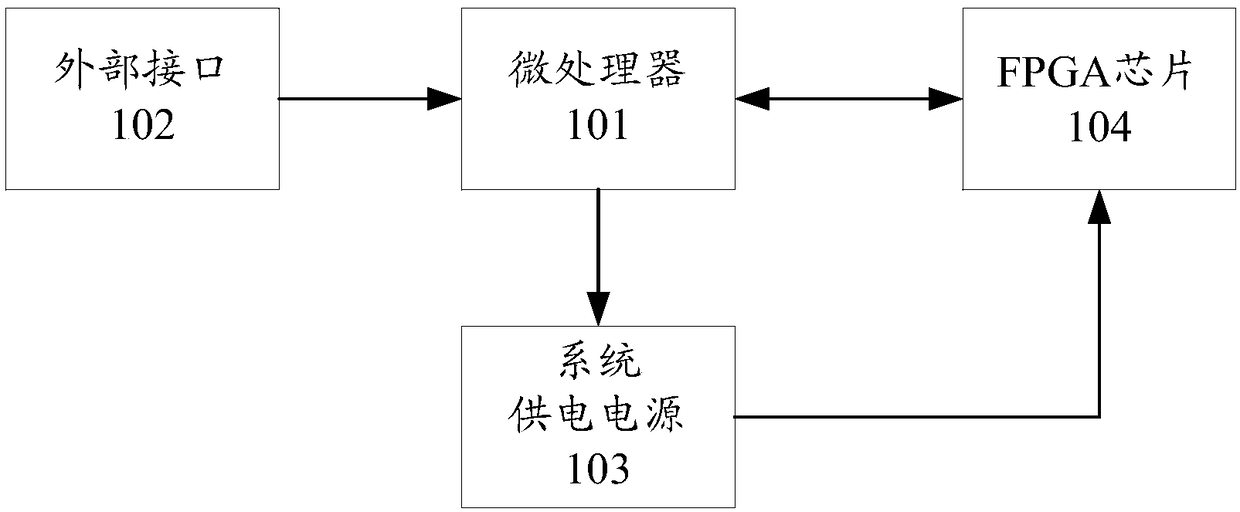

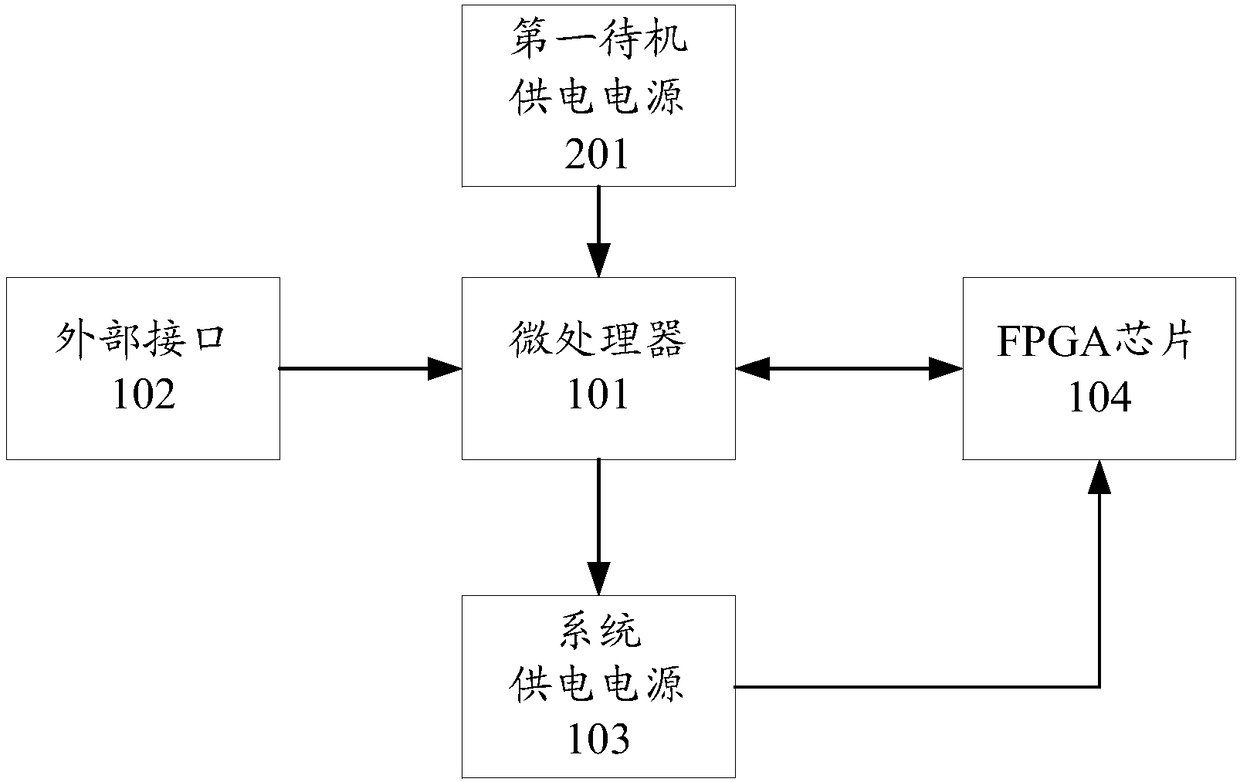

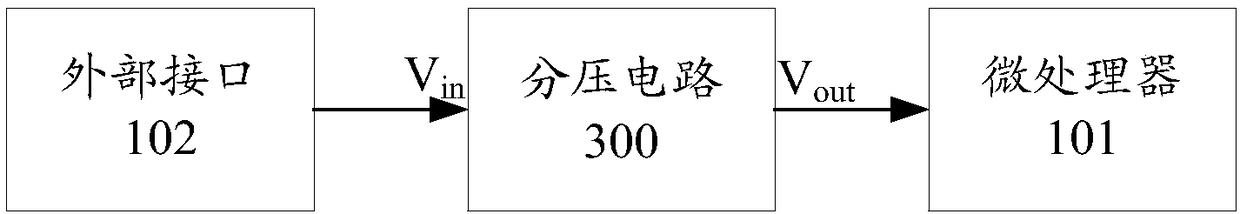

[0034] figure 1 It is a structural representation of the wake-up circuit of the FPGA chip in the embodiment of the present invention Figure 1 , see figure 1 As shown, the wake-up circuit of the FPGA chip can include: a microprocessor 101, an external interface 102, a system power supply 103 and an FPGA chip 104;

[0035]Wherein, the external interface is configured to output the external access signal from the external signal source to the microprocessor; the microprocessor is configured to det...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com