Wafer polishing method

一种晶圆、抛光头的技术,应用在磨削/抛光设备、电气元件、电路等方向,能够解决晶圆厚度不均匀、晶圆平坦度恶化、晶圆厚度均匀性恶化等问题,达到提高平坦度、抑制影响的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

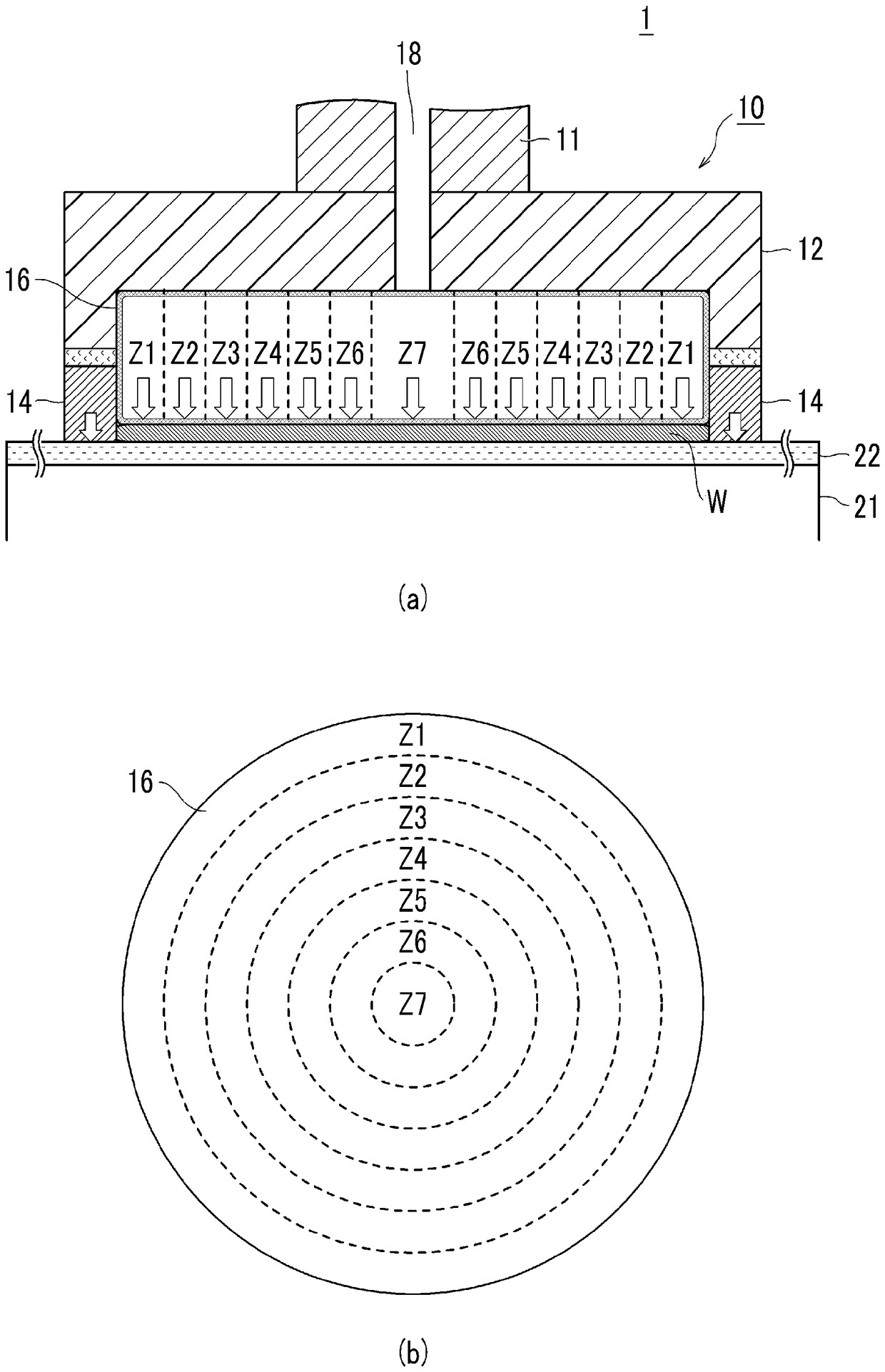

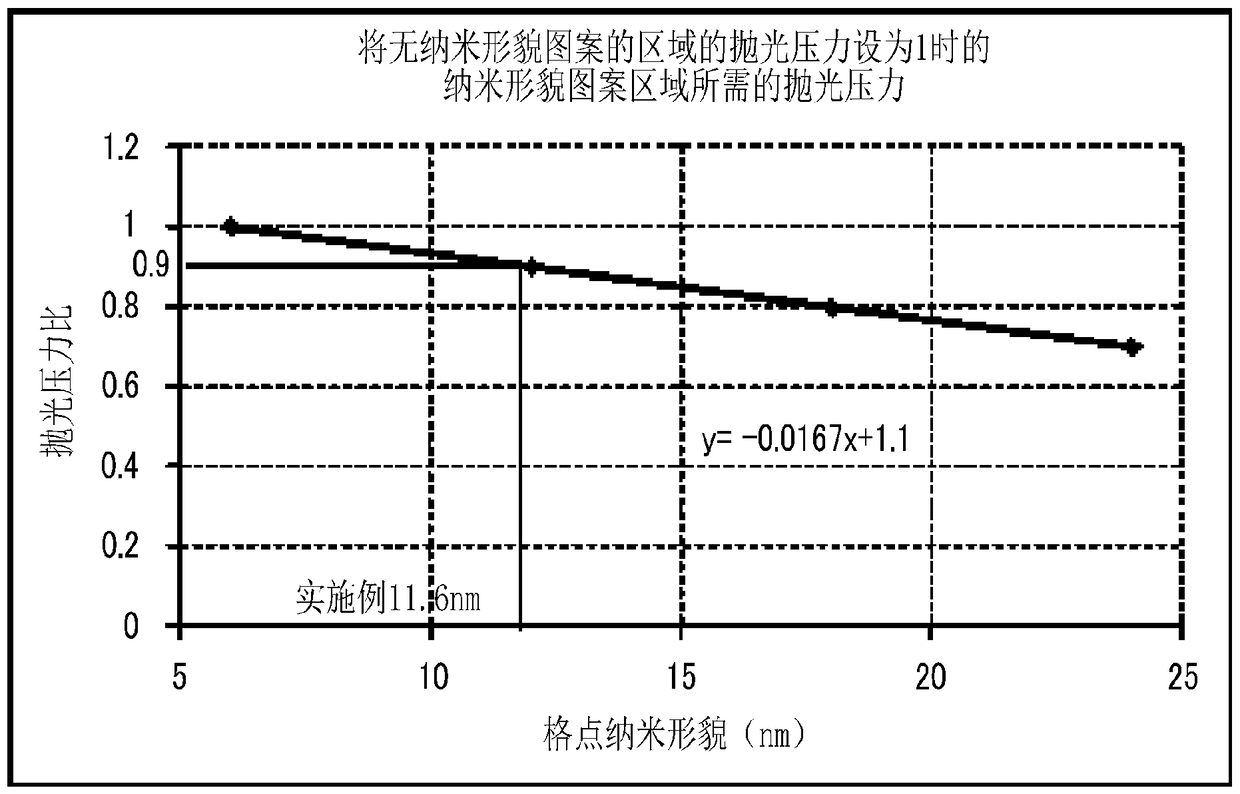

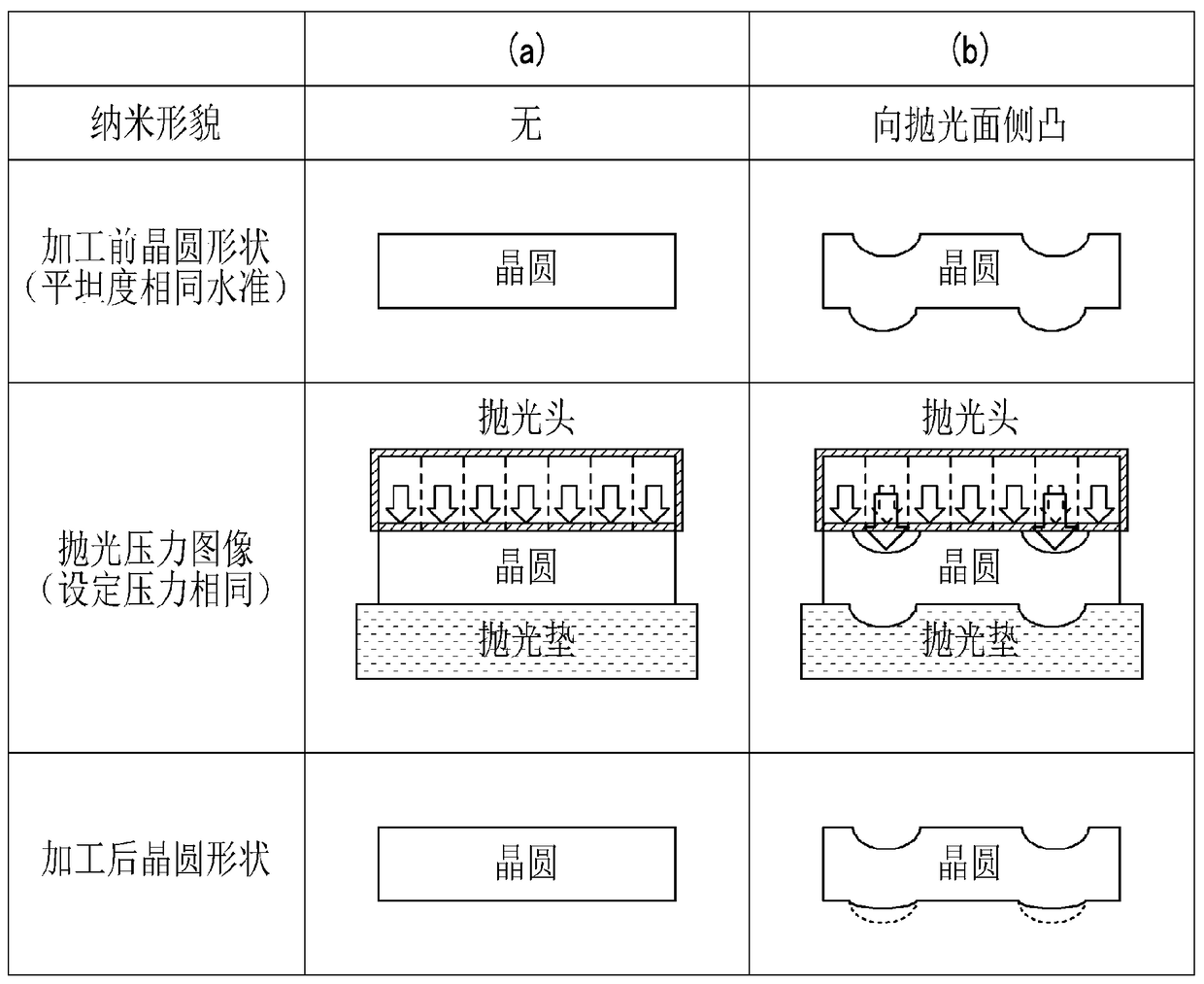

[0050] When performing mirror polishing on a wafer with nano-topography, evaluate the impact of the pressure control method of the polishing head on the flatness of the wafer. In the evaluation test, first, two samples of a 300-mm-diameter silicon single crystal wafer (wafer after double-side polishing) subjected to double-side grinding were prepared, and their nanotopography images were measured. The nanotopography was measured using an optical interferometric flatness / nanotopography measuring device (KLA Tecnor: "WaferSight3"). The grid point size in the wafer plane is 26mm×8mm, and the size of the nano-topography of each grid point is calculated and drawn as a graph.

[0051] Next, one and the other wafer samples were subjected to mirror polishing processing respectively by using the pressure control methods of the conventional and the present invention, to obtain polished wafers of comparative samples and example samples. That is, in the conventional pressure control meth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More