Level shifting structure and manufacturing method thereof

A technology of level shift and drift region, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as ultra-high voltage NDLDMOS reliability problems, difficult process control, large drift region size, etc., and achieves leakage isolation Good effect, easy process control, uniform doping concentration distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

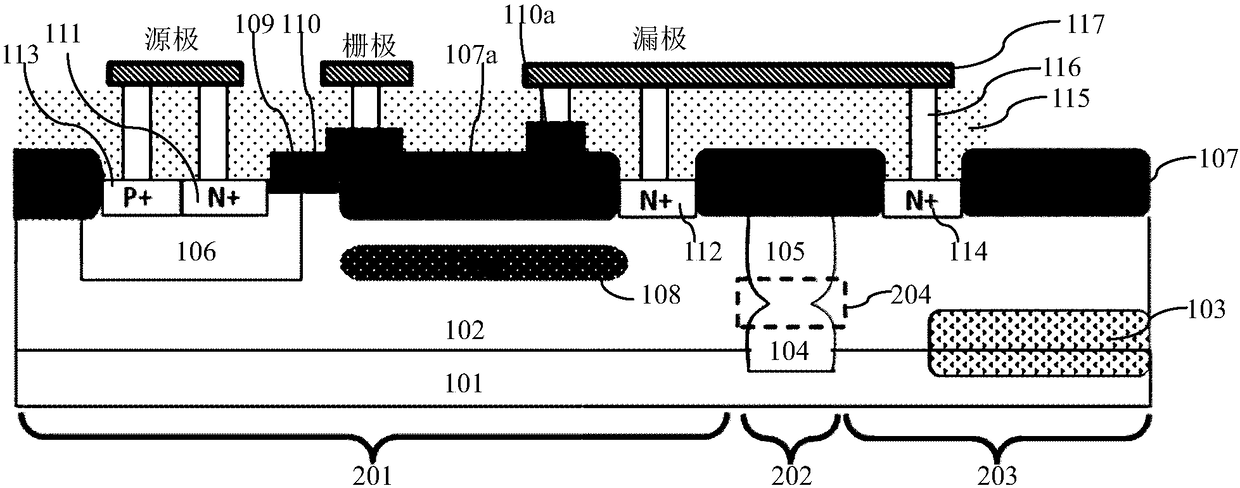

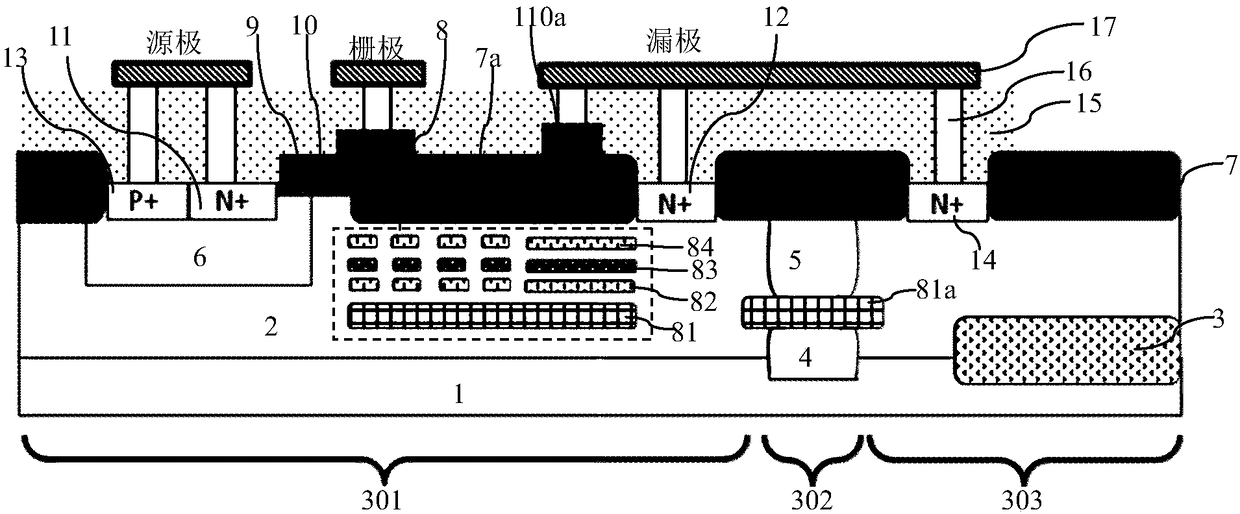

[0057] Such as figure 2 As shown, it is a schematic structural diagram of the level shift structure of the embodiment of the present invention. The level shift structure of the embodiment of the present invention includes: LDMOS301, through isolation region 302 and high side region 303, and the through isolation region 302 displaces the LDMOS301 and between the high side area 303 .

[0058] A first epitaxial layer 2 of a first conductivity type is formed on a surface of a semiconductor substrate of a second conductivity type, such as a silicon substrate 1 .

[0059] The first buried layer 4 with the second conductivity type is formed at the interface of the semiconductor substrate 1 and the first epitaxial layer 2 in the via isolation region 302 .

[0060] The second buried layer 3 with the first conductivity type is formed at the interface of the semiconductor substrate 1 and the first epitaxial layer 2 in the high side region 303 .

[0061] The body region 6 of the LDMOS ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Spacing | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More