Patents

Literature

36results about How to "Uniform doping concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

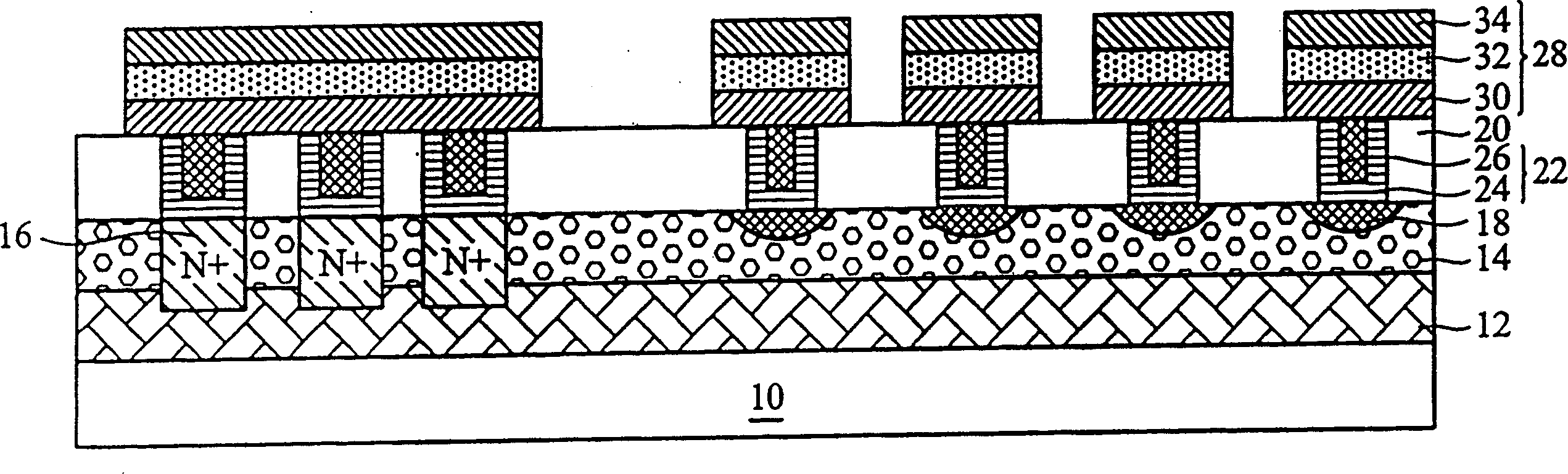

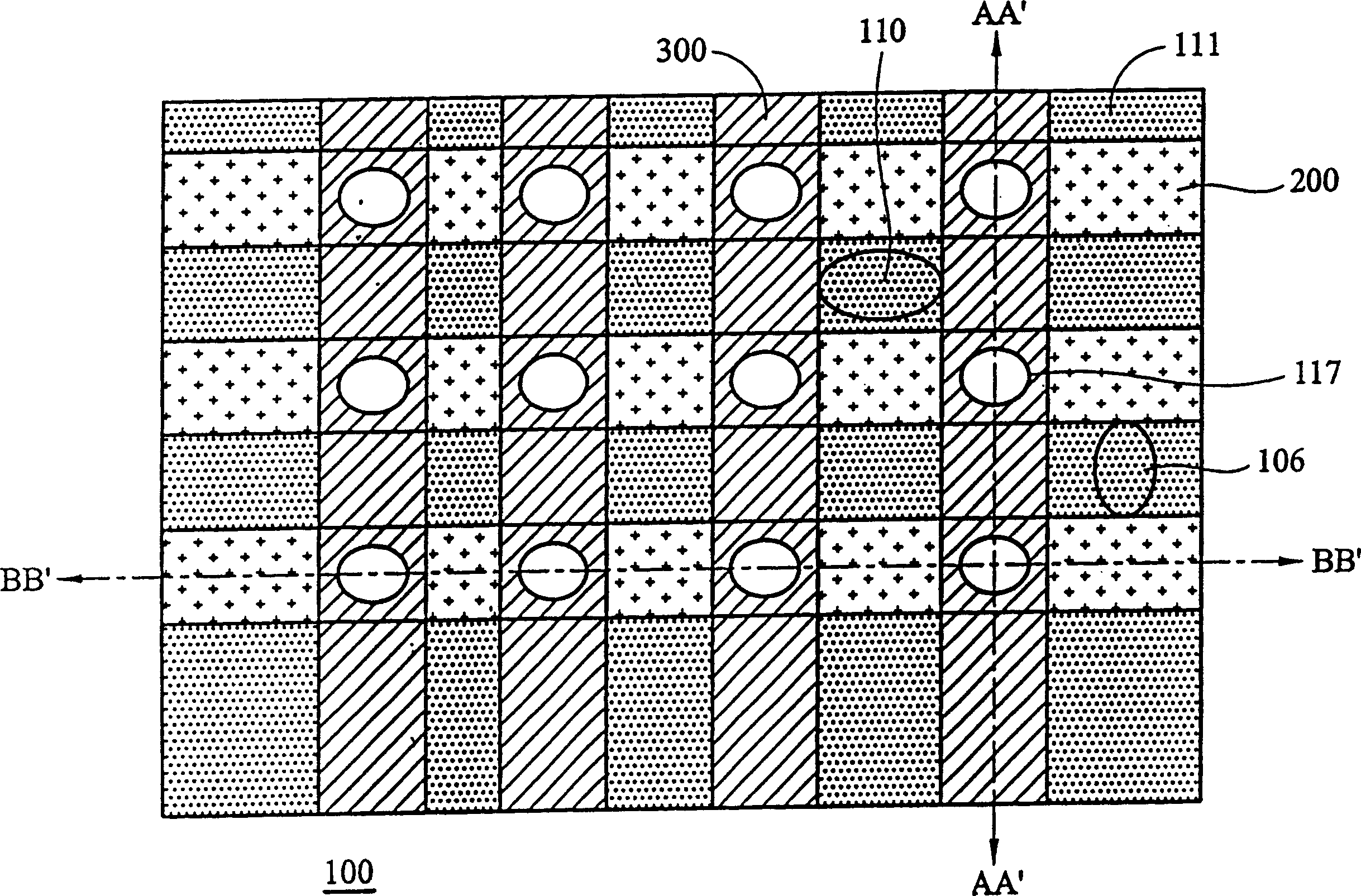

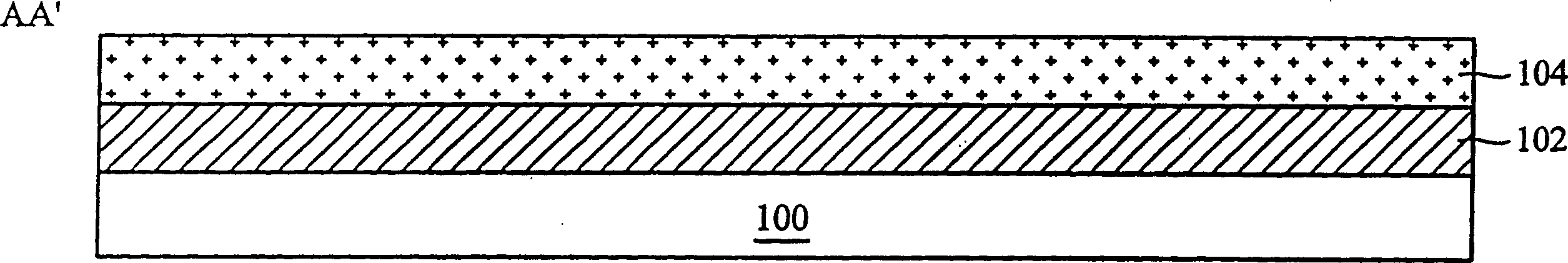

Nanotube Semiconductor Devices

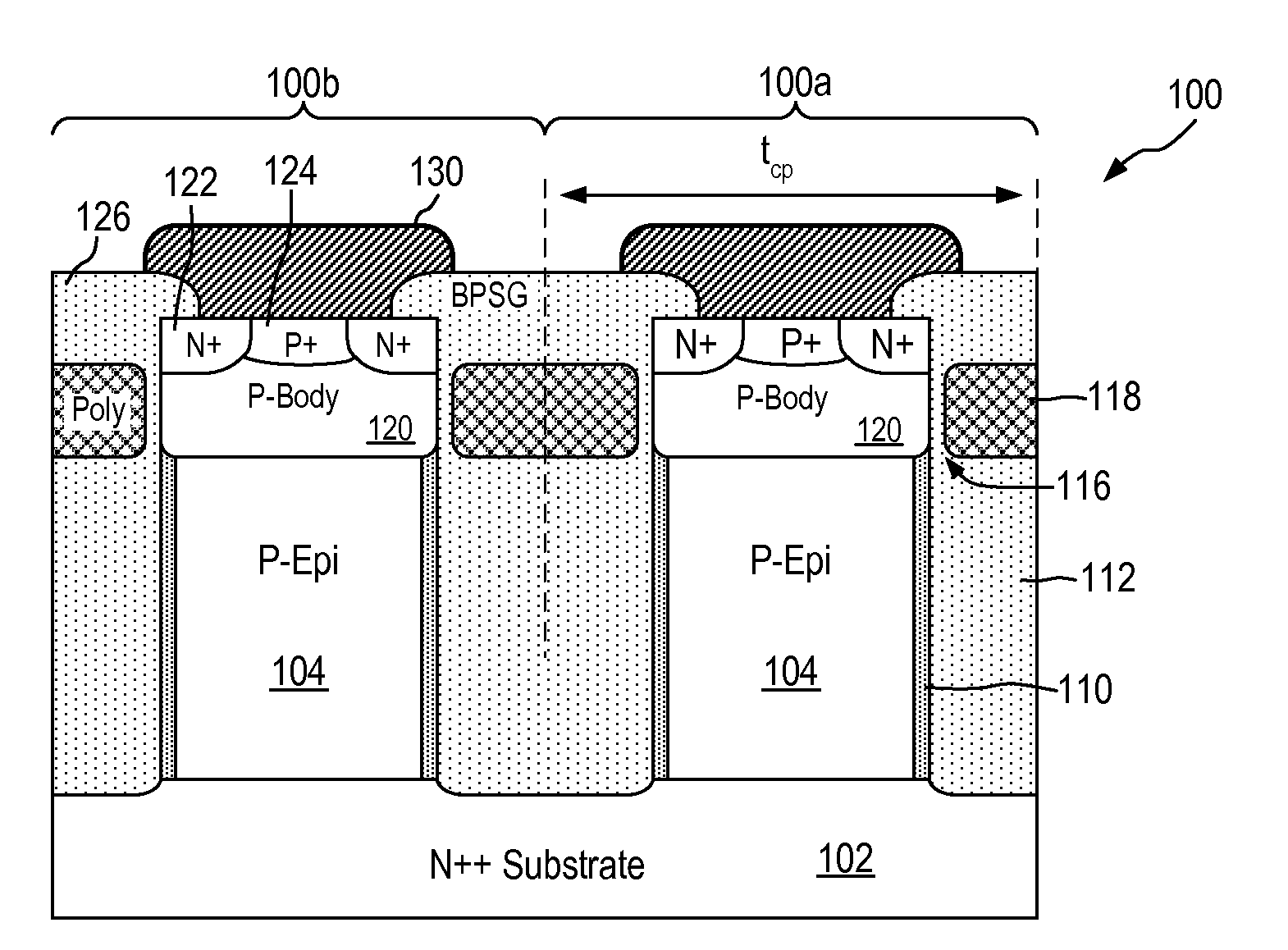

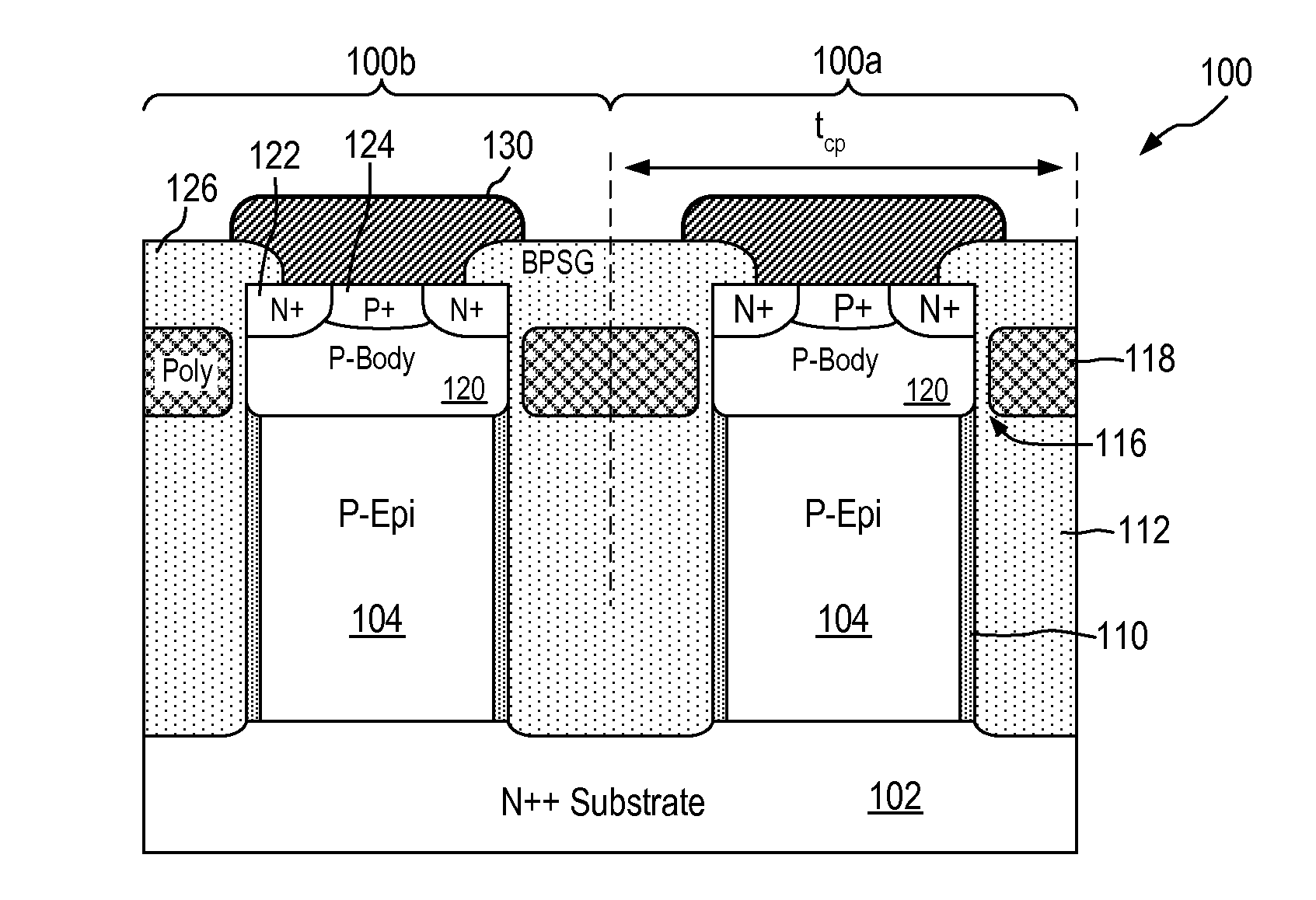

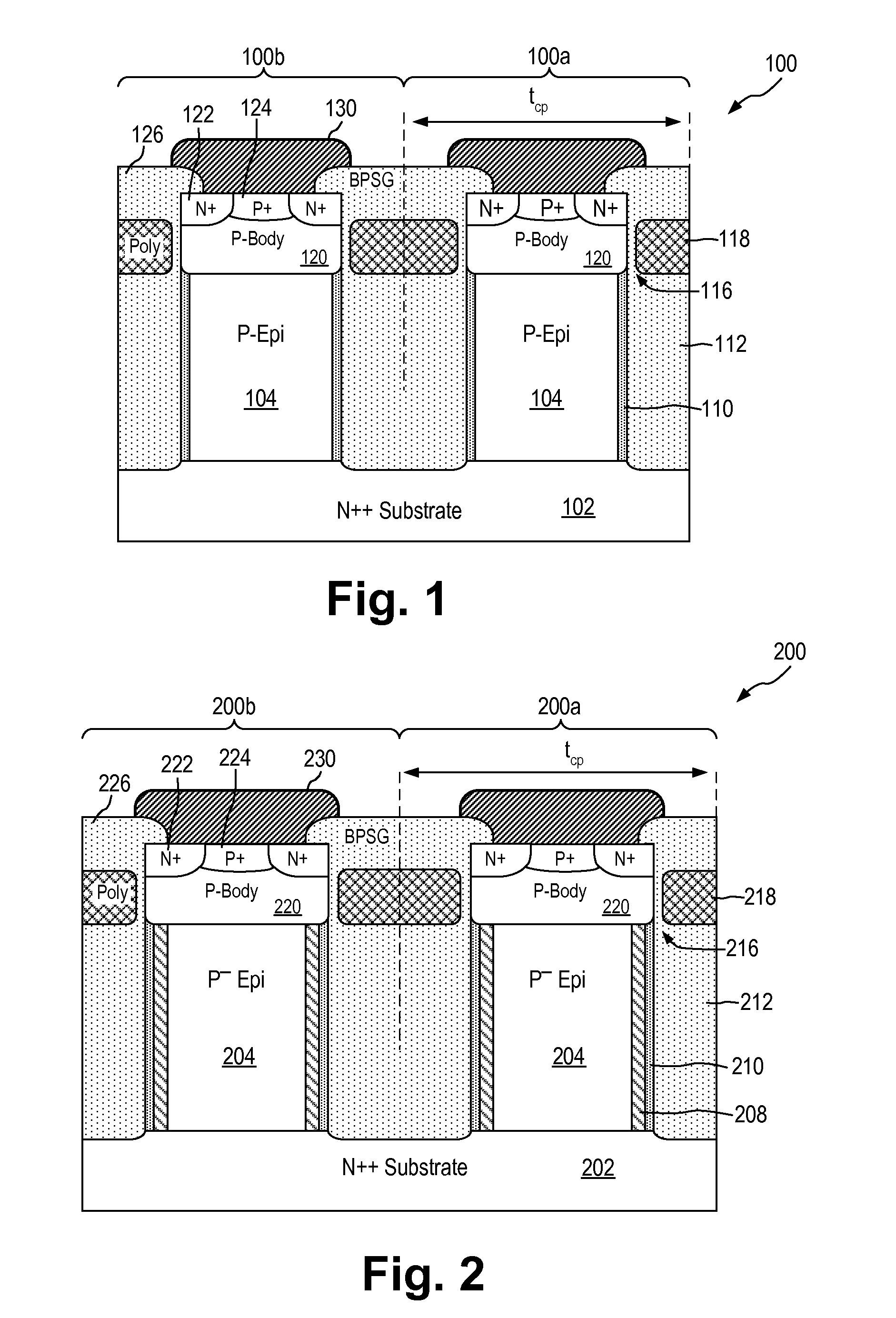

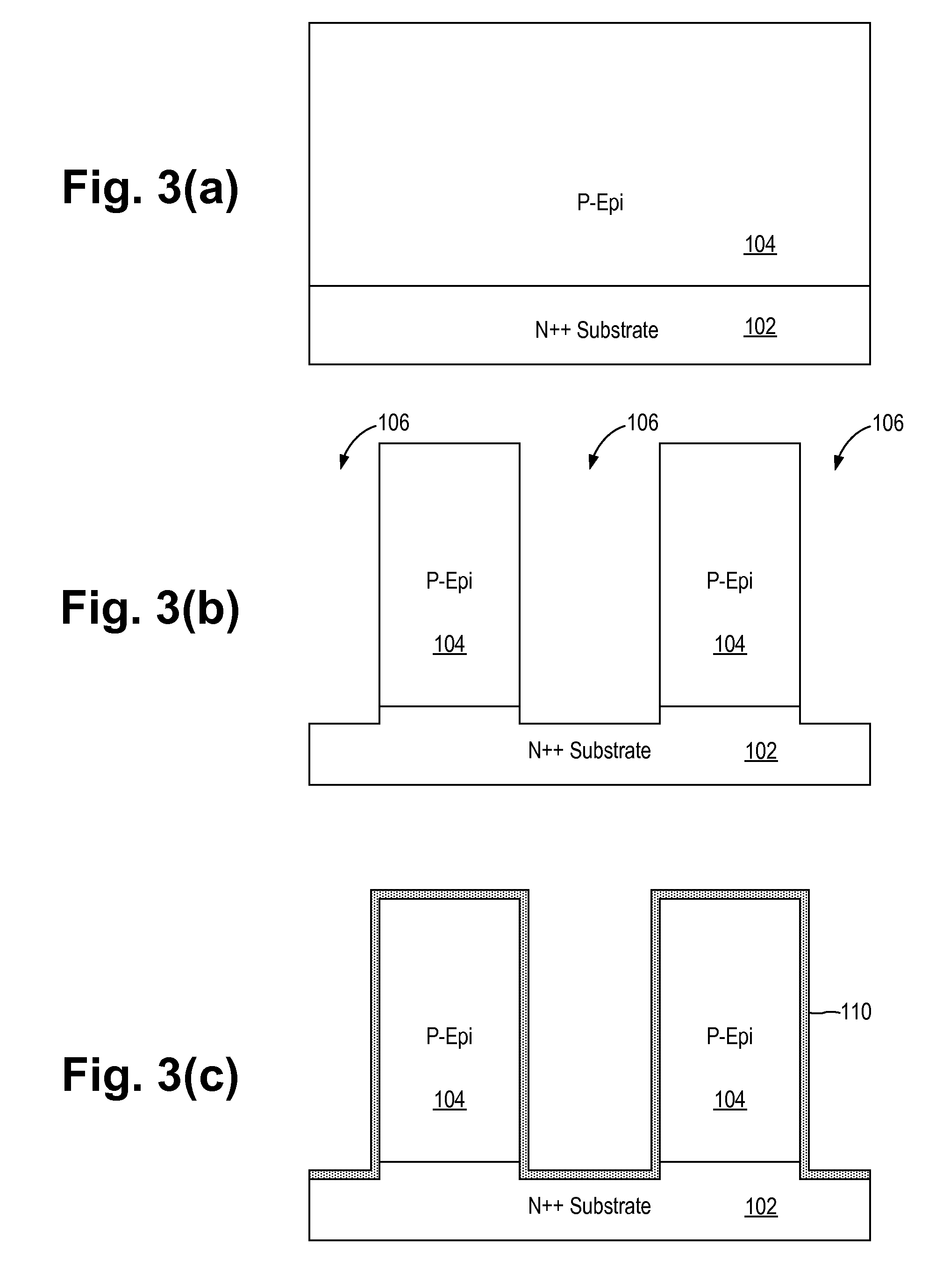

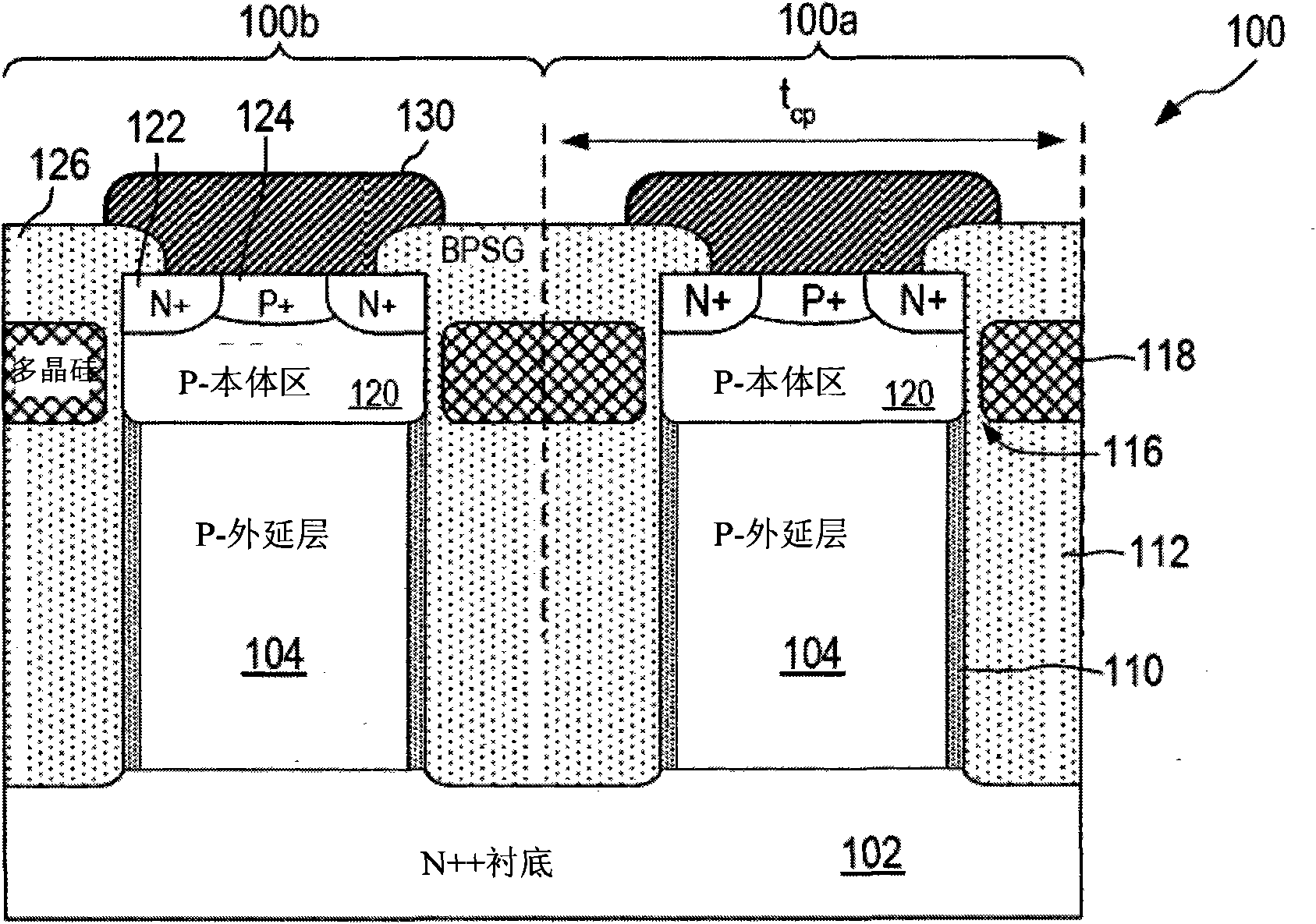

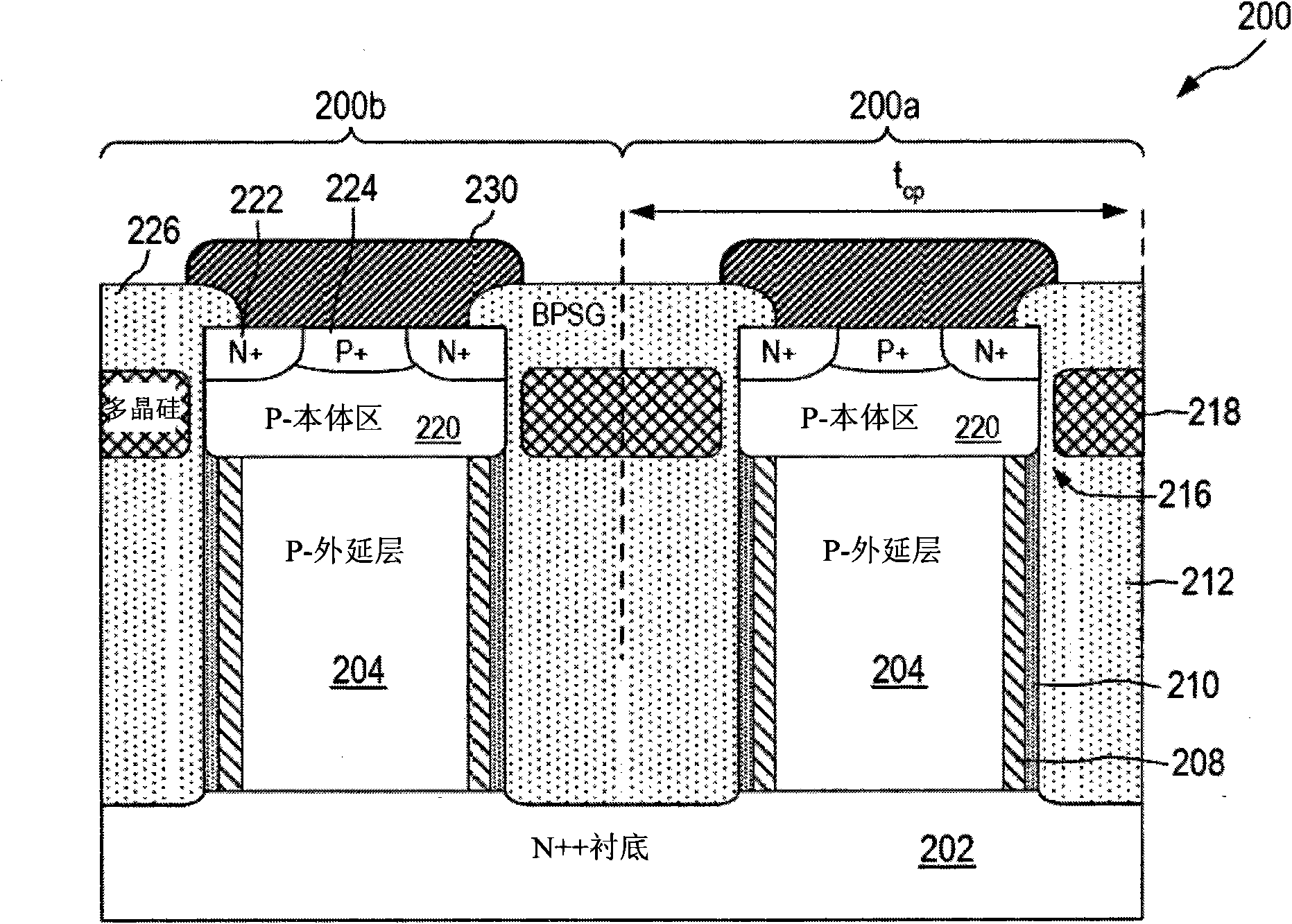

ActiveUS20100314659A1Uniform doping concentrationAchieve charge balanceTransistorSemiconductor/solid-state device manufacturingElectrical conductorNanotube

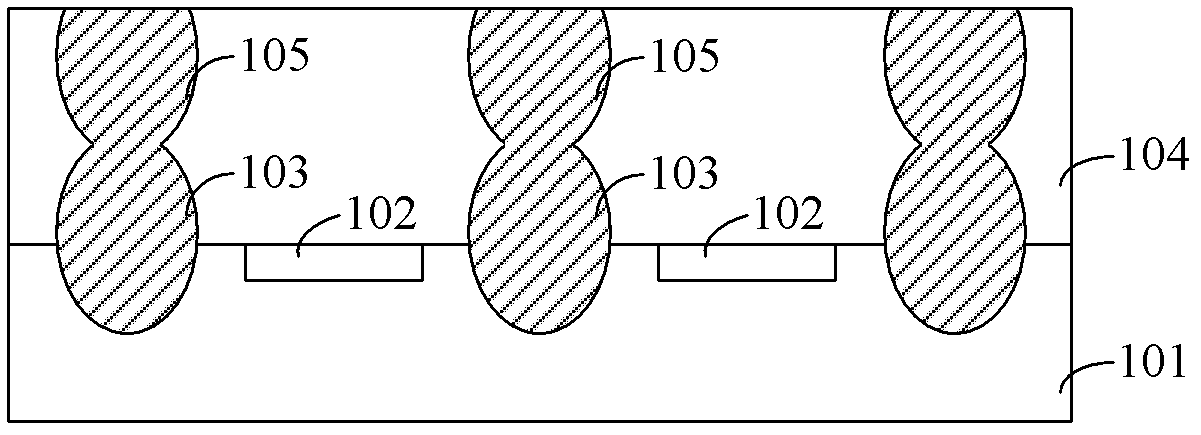

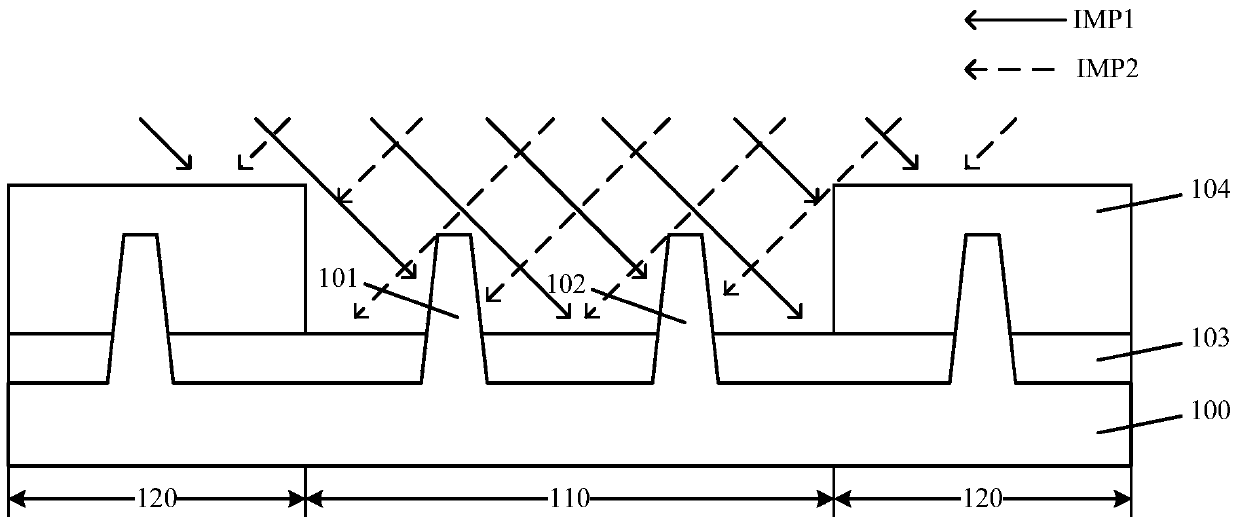

A semiconductor device includes a first semiconductor layer and a second semiconductor layer of opposite conductivity type, a first epitaxial layer of the first conductivity type formed on sidewalls of the trenches, and a second epitaxial layer of the second conductivity type formed on the first epitaxial layer where the second epitaxial layer is electrically connected to the second semiconductor layer. The first epitaxial layer and the second epitaxial layer form parallel doped regions along the sidewalls of the trenches, each having uniform doping concentration. The second epitaxial layer has a first thickness and a first doping concentration and the first epitaxial layer and a mesa of the first semiconductor layer together having a second thickness and a second average doping concentration where the first and second thicknesses and the first doping concentration and second average doping concentrations are selected to achieve charge balance in operation.

Owner:ALPHA & OMEGA SEMICON INC

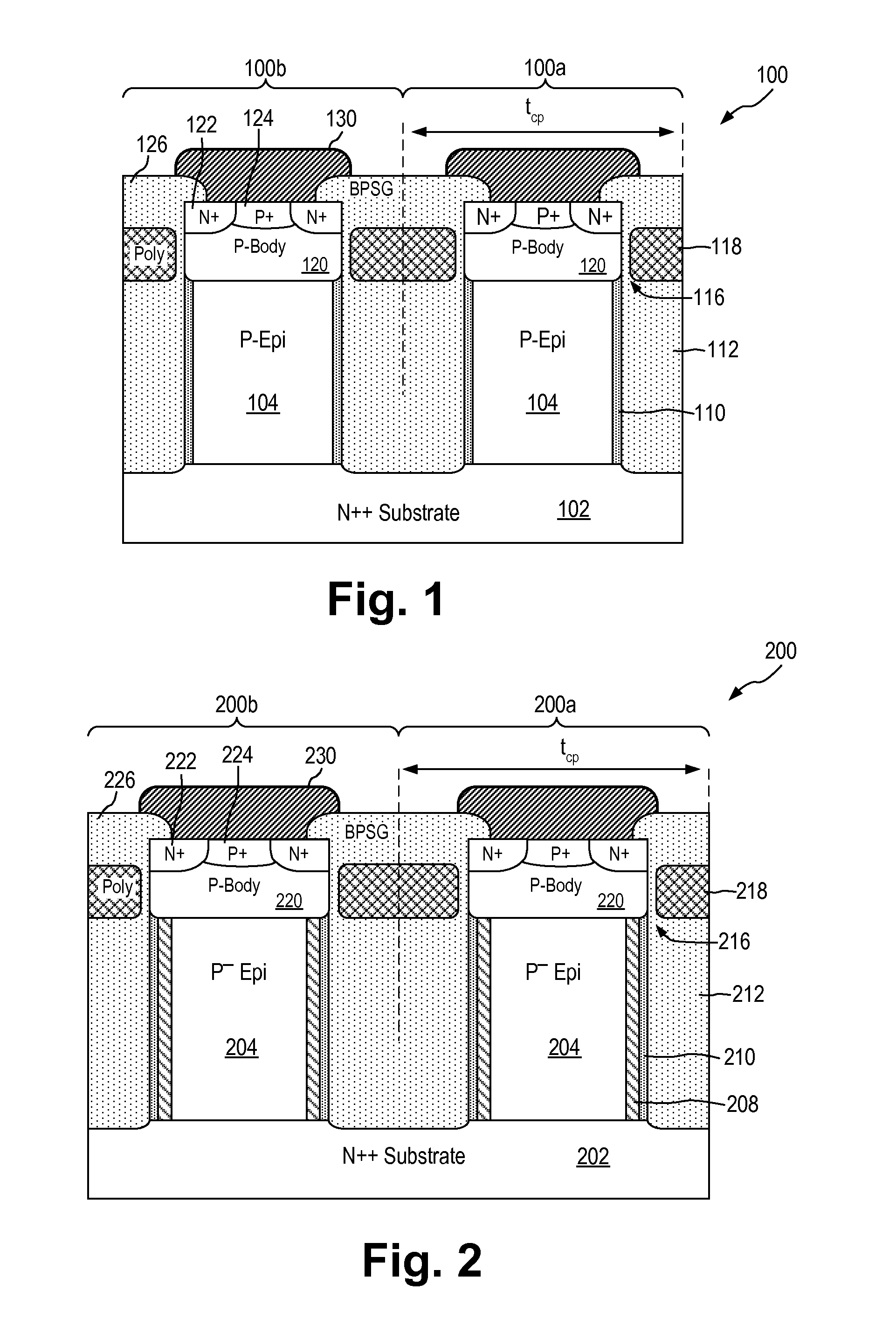

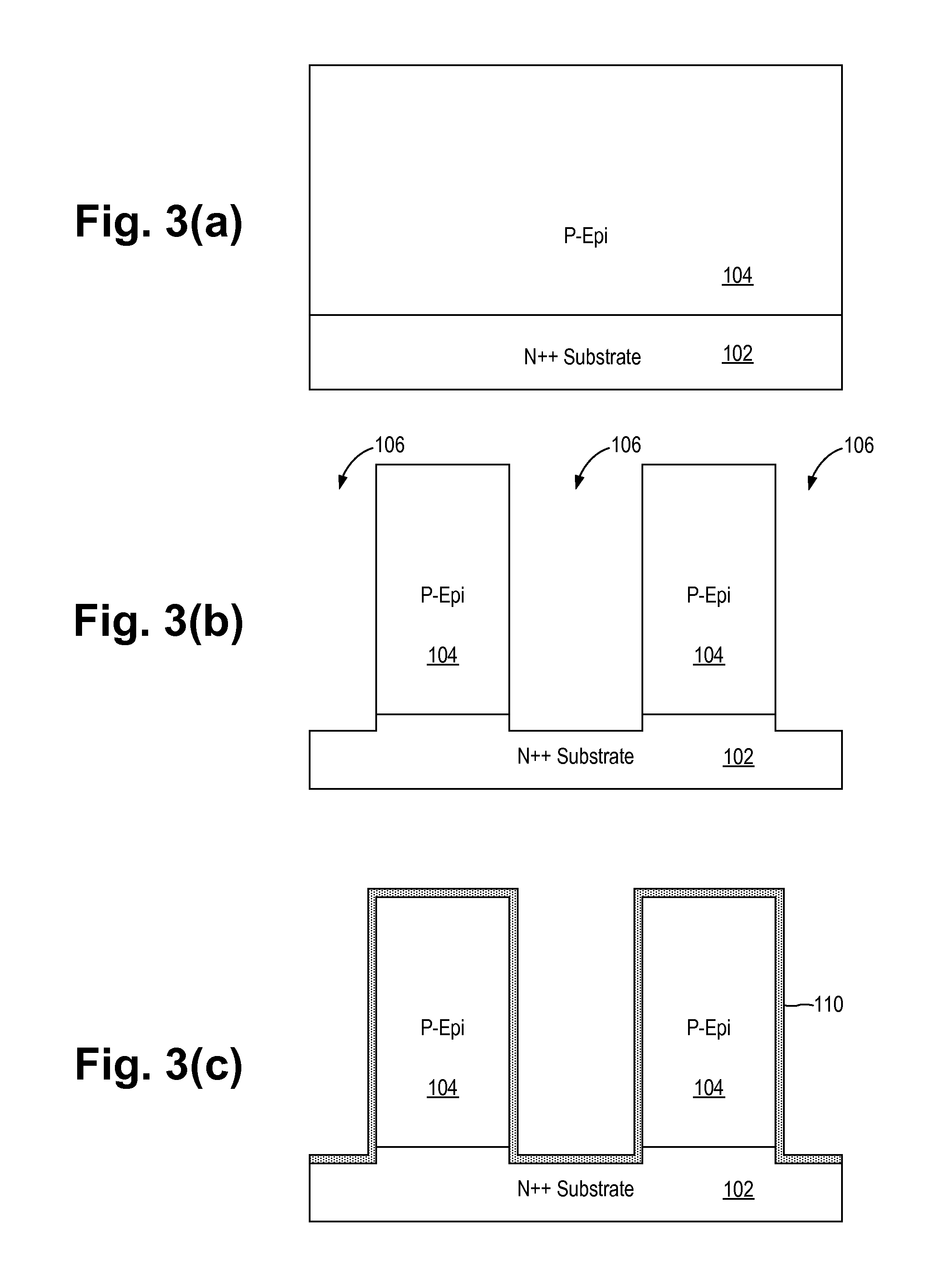

Method for Forming Nanotube Semiconductor Devices

ActiveUS20100317158A1Uniform doping concentrationAchieve charge balanceNanoinformaticsSemiconductor/solid-state device manufacturingPhysicsTrench mosfet

A method for forming a semiconductor device includes forming a nanotube region using a thin epitaxial layer formed on the sidewall of a trench in the semiconductor body. The thin epitaxial layer has uniform doping concentration. In another embodiment, a first thin epitaxial layer of the same conductivity type as the semiconductor body is formed on the sidewall of a trench in the semiconductor body and a second thin epitaxial layer of the opposite conductivity type is formed on the first epitaxial layer. The first and second epitaxial layers have uniform doping concentration. The thickness and doping concentrations of the first and second epitaxial layers and the semiconductor body are selected to achieve charge balance. In one embodiment, the semiconductor body is a lightly doped P-type substrate. A vertical trench MOSFET, an IGBT, a Schottky diode and a P-N junction diode can be formed using the same N-Epi / P-Epi nanotube structure.

Owner:ALPHA & OMEGA SEMICON INC

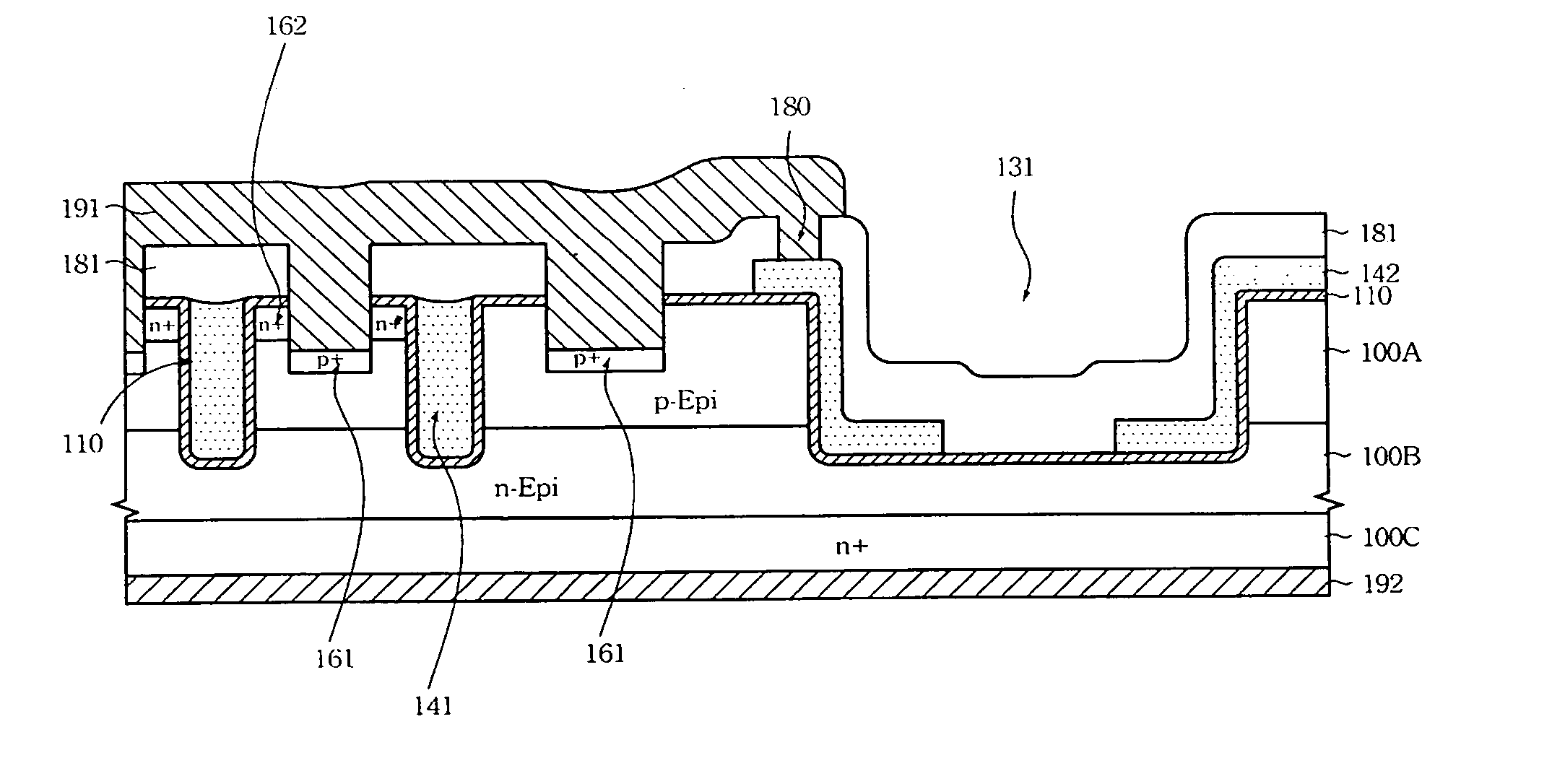

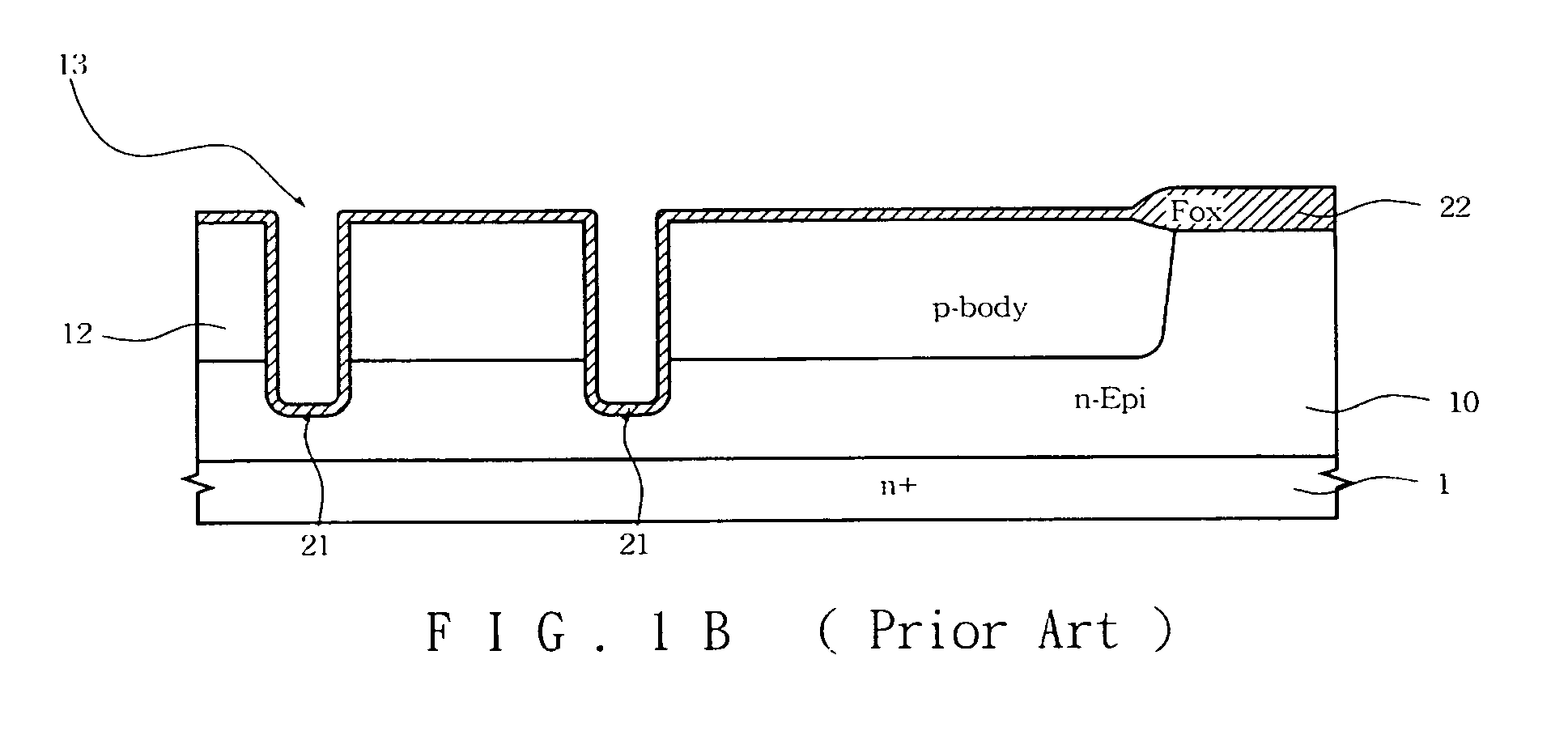

Termination structure of DMOS device

ActiveUS7087958B2Prevents the electric field crowdingUniform doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETIsolation layer

In one embodiment of the invention, a semiconductor device set includes at least one trench-typed MOSFET and a trench-typed termination structure. The trench-typed MOSFET has a trench profile and includes a gate oxide layer in the trench profile, and a polysilicon layer on the gate oxide layer. The trench-typed termination structure has a trench profile and includes an oxide layer in the trench profile. A termination polysilicon layer with discrete features separates the termination polysilicon layer. An isolation layer covers the termination polysilicon layer and filling the discrete features. The trench-typed MOSFET and the trench-typed termination structure may be formed on a DMOS device including an N+ silicon substrate, an N epitaxial layer on the N+ silicon substrate, and a P epitaxial layer on the N epitaxial layer. The trench profiles of the trench-typed MOSFET and of the trench-typed termination structure may penetrate through the P epitaxial layer into the N epitaxial layer.

Owner:PROMOS TECH INC

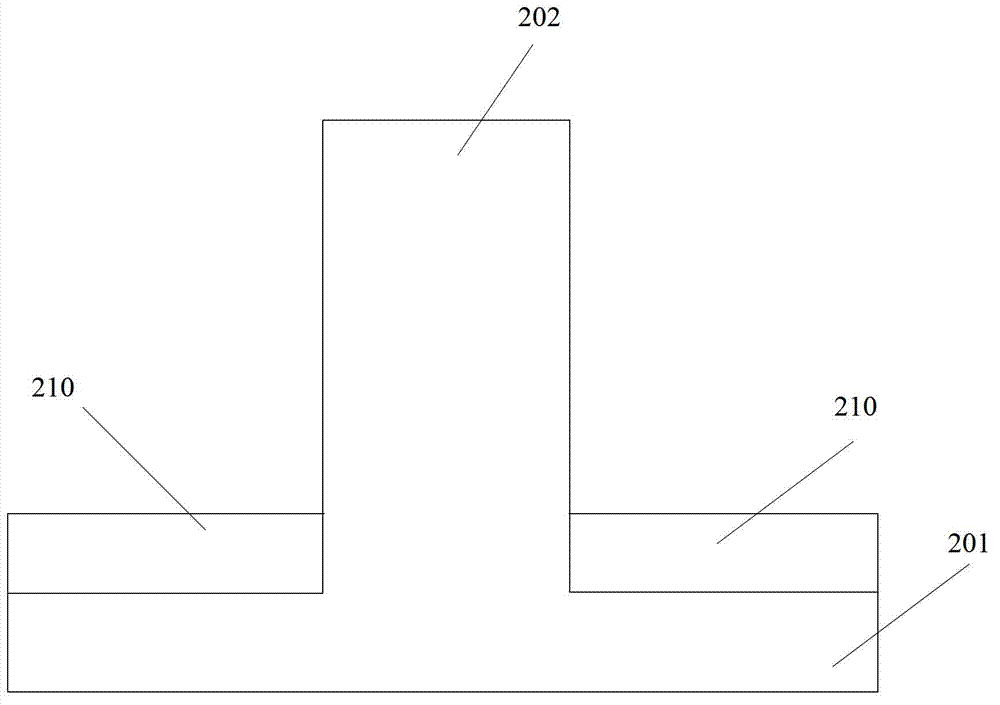

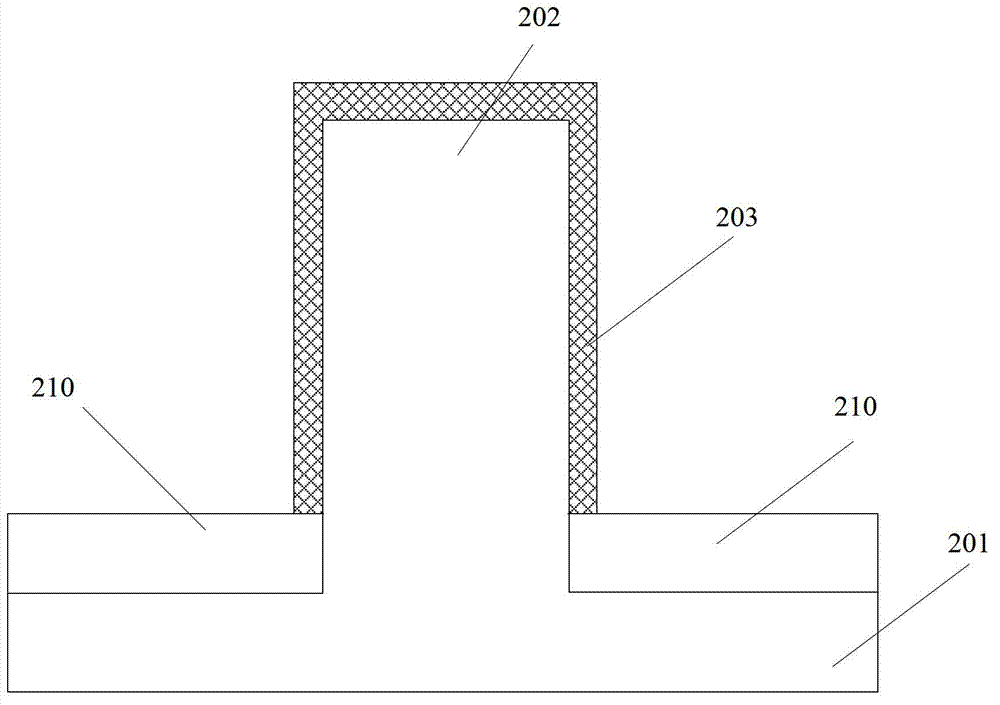

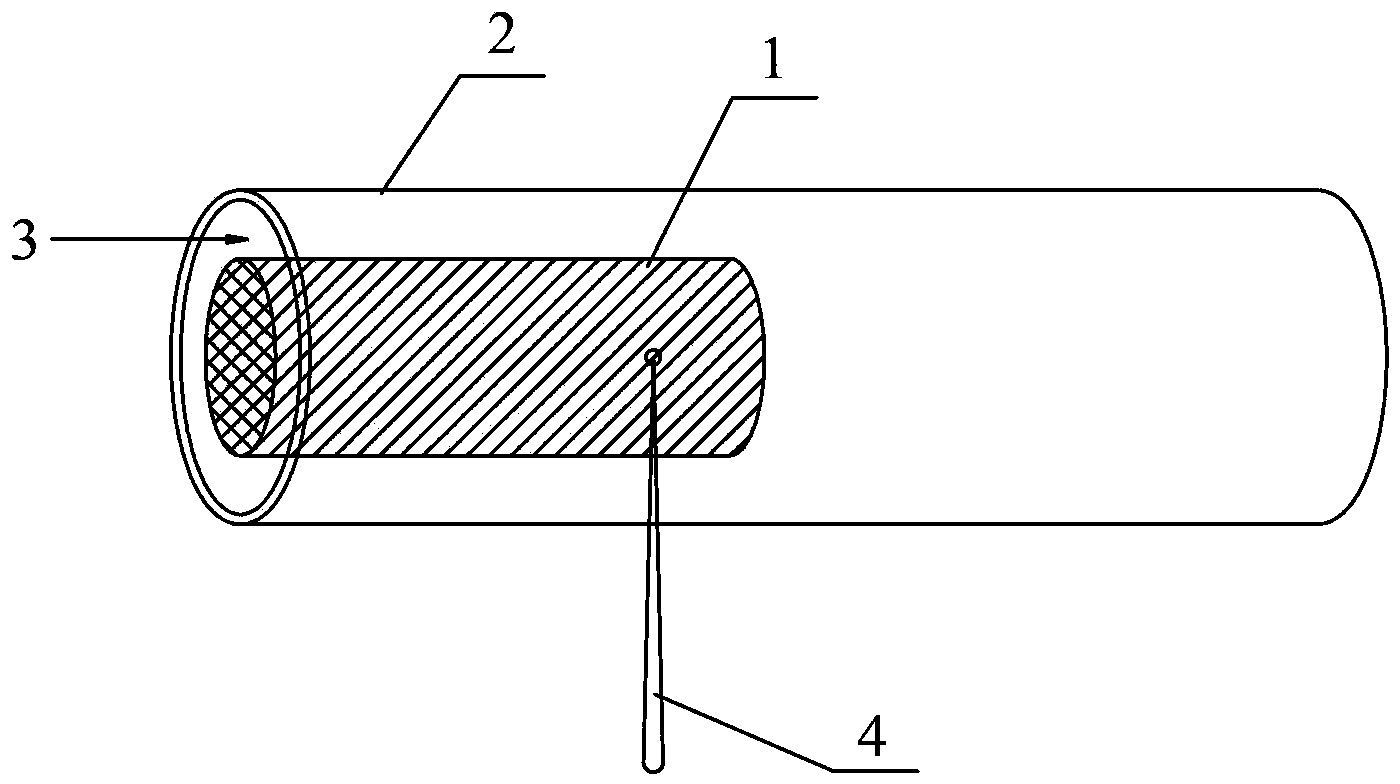

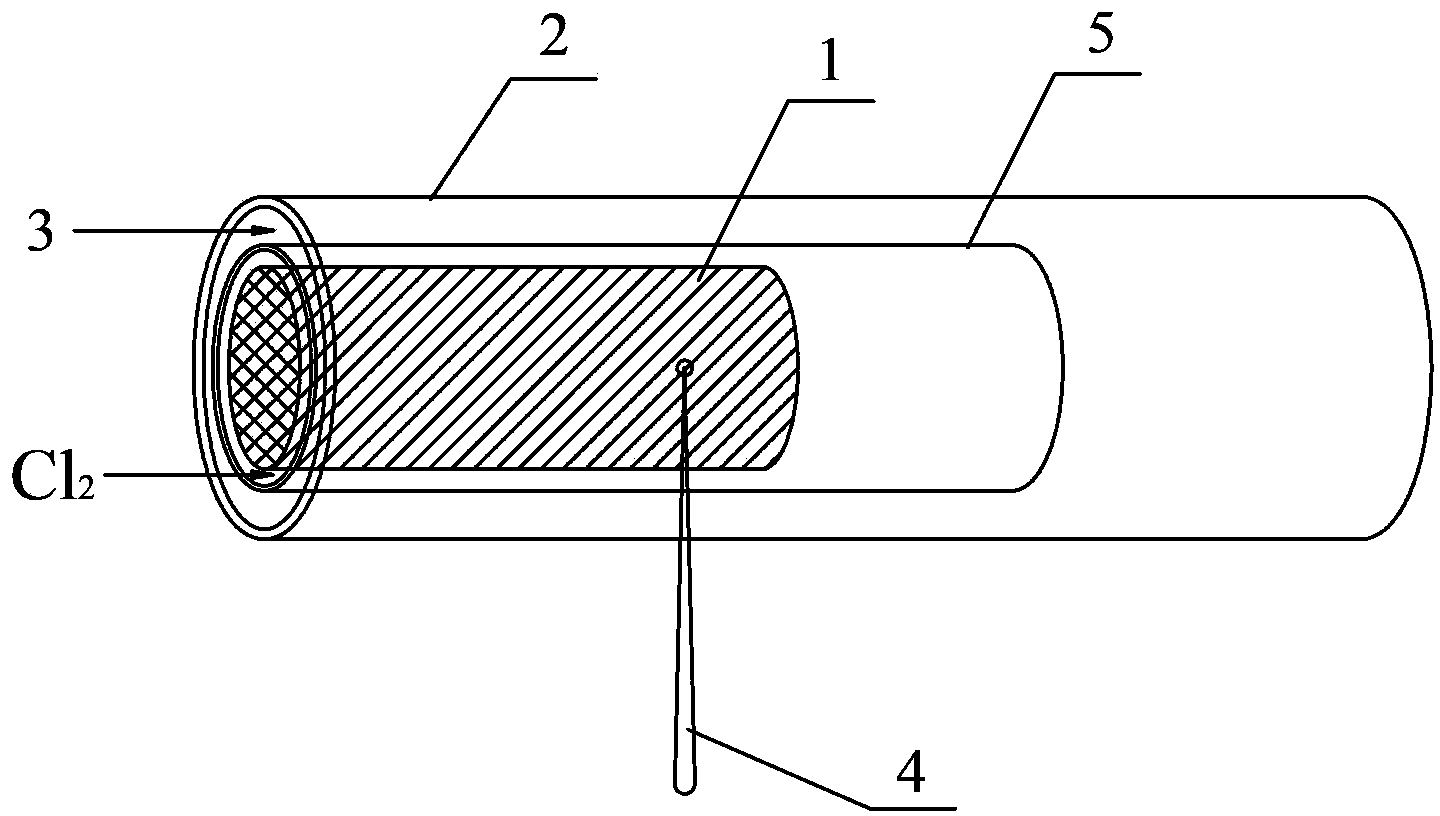

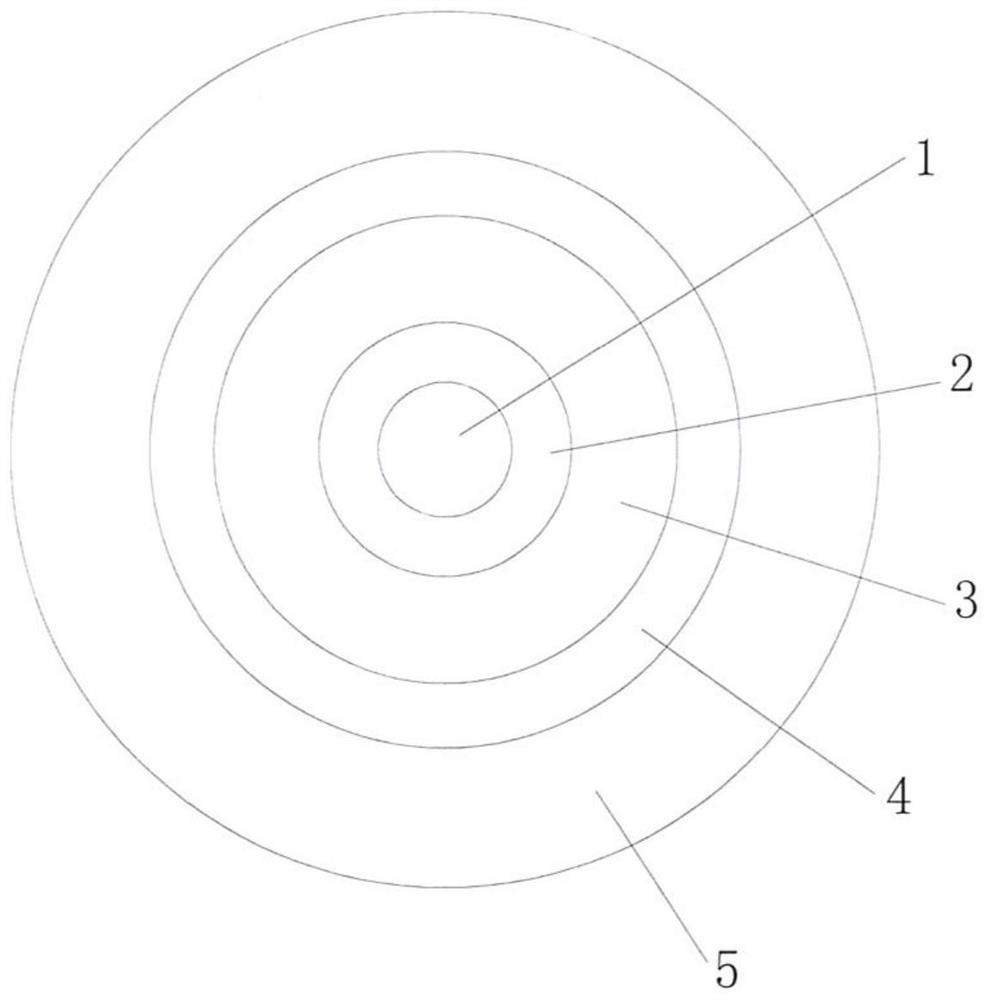

Nano-tubes semiconductor device and preparation method thereof

ActiveCN101924137AImprove charge balance effectUniform doping concentrationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

The invention relates to a semiconductor device and a preparation method thereof. A nano-tubes area is produced by adopting the thin epitaxial layer formed on the channel sidewall of the semiconductor body. The thin epitaxial layer possesses an even and consistent dosage concentration. A first thin epitaxial layer in the same conducting type as the semiconductor body is formed on the channel sidewall of the semiconductor body. A second thin expitaxial layer in the opposite conducting type with the semiconductor body is formed on a first expitaxial layer. The first and the second expitaxial layer possess an even and consistent dosage concentration. An electric charge balance is achieved by choosing an appropriate first and second expitaxial layer and appropriate thickness and dosage concentration of the semiconductor body. The semiconductor body is a P-shaped substrate with light dosage. By adopting the N-expitaxial layer / P-expitaxial layer nano-tubes structure of the same type, a metal oxide field effect tube with a vertical channel, a insulated gate dipole transistor, a Schottky diode and a P-N diode can be produced.

Owner:ALPHA & OMEGA SEMICON INT LP

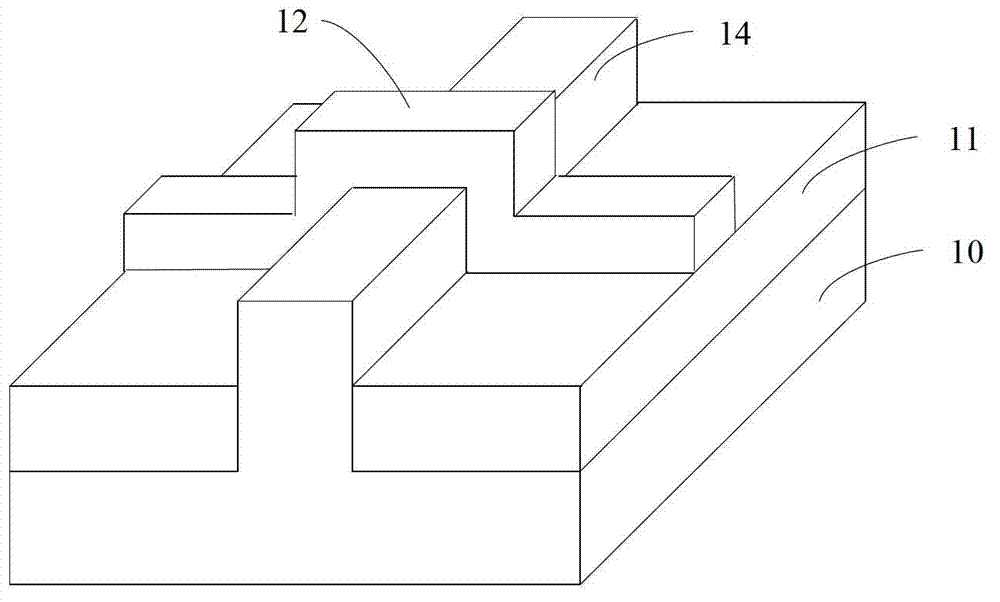

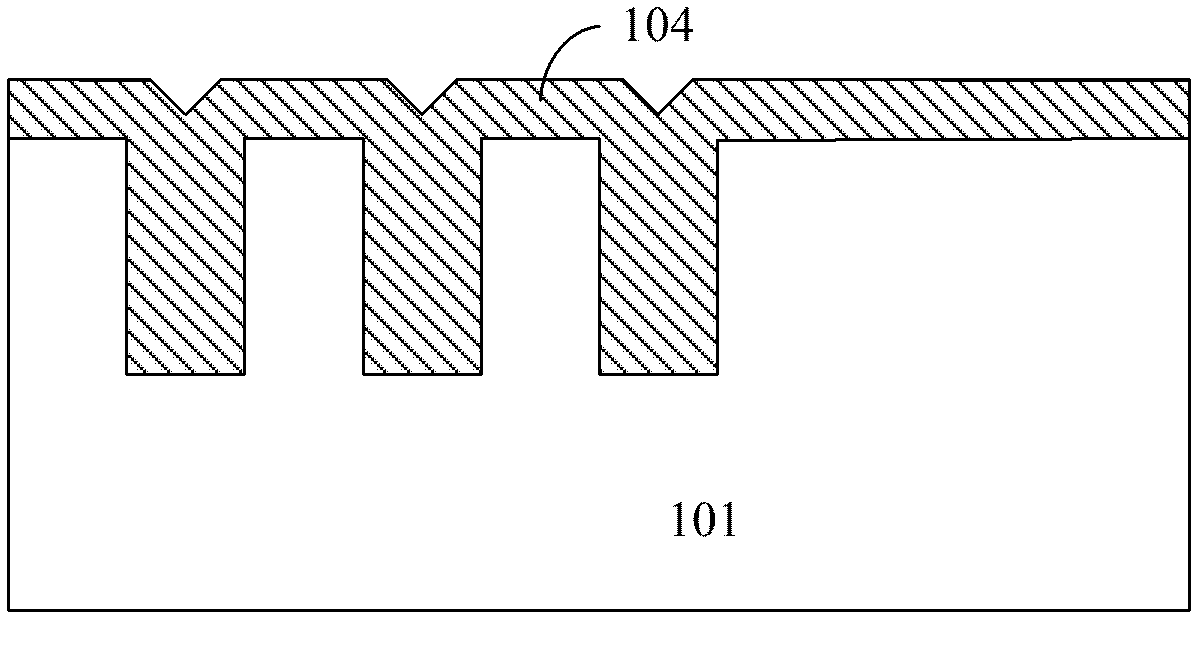

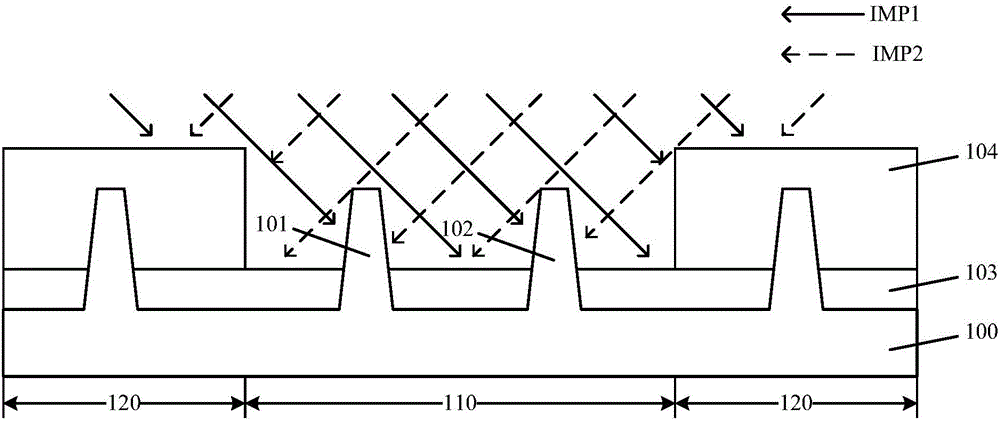

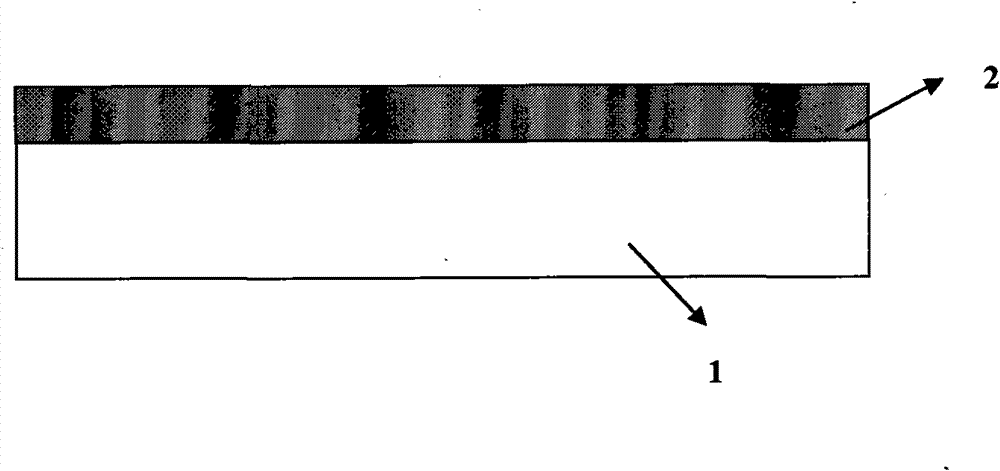

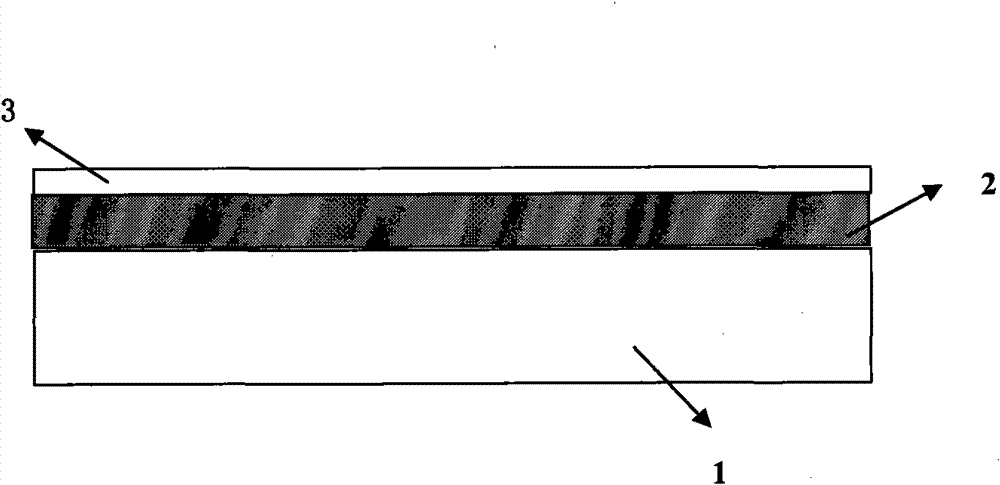

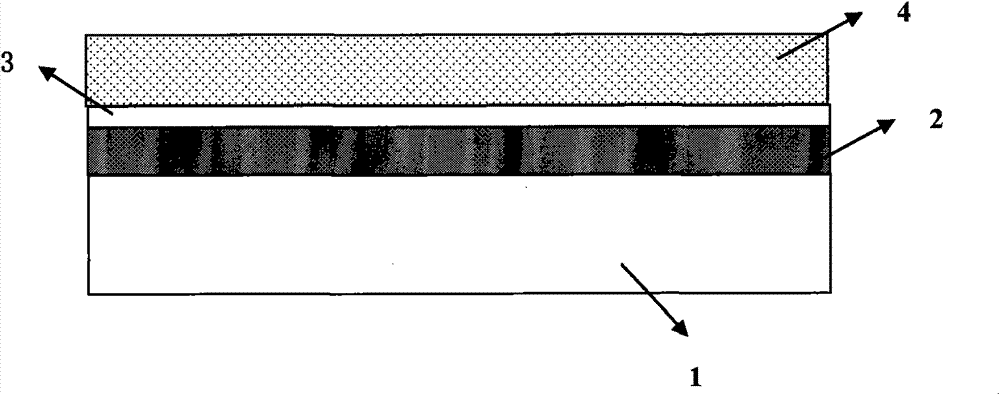

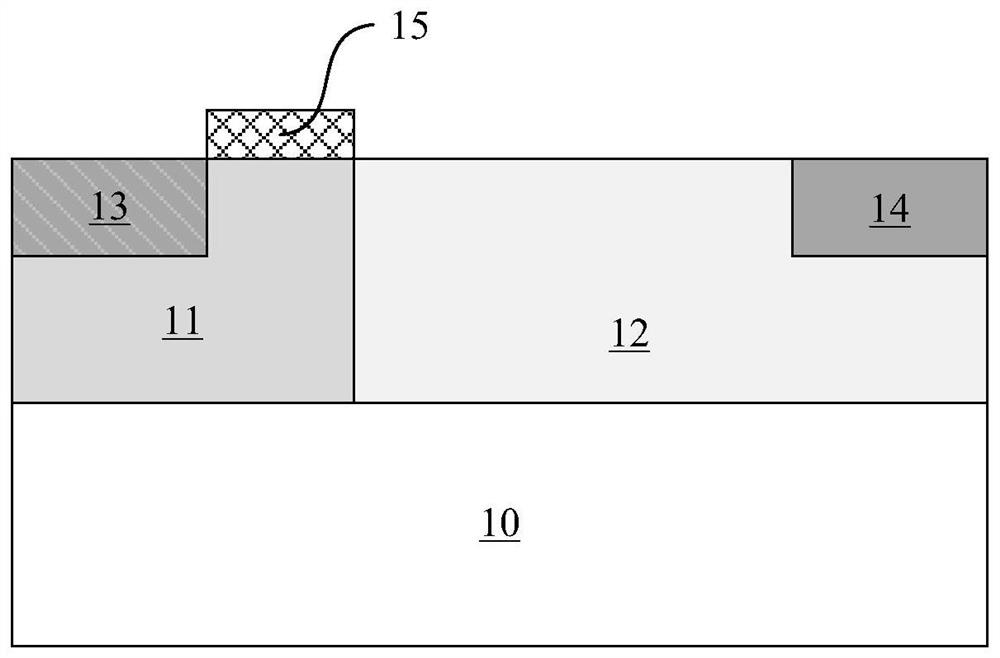

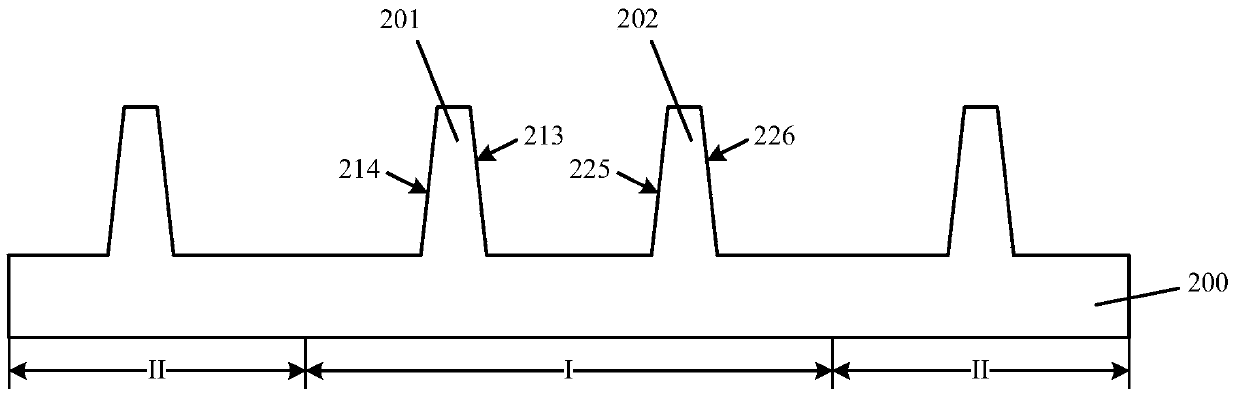

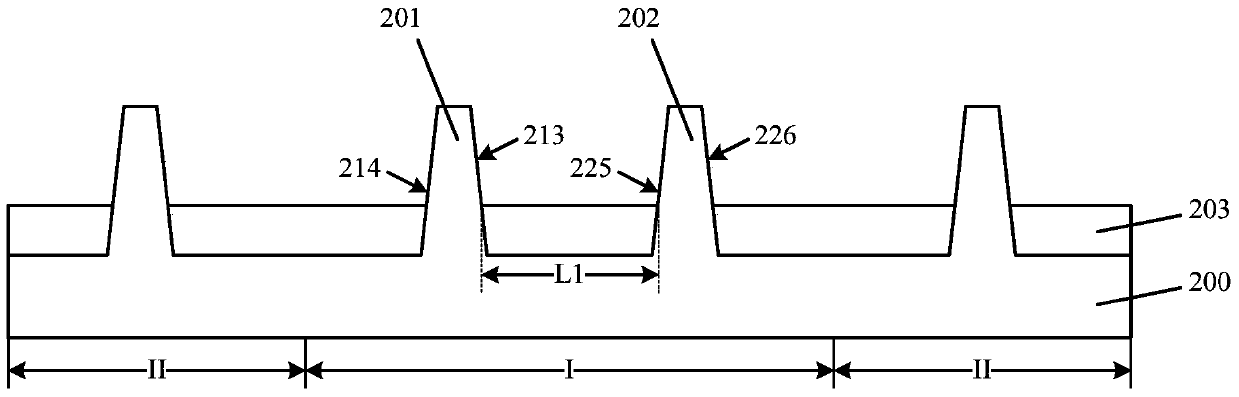

A semiconductor structure, a doping method thereof, and a method for forming a fin field effect transistor

InactiveCN103594341AGood removal effectUniform doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureField-effect transistor

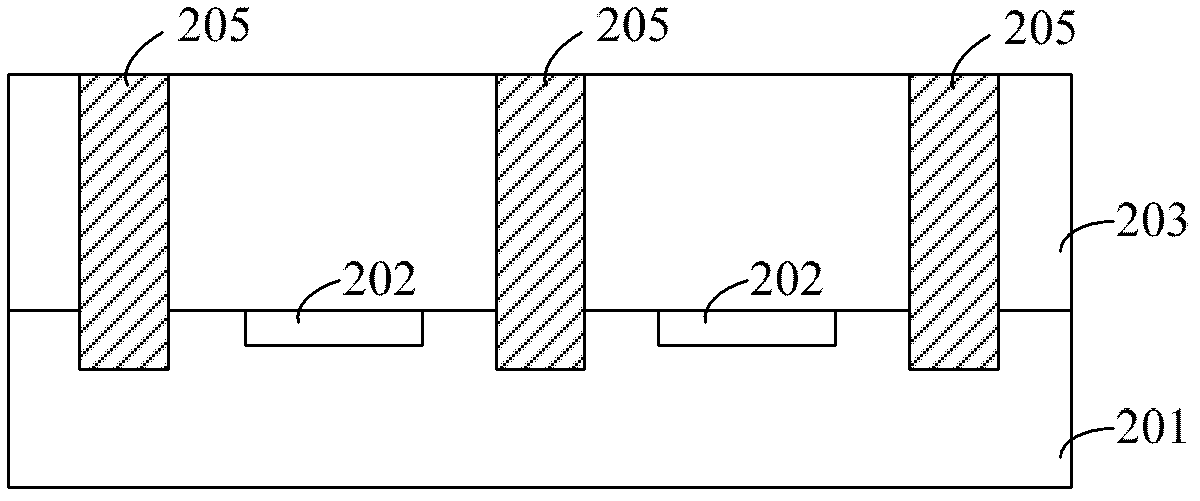

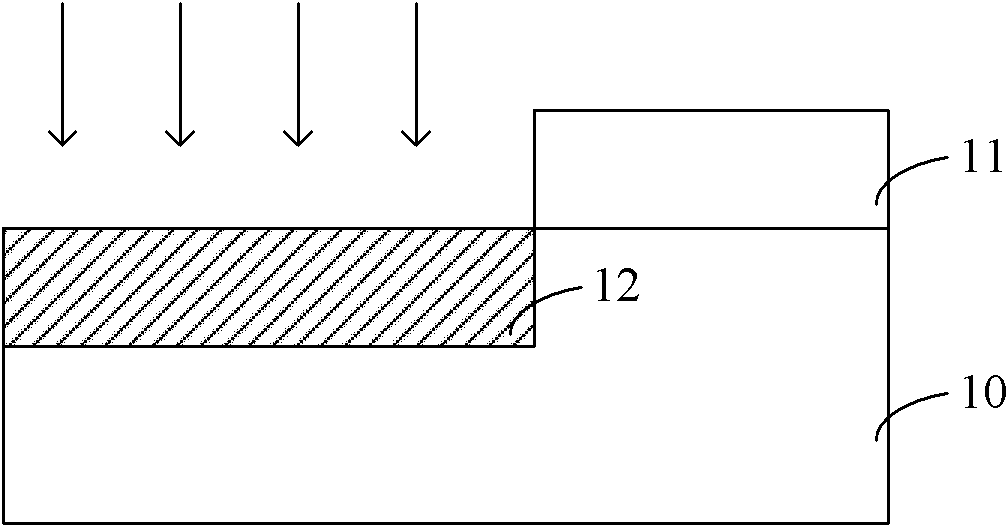

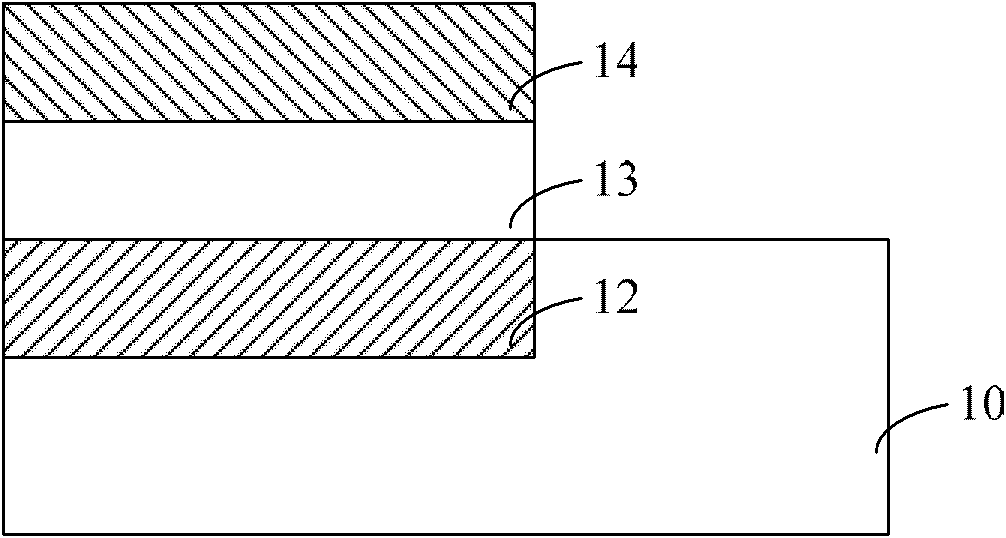

Provided are a semiconductor structure, a doping method thereof, and a method for forming a fin field effect transistor. The doping method of the semiconductor structure comprises: providing a semiconductor substrate on which a fin portion is disposed; forming an impurity layer on the surface of the fin portion; forming a cover cap layer on the surface of the impurity layer, wherein the cover cap layer comprises an amorphous carbon layer; annealing the formed impurity layer and the cover cap layer in order to put the impurity layer into the fin portion; and removing the cover cap layer. The semiconductor structure and the fin field effect transistor are uniformly doped and have simple techniques.

Owner:SEMICON MFG INT (SHANGHAI) CORP

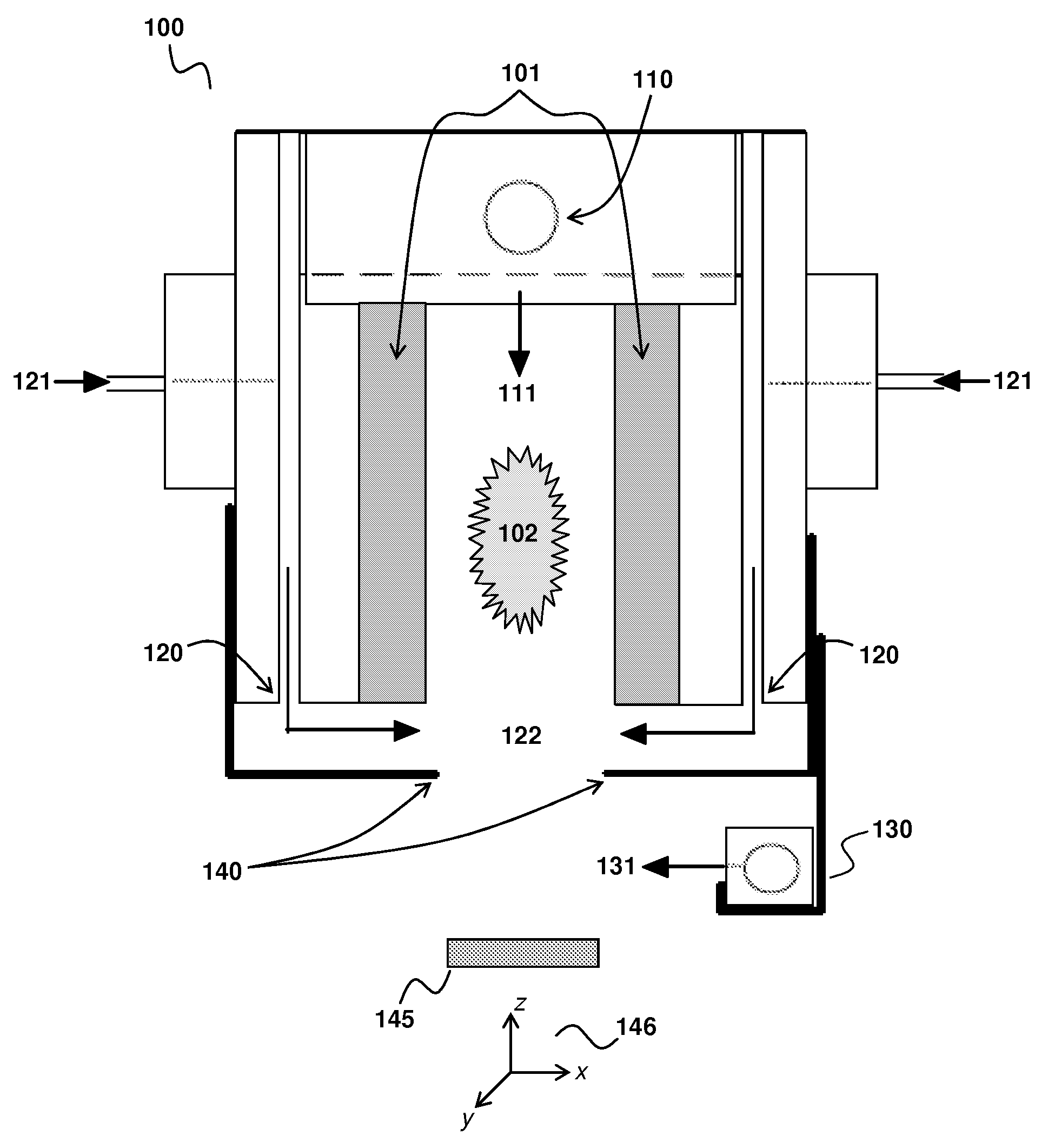

Method for Fabricating a Doped and/or Alloyed Semiconductor

InactiveUS20100320456A1Easily optimize dopant concentrationMaintaining desired structuralCellsVacuum evaporation coatingAlloySemiconductor

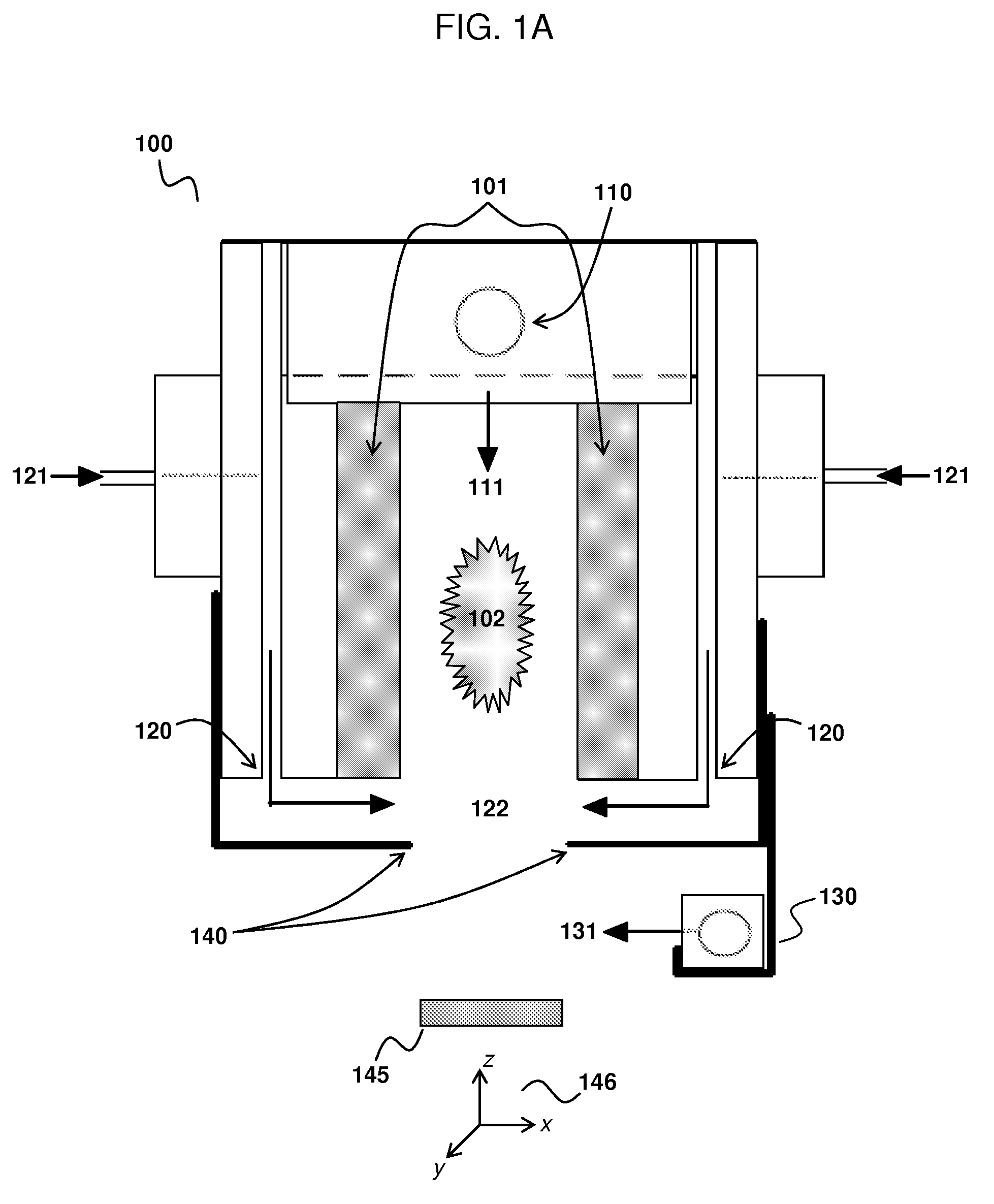

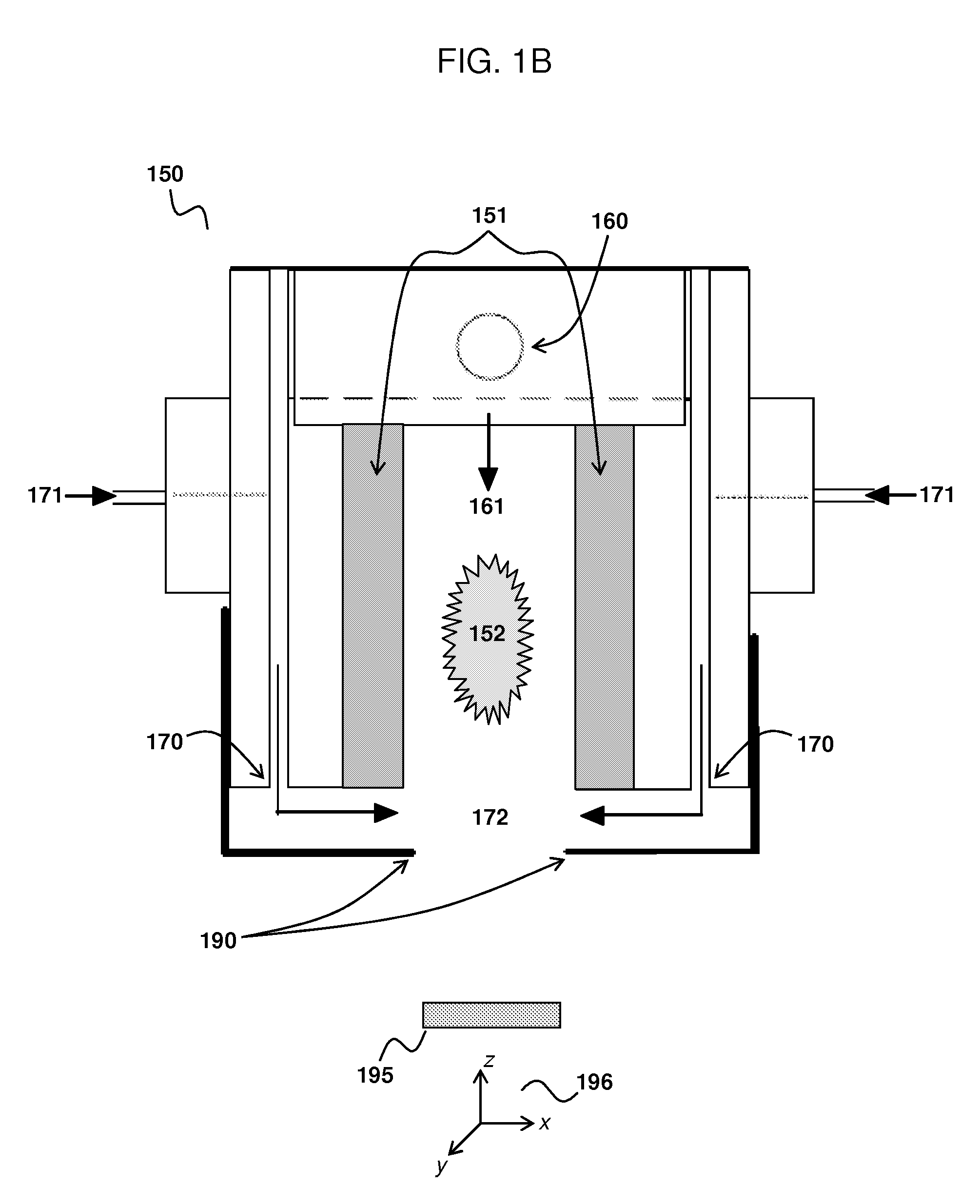

The present invention is directed to methods for depositing doped and / or alloyed semiconductor layers, an apparatus suitable for the depositing, and products prepared therefrom.

Owner:NEW MILLENNIUM SOLAR EQUIP CORP

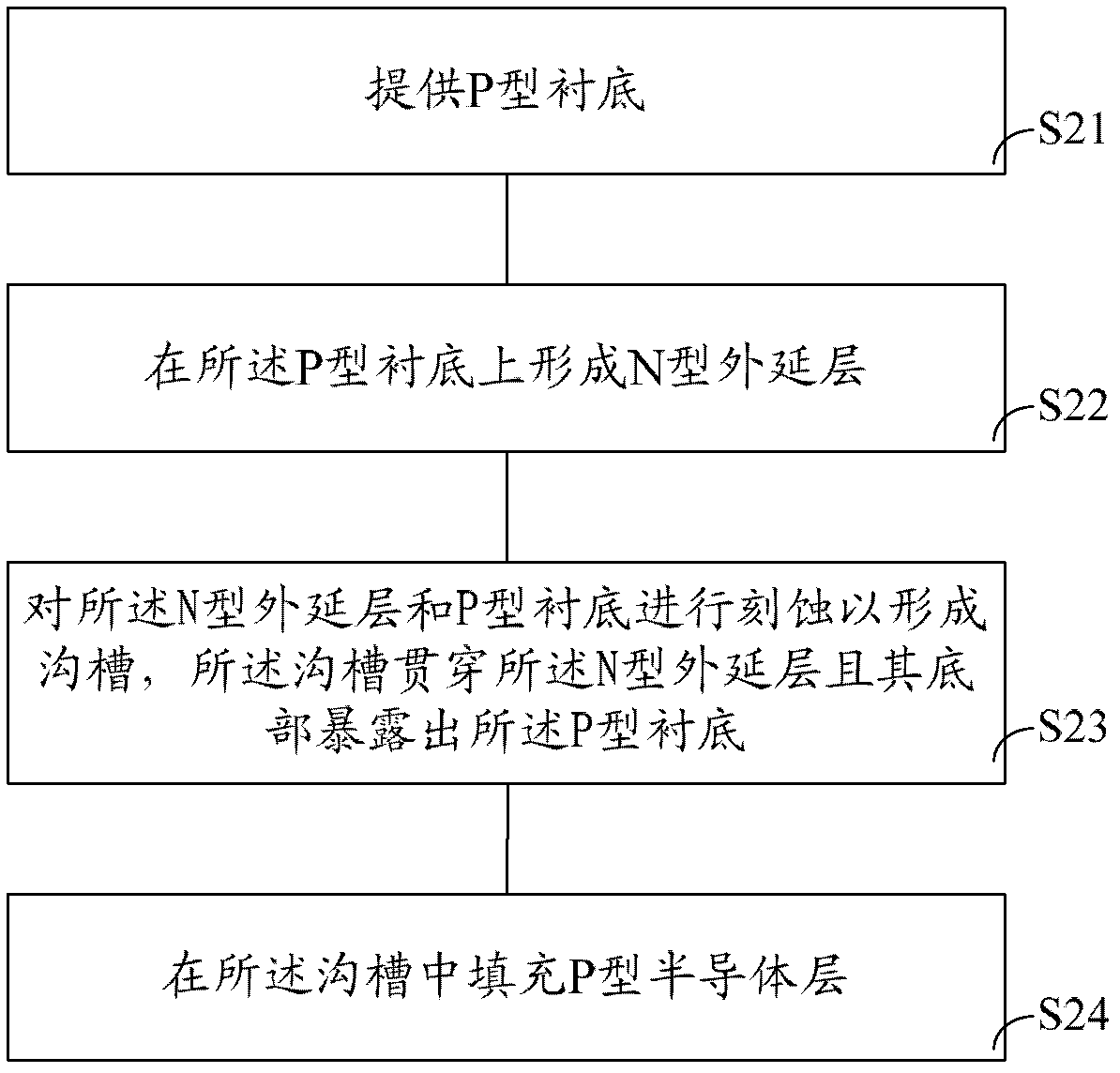

PN junction isolating structure and forming method thereof

InactiveCN102254933AUniform doping concentrationEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesP–n junction

The invention provides a PN junction isolating structure and a forming method thereof. The PN junction isolating structure comprises a P type substrate, an N type epitaxial layer, a groove and a P type semiconductor layer, wherein the N type epitaxial layer is positioned on the P type substrate; the groove passes through the N type epitaxial layer; the P type substrate is exposed out of the bottom of the groove; and the P type semiconductor layer is filled in the groove. The PN junction isolating structure contributes to reducing the occupied chip area, and has a simple process and high operability.

Owner:ADVANCED SEMICON MFG CO LTD

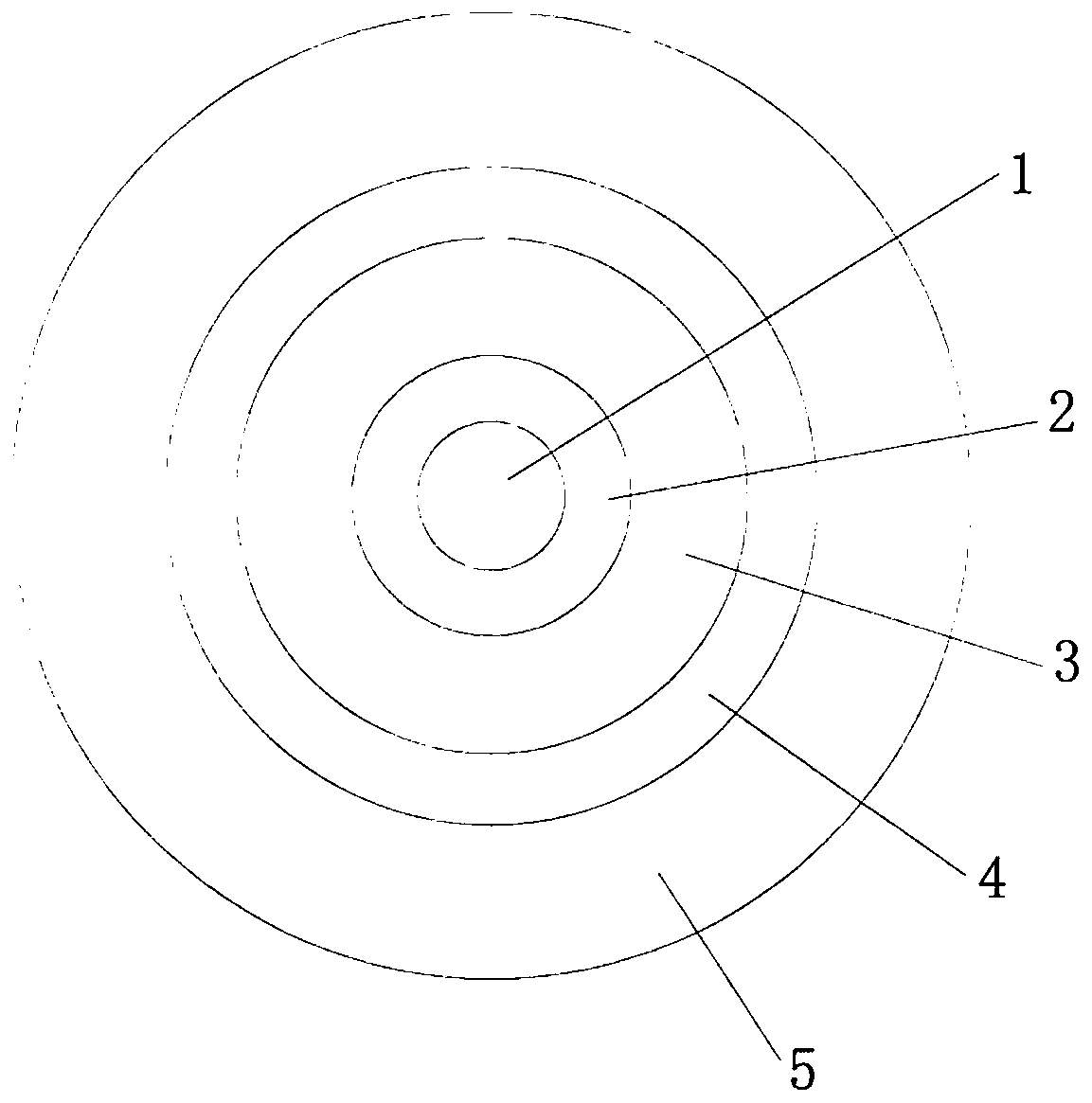

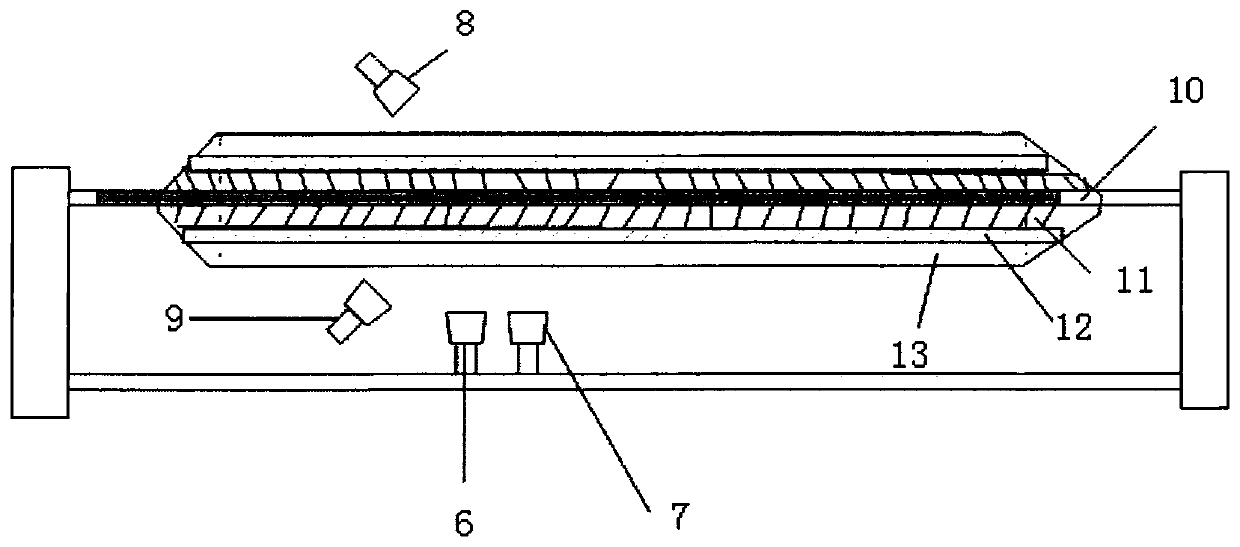

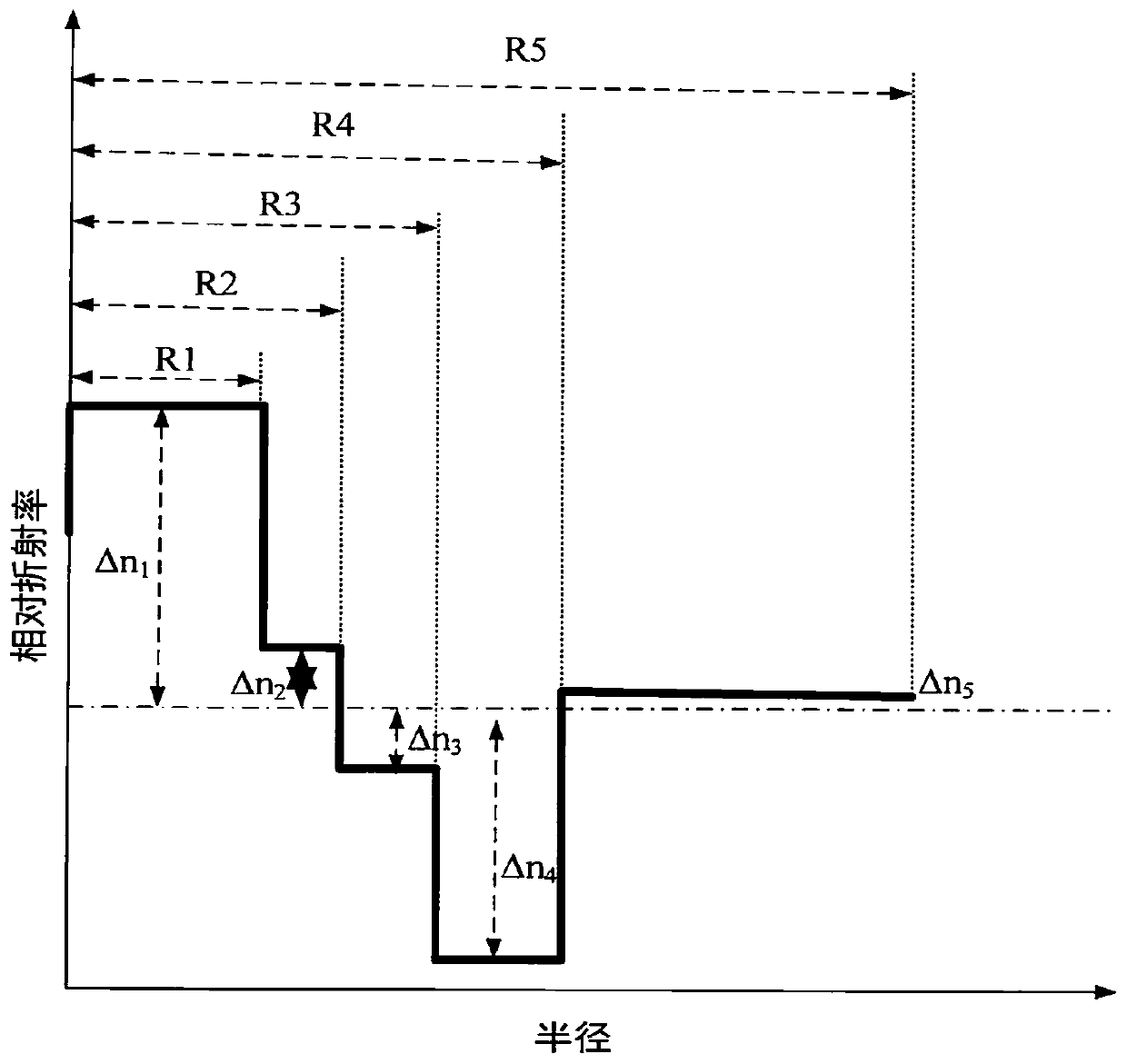

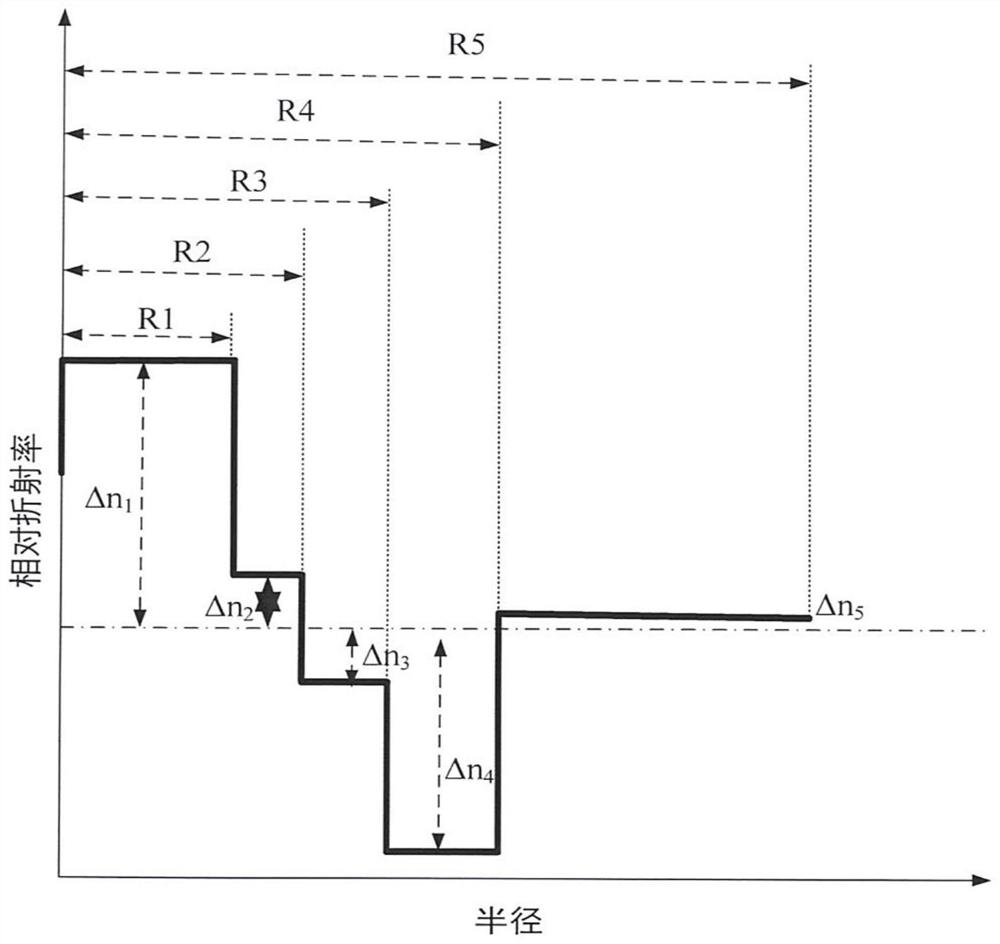

Single-mode fiber and fabrication method thereof

ActiveCN110794509ALow loss and large effective areaBending Loss ImprovementsGlass optical fibreGlass making apparatusPhysicsChemistry

The invention relates to a single-mode fiber and a fabrication method thereof. A bare fiber comprises a core layer and a wrapping layer, wherein the core layer comprises a first core layer, a second core layer and an inner wrapping layer, the relative refractivity difference Delta 1 of the first core layer is more than 0.2% but less than 0.35%, the relative refractivity difference Delta 2 of the second core layer is more than or equal to 0.15% but less than or equal to 0.25%, the refractivity radius of the inner wrapping layer is 24-36 micrometers, the relative refractivity difference Delta 3of the inner wrapping layer is more than or equal to -0.12% but less than or equal to 0%, the wrapping layer comprises a sunken wrapping layer and an external wrapping layer, the relative refractivitydifference Delta 4 of the sunken wrapping layer is more than or equal to -0.40% but less than or equal to -0.28%, and the external wrapping layer is a high-hardness pure quartz sleeve. With the adoption of a method for on-line assembly and drawbenching by two sleeves and a core rod, fiber annealing for many times is performed during the drawbenching process, a coating layer with low modulus is coated in a surface of the fiber, a coating layer with high modulus is coated outside the surface of the fiber, and the fiber with low loss, large effective area and high strength is fabricated. The method is simple, the viscosity of the cord rod can be adjusted according to a demand, the fiber attenuation is reduced without employing a pure silicon core scheme, and production on a large scale is facilitated.

Owner:FASTEN HONGSHENG GRP CO LTD +1

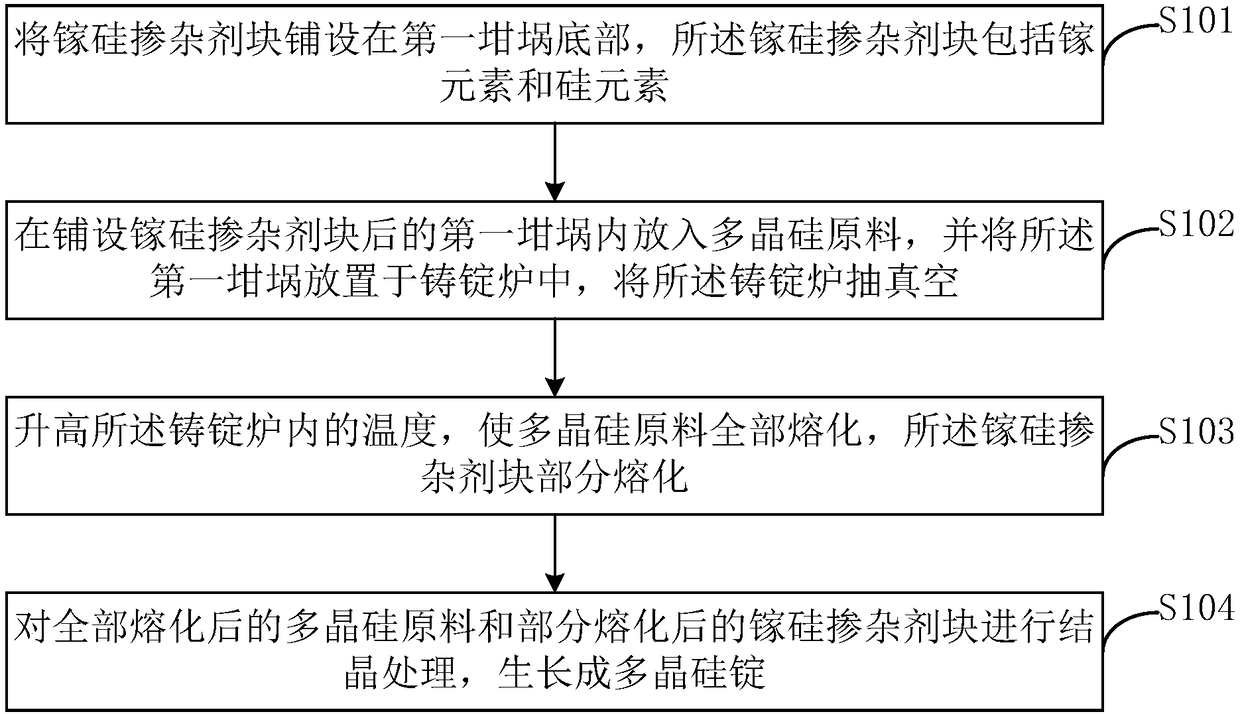

Preparation method for gallium doped polycrystalline silicon ingot and gallium doped polycrystalline silicon ingot

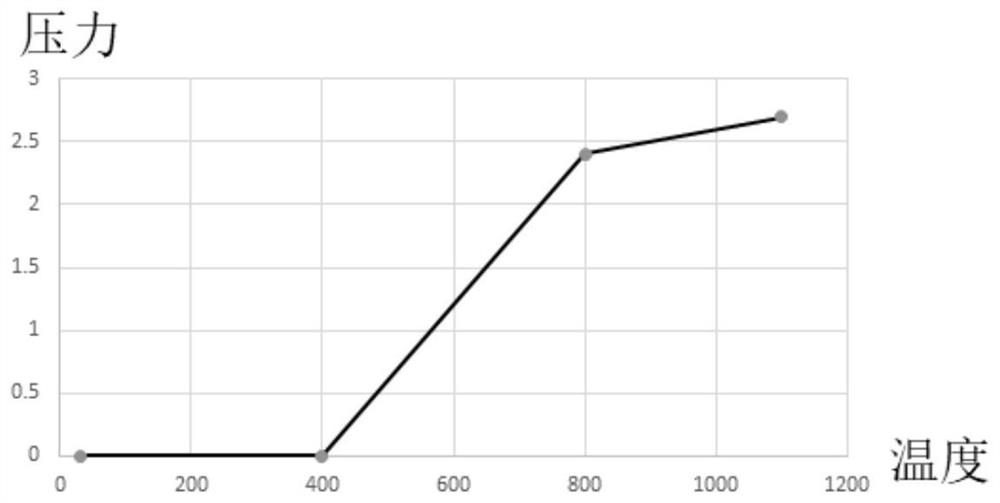

InactiveCN108531983AUniform doping concentrationPolycrystalline material growthSingle crystal growth detailsVacuum pumpingCrucible

The invention is suitable for the technical field of photovoltaic cells, and provides a preparation method for a gallium doped polycrystalline silicon ingot and the gallium doped polycrystalline silicon ingot. The method comprises the following steps: spreading a gallium-silicon doping agent block on the bottom of a first crucible, wherein the gallium-silicon doping agent block comprises an element gallium and an element silicon; putting a polycrystalline silicon raw material into the first crucible which is layed with the gallium-silicon doping agent block, putting the first crucible into a cast ingot furnace, and performing vacuum-pumping on the cast ingot furnace; rising the temperature in the cast ingot furnace, completely melting the polycrystalline silicon raw material, and partiallymelting the polycrystalline silicon doping agent; and performing crystallization treatment on the completely-molten polycrystalline silicon raw material and the partially molten gallium-silicon doping agent block to grow to be the polycrystalline silicon ingot. The preparation method can be used for preparing the gallium doped polycrystalline silicon ingot with uniform doping concentration.

Owner:YINGLI ENERGY CHINA

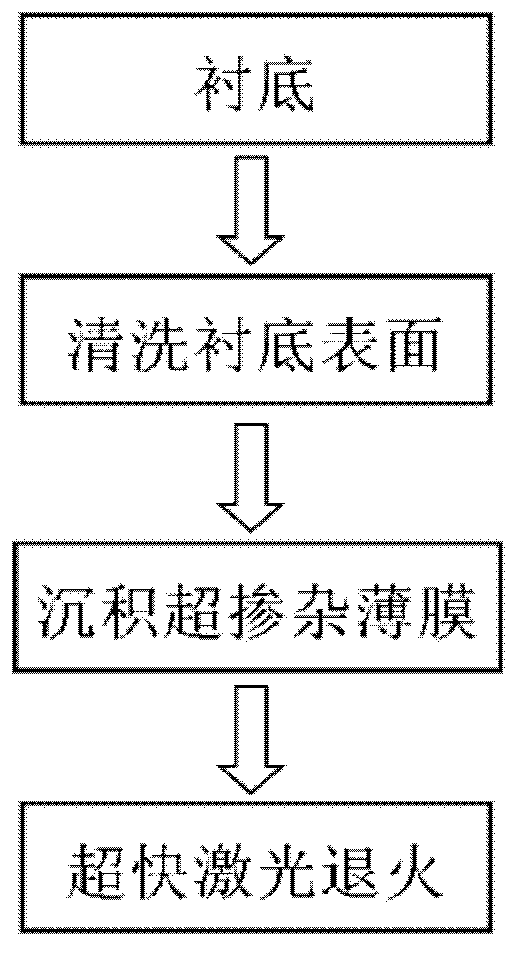

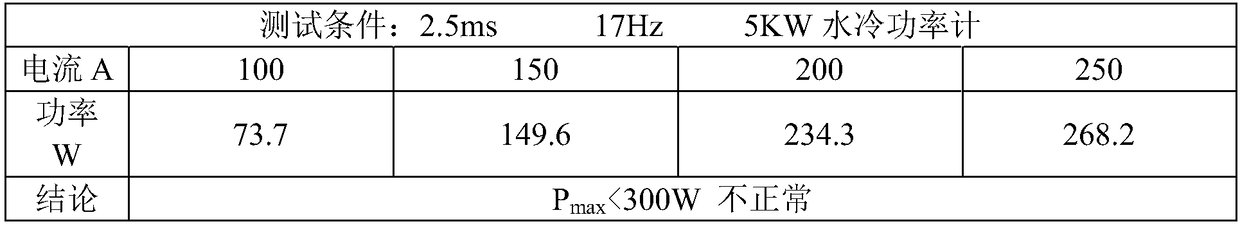

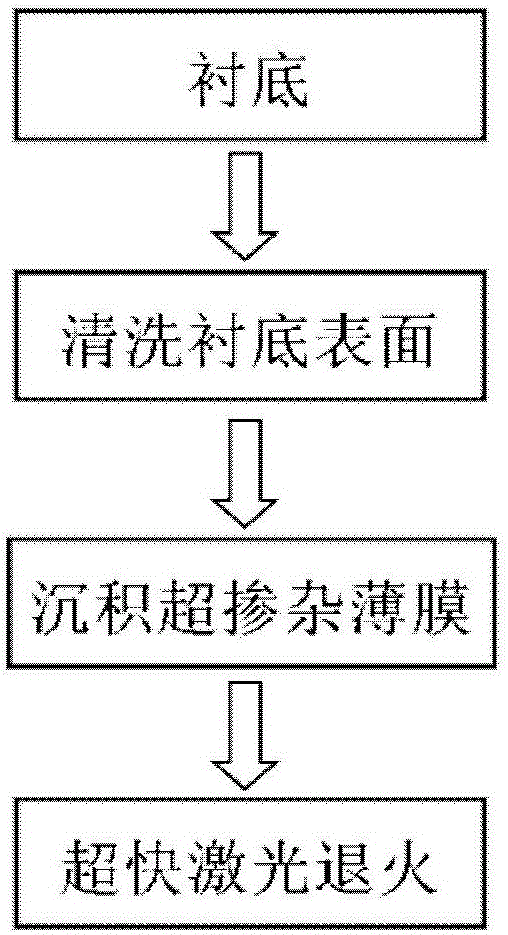

Method for preparing supersaturated-doping semiconductor thin film

InactiveCN103268852AUniform doping concentrationImprove convenienceSemiconductor/solid-state device manufacturingUltra fastSilicon thin film

The invention discloses a method for preparing a supersaturated-doping semiconductor thin film. The method includes the following steps: step one, a substrate is chosen; step two, the surface of the substrate is cleaned up; step three, at a low growth temperature, a semiconductor amorphous thin film is deposited on the surface of the substrate, wherein through control over a deposition speed ratio of atoms, a supersaturated-doping semiconductor amorphous thin film is obtained; step four, laser annealing is carried out on the supersaturated-doping semiconductor amorphous thin film by the utilization of ultra-fast lasers, and the preparation of the supersaturated-doping semiconductor thin film is completed. According to the preparation method, the molecular beam epitaxy technology is used for preparing the supersaturated-doping thin film which is even in doping concentration. Depth distribution of impurities in the prepared supersaturated-doping silicon thin film is very even.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

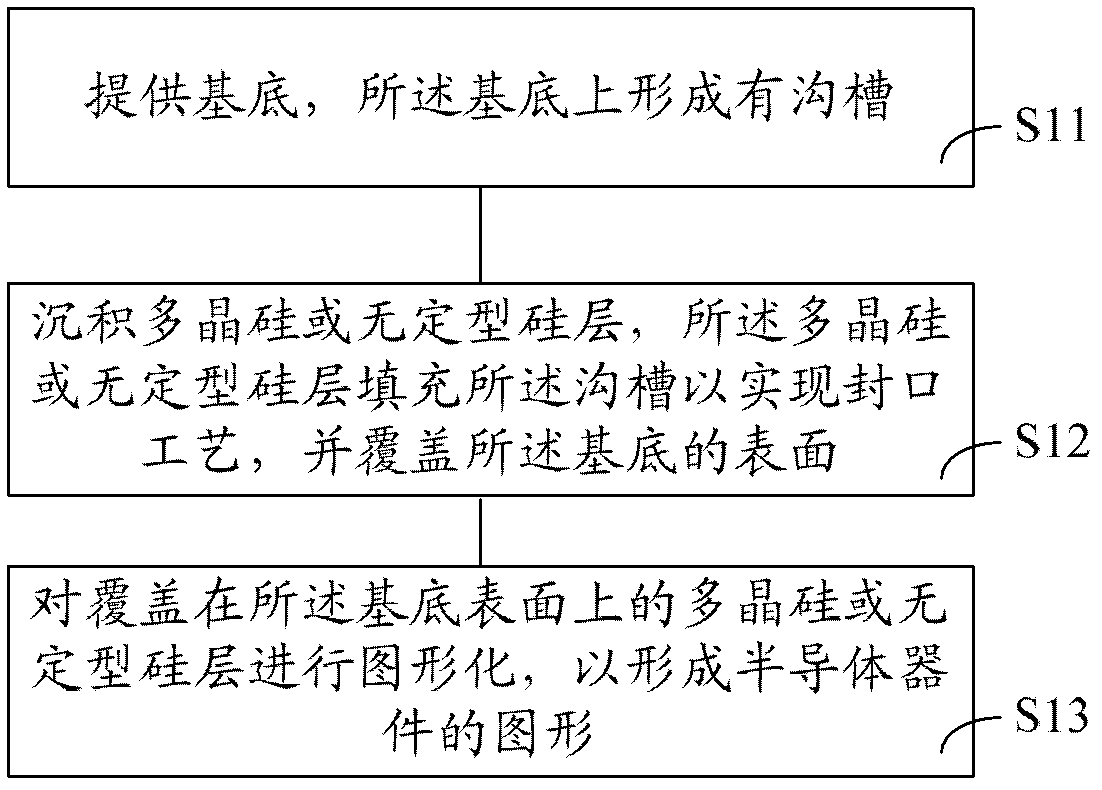

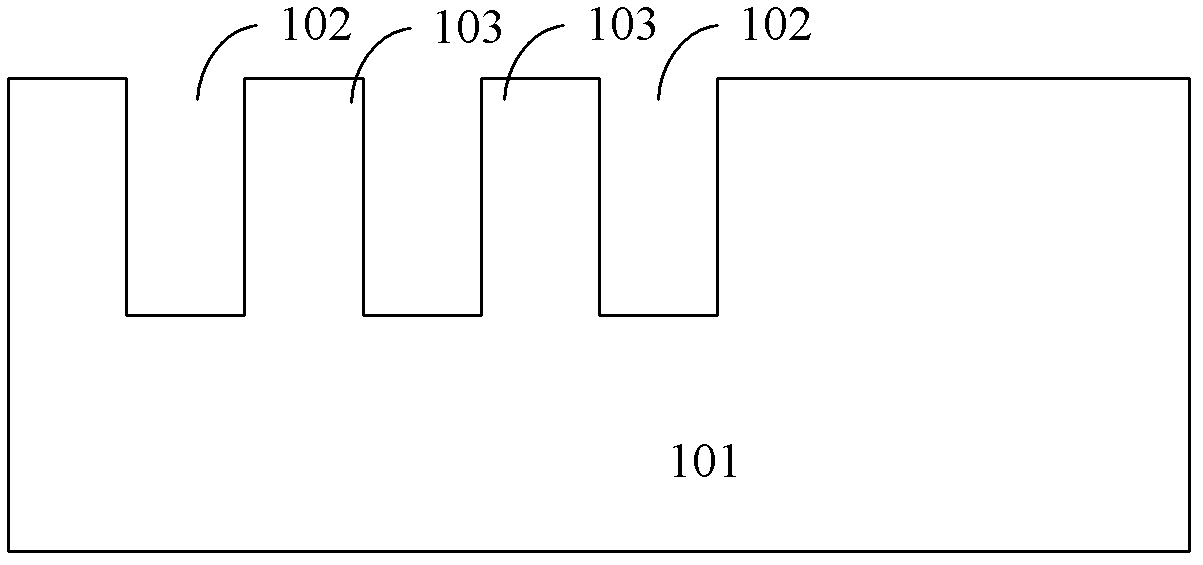

MEMS (micro electro mechanical system) apparatus and forming method thereof

ActiveCN102303844AImprove reliabilityEasy to fillSemi-permeable membranesFixed microstructural devicesAmorphous siliconSemiconductor

The invention provides an MEMS (micro electro mechanical system) apparatus and a forming method thereof. The forming method comprises the following steps: providing a substrate on which a groove is formed; depositing polycrystalline silicon or an amorphous silicon layer which is used for filling the groove to realize the sealing process and cover the surface of the substrate; patterning the polycrystalline silicon or amorphous silicon layer covered on the substrate surface so as to form a pattern of a semiconductor apparatus. The invention can improve the reliability of the filling, simplify the process flow and reduce the cost.

Owner:ADVANCED SEMICON MFG CO LTD

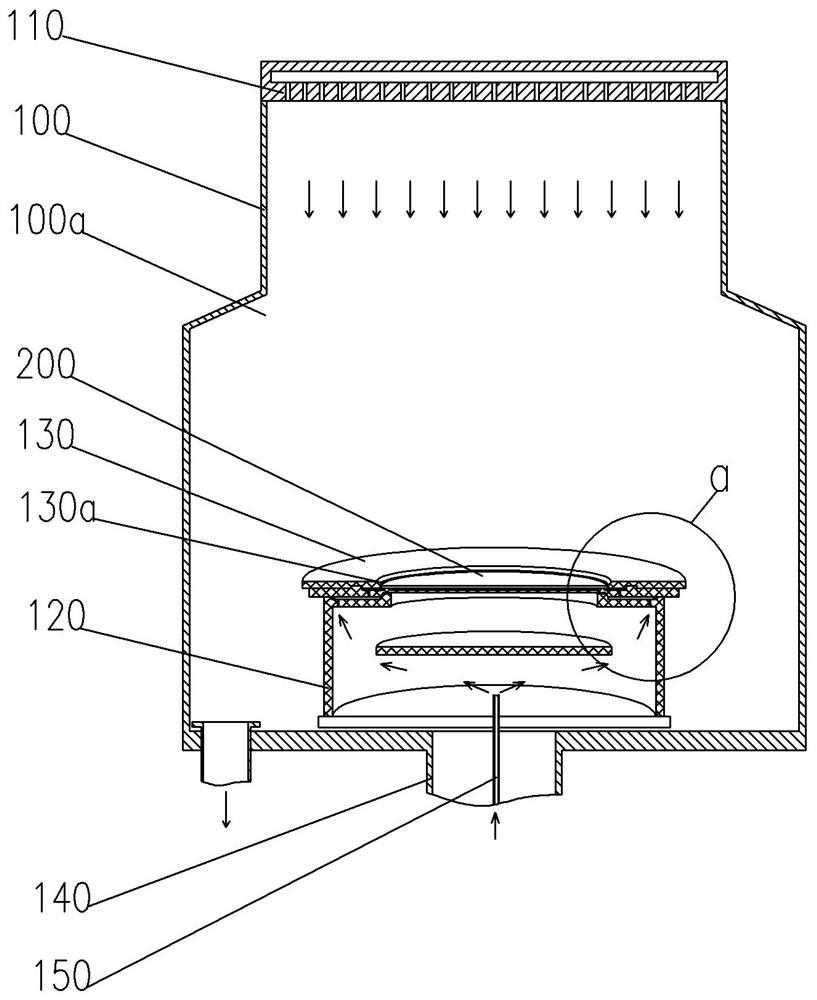

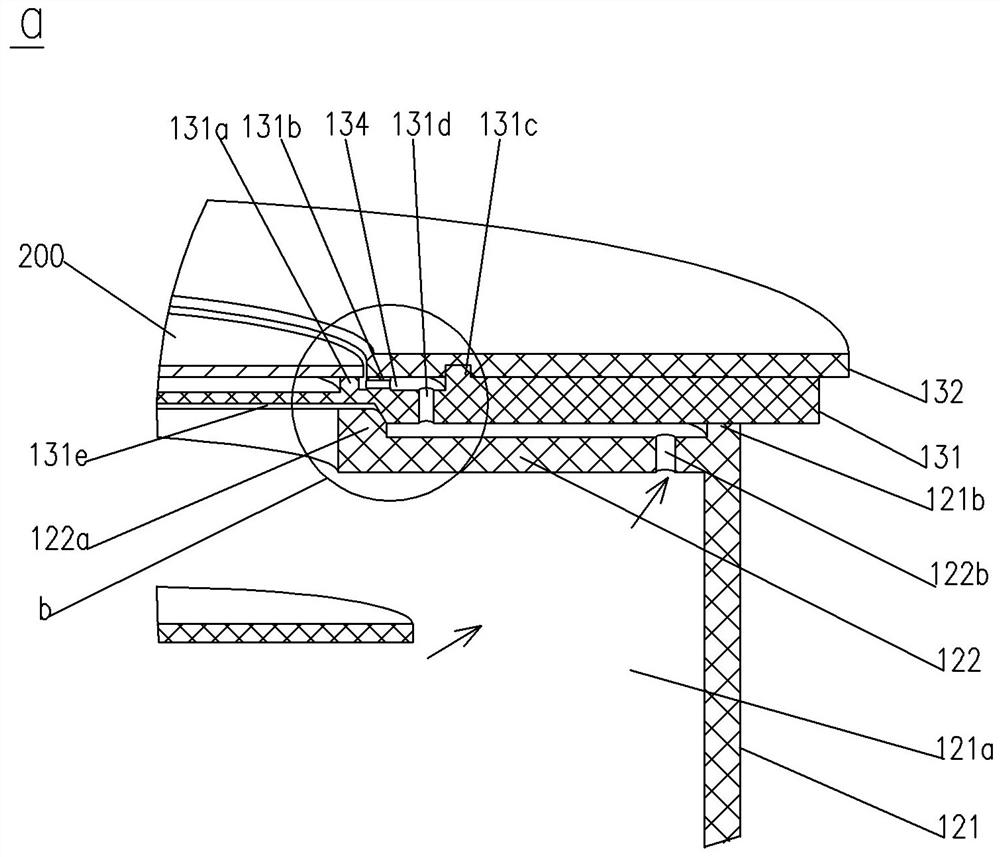

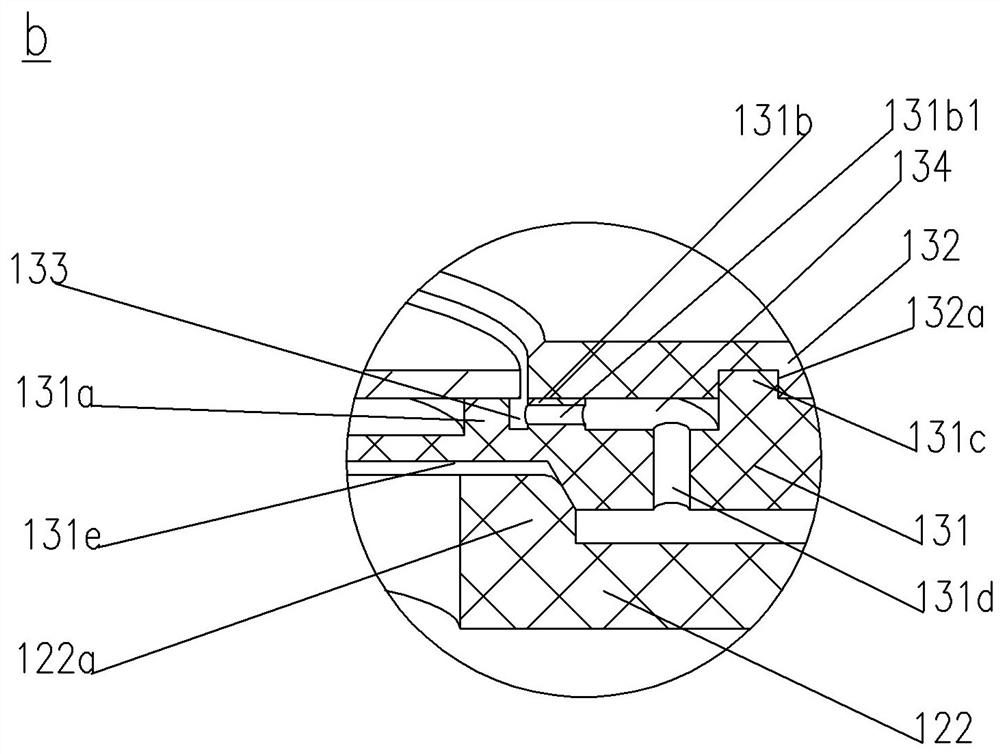

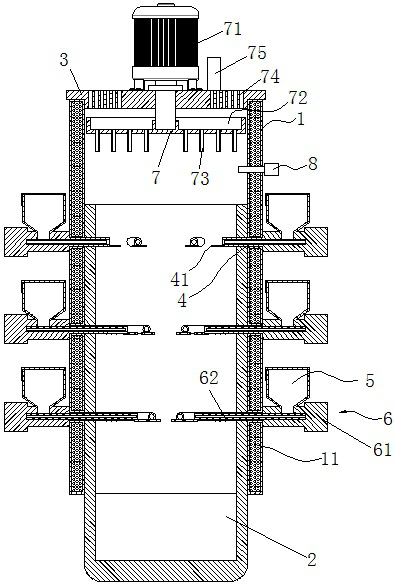

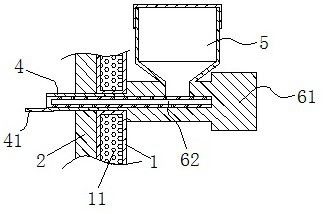

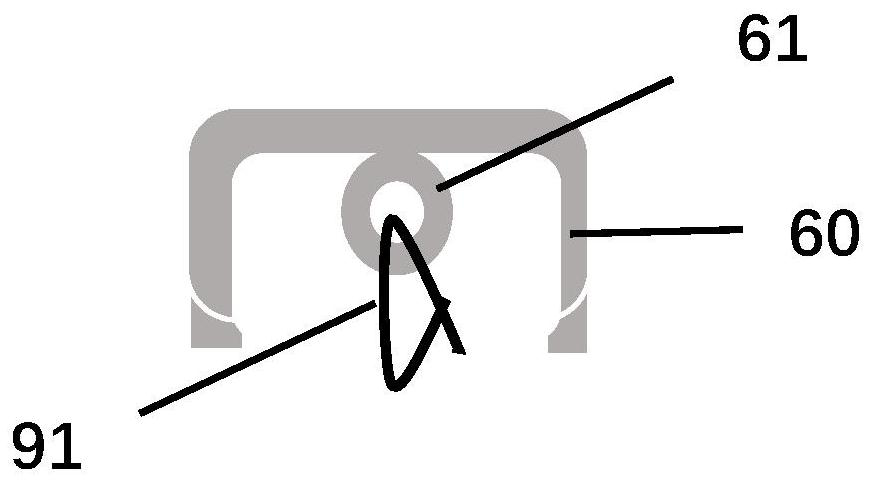

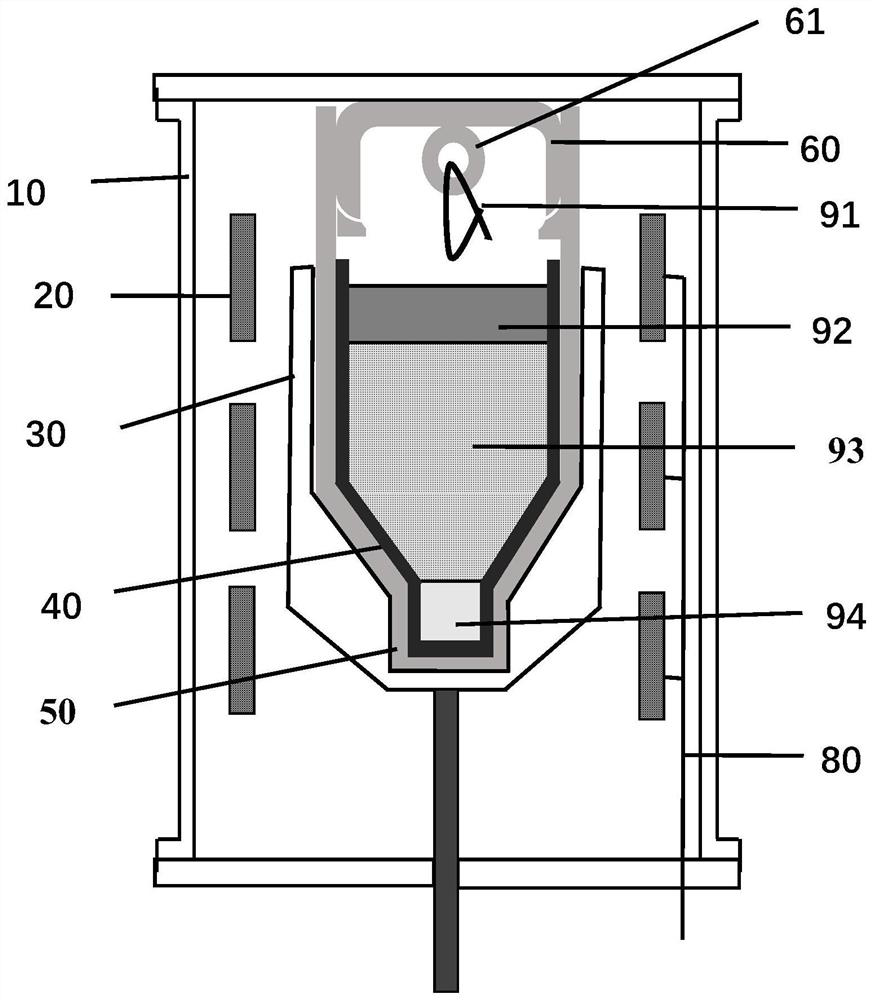

Silicon carbide epitaxial growth device and growth process method

ActiveCN114737254ASuppress doping efficiencyReduce edge effectsPolycrystalline material growthFrom chemically reactive gasesCarbide siliconGraphite

The invention discloses a silicon carbide epitaxial growth device and a growth process method. The growth device comprises a reaction module and a rotary tray assembly, a reaction cavity is formed in the reaction module, the rotary tray assembly is arranged at the bottom of the reaction cavity, the rotary tray assembly comprises a graphite tray and a rotary supporting part, the graphite tray is provided with a concave part used for containing a substrate, an annular first groove is formed in the concave part, and the rotary supporting part is arranged in the annular first groove. The graphite tray is provided with a first groove, the first groove is configured to enable the projection of the edge of the substrate on the graphite tray to fall in the first groove, the graphite tray is provided with a plurality of edge C source gas flow paths, the edge C source gas flow paths are arranged in the circumferential direction of the first groove, and the first groove is communicated with an inner cavity of the rotary supporting part; the plurality of edge C-source gas flow paths guide the C-source gas injected into the inner cavity of the rotary support part to the first groove, and the C-source gas is guided to the edge side of the substrate through the first groove. Therefore, the C content of the edge side of the substrate is improved, the doping efficiency of the edge N is inhibited, and the purpose of uniform doping concentration is achieved.

Owner:芯三代半导体科技(苏州)有限公司

Process for preparing crystalline silicon solar cell by solution method

ActiveCN110416355AImprove passivation functionUniform doping concentrationFinal product manufactureSemiconductor/solid-state device manufacturingPolyethylene glycolPhosphoric acid

The invention discloses a process for preparing a crystalline silicon solar cell by a solution method. The method comprises the steps: adding ethyl alcohol, polyethylene glycol, vinyltrimethoxysilaneand the like into a phosphoric acid solution to serve as a phosphorus diffusion solution source, and uniformly coating the surface of a silicon wafer with diffusion liquid through an ultrasonic atomization spraying method; then diffusing phosphorus at the high temperature to obtain the uniform doping concentration of the surface. According to the invention, the solution spraying method is adoptedto prepare a titanium dioxide anti-reflection film to replace a silicon nitride anti-reflection film prepared by a PECVD method, and a microemulsion composed of anionic polyacrylamide (APAM), isopropanol and the like is added into a titanium tetrachloride solution to serve as a precursor solution of the titanium dioxide film, so that the passivation function of the film on the silicon surface is improved.

Owner:ZHEJIANG NORMAL UNIVERSITY

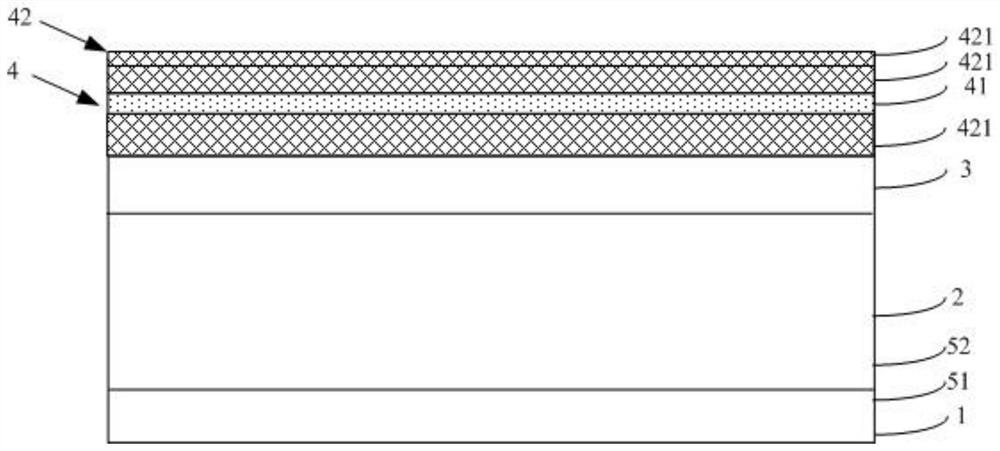

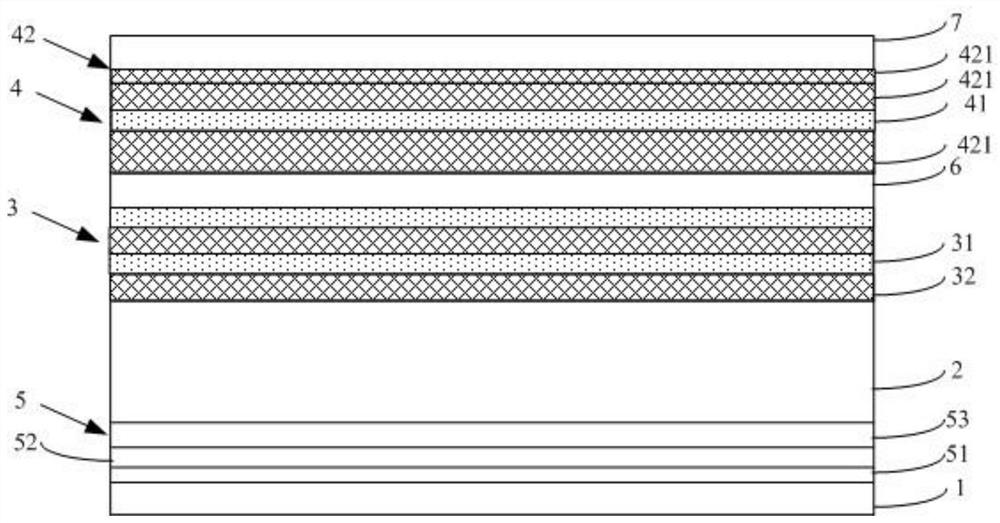

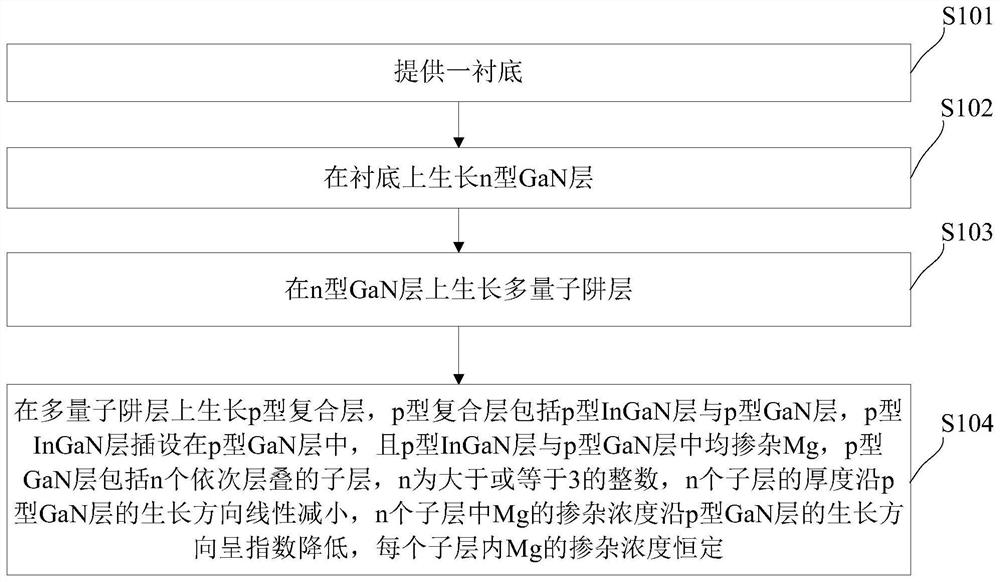

Preparation method of light-emitting diode epitaxial wafer with p-type composite layer

ActiveCN113644174ALower activation energyHigh activation rateSemiconductor devicesElectron holePhysical chemistry

The invention discloses a preparation method of a light-emitting diode epitaxial wafer with a p-type composite layer, and belongs to the field of light-emitting diode manufacturing. The p-type composite layer is grown on a multi-quantum well layer, the p-type composite layer comprises a p-type InGaN layer and a p-type GaN layer, the In element has the effect of reducing the activation energy of Mg, and the activation rate of Mg in the p-type InGaN layer and the p-type GaN layer can be improved so as to improve the number of holes. The p-type InGaN layer is inserted in the p-type GaN layer, and the p-type InGaN layer can be used as a low-barrier region, stores part of holes and expands the holes, so that the holes can enter the multi-quantum well layer more uniformly, and the light emitting uniformity of the light emitting diode is improved. The light-emitting efficiency and the light-emitting uniformity of the light-emitting diode can be improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

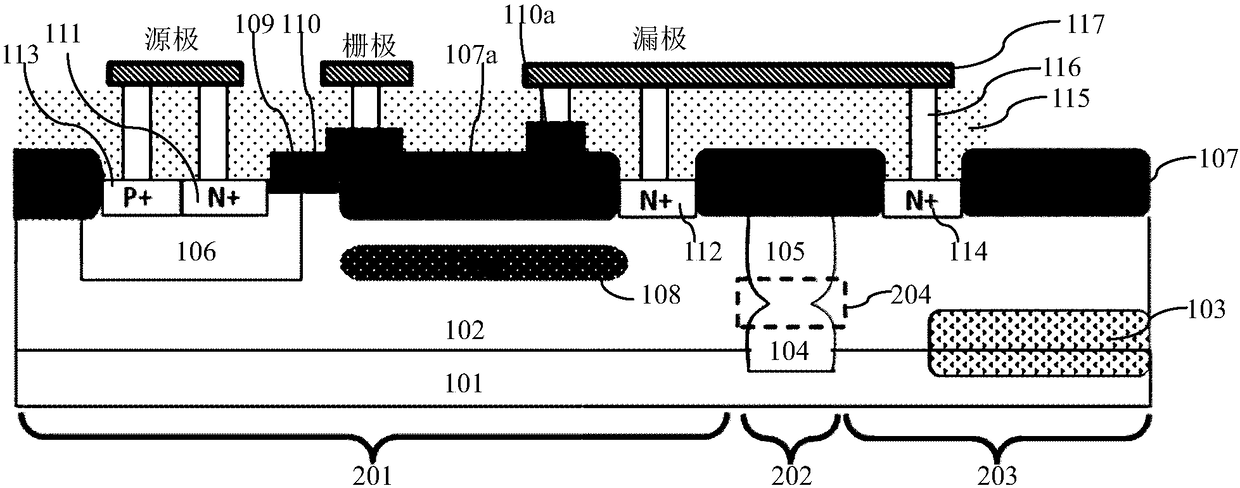

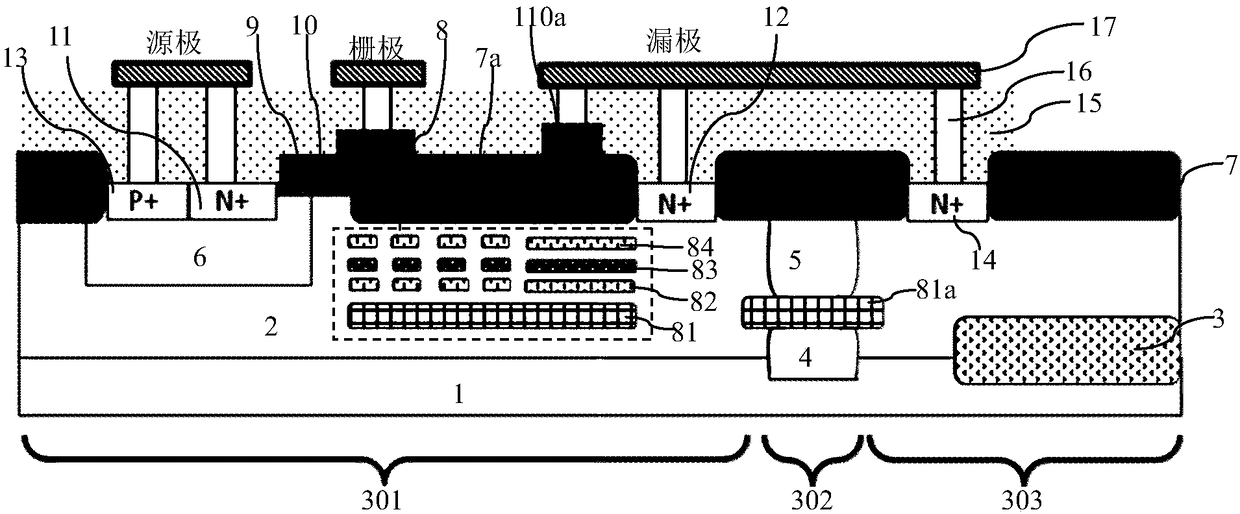

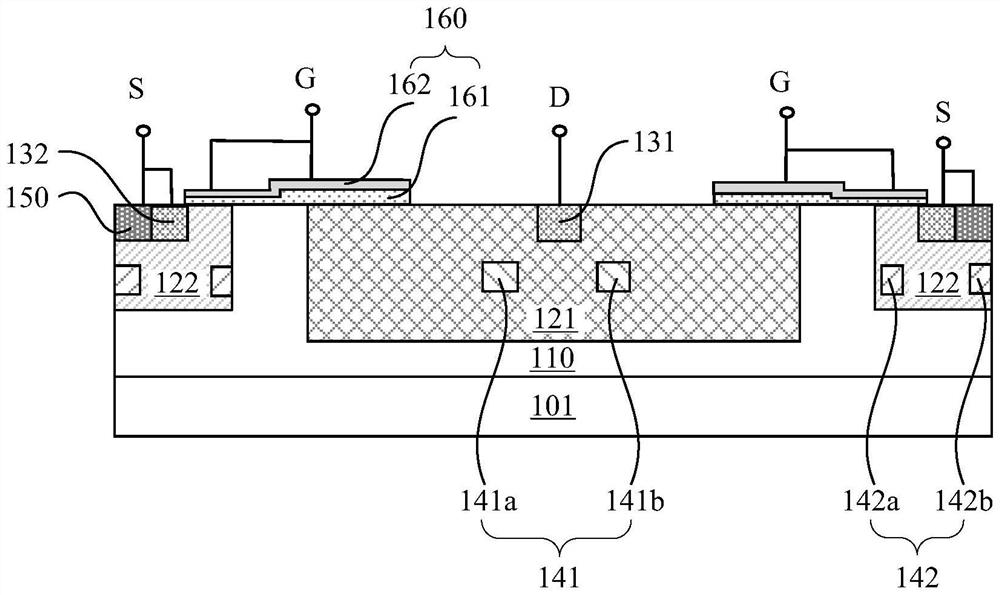

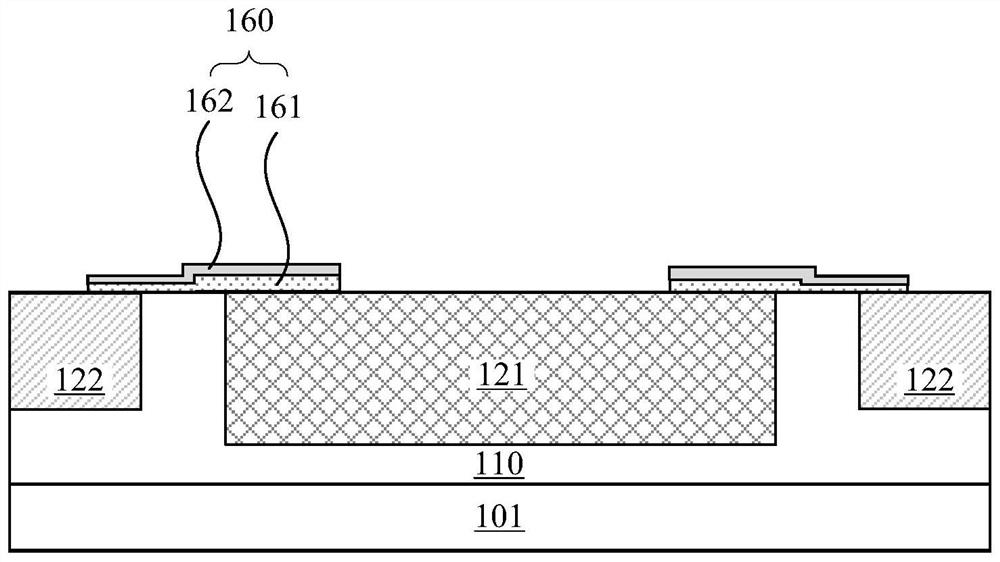

Level shifting structure and manufacturing method thereof

ActiveCN108493248ABoost exhaustionAvoid collusion leakageSemiconductor/solid-state device manufacturingSemiconductor devicesElectric fieldLevel shifting

The present invention discloses a level shifting structure. The level shifting structure includes an LDMOS, a pass isolation region and a high side region; the pass isolation region includes a first buried layer having a second conductivity type and a second well region having a second conductivity type, wherein the second well region is connected to the bottom first buried layer; a drift region of the LDMOS is composed of a first epitaxial layer, and drift region field oxygen is formed on a surface of the drift region; a surface electric field reduction structure is formed in the drift regionon the bottom of the drift region field oxygen, the surface electric field reduction structure comprises two or more second conductivity type injection layers; the injection depth of the second conductivity type injection layer on the bottommost layer is equal to a connection position between the second well region and the first buried layer, and a third injection region is superimposed at the connection position and is formed simultaneously with the bottommost second conductivity type injection layer. The invention discloses a manufacturing method for the level shifting structure. The invention can reduce the leakage of the pass isolation region while enhancing the effect of reducing the surface electric field and reducing the on-resistance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Phase transformation memory and manufacturing method thereof

InactiveCN1455448AIncreasing the thicknessPrevent breakdownSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorInsulation layer

First, an N+polycrystal layer and an N- polycrystal layer are formed on a semiconductor substrate. The first shallow-channel isolation structure is formed in the N+ layer in order to isolate the prearranged character line region; and the second shallow-channel isolation structure is formed in the N- layer in order to isolate the prearranged P+ adulteration region. Next, the defined insulation layer is formed. N+ adulterating is carried out for the part of N- polycrystal layer in order to connect N+ adulteration region in N+ polycrystal layer. P+ is adulterated in the N+ polycrystal layer so as to form a P+ adulteration region. The, the contact plug across the insulation layer is formed on the N+ adulteration region and the P+ adulteration region respetively. Finally, an upper electrode, a phase change layer and a lower electrode are formed on the contact plug being as an electrod.

Owner:MACRONIX INT CO LTD

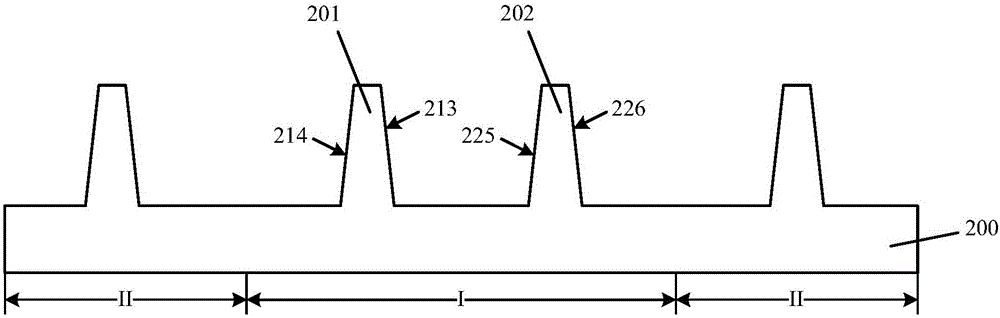

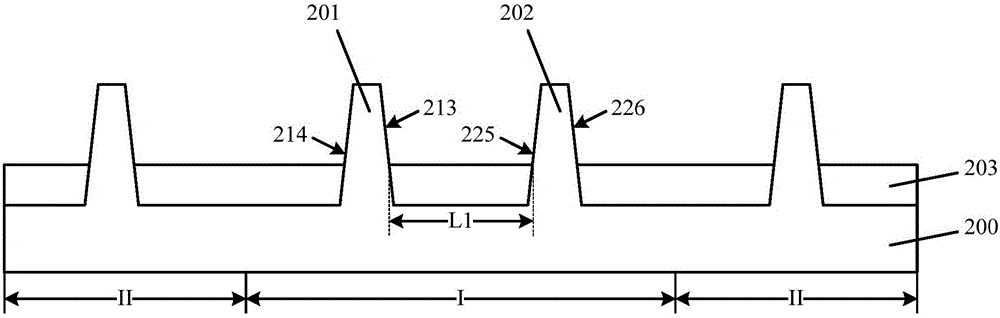

Semiconductor structure forming method

ActiveCN106328528AInhibit injectionAvoid dopant implantationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureIsolation layer

The invention discloses a semiconductor structure forming method. The method comprises steps: a substrate with a first area and an adjacent second area is provided, wherein the surface of the substrate in the first area is provided with a first fin part and an adjacent second fin part, the surface of the substrate is provided with an isolation layer, and the minimal distance between the side wall of the first fin part and the side wall of the second fin part is a first distance; a mask layer is formed on the surface of the isolation layer, wherein an opening for enabling the first area to be exposed is arranged in the mask layer, the opening is provided with a first side wall and an opposite second side wall, the minimal distance between the side wall of the first fin part and the first side wall is larger than the minimal distance between the side wall of the second fin part and the first side wall, and the value obtained by dividing the thickness of the mask layer by the minimal distance between the side wall of the first fin part and the first side wall is larger than that obtained by dividing the distance between the top of the second fin part and the surface of the isolation layer by the first distance; and first lightly-doped injection with a first injection angle is carried out on the first fin part from one side of the first side wall, wherein the tangent value of the first injection angle is smaller than or equal to the value obtained of dividing the thickness of the mask layer by the second distance. The formed semiconductor structure is stable in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

PCM (phase change memory) and forming method thereof

InactiveCN102569645AUniform doping concentrationImprove performanceElectrical apparatusElectrical resistance and conductancePhase-change memory

The invention provides a PCM (phase change memory) and a forming method thereof. The forming method of the PCM comprises the steps as follows: providing a semiconductor substrate, forming a groove on the semiconductor substrate, and forming epitaxy growth in the groove to form a first epilayer, which is an N-type doped semiconductor material or a P-type doped semiconductor material. According to the invention, the improvement on the film quality of a PN junction can be facilitated, the uniformity of doping concentration of the first epilayer serving as a word line is improved, and the problem of resistance increase of the word line can be avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Preparation method of large-size yttrium aluminum garnet (YAG) laser crystal

InactiveCN109280974AReduce defectsImprove effective utilizationPolycrystalline material growthBy pulling from meltMolten stateCrystallographic defect

The invention provides a preparation method of a large-size yttrium aluminum garnet (YAG) laser crystal. The preparation method comprises the following steps: mixing raw materials for preparing yttrium aluminum garnet with raw materials of doping elements, pressing the mixed raw materials into a cake material, and carrying out sintering to obtain a YAG polycrystalline cake material; heating the obtained YAG polycrystalline cake material to a molten state, placing the molten material in a mixed atmosphere of oxygen and inert gas for oxygen diffusion, and then carrying out liquid purification; adding a seed crystal into the molten raw materials subjected to the liquid purification, and carrying out crystal growth by a Czochralski method; and after crystal growth is finished, lifting a growncrystal to the liquid surface, and carrying out cooling to obtain the YAG laser crystal. The preparation method can be used to prepare the YAG laser crystal with high quality, the diameter of the YAGlaser crystal can reach 100 mm, the effective length can reach 200 mm, the doping concentration of crystal active ions is uniform, crystal defects are few, the core is small, the effective utilizationrate of the crystal is greatly improved, and large-size laser slabs and discs can be conveniently processed by cutting. Meanwhile, the process steps of the preparation method is simplified, and costis reduced.

Owner:SHANGHAI ADVANCED SILICON TECH CO LTD

A kind of preparation method of supersaturated doped semiconductor thin film

InactiveCN103268852BUniform doping concentrationImprove convenienceSemiconductor/solid-state device manufacturingUltra fastSilicon thin film

The invention discloses a method for preparing a supersaturated-doping semiconductor thin film. The method includes the following steps: step one, a substrate is chosen; step two, the surface of the substrate is cleaned up; step three, at a low growth temperature, a semiconductor amorphous thin film is deposited on the surface of the substrate, wherein through control over a deposition speed ratio of atoms, a supersaturated-doping semiconductor amorphous thin film is obtained; step four, laser annealing is carried out on the supersaturated-doping semiconductor amorphous thin film by the utilization of ultra-fast lasers, and the preparation of the supersaturated-doping semiconductor thin film is completed. According to the preparation method, the molecular beam epitaxy technology is used for preparing the supersaturated-doping thin film which is even in doping concentration. Depth distribution of impurities in the prepared supersaturated-doping silicon thin film is very even.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

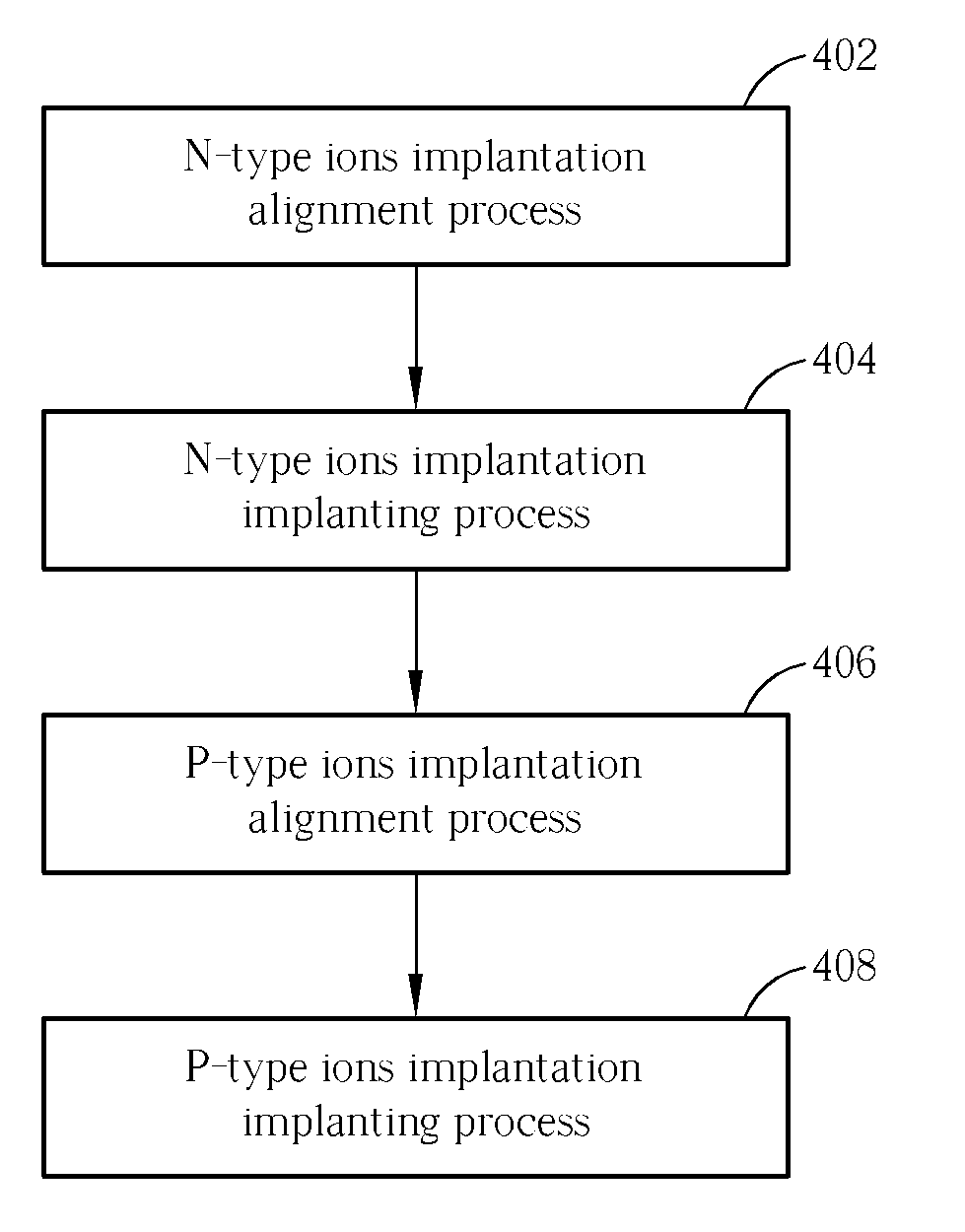

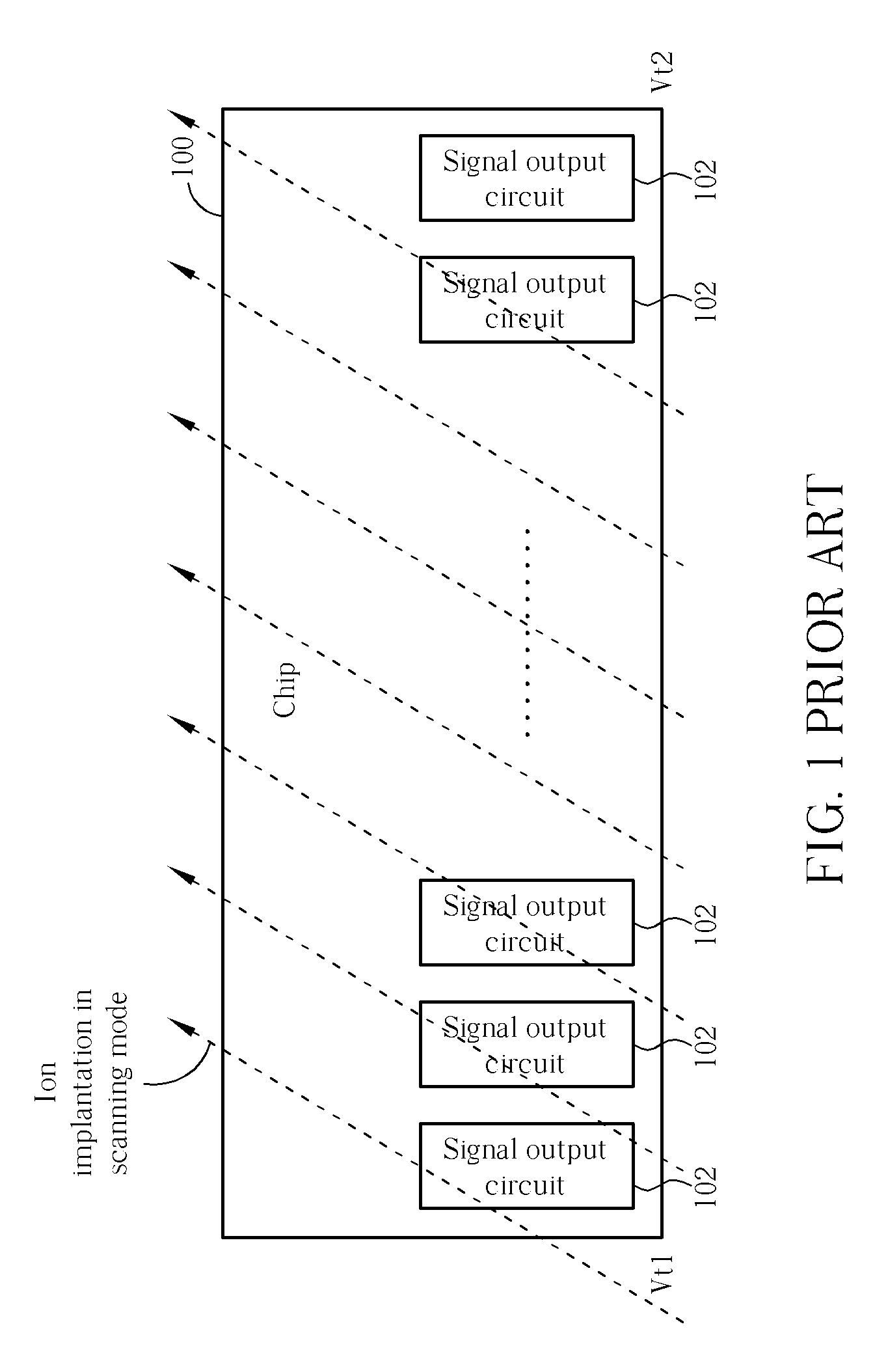

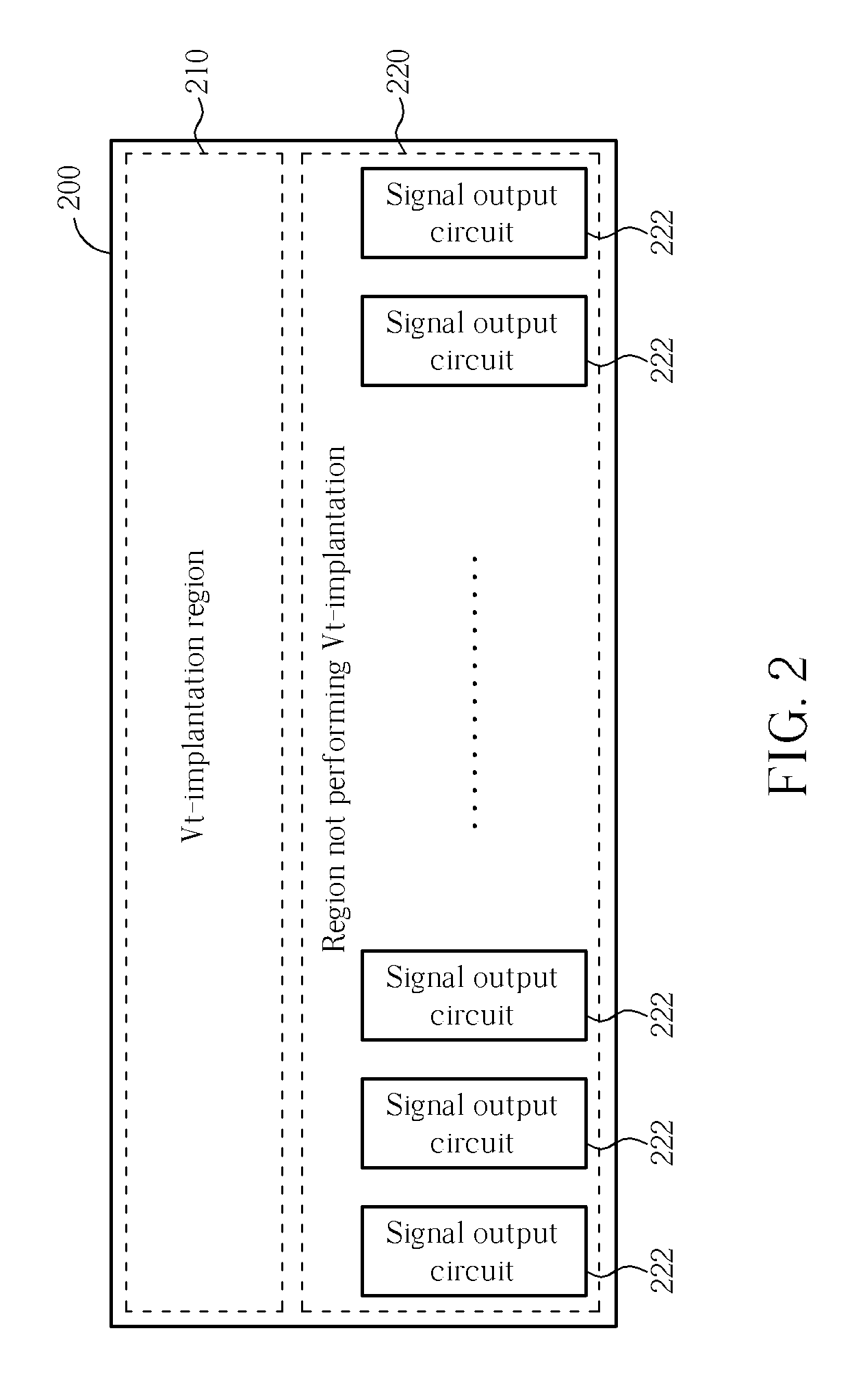

Method for manufacturing integrated circuit and semiconductor structure of integrated circuit

InactiveUS20090166796A1Uniform doping concentrationStable output voltageTransistorSemiconductor/solid-state device detailsSemiconductor structureSingle ion

A method for manufacturing an integrated circuit includes: performing ion implantation on a wafer to make a chip in the wafer have an original doping concentration; dividing the chip into a plurality of regions; and controlling at least one region of plurality of the regions to not have further ion implantation performed thereon, thereby making the region only have single ion implantation performed thereon utilize the original doping concentration as a doping concentration of N-wells or P-wells of transistors in the region. Additionally, the region corresponds to signal output circuits of the integrated circuit.

Owner:UNITED MICROELECTRONICS CORP

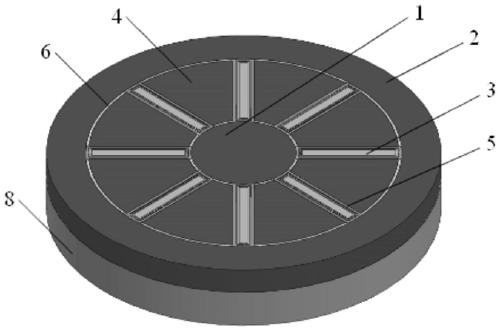

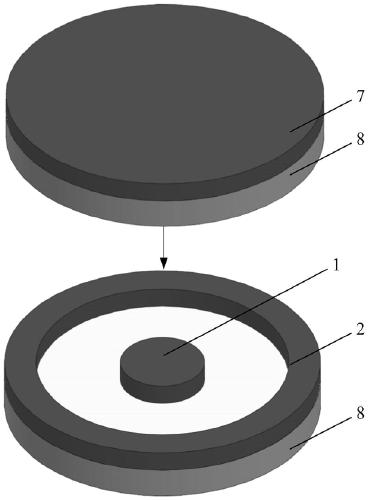

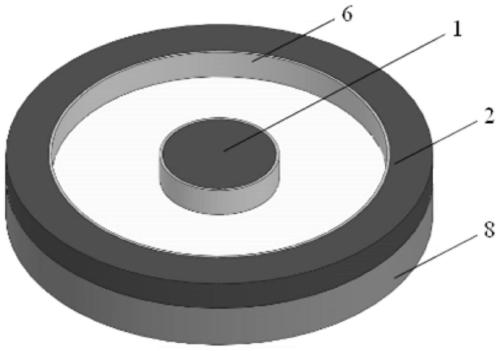

MOS device with annular channel region and preparation method thereof

ActiveCN111244160AStretched areaIncrease saturation currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate controlMaterials science

The invention discloses an MOS device with an annular channel region and a preparation method of the MOS device, belongs to the technical field of MOS devices, and solves the problems of short channeleffect, gate control capability and saturation current reduction of a planar MOS device with a small size (such as nanoscale) in the prior art. The MOS device comprises a source electrode, a drain electrode, a grid electrode and a channel region, the drain electrode is located on the periphery of the source electrode, the channel region is located between the source electrode and the drain electrode, and the channel region is annular; and a plurality of channels are formed in the surface of the channel region in the direction from the source to the drain, and the grid is located in the channels. The preparation method comprises the following steps: forming a source electrode and a drain electrode; forming a channel region between the source electrode and the drain electrode; etching the surface of the channel region along the direction from the source electrode to the drain electrode, and extending a channel material to form a channel; and forming a gate in the channel. According to the MOS device and the preparation method thereof, the area of a current channel can be expanded, and the saturation current is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for enhancing reliability of SONOS (Silicon Oxide Nitride Oxide Semiconductor) flash memory device by means of selective epitaxy

ActiveCN102117779BImprove reliabilityIncrease reliability lifeSolid-state devicesSemiconductor/solid-state device manufacturingIn situ dopingSilicon oxide

The invention discloses a method for enhancing the reliability of an SONOS (Silicon Oxide Nitride Oxide Semiconductor) flash memory device by means of selective epitaxy, which comprises the following steps: step 1, growing an epitaxial doping layer on a silicon substrate by adopting a selective epitaxial process; step 2, growing a tunneling oxidation layer on the epitaxial doping layer; step 3, growing a silicon oxynitride trap layer on the tunneling oxidation layer, and simultaneously carrying out in-situ doping on the silicon oxynitride trap layer by using N2O to form a silicon oxynitride mixture to serve as a medium for storing charges; and step 4, growing a high-temperature thermal-oxidation layer on the silicon oxynitride trap layer. In the method disclosed by the invention, an erasing voltage is regulated by means of selective epitaxial doping growth instead of ion implantation so as to avoid the damage to a silicon surface, thus the reliability of the SONOS flash memory device is improved and the service life of the SONOS flash memory device is prolonged.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

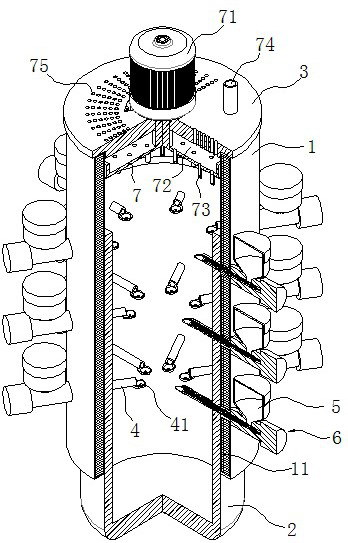

Silicon carbide crystal ingot growth device and method

PendingCN114737249AAvoid the problem of sequential sublimationImprove uniformityPolycrystalline material growthFrom condensed vaporsCarbide siliconDopant

The invention discloses a silicon carbide crystal ingot growing device, and relates to the technical field of silicon carbide crystal ingots, the silicon carbide crystal ingot growing device comprises a cylinder body, a heating liner is arranged in the cylinder body, and a cover body is arranged on the upper part of the cylinder body; a plurality of feeding pipes are arranged on the barrel in a penetrating manner, one end of each feeding pipe penetrates through the heating inner container and extends into the heating inner container, and a crucible is fixed to the end of each feeding pipe; the plurality of crucibles are arranged in the heating inner container to form an inverted heap-shaped structure; each feeding pipe is connected with a material storage box, and a feeding mechanism is arranged between each material storage box and the corresponding feeding pipe; a rotatable silicon carbide crystal ingot growth plate is arranged below the cover body, and a cooling tank is arranged above the silicon carbide crystal ingot growth plate. The invention further provides a method for growing the silicon carbide crystal ingot. The silicon carbide crystal ingot grows in a sublimation mode between silicon carbide and a doping substance. According to the invention, the silicon carbide and the dopant can be synchronously sublimated and mixed in a three-dimensional distribution manner, the semi-insulating silicon carbide crystal ingot with more uniform doping concentration is generated, and the quality of the semi-insulating silicon carbide crystal ingot is improved.

Owner:安徽微芯长江半导体材料有限公司

A crystal growth method based on vgf method for vapor phase doping

ActiveCN111041550BImprove uniformityIncrease crystallization ratePolycrystalline material growthFrom frozen solutionsDopantCrucible

The invention discloses a crystal growth method based on a VFG method for gas phase doping, and relates to the technical field of crystal preparation. The method includes the following steps: S1, putting polycrystals, seed crystals, and red phosphorus into the crucible for crystal growth; S2, placing the crucible in a quartz tube; it is characterized in that, after step S2, it also includes, S3, connecting the doped A quartz sealing cap of the dopant is covered on the quartz tube, and the dopant is located in the quartz tube, and the dopant is not in contact with the polycrystal, the seed crystal and the red phosphorus; The quartz tube is sealed. Through the improvement of the quartz capping and heating process used for VGF crystal growth, the dopant is separated from other raw materials for crystal growth, and the dopant Fe element enters the melt through gas phase diffusion to achieve uniform doping concentration. The uniformity of the crystal resistivity and the crystal formation rate are improved; meanwhile, the doping amount of the dopant Fe can be reduced, and the cost is saved.

Owner:珠海鼎泰芯源晶体有限公司

ldmos device and its manufacturing method

ActiveCN111987164BLower specific on-resistanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSElectrical resistance and conductance

This patent application discloses an LDMOS device and a manufacturing method thereof. The manufacturing method includes: forming an epitaxial layer over a substrate, implanting a drift region and a well region in the epitaxial layer; forming a gate structure over part of the well region; A first mask with a first opening is formed above the epitaxial layer, and an inversion region is formed by implanting at an oblique angle of the first opening. The inversion region is doped opposite to the drain region in the drift region and is symmetrical about the drain region. At the same time, An additional doping region of the same doping type as the well region is formed in the well region through the second opening of the first mask; then the source region and the drain region are also doped in the first opening and the second opening. The advantage of this patent is that the same mask is used to form the drain region, the inversion region in the drift region, and the additional doping region in the well region with the same doping concentration as the well region, which can not only effectively increase the breakdown voltage of the device, but also reduce the The on-resistance of the device is improved, and the self-protection capability of the device is improved without adding any additional cost.

Owner:JOULWATT TECH INC LTD

Formation method of semiconductor structure

ActiveCN106328528BInhibit injectionAvoid dopant implantationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureIsolation layer

The invention discloses a semiconductor structure forming method. The method comprises steps: a substrate with a first area and an adjacent second area is provided, wherein the surface of the substrate in the first area is provided with a first fin part and an adjacent second fin part, the surface of the substrate is provided with an isolation layer, and the minimal distance between the side wall of the first fin part and the side wall of the second fin part is a first distance; a mask layer is formed on the surface of the isolation layer, wherein an opening for enabling the first area to be exposed is arranged in the mask layer, the opening is provided with a first side wall and an opposite second side wall, the minimal distance between the side wall of the first fin part and the first side wall is larger than the minimal distance between the side wall of the second fin part and the first side wall, and the value obtained by dividing the thickness of the mask layer by the minimal distance between the side wall of the first fin part and the first side wall is larger than that obtained by dividing the distance between the top of the second fin part and the surface of the isolation layer by the first distance; and first lightly-doped injection with a first injection angle is carried out on the first fin part from one side of the first side wall, wherein the tangent value of the first injection angle is smaller than or equal to the value obtained of dividing the thickness of the mask layer by the second distance. The formed semiconductor structure is stable in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

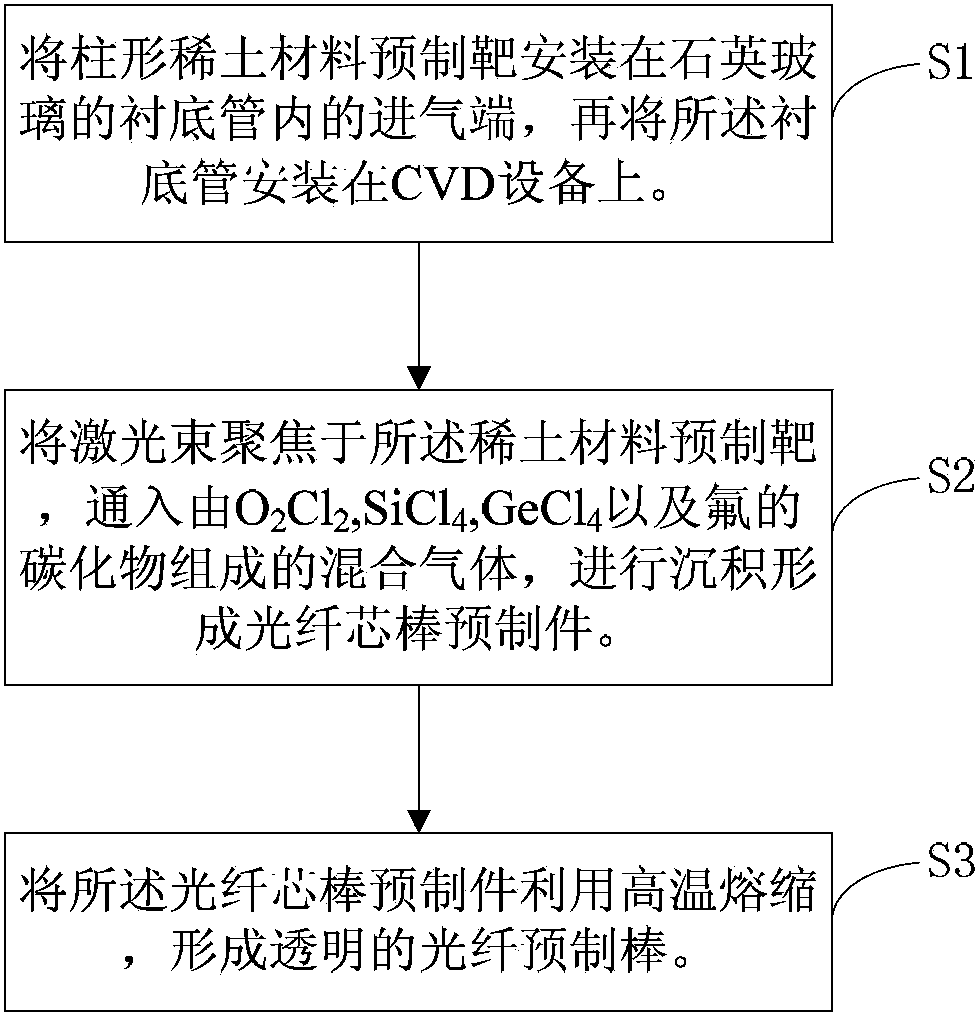

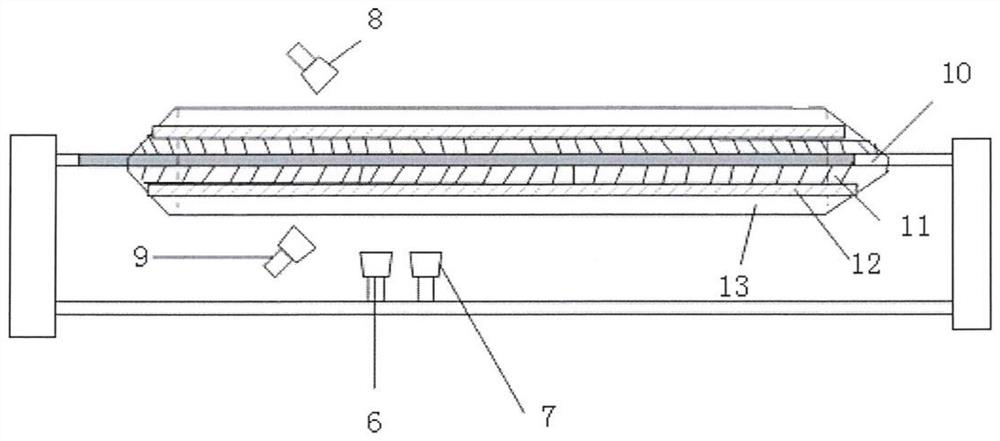

Manufacturing method of rare earth-doped optical fiber preformed rod

A manufacturing method of a rare earth-doped optical fiber preformed rod relates to the field of optical fiber preformed rods, and comprises the following steps: S1, mounting a cylindrical rare earth material preformed target rod at a gas inlet end in a quartz glass substrate tube, mounting the substrate tube on a chemical vapor deposition device; S2, focusing laser on the rare earth material preformed target rod, introducing mixed gas composed of oxygen, chlorine, silicon tetrachloride gas, germanium tetrachloride gas, and carbides of fluorine, performing deposition to form an optical fiber core rod preform; S3, melting the optical fiber core rod preform for contraction at a high temperature to form the transparent optical fiber preformed rod. The method increases the diameter of the optical fiber preformed rod, greatly improves the production manufacturing efficiency and the rare earth ion doping uniformity of the rare earth-doped optical fiber preformed rod, reduces the content of ineffective impurities of the optical fiber preformed rod, also reduces the production cost, and is suitable for popularization of large-scale production.

Owner:RUIGUANG TELECOMM TECH CO LTD

A solution method for preparing crystalline silicon solar cells

ActiveCN110416355BImprove passivation functionUniform doping concentrationFinal product manufactureSemiconductor/solid-state device manufacturingO-Phosphoric AcidPolyethylene glycol

The invention discloses a process for preparing a crystalline silicon solar cell by a solution method. The method comprises the steps: adding ethyl alcohol, polyethylene glycol, vinyltrimethoxysilaneand the like into a phosphoric acid solution to serve as a phosphorus diffusion solution source, and uniformly coating the surface of a silicon wafer with diffusion liquid through an ultrasonic atomization spraying method; then diffusing phosphorus at the high temperature to obtain the uniform doping concentration of the surface. According to the invention, the solution spraying method is adoptedto prepare a titanium dioxide anti-reflection film to replace a silicon nitride anti-reflection film prepared by a PECVD method, and a microemulsion composed of anionic polyacrylamide (APAM), isopropanol and the like is added into a titanium tetrachloride solution to serve as a precursor solution of the titanium dioxide film, so that the passivation function of the film on the silicon surface is improved.

Owner:ZHEJIANG NORMAL UNIVERSITY

A kind of single-mode optical fiber and its preparation method

ActiveCN110794509BReduce lossIncrease the effective areaGlass optical fibreGlass making apparatusRelative refractive indexBare fiber

A single-mode optical fiber and its preparation method. The bare optical fiber includes a core layer and a cladding layer. The core layer includes a first core layer, a second core layer, and an inner cladding layer. The relative refractive index difference of the first core layer is 0.2%≤Δ 1 ≤0.35%, the relative refractive index difference of the second core layer is 0.15%≤Δ 2 ≤0.25%, the refractive index radius of the inner cladding is 24μm~36μm, and the relative refractive index difference of the inner cladding is -0.12%≤Δ 3 ≤0%. The cladding, including the depressed cladding and the outer cladding, the relative refractive index difference of the depressed cladding is -0.40%≤Δ 4 ≤‑0.28%, the outer cladding is high hardness pure quartz casing. The two-stage sleeve and core rod are assembled and drawn on-line, and the optical fiber is annealed multiple times during the drawing process, and the surface of the optical fiber is coated with a low-modulus coating and a high-modulus coating on the outside to prepare a low-loss, large effective area, and high-strength optical fiber. The method is simple, the viscosity of the core rod can be adjusted according to the requirement, and there is no need to use a pure silicon core solution to reduce the attenuation of the optical fiber, which is conducive to large-scale production.

Owner:FASTEN HONGSHENG GRP CO LTD +1