MOS device with annular channel region and preparation method thereof

A MOS device and annular trench technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as gate control capability and saturation current drop, and achieve the effect of improving activation, eliminating damage and uniform size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

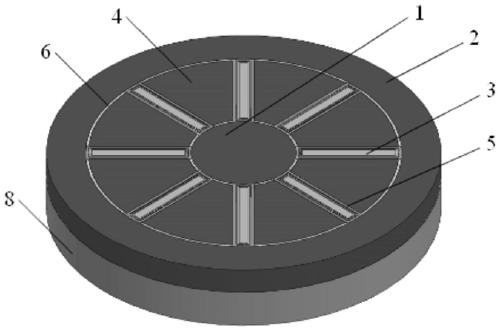

[0053] This embodiment provides a MOS device with an annular channel region, see figure 1 , which includes a substrate 8 and a source 1, a drain 2, a gate 3 and a channel region 4 arranged on the substrate 8, wherein the drain 2 is located at the periphery of the source 1, and the channel region 4 is located at the source 1 and the drain Between the poles 2, the shape of the channel region 4 is ring-shaped, along the direction from the source 1 to the drain 2, a plurality of channels 5 are provided on the surface of the channel region 4, and the side walls and bottoms of the channels 5 are channel functional areas. The gate 3 is located in the channel 5 .

[0054] Compared with the prior art, in the MOS device with an annular channel region provided in this embodiment, the channel region 4 is an annular channel region, and a channel is opened on the surface of the channel region 4 along the direction from the source 1 to the drain 2 5. The channel functional area is the sidew...

Embodiment 2

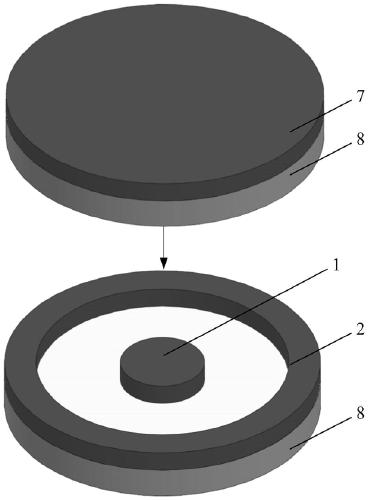

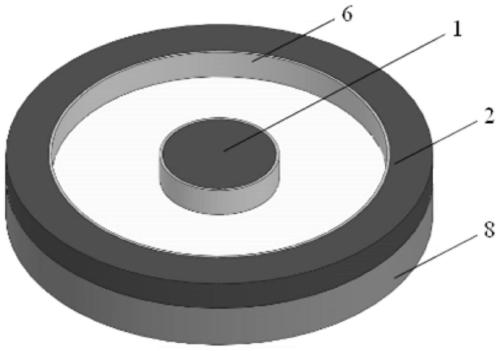

[0063] This embodiment provides a method for preparing a MOS device with an annular channel region, see Figure 2 to Figure 6 , for preparing the MOS device with an annular channel region provided in Example 1, the above preparation method includes the following steps:

[0064] Step 1: providing a substrate 8, forming a source 1 and a drain 2 on the surface of the substrate 8;

[0065] Step 2: epitaxially grow the channel material between the source 1 and the drain 2 to form the channel region 4, by means of chemical mechanical polishing (for example, thermal oxidation, the thermal oxidation temperature is 750°C-850°C, the thermal oxidation time 1min~10min) to smooth the surface, wherein the doping concentration is controlled at 1E16 / cm 3 ~1E18 / cm 3 (for example, 1E17 / cm 3 ~5E17 / cm 3 ), the doping type of the channel region 4 is opposite to that of the source 1 and the drain 2;

[0066] Step 3: Etching and epitaxial channel material (using SiCl 4 , SiH 2 Cl 2 as the ra...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More