Patents

Literature

97results about How to "Improved breakdown voltage characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

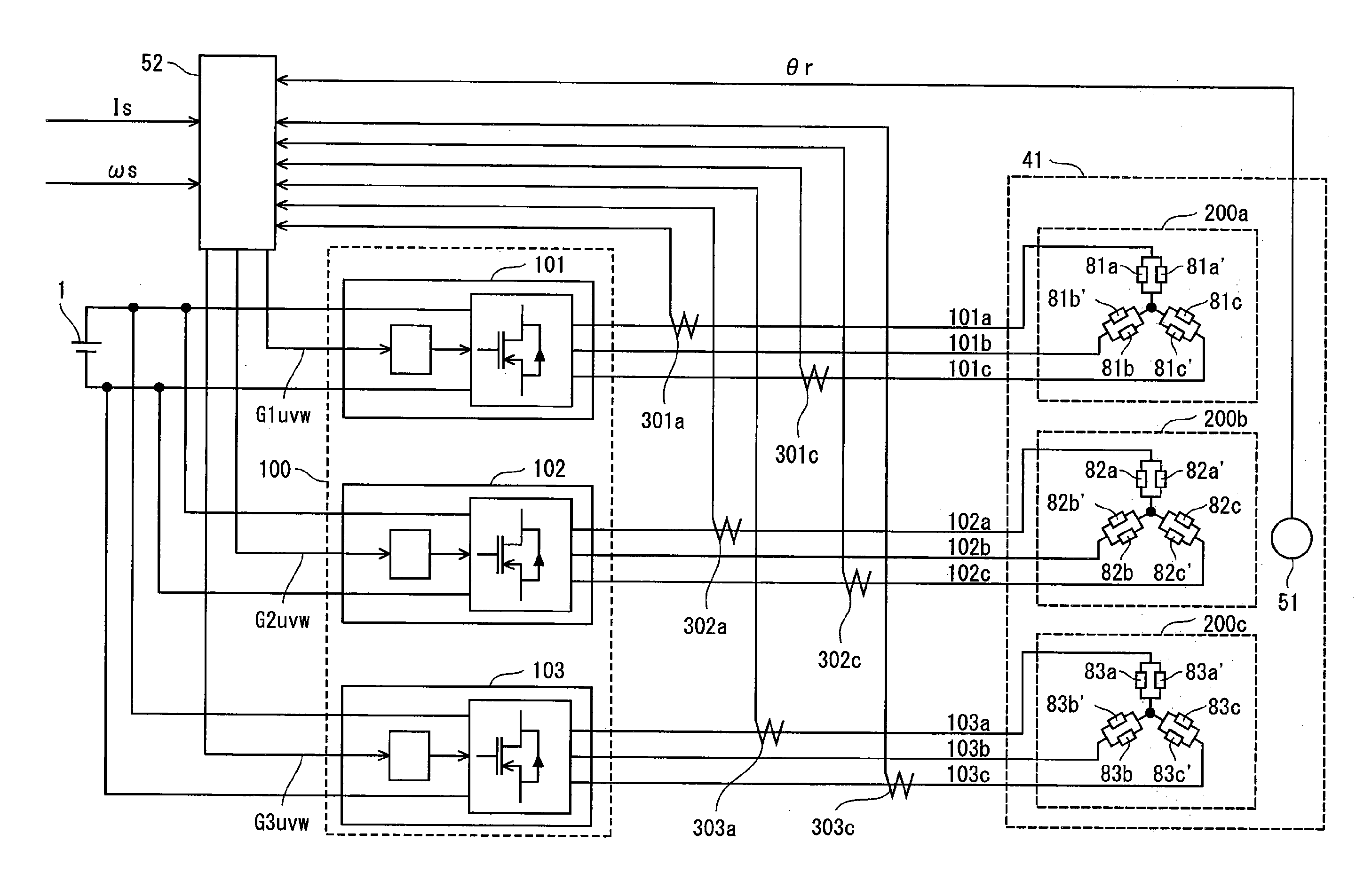

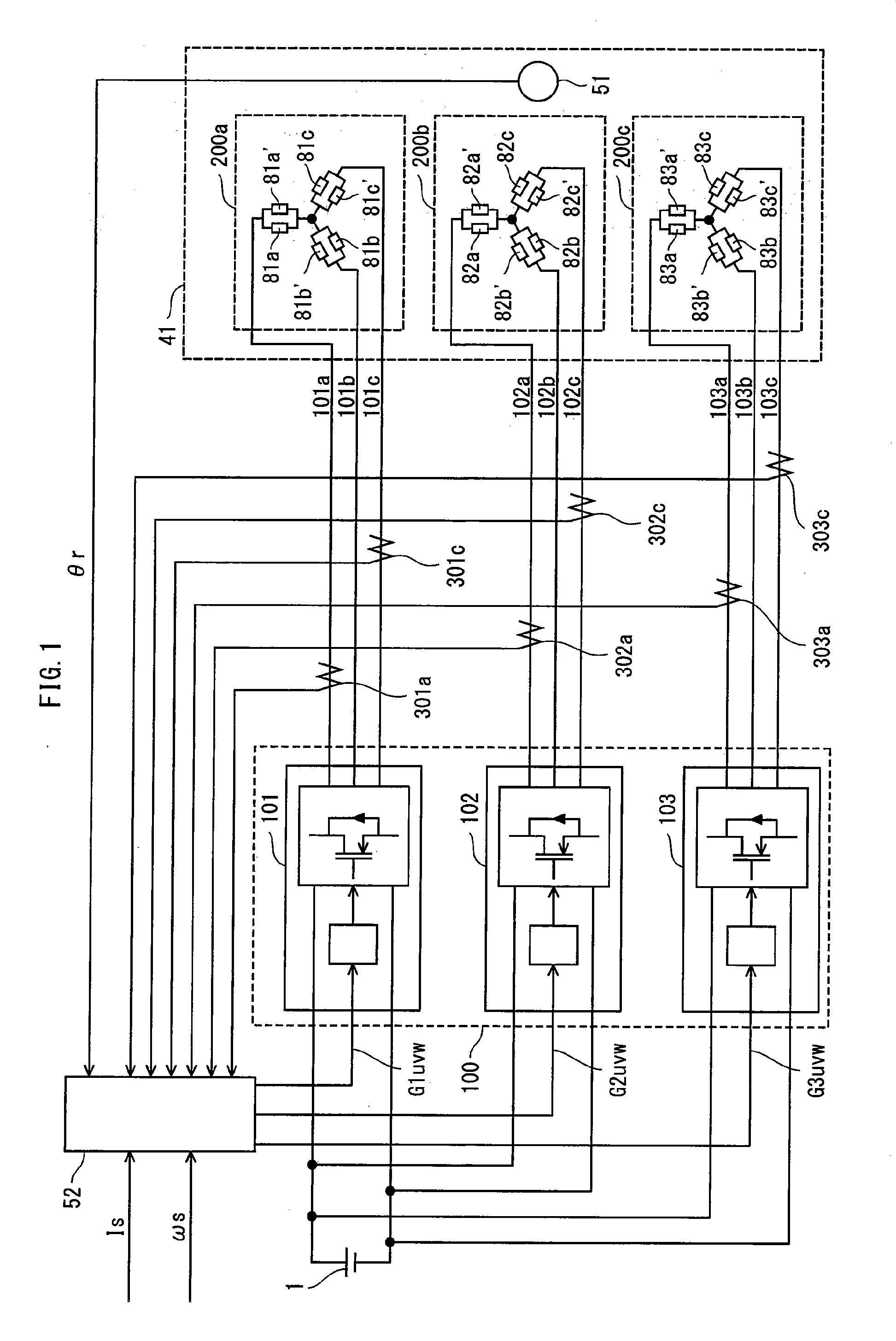

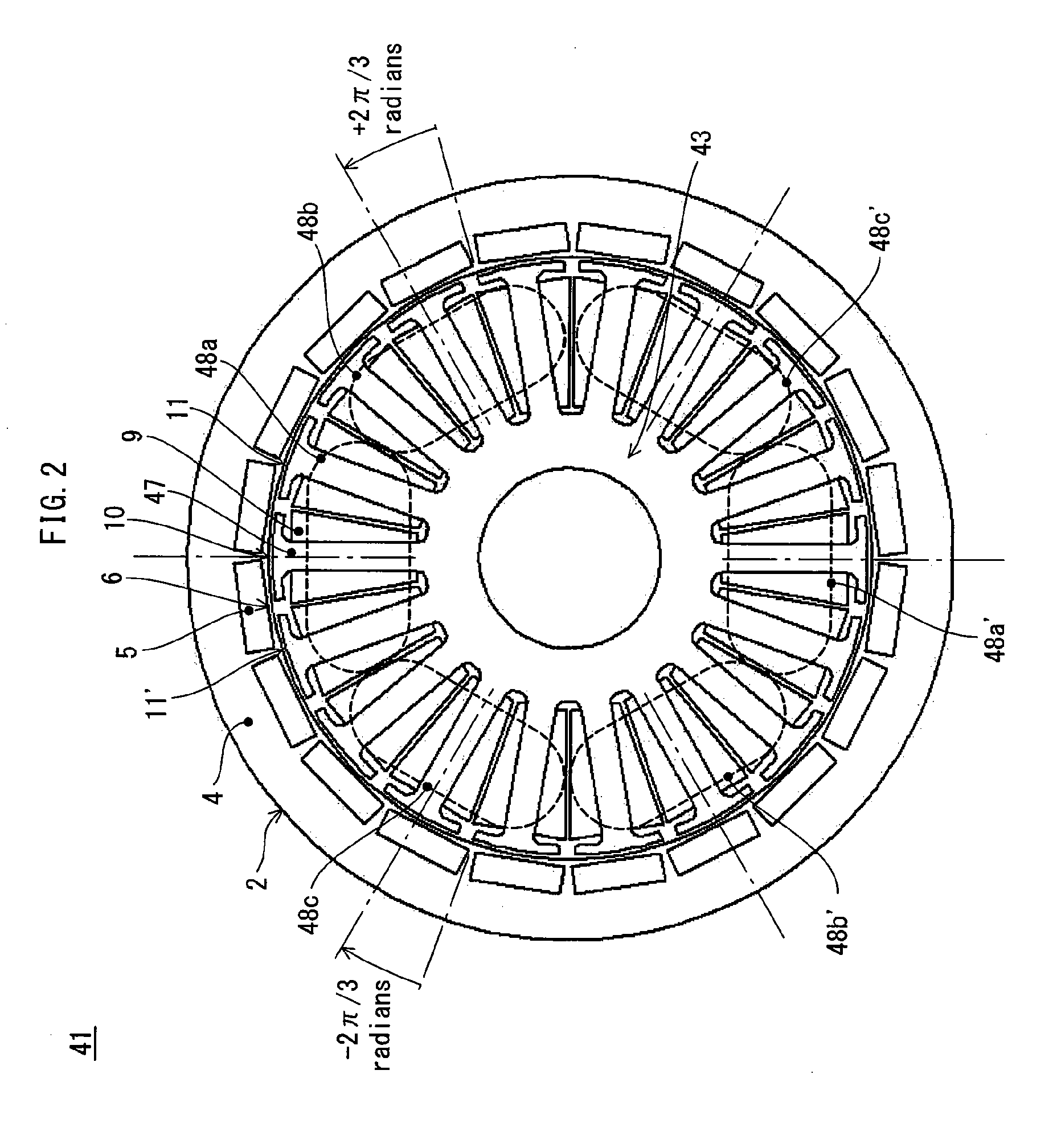

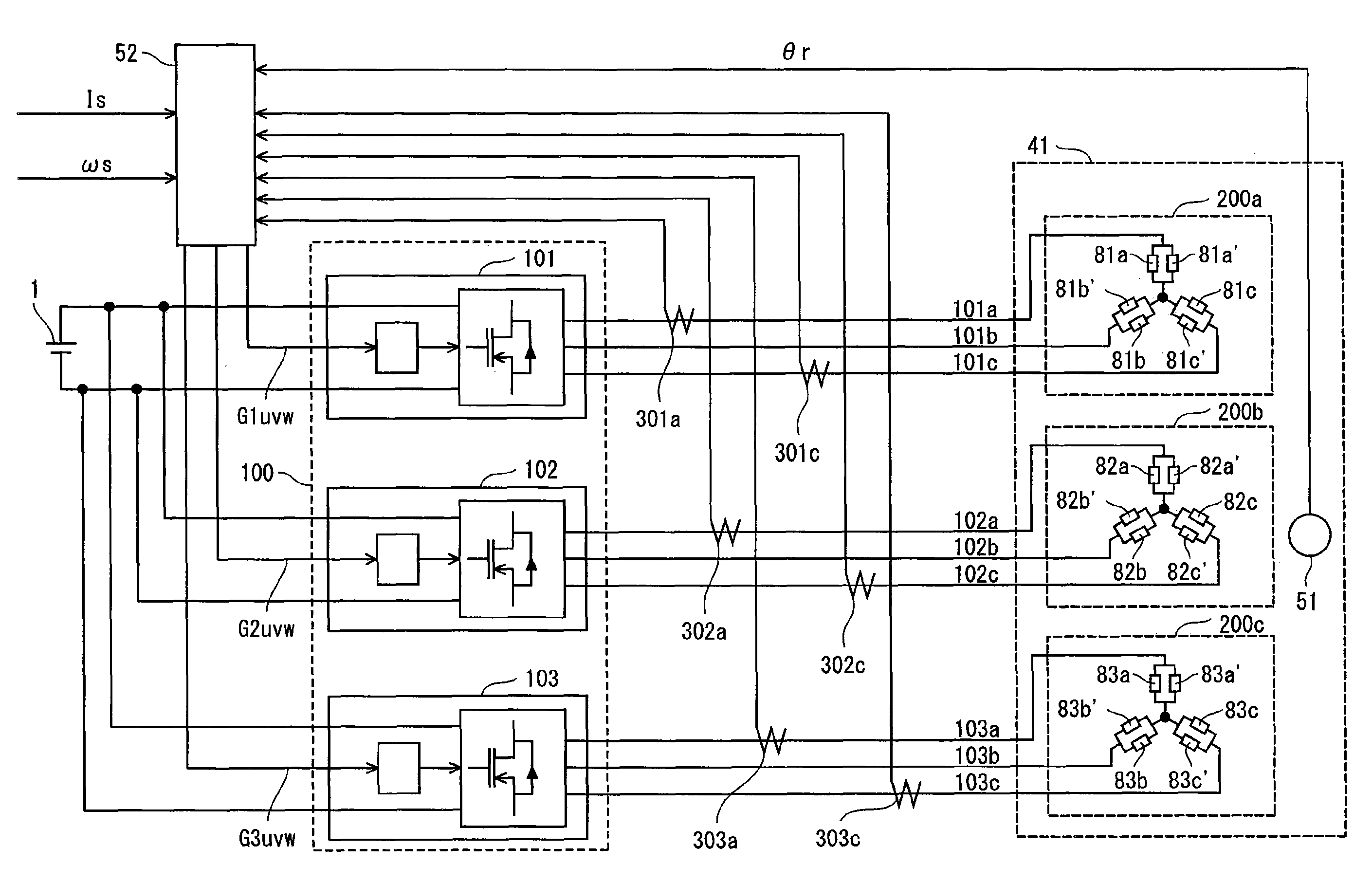

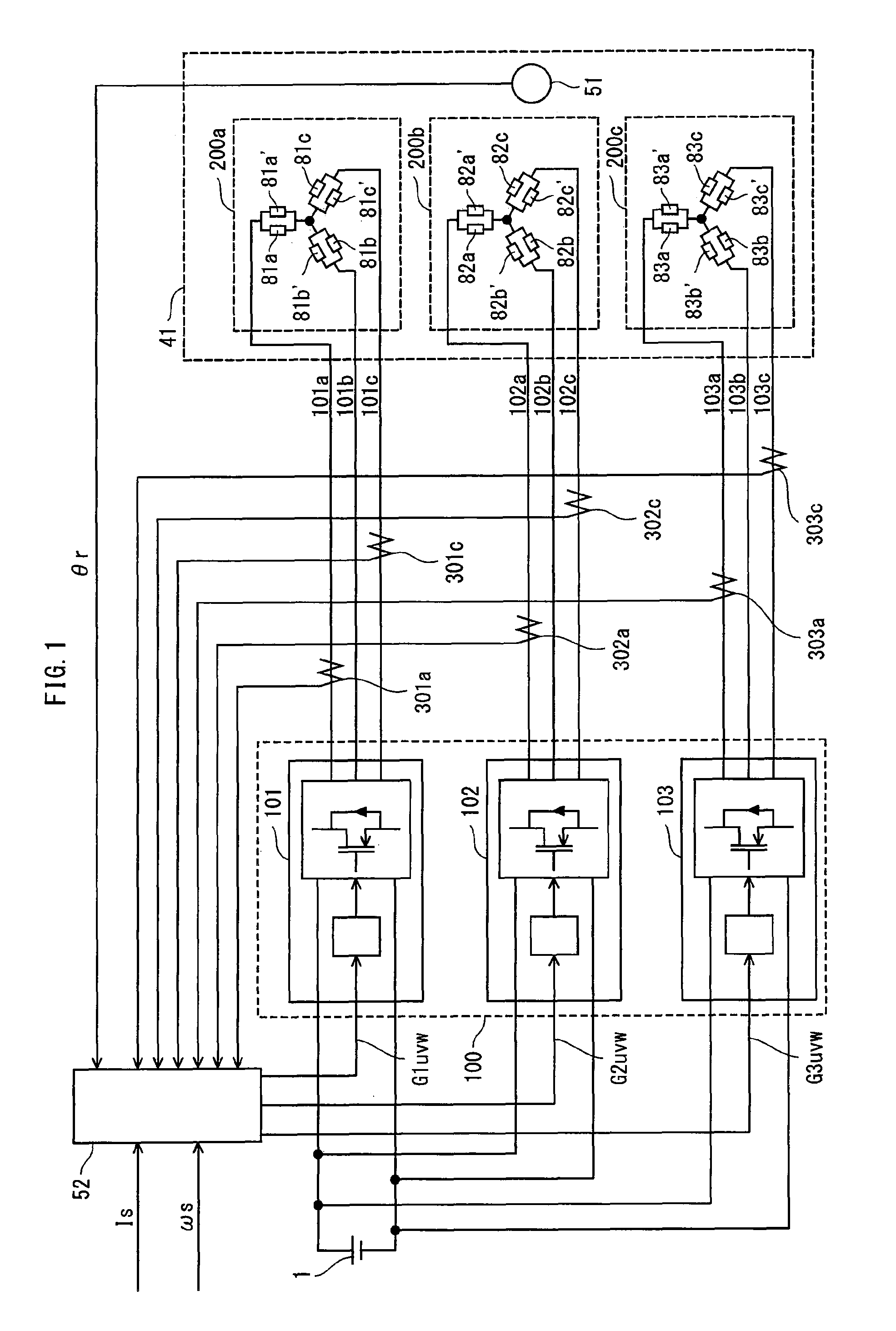

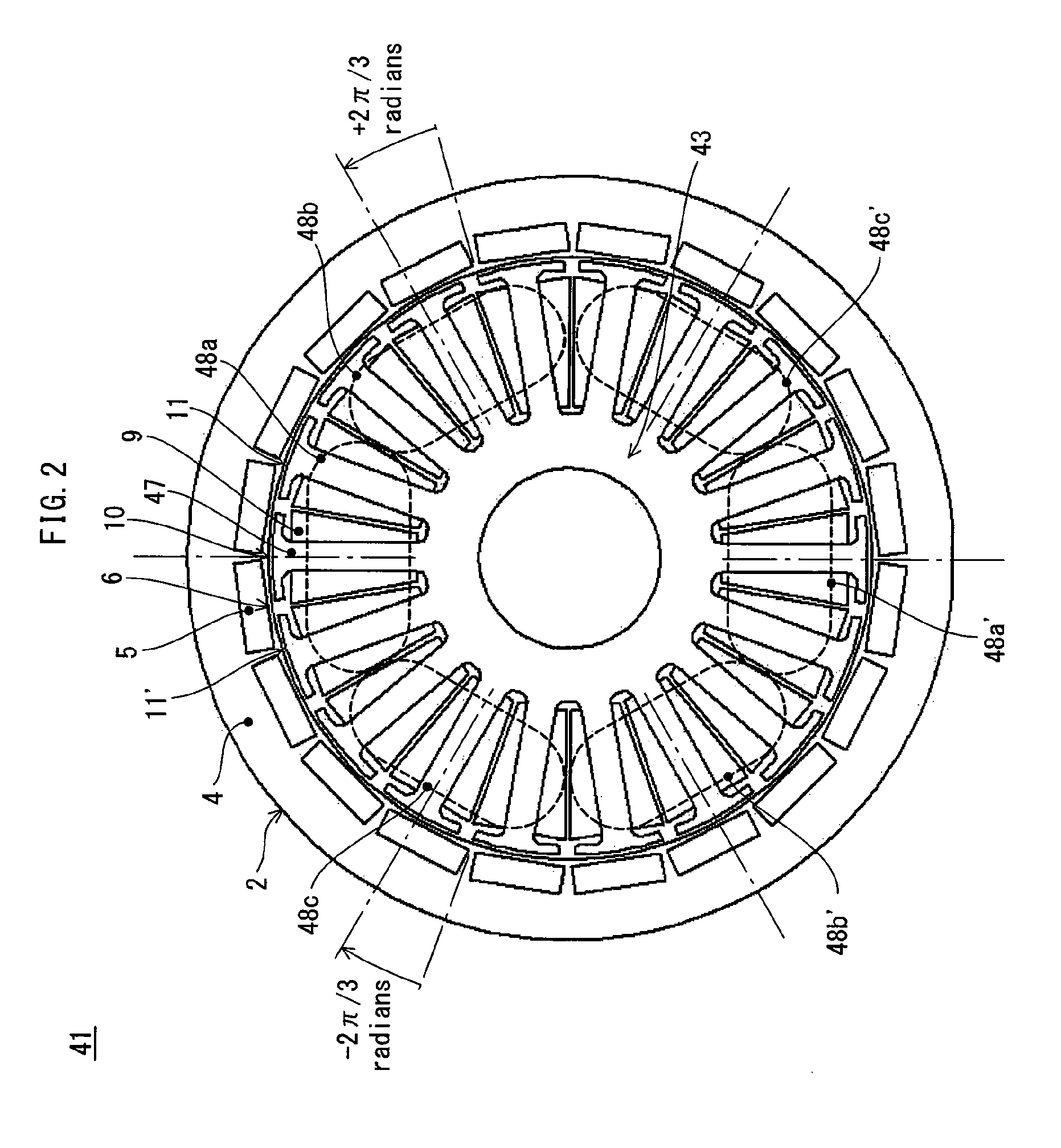

Synchronous electric motor drive system

ActiveUS20110057591A1Prevents degradation of inverter efficiencyPrevents an increase of iron lossesTorque ripple controlSynchronous motors startersSynchronous motorDC - Direct current

The present invention provides a synchronous motor drive system designed to realize reduced vibration and noise along with high output. The system includes: inverters 101, 102, and 103 for converting a direct current to a three-phase alternating current; a current application control unit 52 that controls operations of the three-phase inverters; and a synchronous motor 41 driven by three-phase alternating currents supplied from the three-phase inverters. The current application control unit 52 determines, for each three-phase inverter, a current phase angle and a current amount of a three-phase alternating current to output, and each inverter supplies a three-phase alternating current having the determined current phase angle and current amount to a different one of three-phase coil groups 200a to 200c.

Owner:PANASONIC CORP

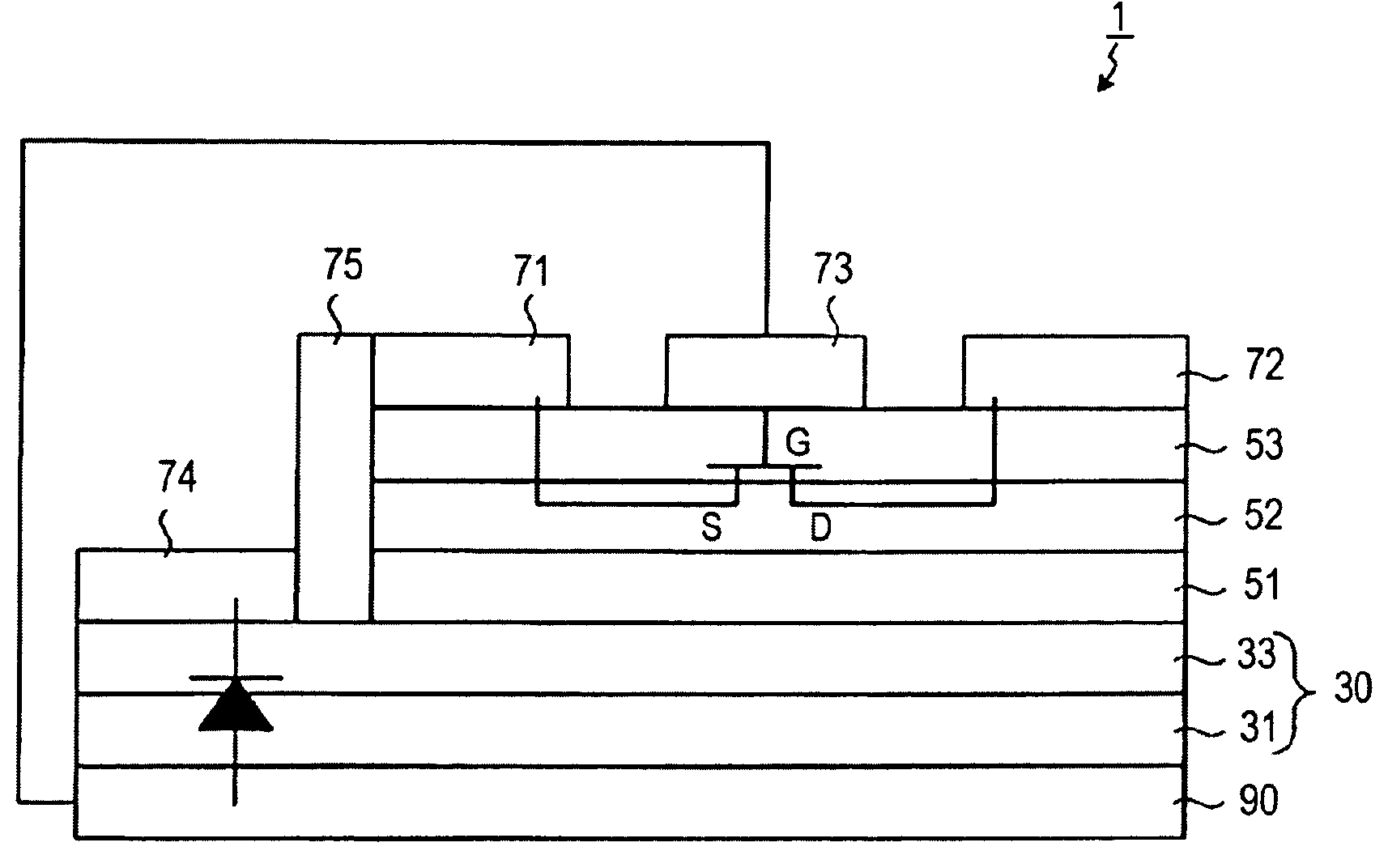

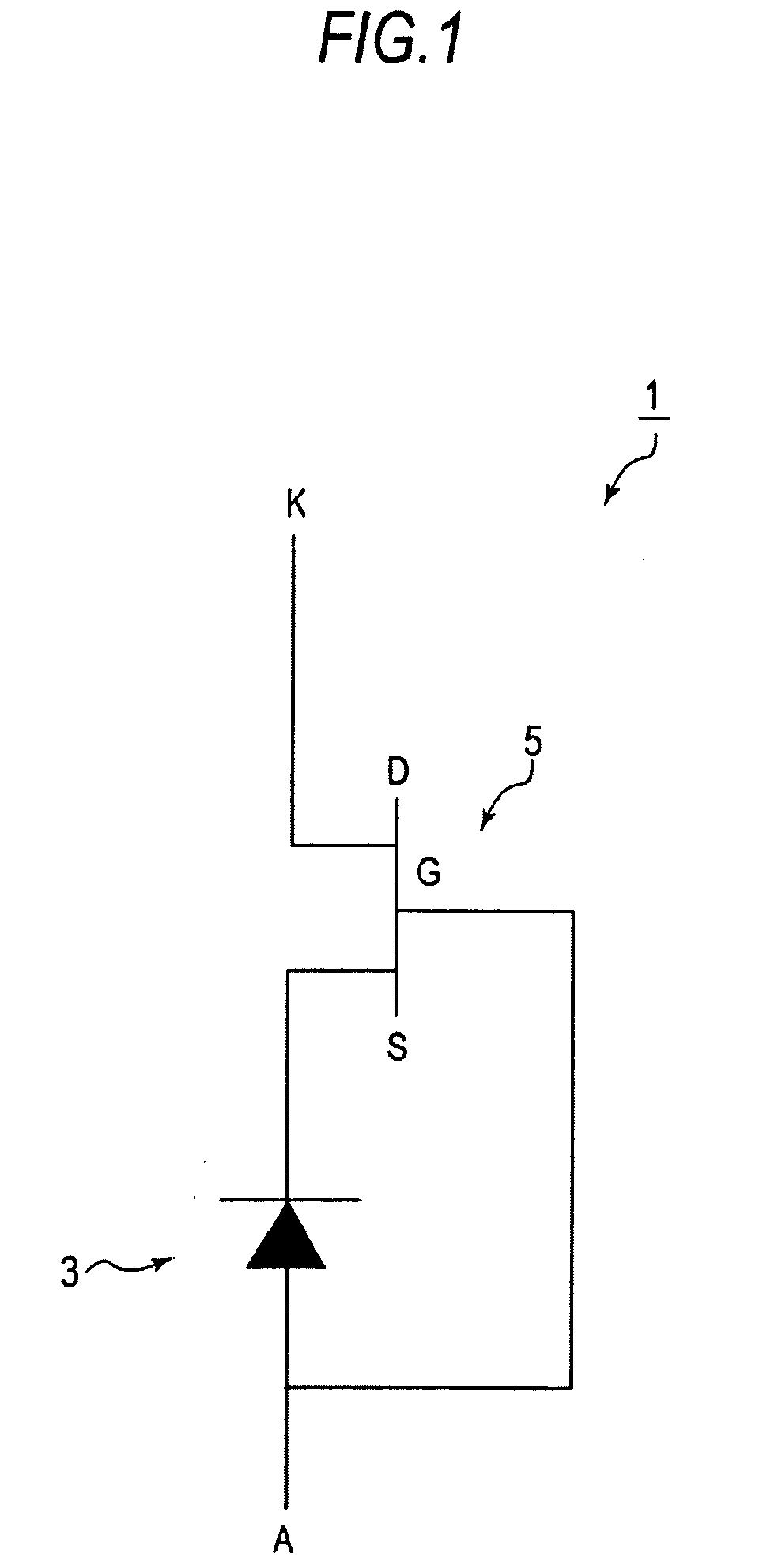

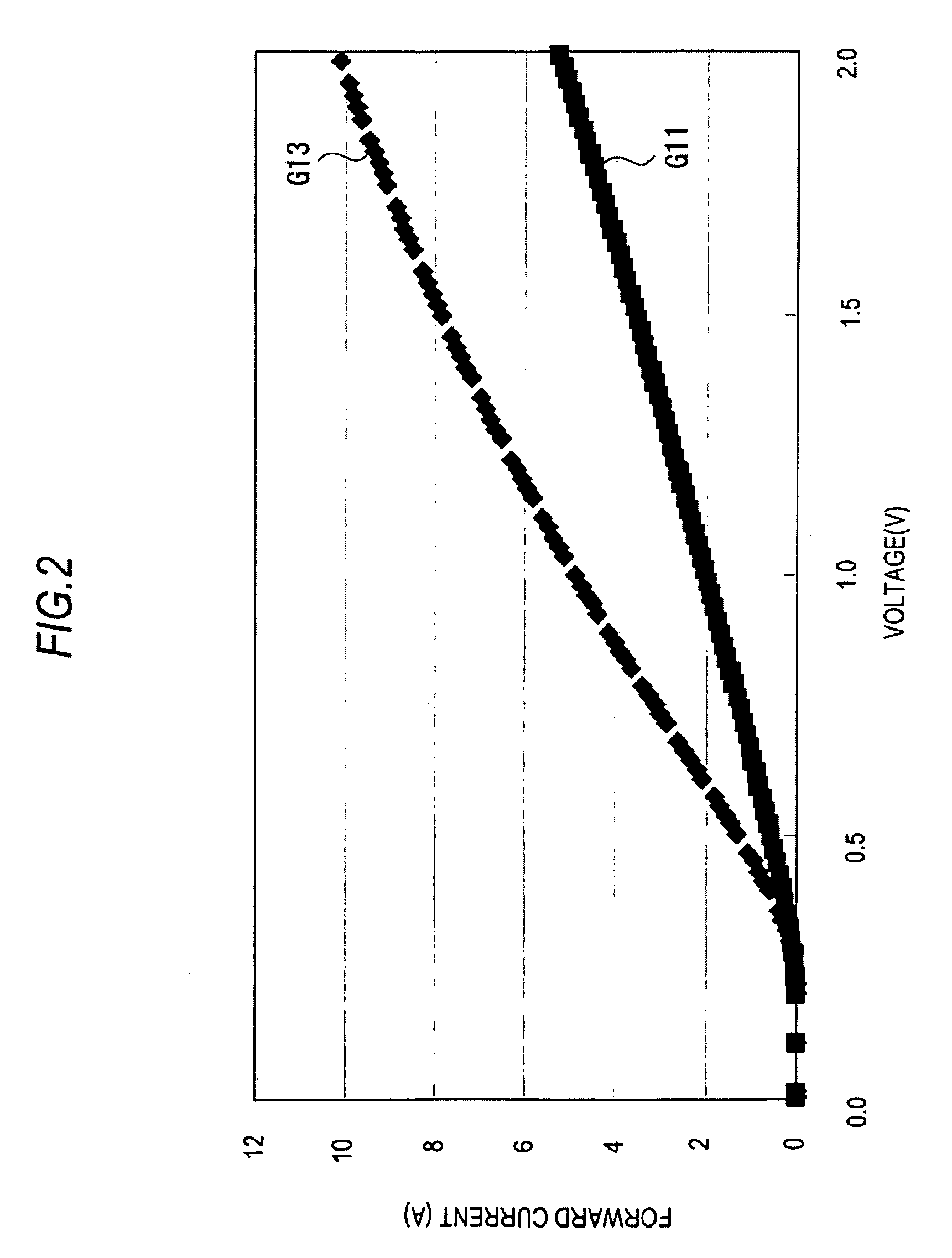

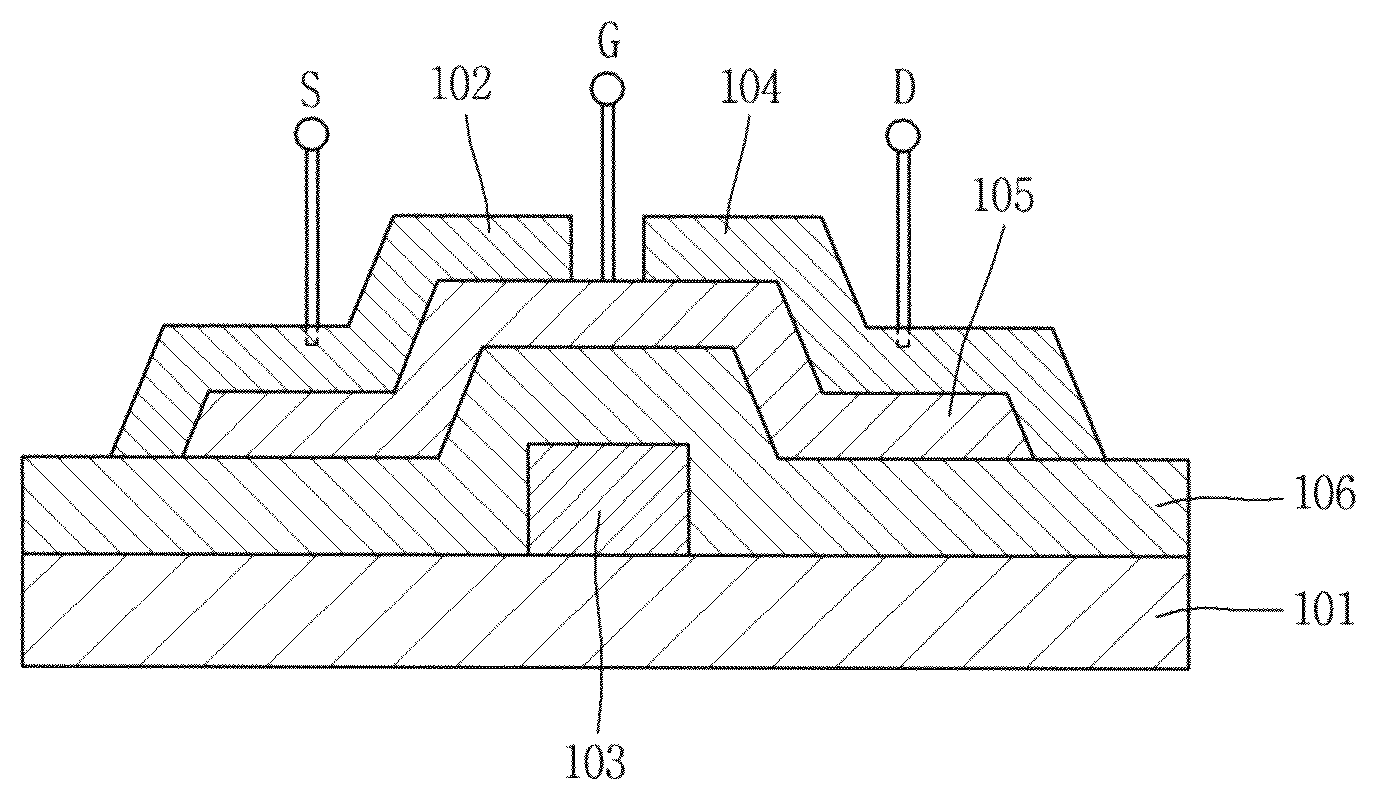

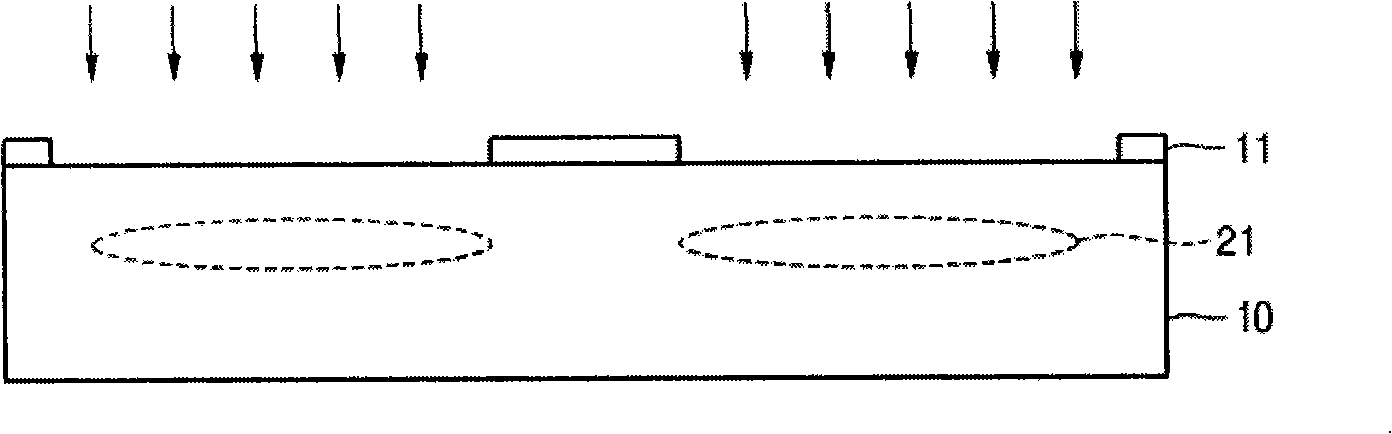

Semiconductor device

InactiveUS20090189191A1Improved breakdown voltage characteristicsLower on-resistanceTransistorSolid-state devicesField-effect transistorCathode electrode

A semiconductor device includes a field effect transistor formed of a GaN-based compound semiconductor and having a source electrode, a drain electrode, and a gate electrode, and a diode formed of a semiconductor material having a gandgap energy smaller than a bandgap energy of the GaN-based compound semiconductor. A cathode electrode and an anode electrode of the diode are electrically connected to the source electrode and the gate electrode of the field effect transistor, respectively.

Owner:FURUKAWA ELECTRIC CO LTD

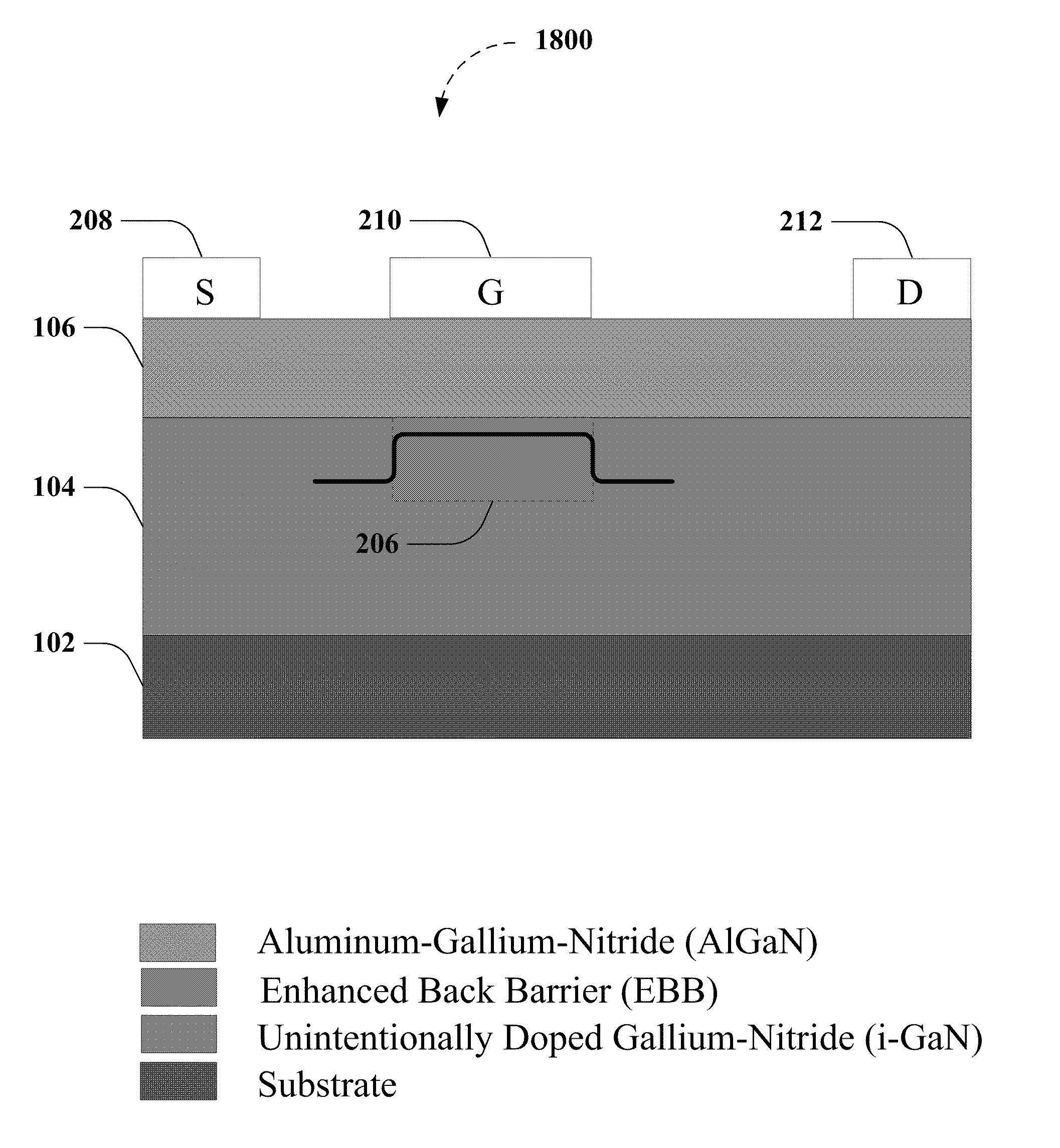

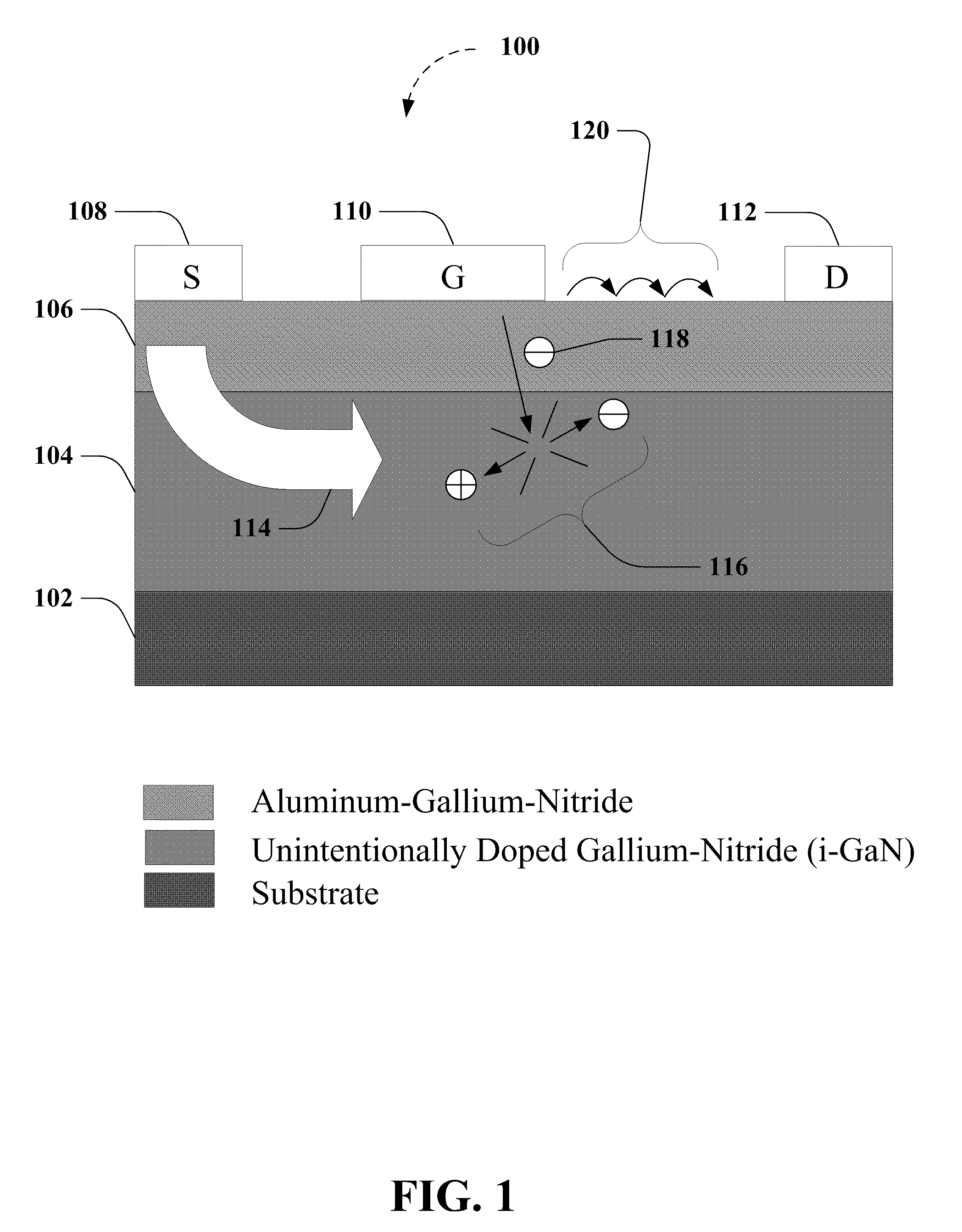

Aluminum gallium nitride/gallium nitride high electron mobility transistors

InactiveUS20100084687A1Improve electric field distributionImprove isolationSemiconductor/solid-state device manufacturingSemiconductor devicesElectron mobilityGallium nitride

Structures, devices and methods are provided for creating enhanced back barriers that improve the off-state breakdown and blocking characteristics in aluminum gallium nitride AlGaN / GaN high electron mobility transistors (HEMTs). In one aspect, selective fluorine ion implantation is employed when developing HEMTs to create the enhanced back barrier structures. By creating higher energy barriers at the back of the two-dimensional electron gas channel in the unintentionally doped GaN buffer, higher off-state breakdown voltage is advantageously provided and blocking capability is enhanced, while allowing for convenient and cost-effective post-epitaxial growth fabrication. Further non-limiting embodiments are provided that illustrate the advantages and flexibility of the disclosed structures.

Owner:THE HONG KONG UNIV OF SCI & TECH

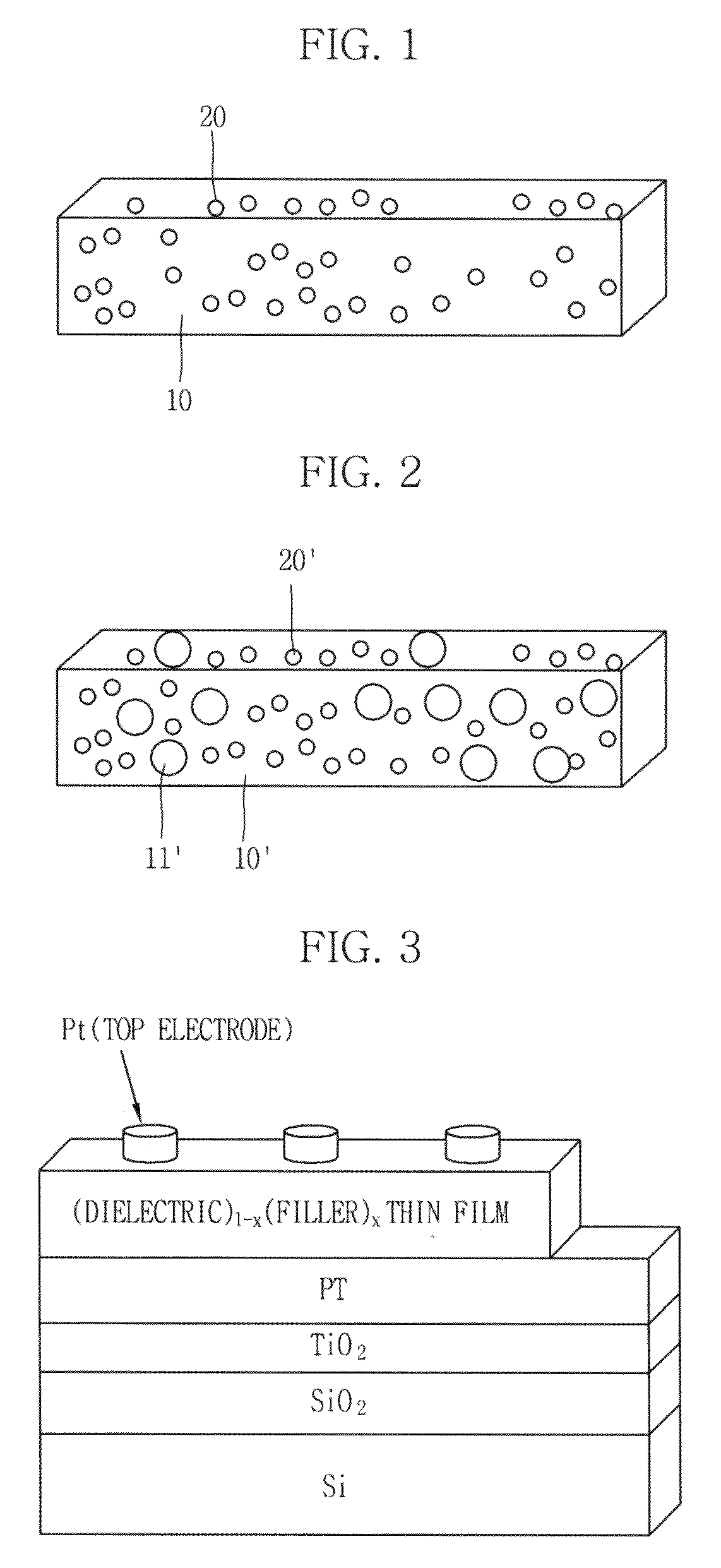

Composite dielectric thin film, capacitor and field effect transistor using the same, and each fabrication method thereof

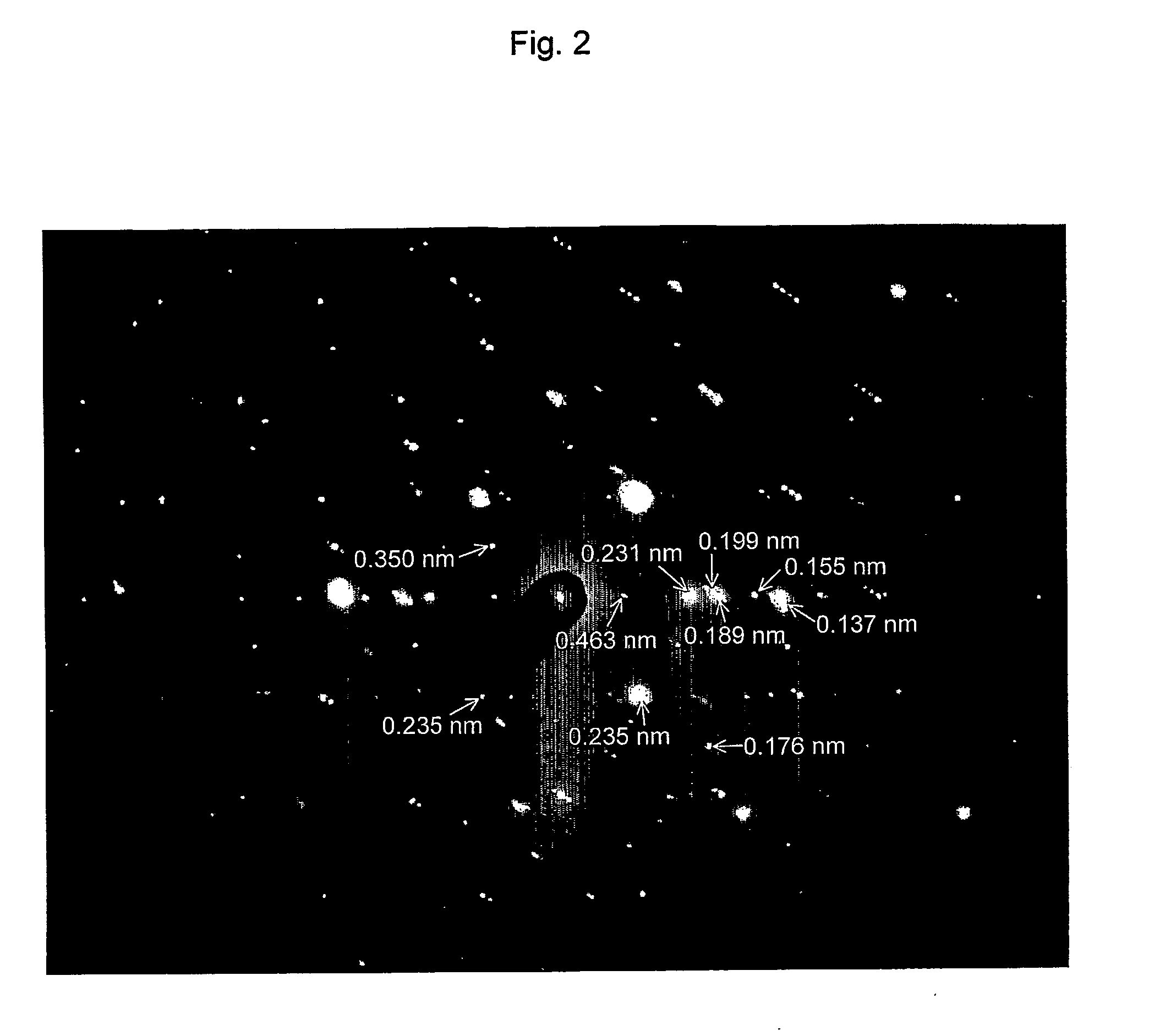

InactiveUS20090278211A1Improved breakdown voltage characteristicsImproved leakage current characteristicThin/thick film capacitorFixed capacitor dielectricNanometreLow leakage

a composite dielectric thin film capable of high dielectric constant, low leakage current characteristics, and high dielectric breakdown voltage while being deposited at a room temperature, a capacitor and a field effect transistor (FET) using the same, and their fabrication methods. The composite dielectric thin film is deposited at a room temperature or less than 200° C. and comprises crystalline or amorphous insulating filler uniformly distributed within an amorphous dielectric matrix or within an amorphous and partially nanocrystalline dielectric matrix.

Owner:KOREA INST OF SCI & TECH

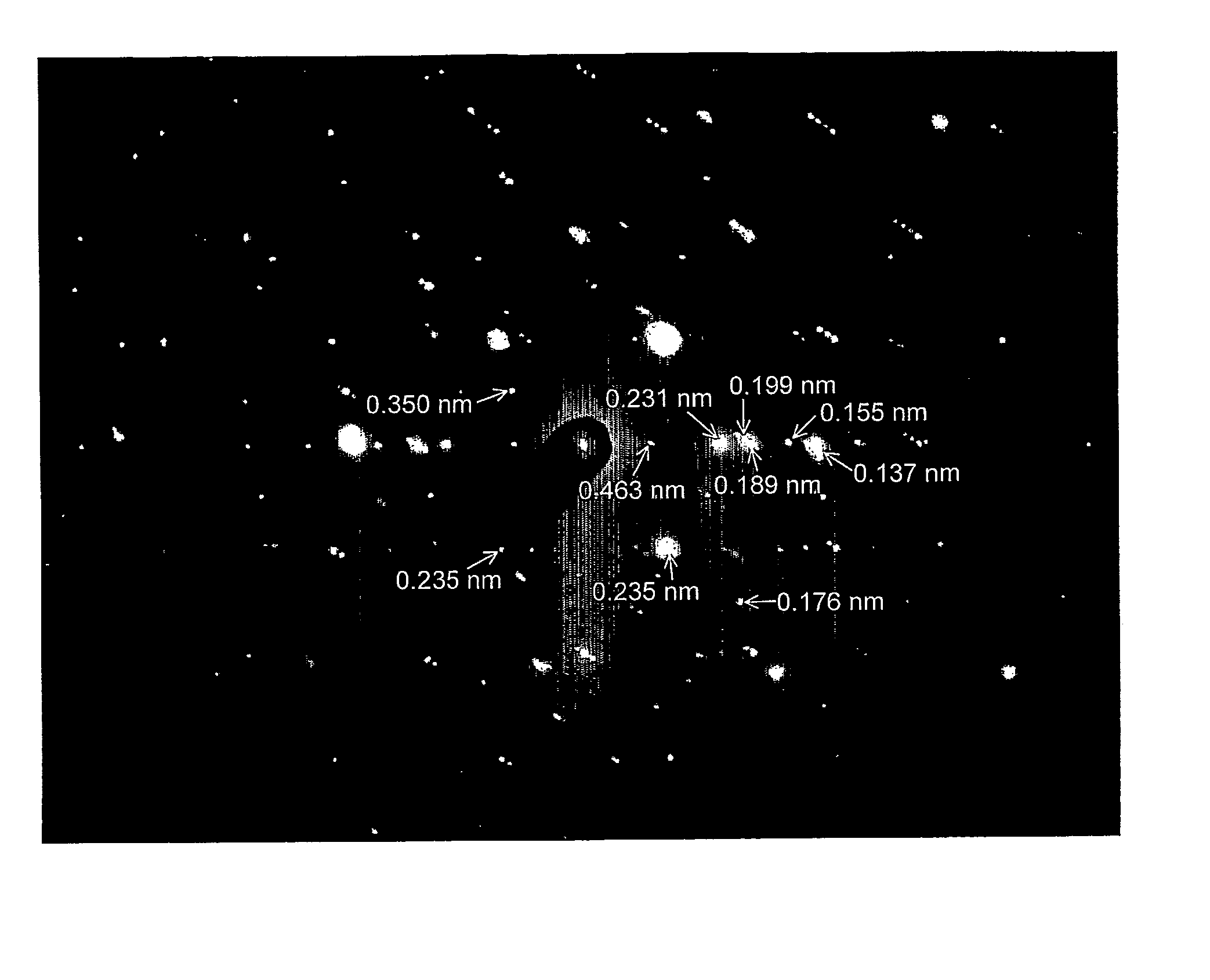

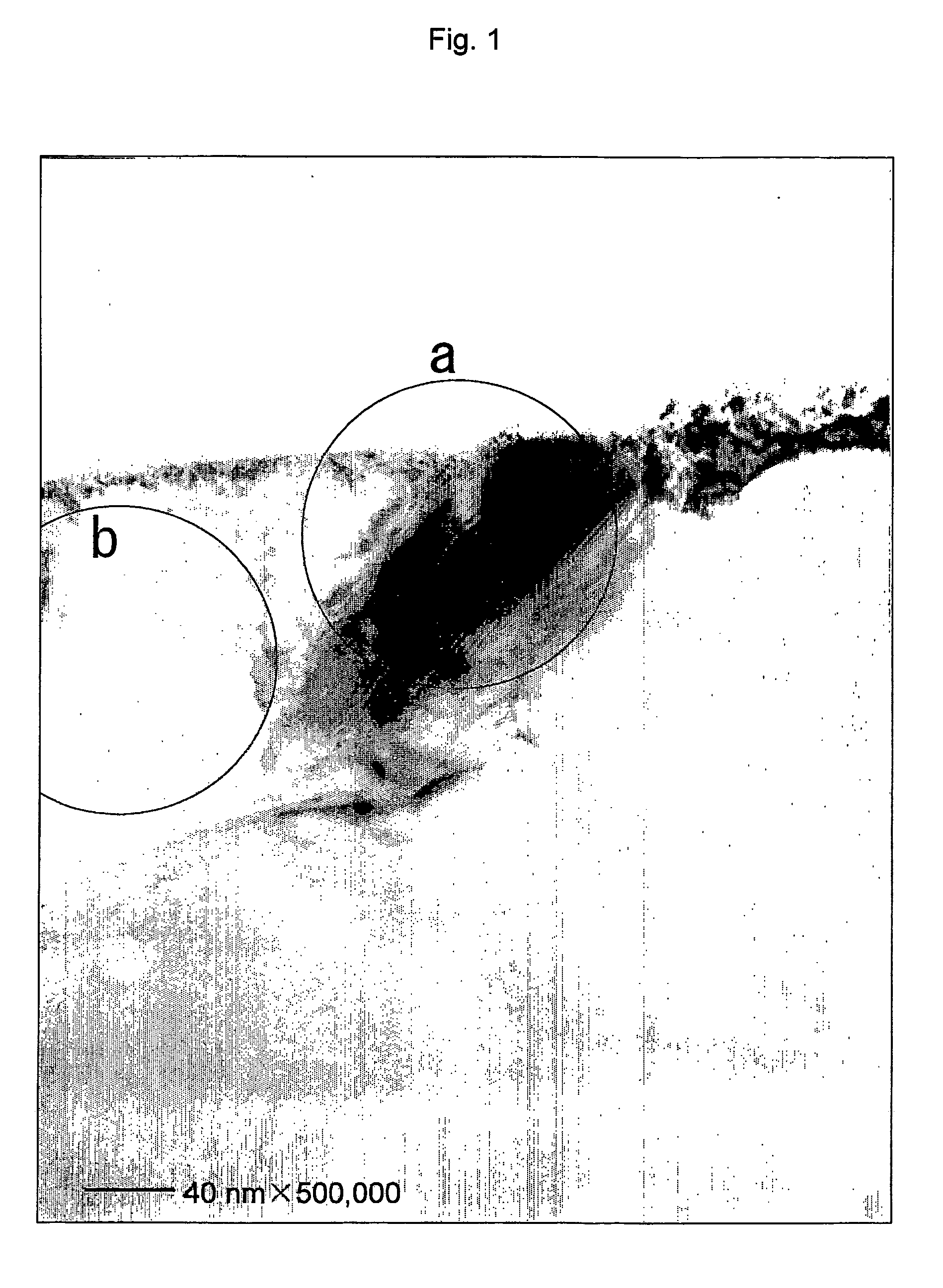

Negative electrode member for lithium battery and process for producing the same

InactiveUS7416815B2Improve the level ofLow electronic conductivityFinal product manufactureElectrode carriers/collectorsMetallic lithiumHigh energy

Affords high-stability, high-safety lithium secondary batteries of high energy density and superlative charge / discharge cyclability, in which shorting due to the growth of dendrites from the metallic-lithium negative electrode is kept under control.A lithium secondary battery negative-electrode component material, formed by laminating onto a substrate a metallic lithium film and an inorganic solid-electrolyte film, the lithium secondary battery negative-electrode component material characterized in that the inorganic solid-electrolyte film incorporates lithium, phosphorous, sulfur, and oxygen, and is represented by the compositional formula noted below.aLi·bP·cS·dO(Li: lithium; P: phosphorous; S: sulfur; O: oxygen), wherein the ranges of the atomic fractions in the composition are:0.20≦a≦0.45;0.10≦b≦0.20;0.35≦c≦0.60;0.03≦d≦0.13;(a+b+c+d=1).

Owner:SUMITOMO ELECTRIC IND LTD

Semiconductor device

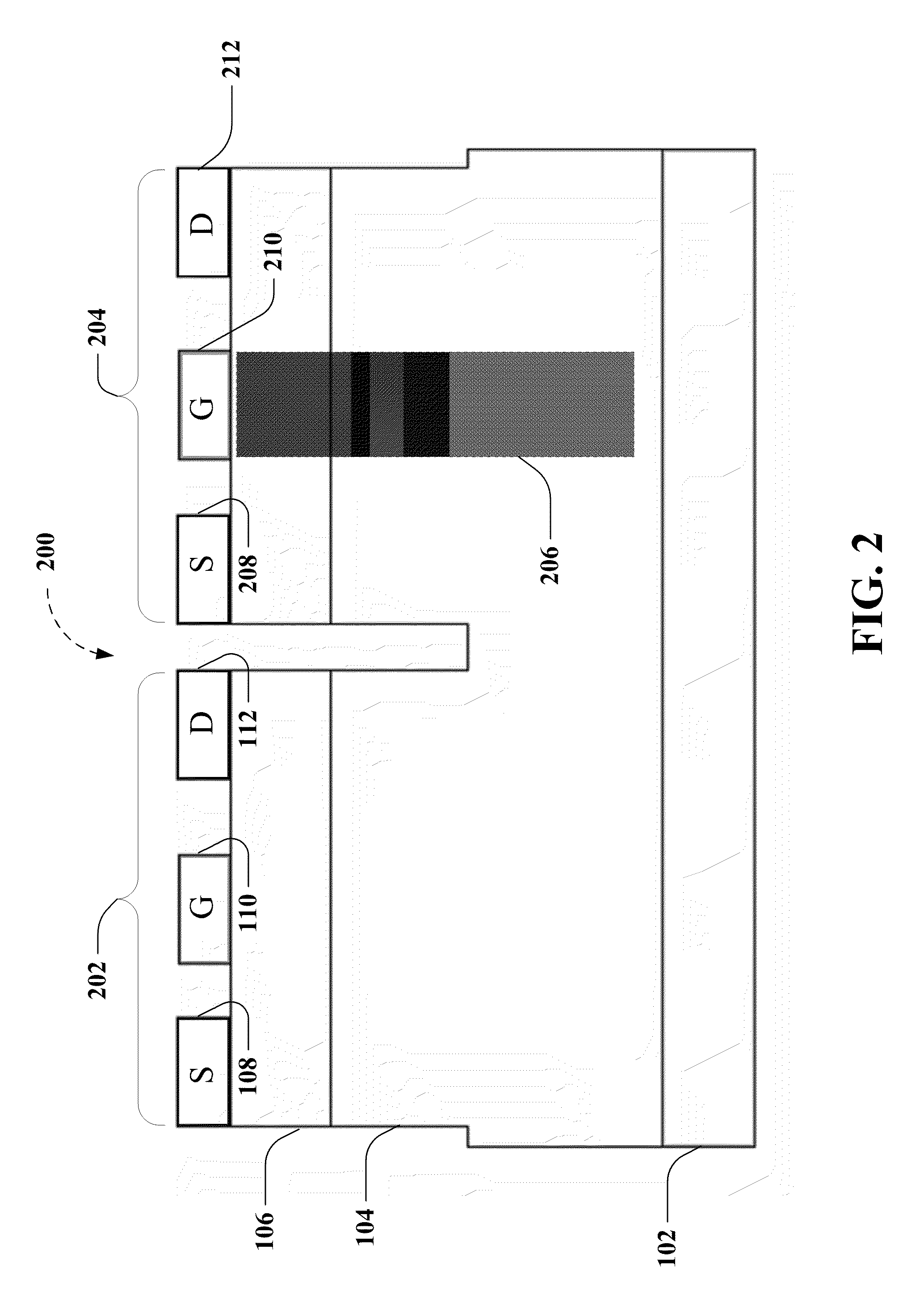

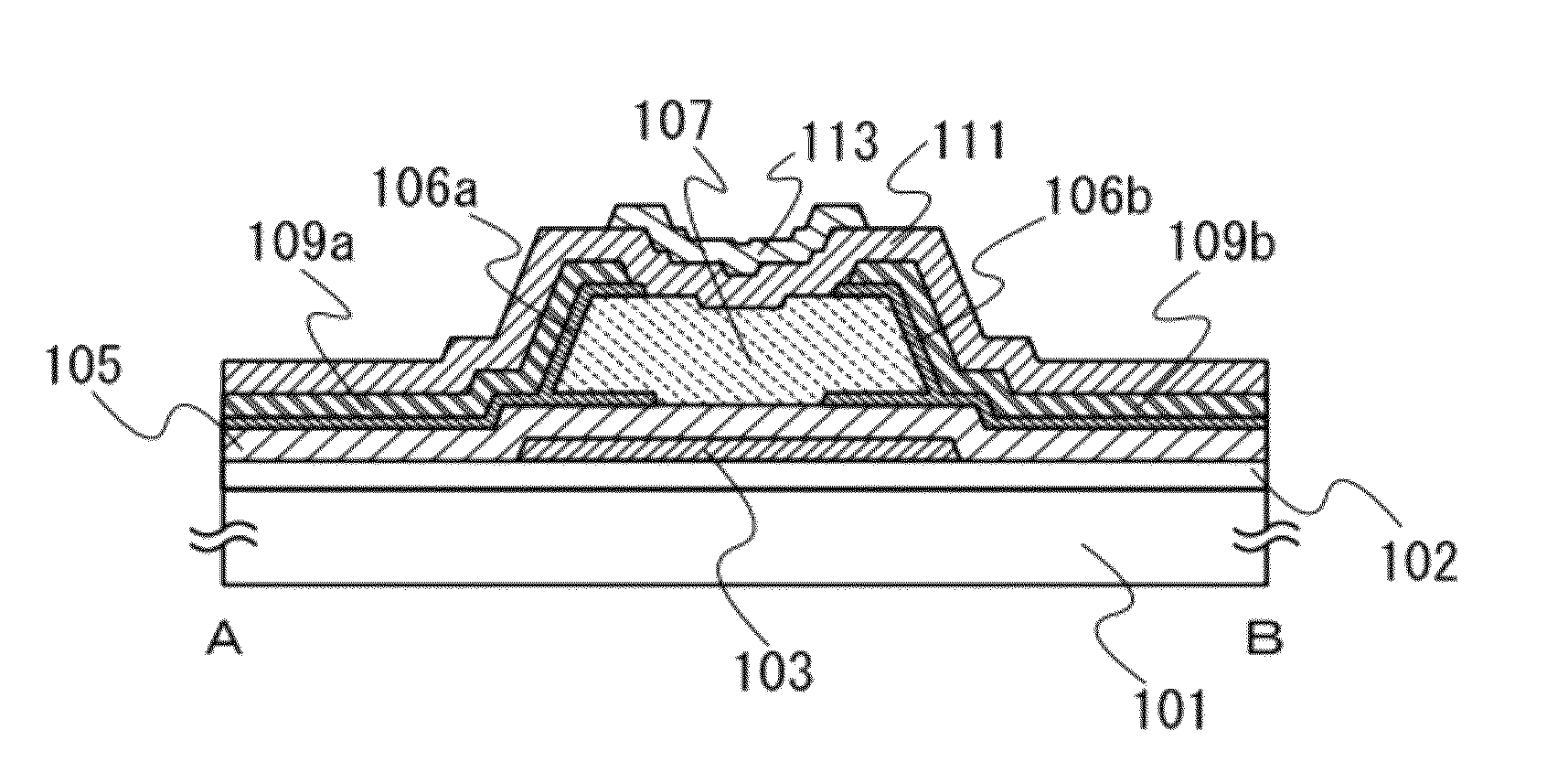

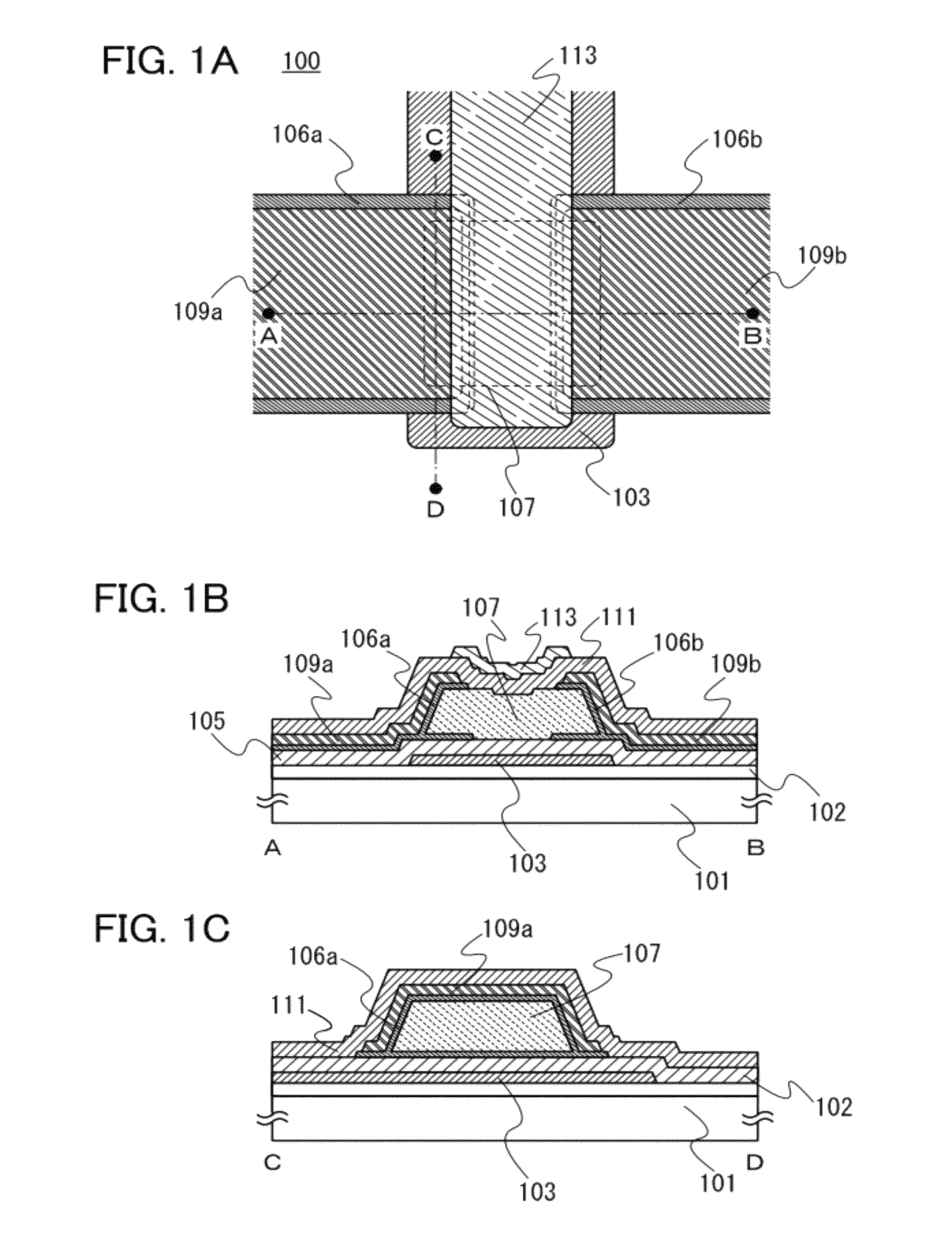

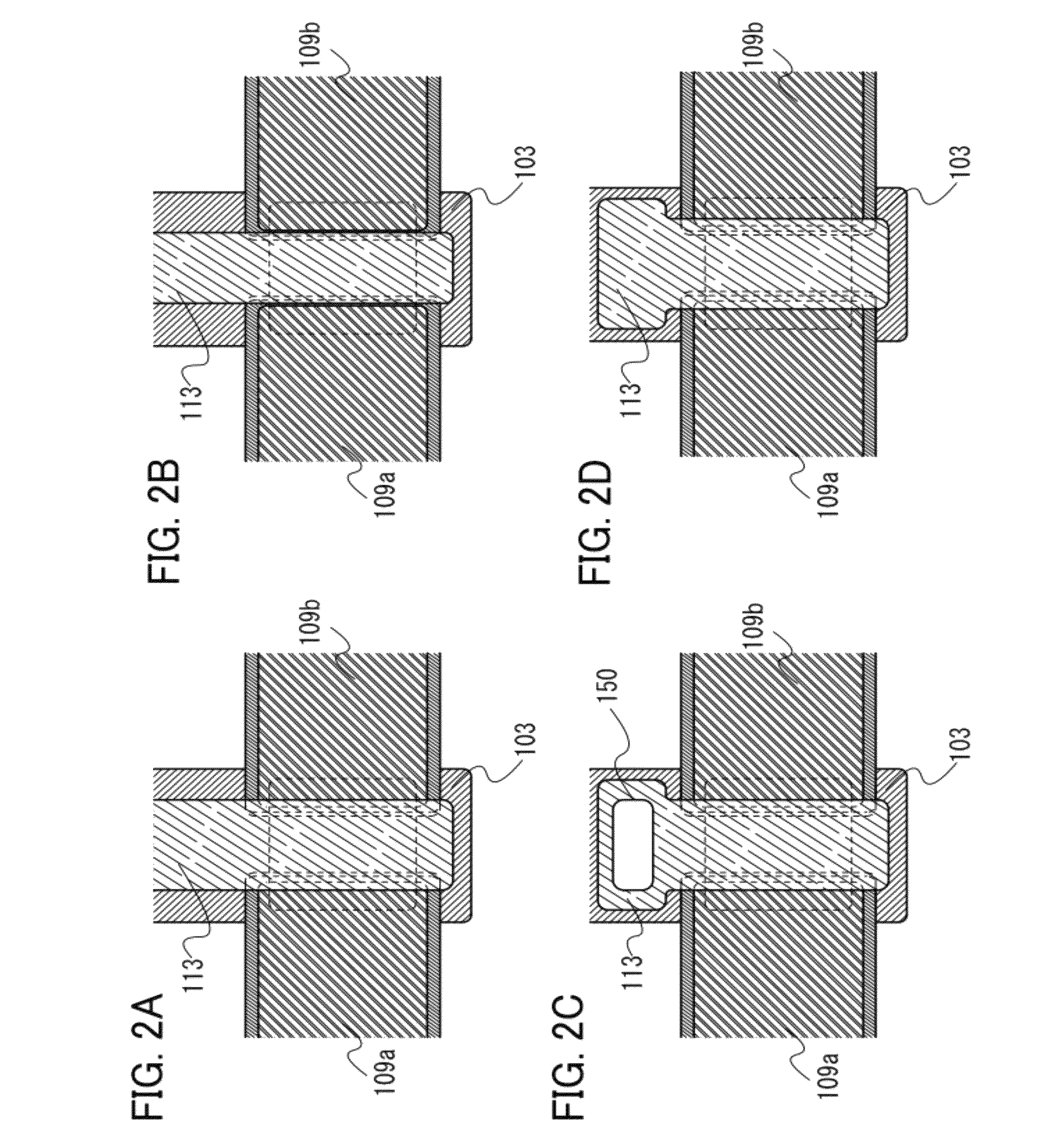

InactiveUS8916866B2Improve featuresHigh densityTransistorSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

A semiconductor device includes a first gate electrode; a gate insulating layer covering the first gate electrode; an oxide semiconductor layer that overlaps with the first gate electrode; oxide semiconductor layers having high carrier density covering end portions of the oxide semiconductor layer; a source electrode and a drain electrode in contact with the oxide semiconductor layers having high carrier density; an insulating layer covering the source electrode, the drain electrode, and the oxide semiconductor layer; and a second gate electrode that is in contact with the insulating layer. Each of the oxide semiconductor layers is in contact with part of each of an upper surface, a lower surface, and a side surface of one of the end portions of the oxide semiconductor layer and part of an upper surface of the gate insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

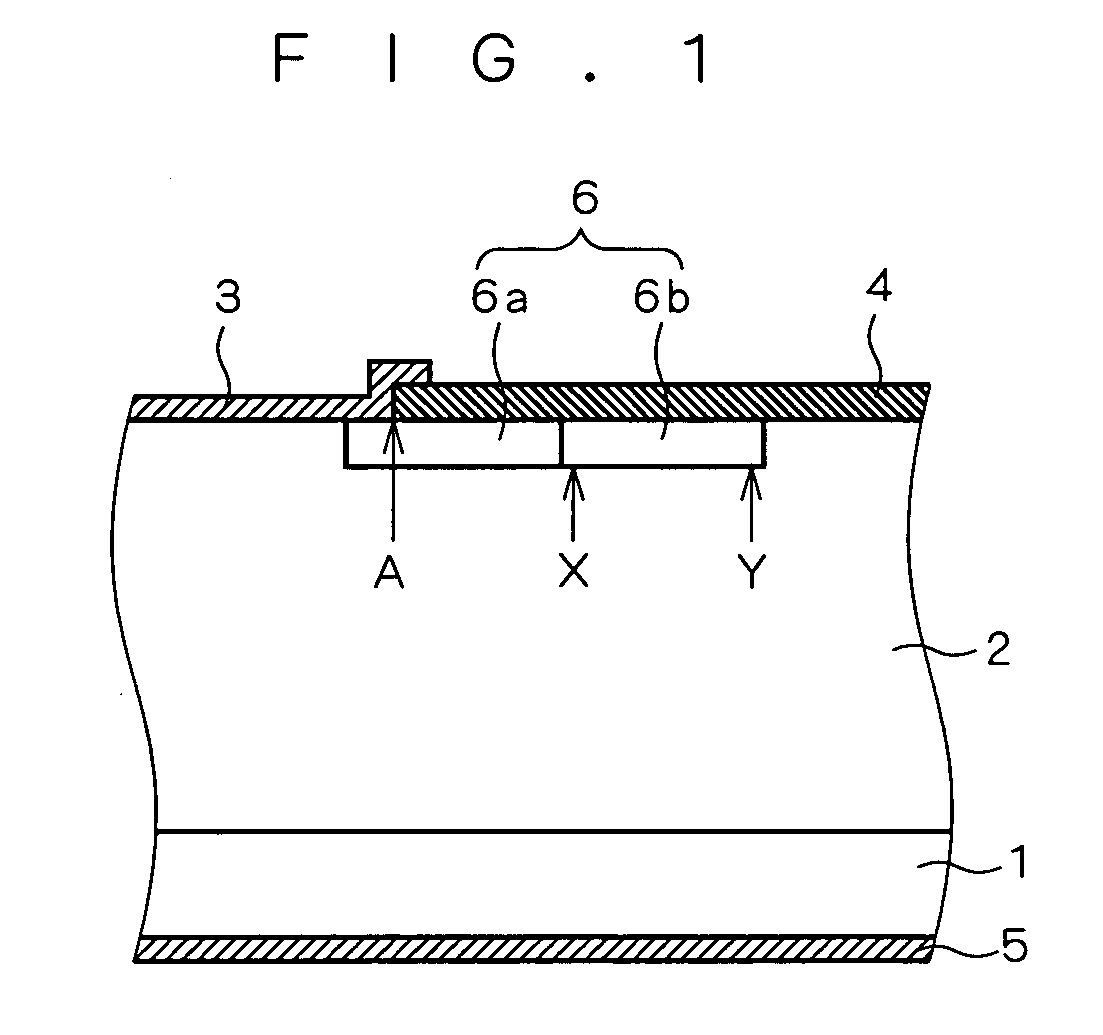

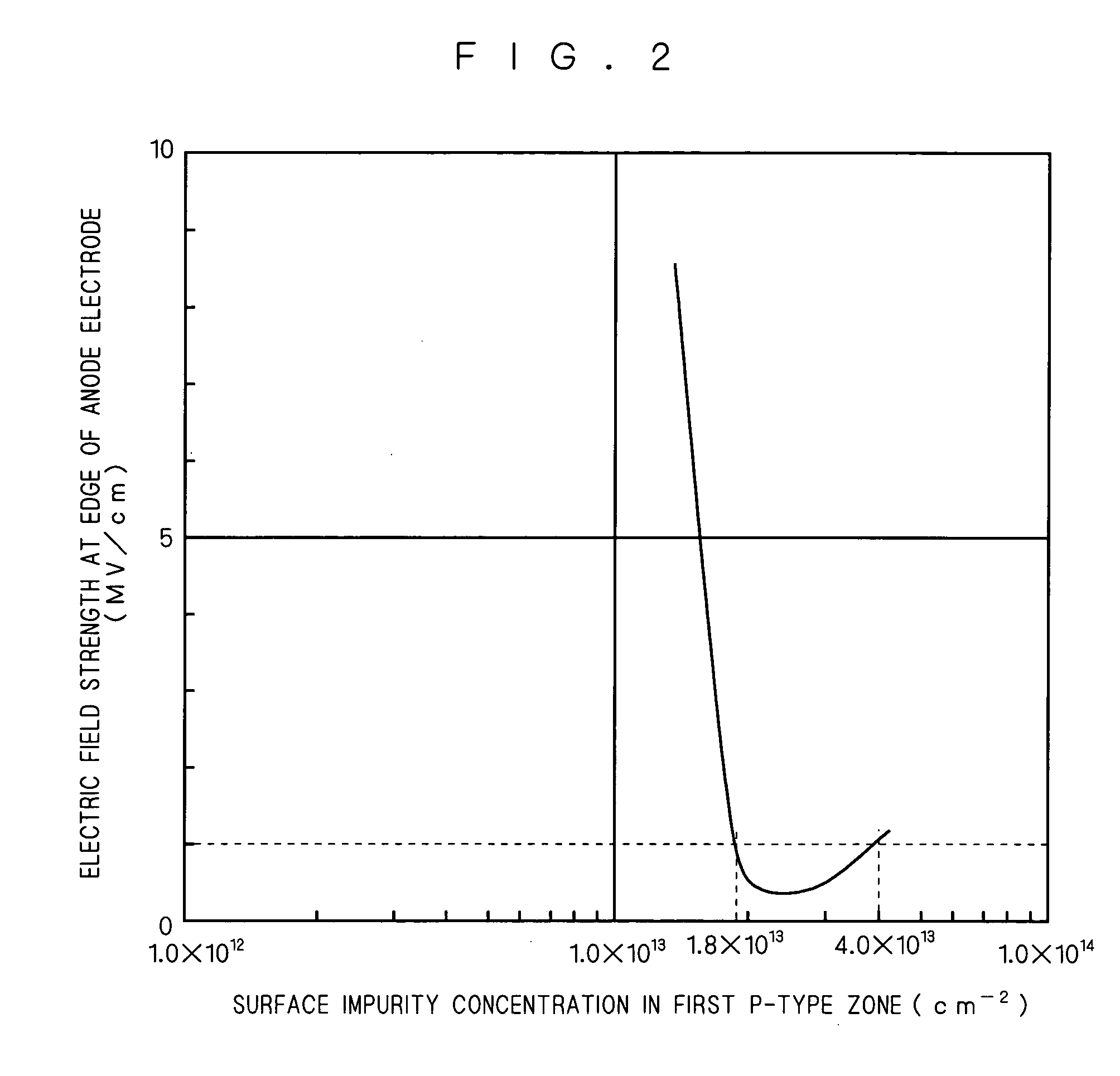

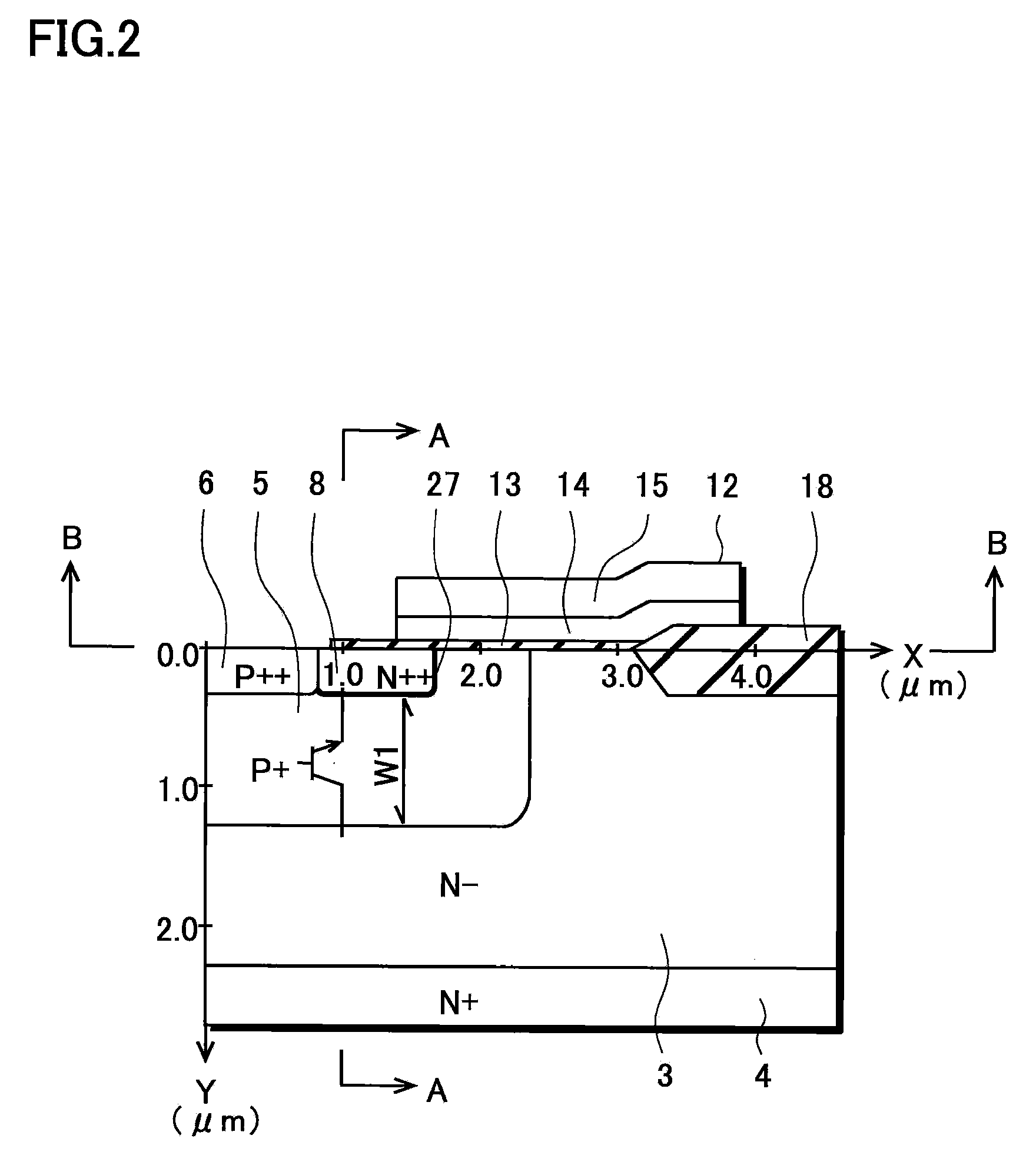

ActiveUS20060118812A1Sufficient breakdown voltage characteristicInhibitionThyristorElectric motor controlDevice materialSemiconductor

A semiconductor device includes an anode electrode in Schottky contact with an n-type drift layer formed in an SiC substrate and a JTE region formed outside the anode electrode. The JTE region is made up of a first p-type zone formed in an upper portion of the drift layer under an edge of the anode electrode and a second p-type zone formed outside the first p-type zone having a lower surface impurity concentration than the first p-type zone. The second p-type zone is provided 15 μm or more outwardly away from the edge of the anode electrode. The surface impurity concentration of the first p-type zone ranges from 1.8×1013 to 4×1013 cm−2, and that of the second p-type zone ranges from 1×1013 to 2.5×1013 cm−2.

Owner:MITSUBISHI ELECTRIC CORP

Negative electrode member for lithium battery and process for producing the same

InactiveUS20060127772A1Degree of improvementIncrease rangeFinal product manufactureElectrode carriers/collectorsMetallic lithiumSulfur

Affords high-stability, high-safety lithium secondary batteries of high energy density and superlative charge / discharge cyclability, in which shorting due to the growth of dendrites from the metallic-lithium negative electrode is kept under control. A lithium secondary battery negative-electrode component material, formed by laminating onto a substrate a metallic lithium film and an inorganic solid-electrolyte film, the lithium secondary battery negative-electrode component material characterized in that the inorganic solid-electrolyte film incorporates lithium, phosphorous, sulfur, and oxygen, and is represented by the compositional formula noted below. aLi·bP·cS·dO (Li: lithium; P: phosphorous; S: sulfur; O: oxygen), wherein the ranges of the atomic fractions in the composition are: 0.20≦a≦0.45; 0.10≦b≦0.20; 0.35≦c≦0.60; 0.03≦d≦0.13; (a+b+c+d=1).

Owner:SUMITOMO ELECTRIC IND LTD

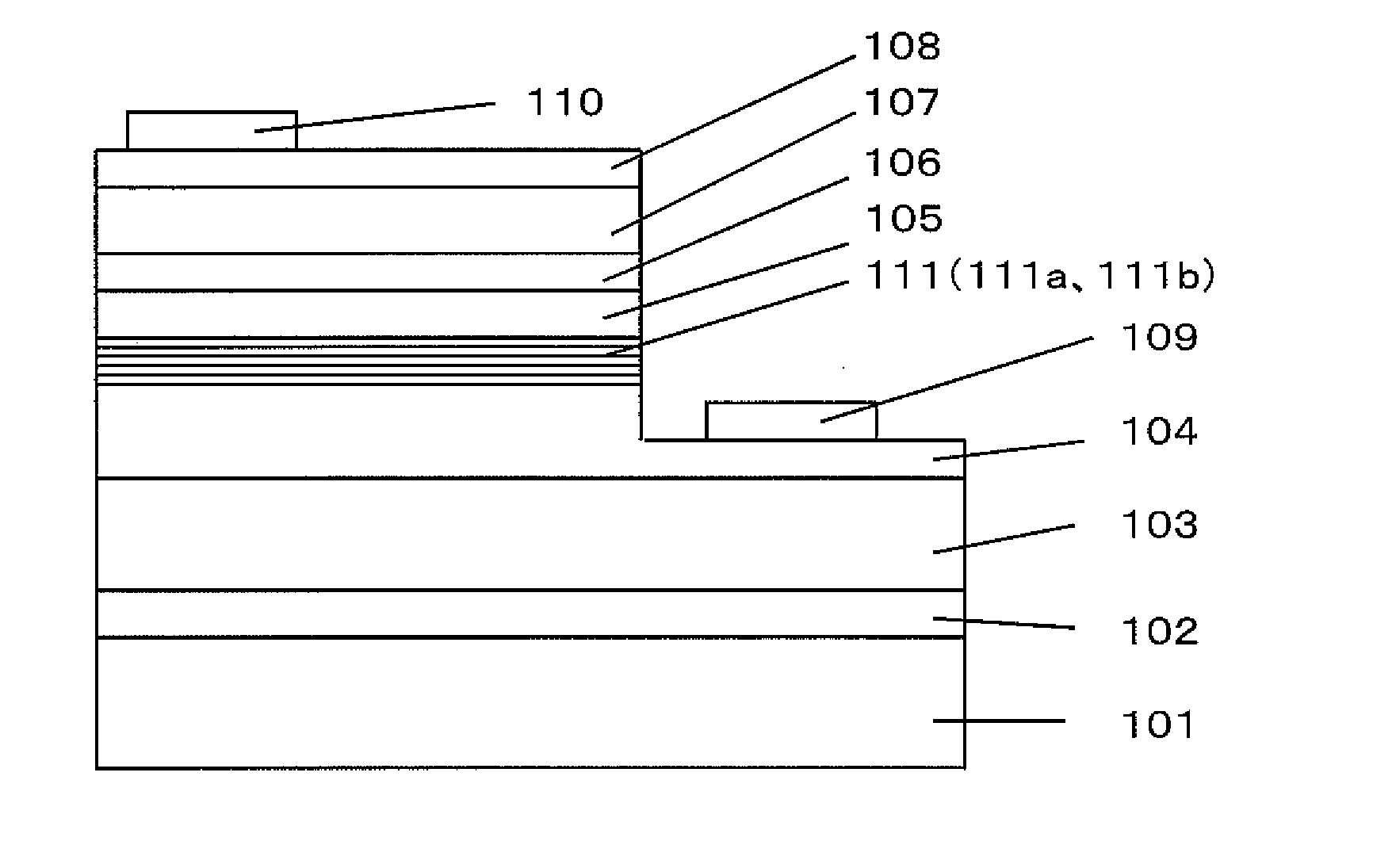

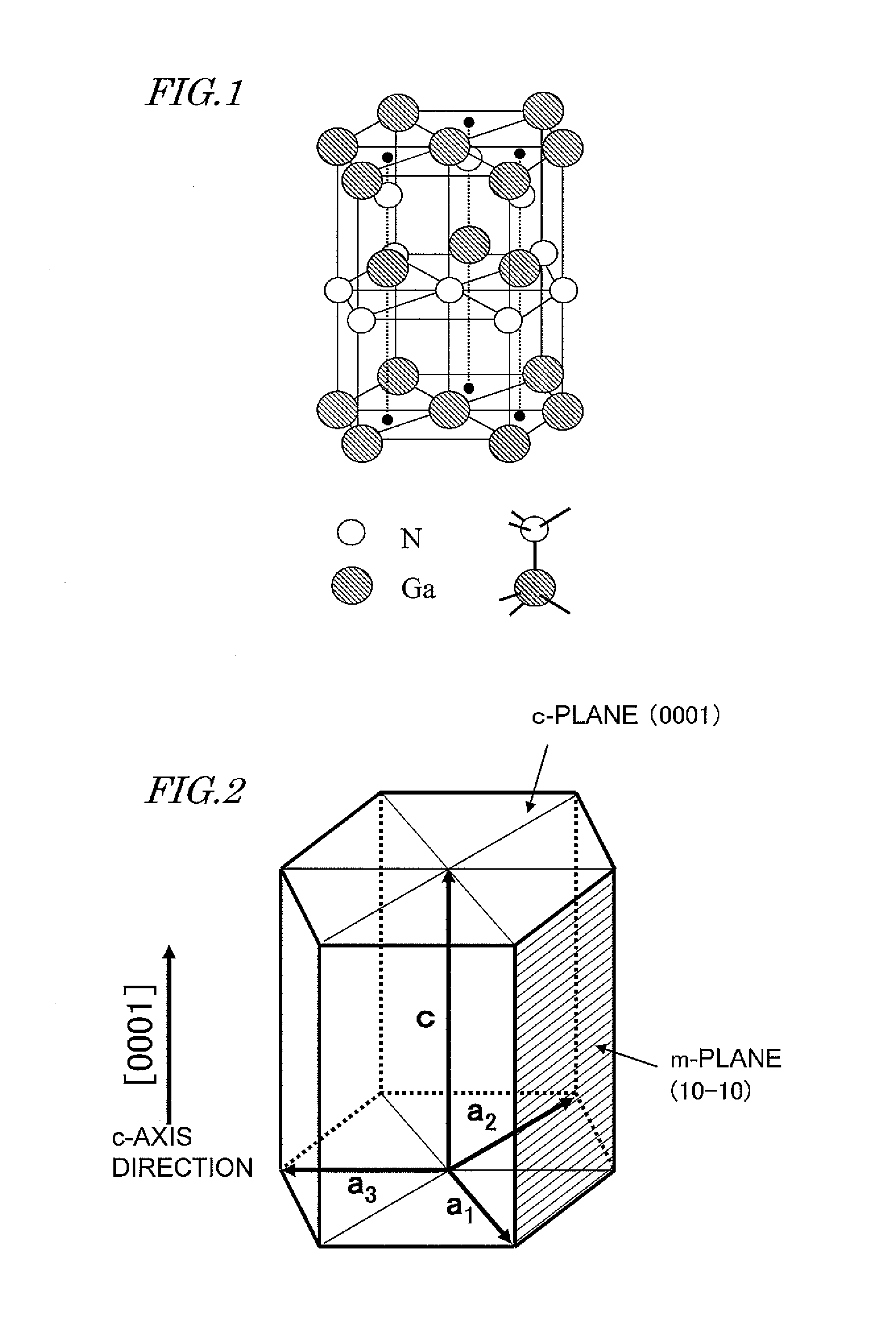

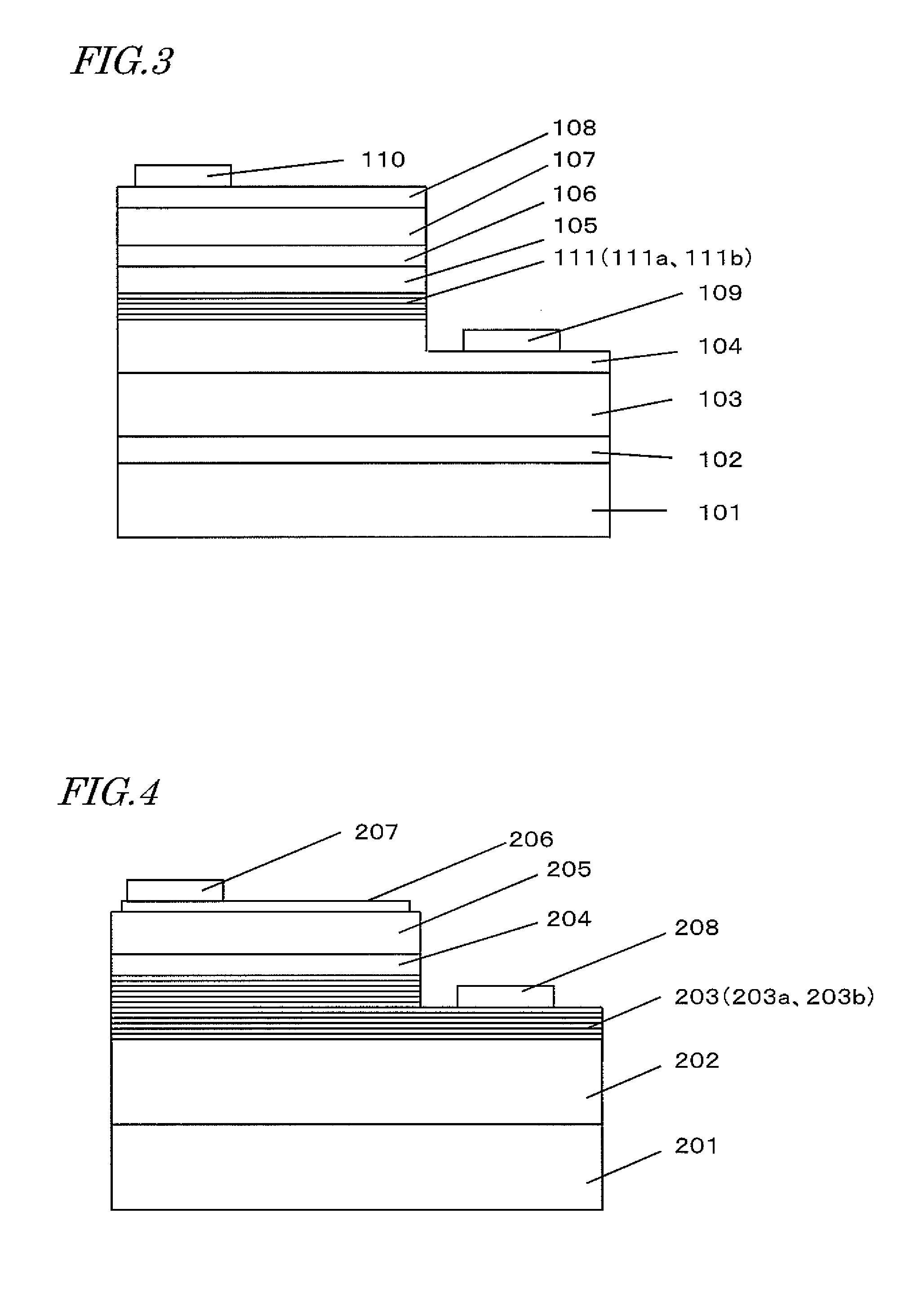

Nitride semiconductor light-emitting element and process for production thereof

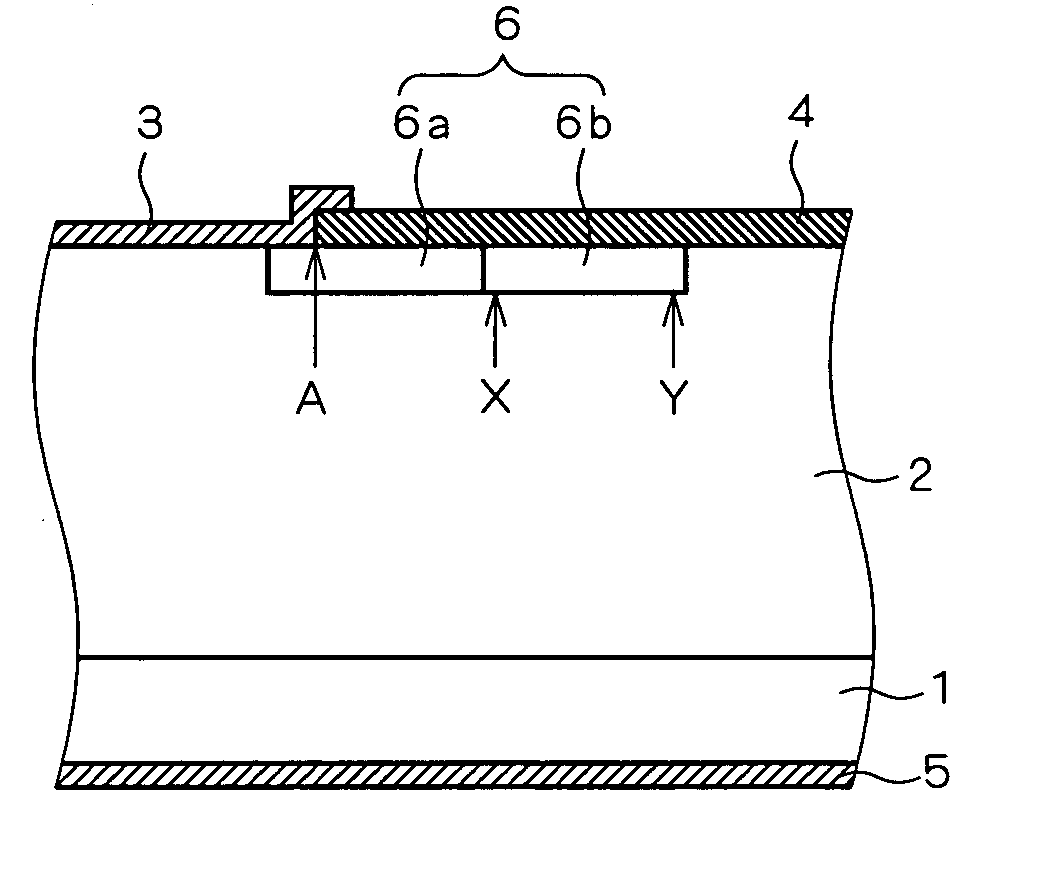

InactiveUS20120001223A1Improve featuresImprove conversion efficiencySolid-state devicesSemiconductor devicesActive layerLight emitting device

A nitride-based semiconductor light-emitting device 31 includes: an n-type GaN substrate 1 which has an m-plane principal surface; a current diffusing layer 7 provided on the n-type GaN substrate 1; an n-type nitride semiconductor layer 2 provided on the current diffusing layer 7; an active layer 3 provided on the n-type nitride semiconductor layer 2; a p-type nitride semiconductor layer 4 provided on the active layer 3; a p-electrode 5 which is in contact with the p-type nitride semiconductor layer 4; and an n-electrode 6 which is in contact with the n-type GaN substrate 1 or the n-type nitride semiconductor layer 2. The donor impurity concentration of the n-type nitride semiconductor layer 2 is not more than 5×1018 cm−3, and the donor impurity concentration of the current diffusing layer 7 is ten or more times the donor impurity concentration of the n-type nitride semiconductor layer 2.

Owner:PANASONIC CORP

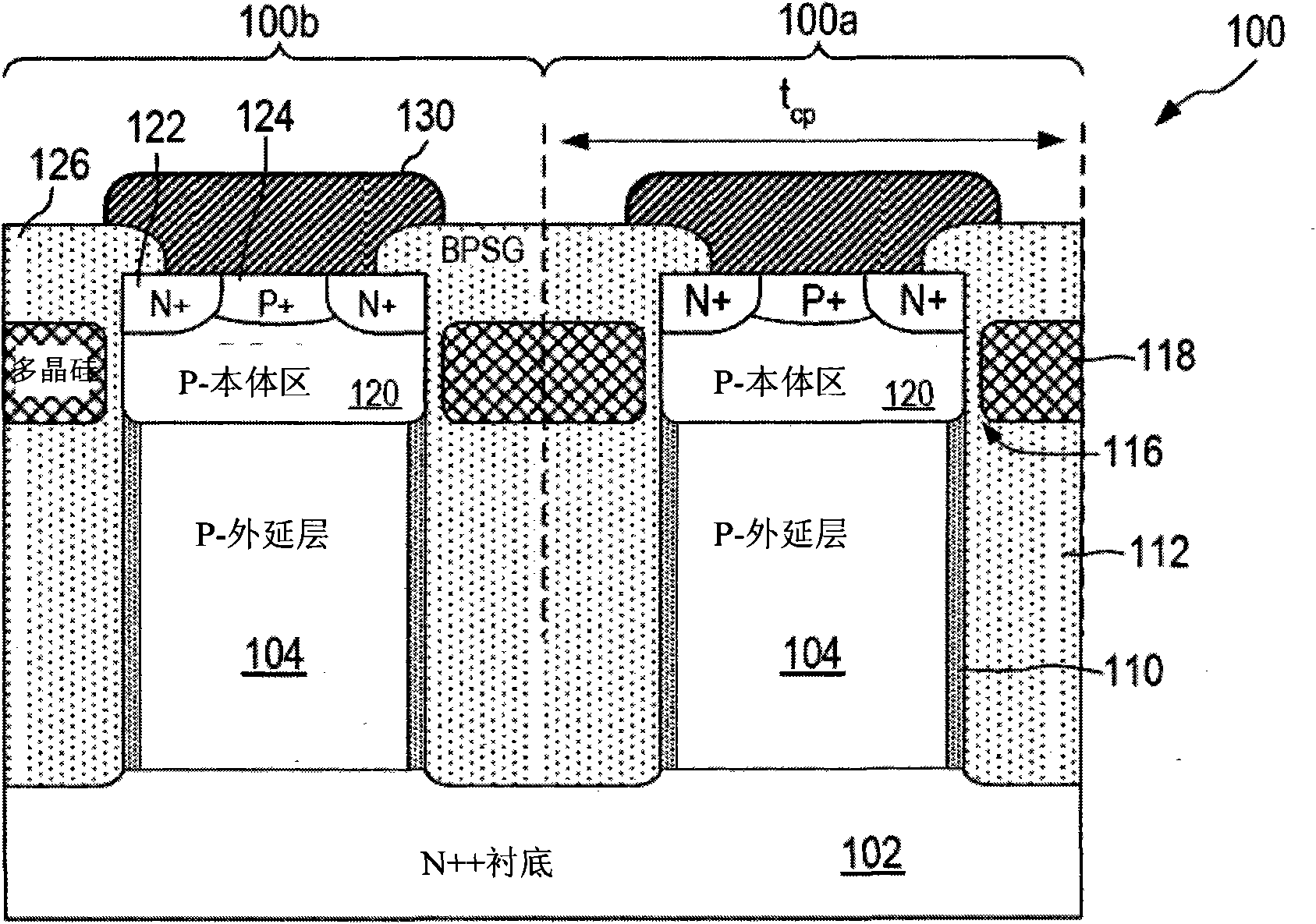

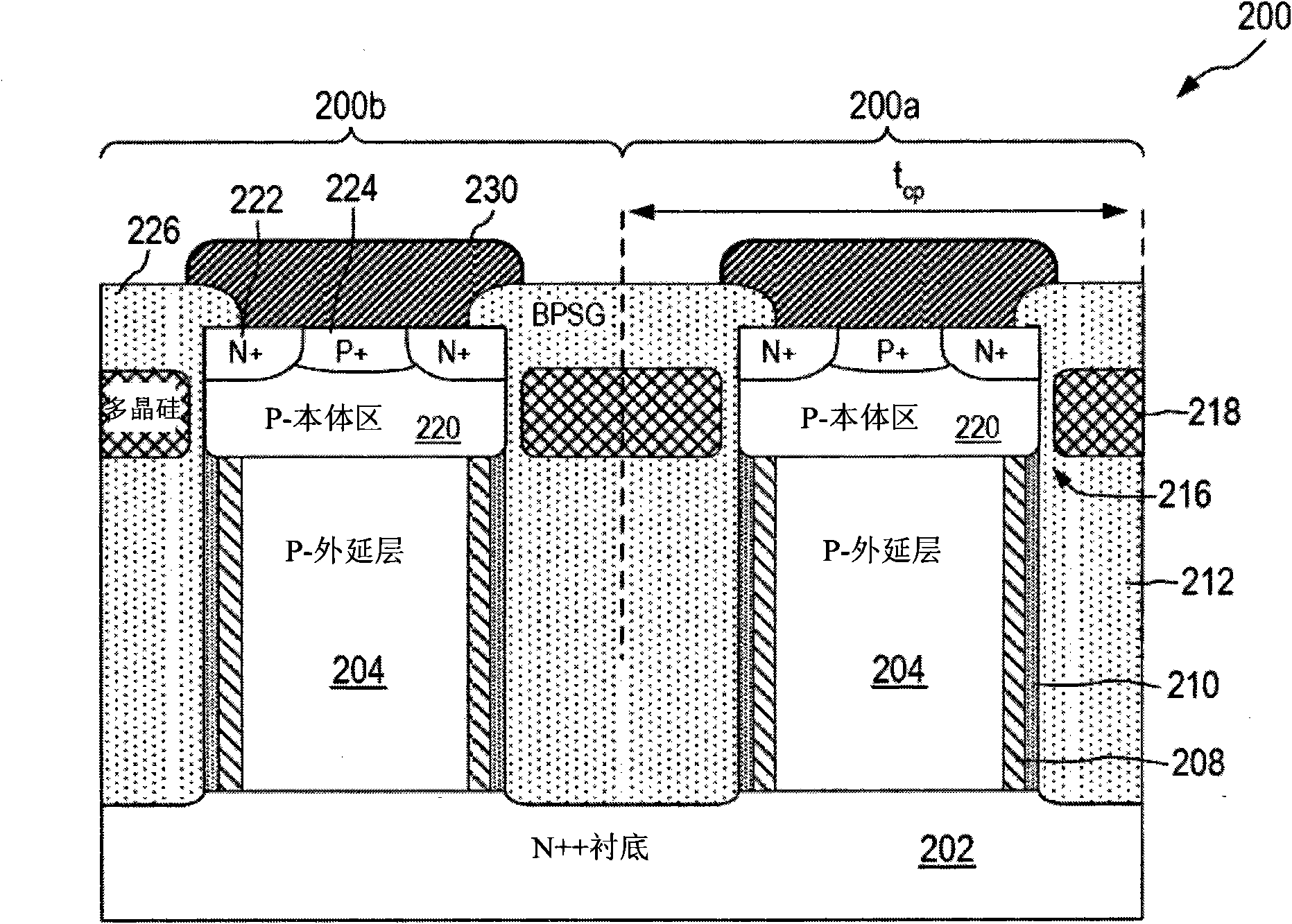

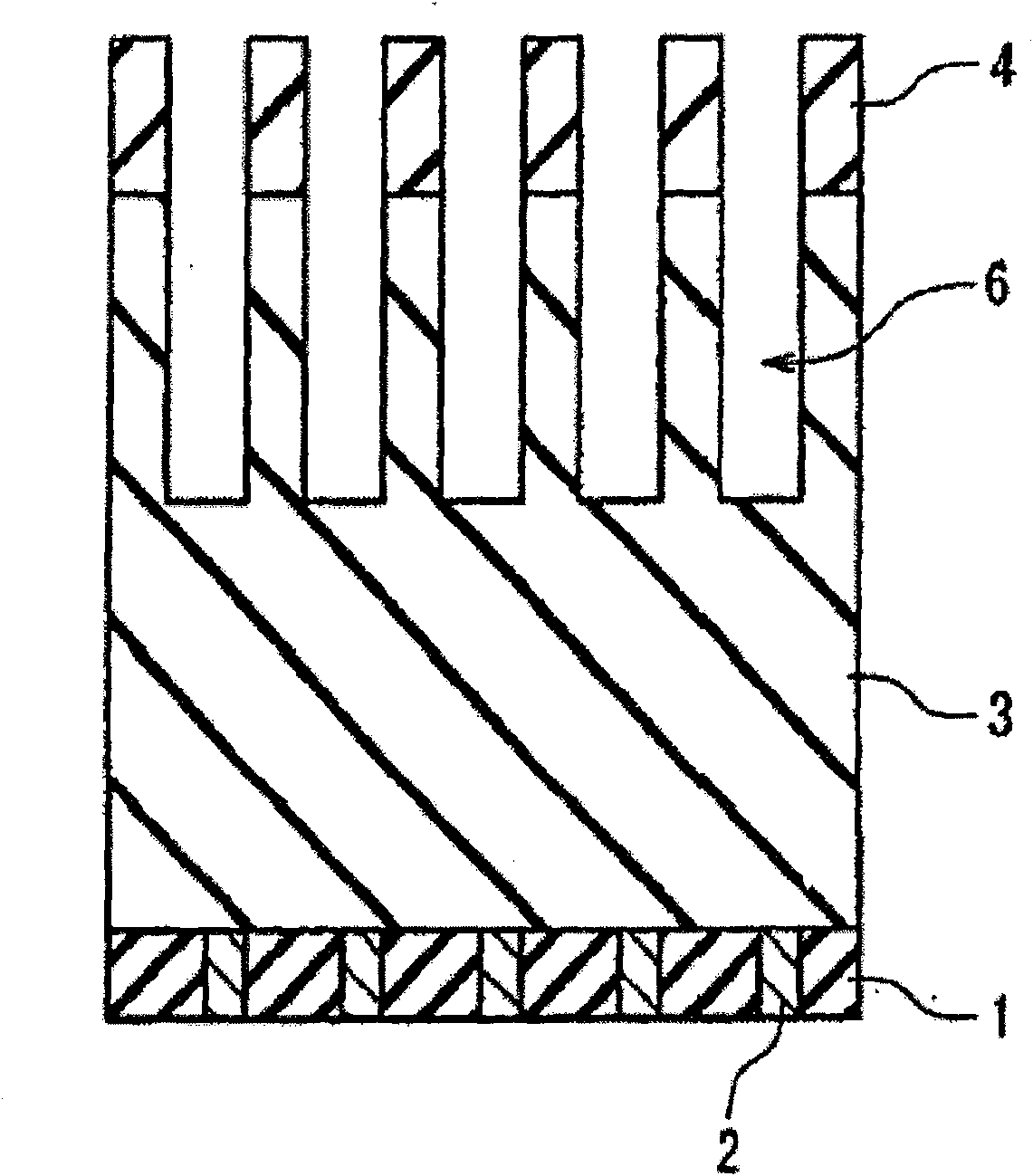

Nano-tubes semiconductor device and preparation method thereof

ActiveCN101924137AImprove charge balance effectUniform doping concentrationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

The invention relates to a semiconductor device and a preparation method thereof. A nano-tubes area is produced by adopting the thin epitaxial layer formed on the channel sidewall of the semiconductor body. The thin epitaxial layer possesses an even and consistent dosage concentration. A first thin epitaxial layer in the same conducting type as the semiconductor body is formed on the channel sidewall of the semiconductor body. A second thin expitaxial layer in the opposite conducting type with the semiconductor body is formed on a first expitaxial layer. The first and the second expitaxial layer possess an even and consistent dosage concentration. An electric charge balance is achieved by choosing an appropriate first and second expitaxial layer and appropriate thickness and dosage concentration of the semiconductor body. The semiconductor body is a P-shaped substrate with light dosage. By adopting the N-expitaxial layer / P-expitaxial layer nano-tubes structure of the same type, a metal oxide field effect tube with a vertical channel, a insulated gate dipole transistor, a Schottky diode and a P-N diode can be produced.

Owner:ALPHA & OMEGA SEMICON INT LP

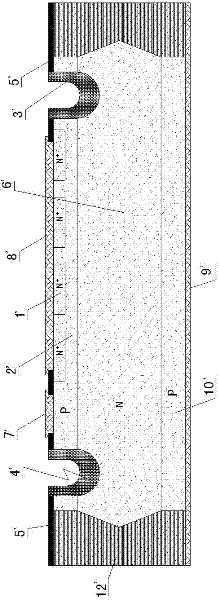

Controlled silicon chip structure of mesa technology and implementation method

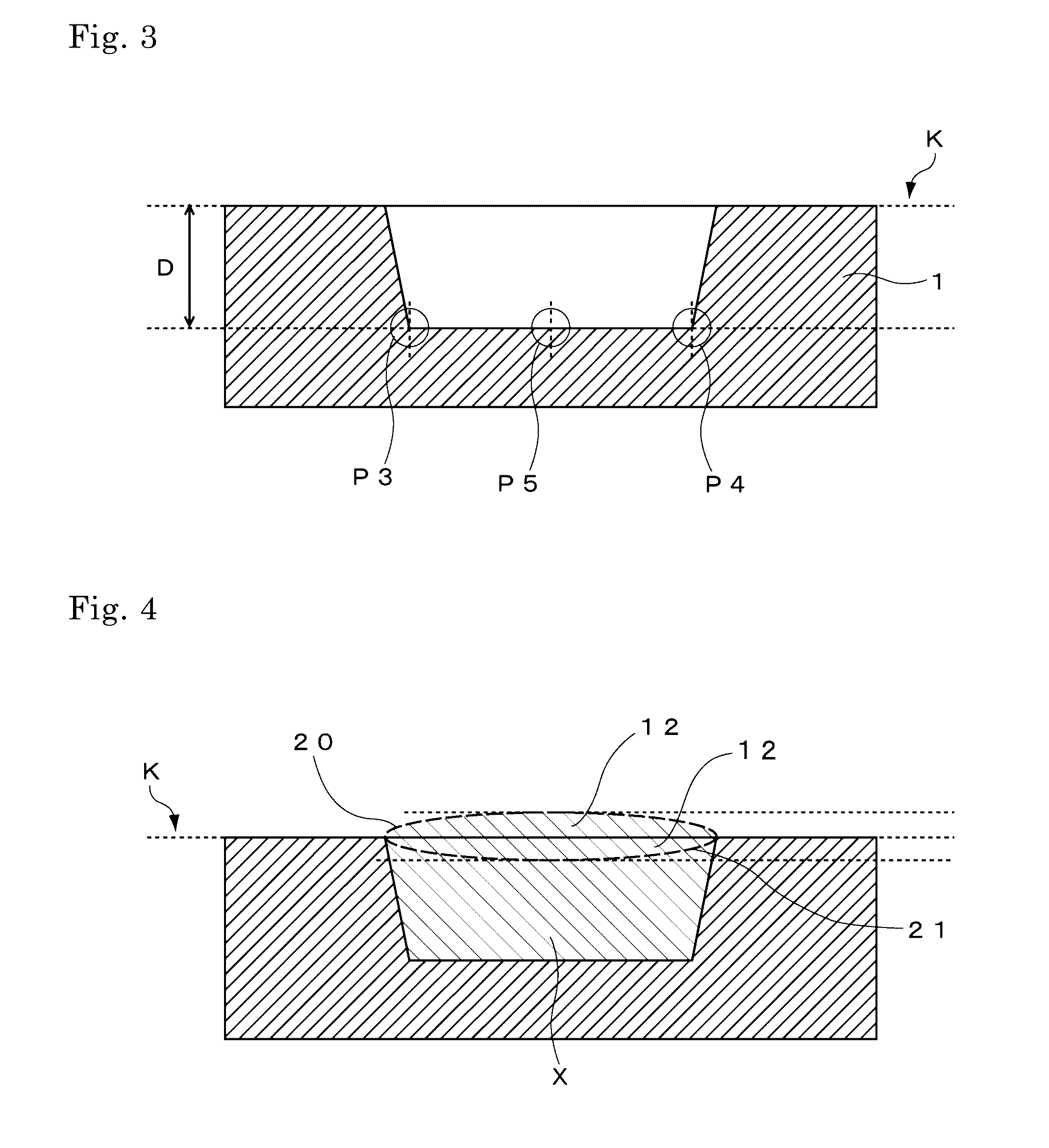

ActiveCN102244078AImproved breakdown voltage characteristicsSmall expansion coefficientTransistorSemiconductor/solid-state device manufacturingSilicon chipPhysics

The invention relates to a controlled silicon chip structure of a mesa technology. The structure comprises an N+ type cathode region, a front surface P-type short base region, a glass passivation film, front surface grooves, a SiO2 protective film, a silicon single crystal chip, a gate pole aluminum electrode and a cathode aluminum electrode, wherein the front side of the silicon single crystal chip is provided with the front P-type short base region; the back side of the silicon single crystal chip is provided with a P-type region; the surface of the front surface P-type short base region isprovided with the SiO2 protective film, the gate pole aluminum electrode and the cathode aluminum electrode; the front grooves are arranged on the front surface P-type short base region and the silicon single crystal chip, and are positioned at two sides of the gate pole aluminum electrode and the cathode aluminum electrode; and the N+ type cathode region is arranged between the cathode aluminum electrode and the front P-type short base region. The structure is characterized in that the bottom part of a dual-pass insulation diffusion region is provided with a back side stress balance groove. The structure provided by the invention has the advantages of mature structure and technology, simple manufacturing process, good breakdown voltage property of the manufactured chip, high percent of pass, and high reliability of products.

Owner:JIANGSU JIEJIE MICROELECTRONICS

Niobium powder for capacitor, niobium sintered body and capacitor

InactiveUS20070137434A1Increase capacitanceReduce leakage currentHybrid capacitor electrolytesNitrogen-metal/silicon/boron binary compoundsCapacitanceNiobium capacitor

The present invention relates to niobium powder for a capacitor, comprising a niobium layer and a mixed layer of silicon nitride and niobium, the mixed layer being present in the vicinity of the powder particle surface; granulated niobium powder thereof; a niobium sintered body using the niobium powder and the granulated powder; and a capacitor using the sintered body as one electrode. The niobium powder for a capacitor of the present invention enables to produce a niobium capacitor having a high capacitance, a low leakage current, a low ESR and good tan δ characteristics and being excellent particularly in the properties of the breakdown voltage and soldering heat resistance.

Owner:SHOWA DENKO KK

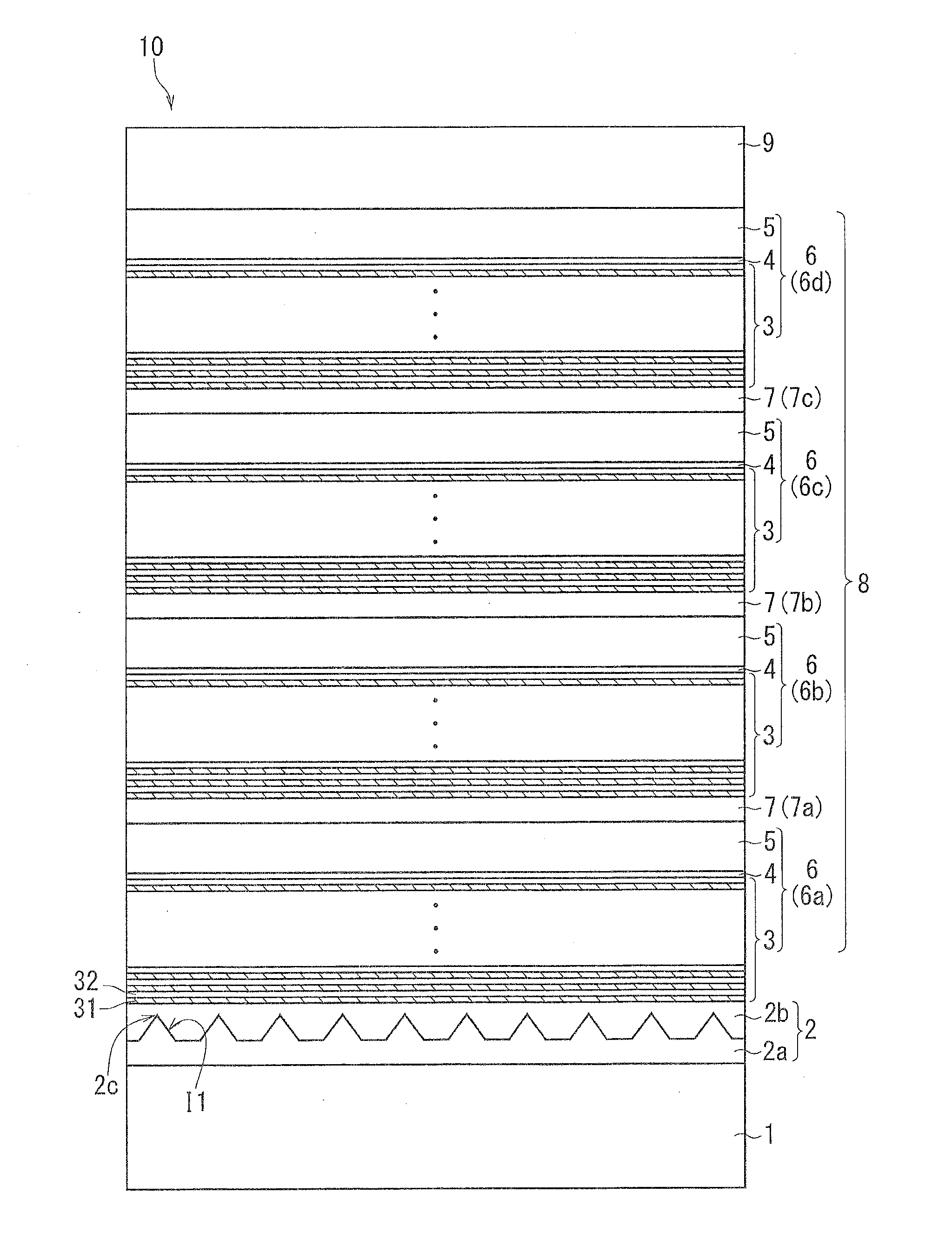

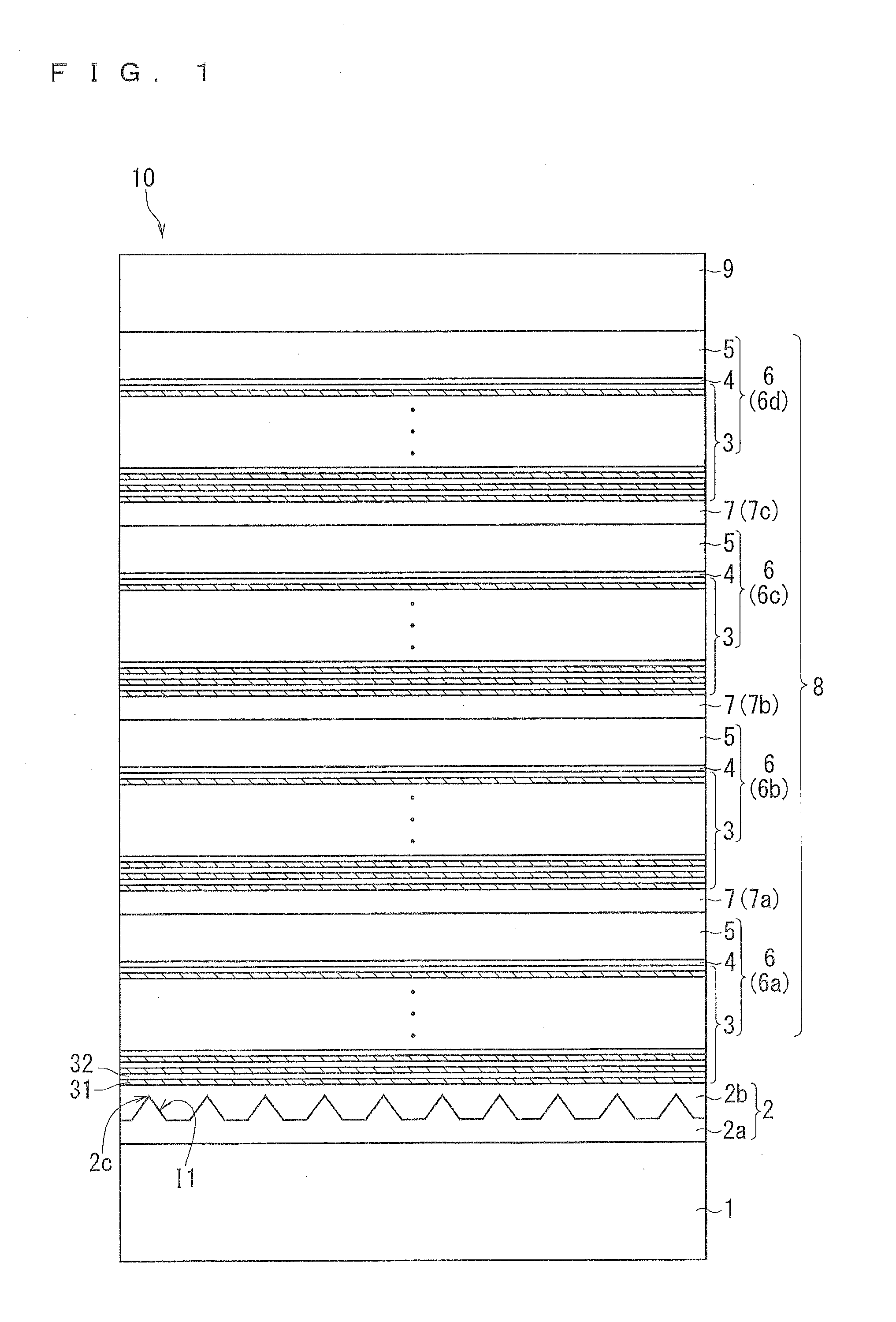

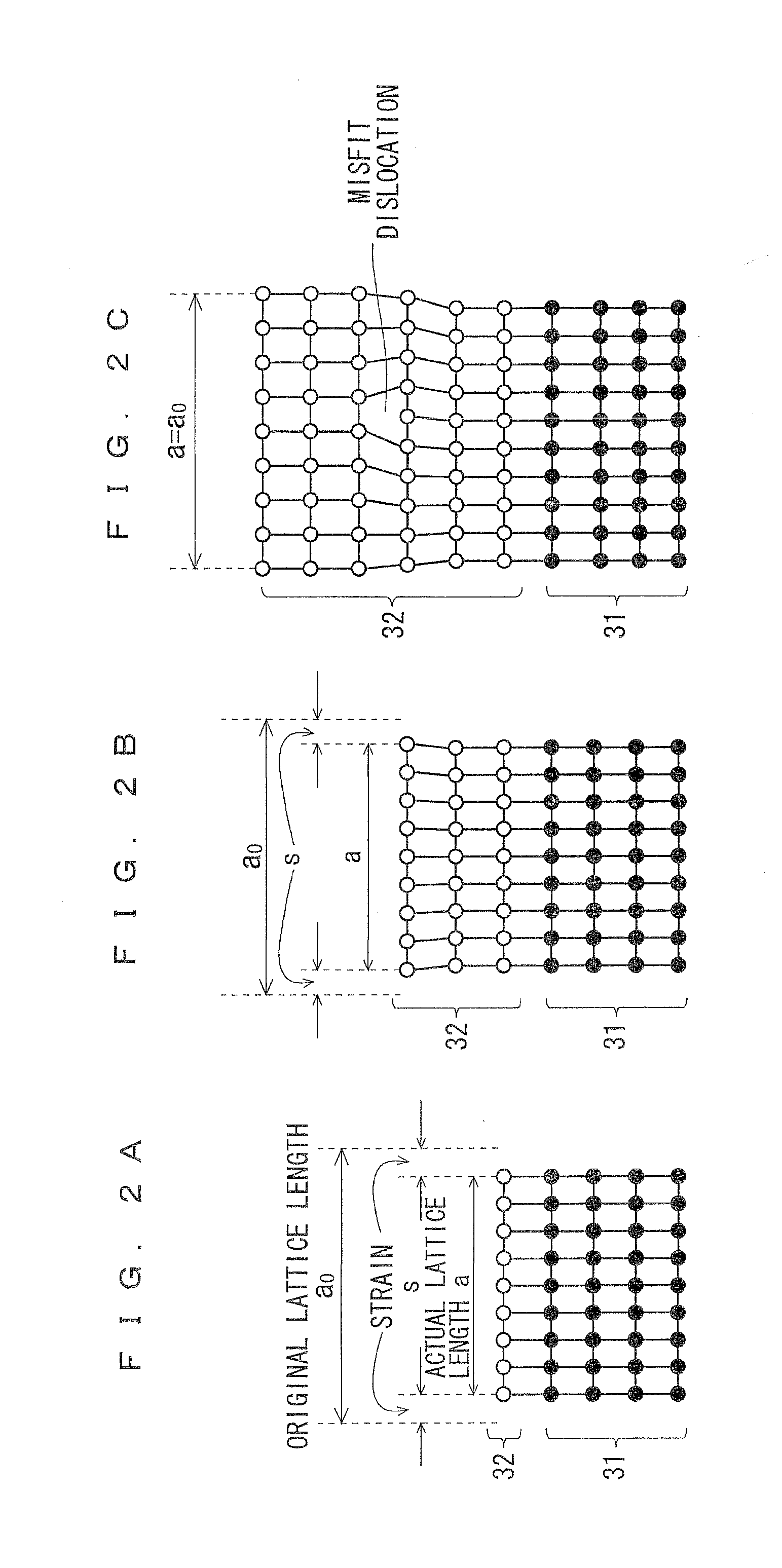

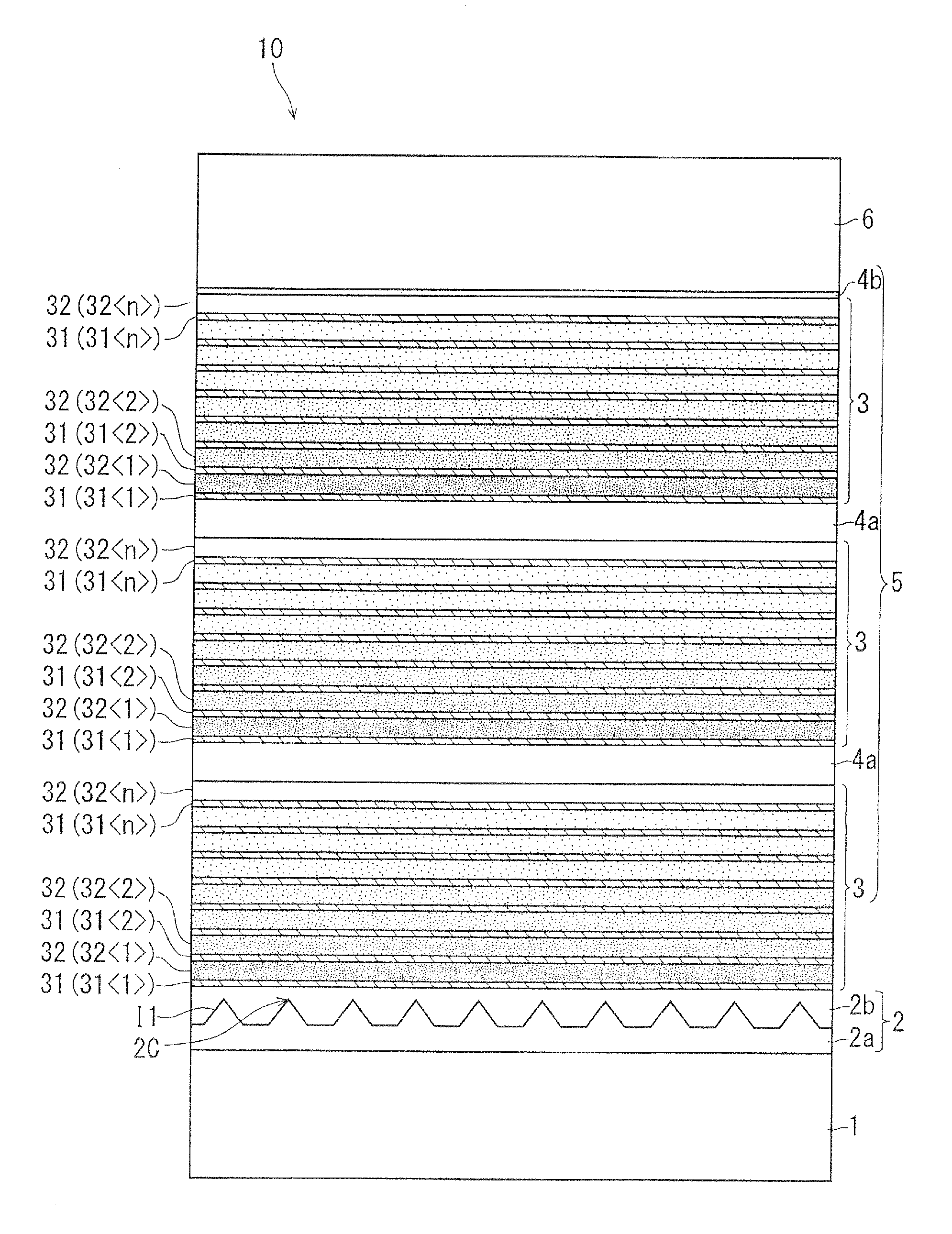

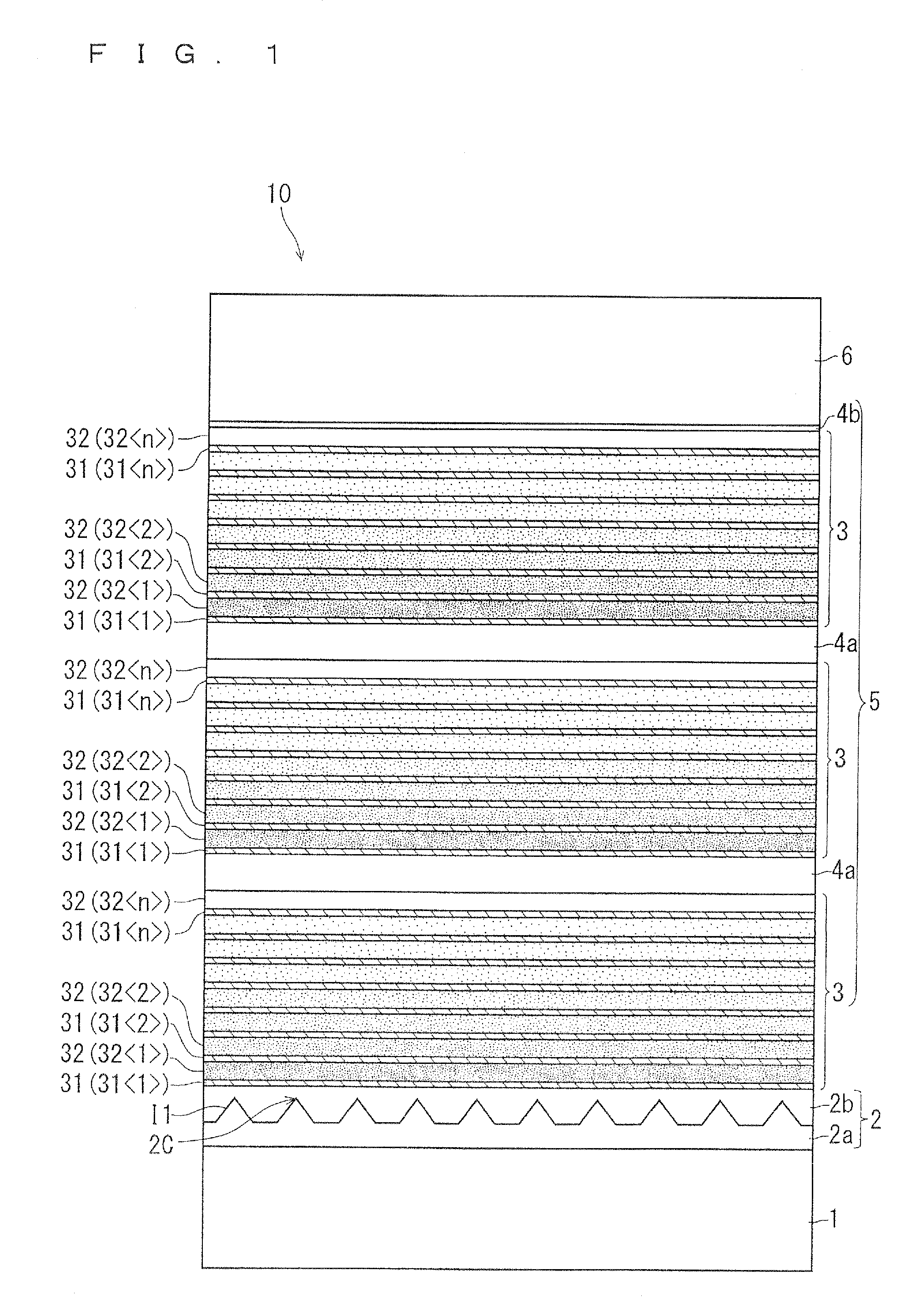

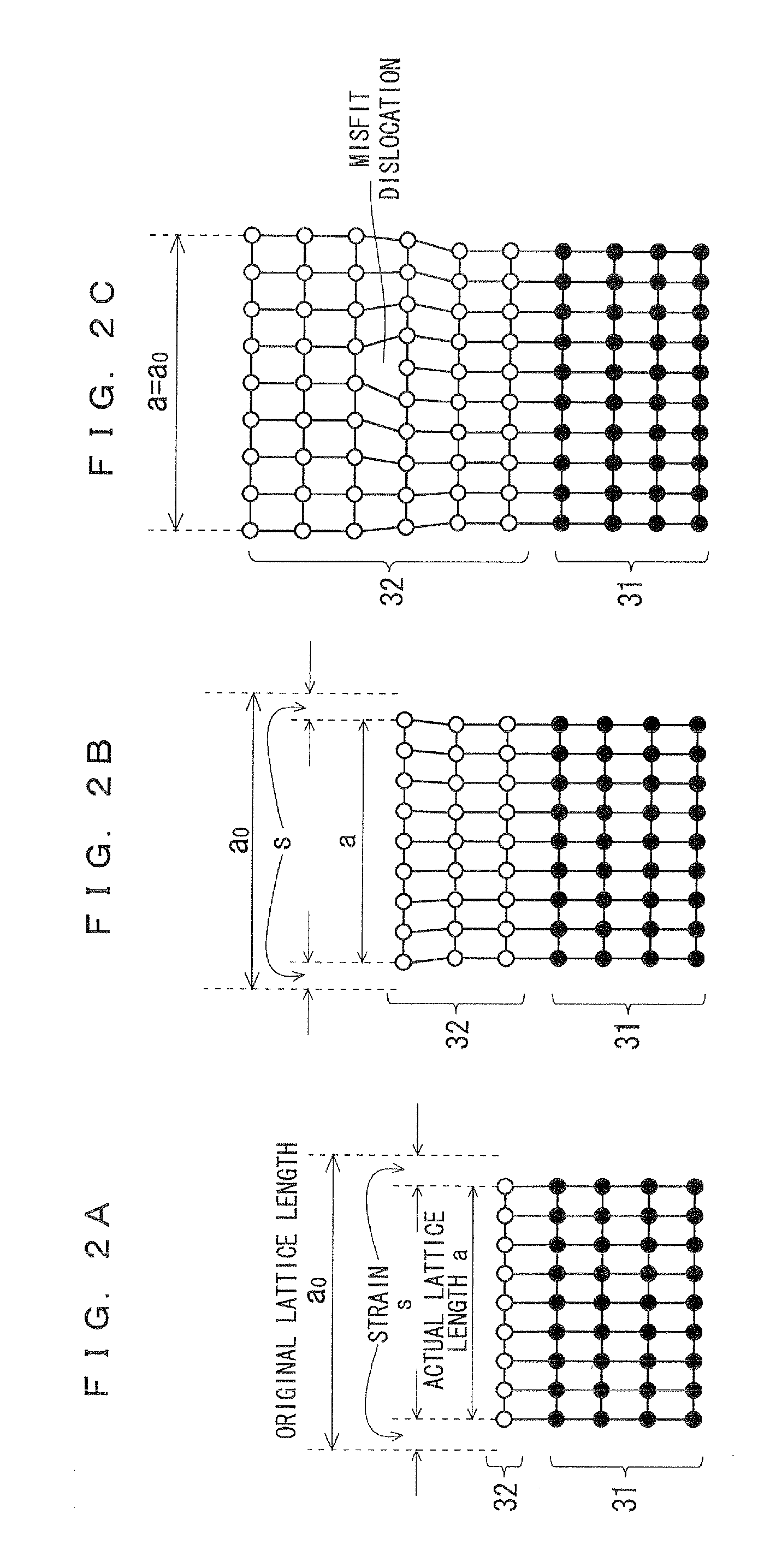

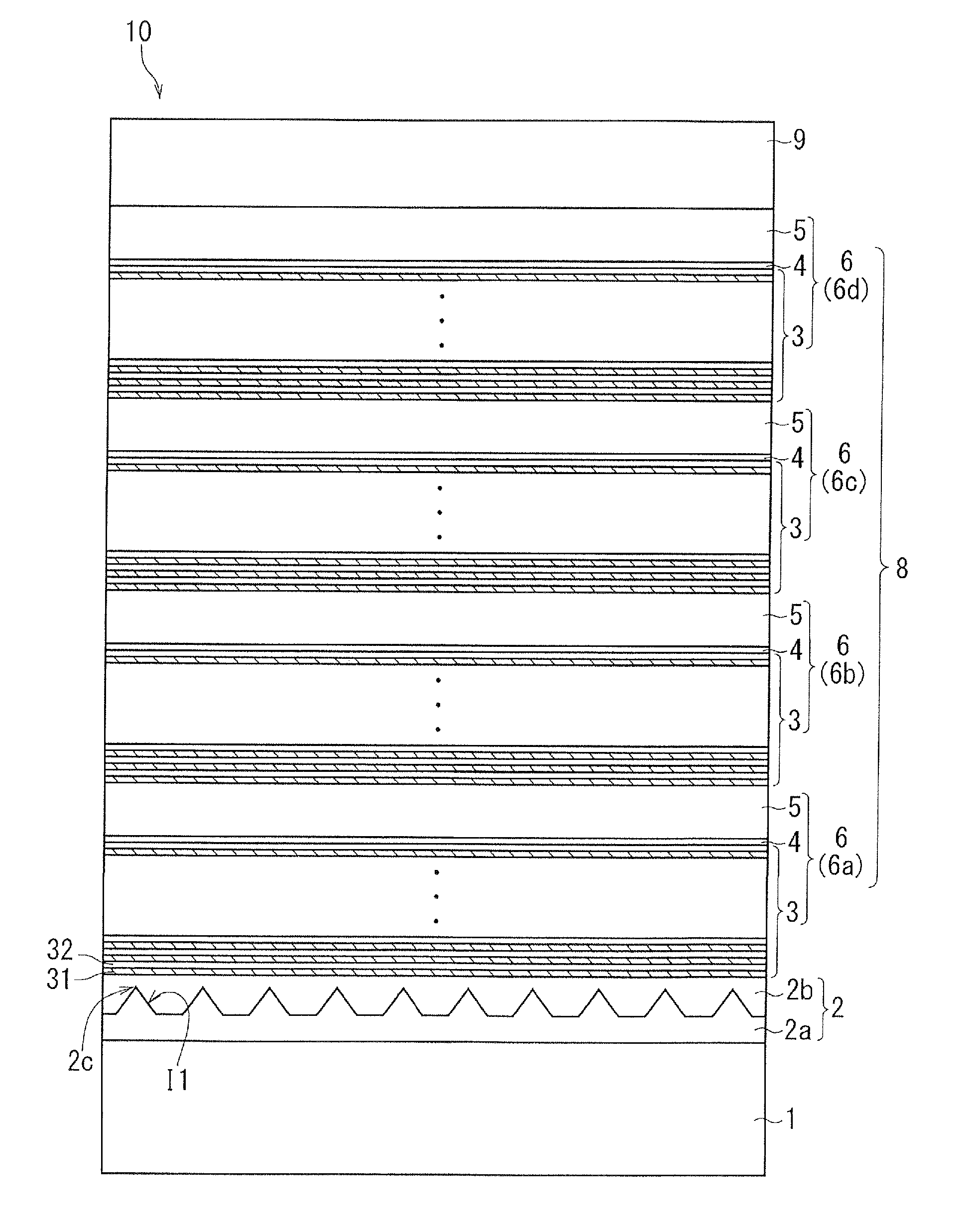

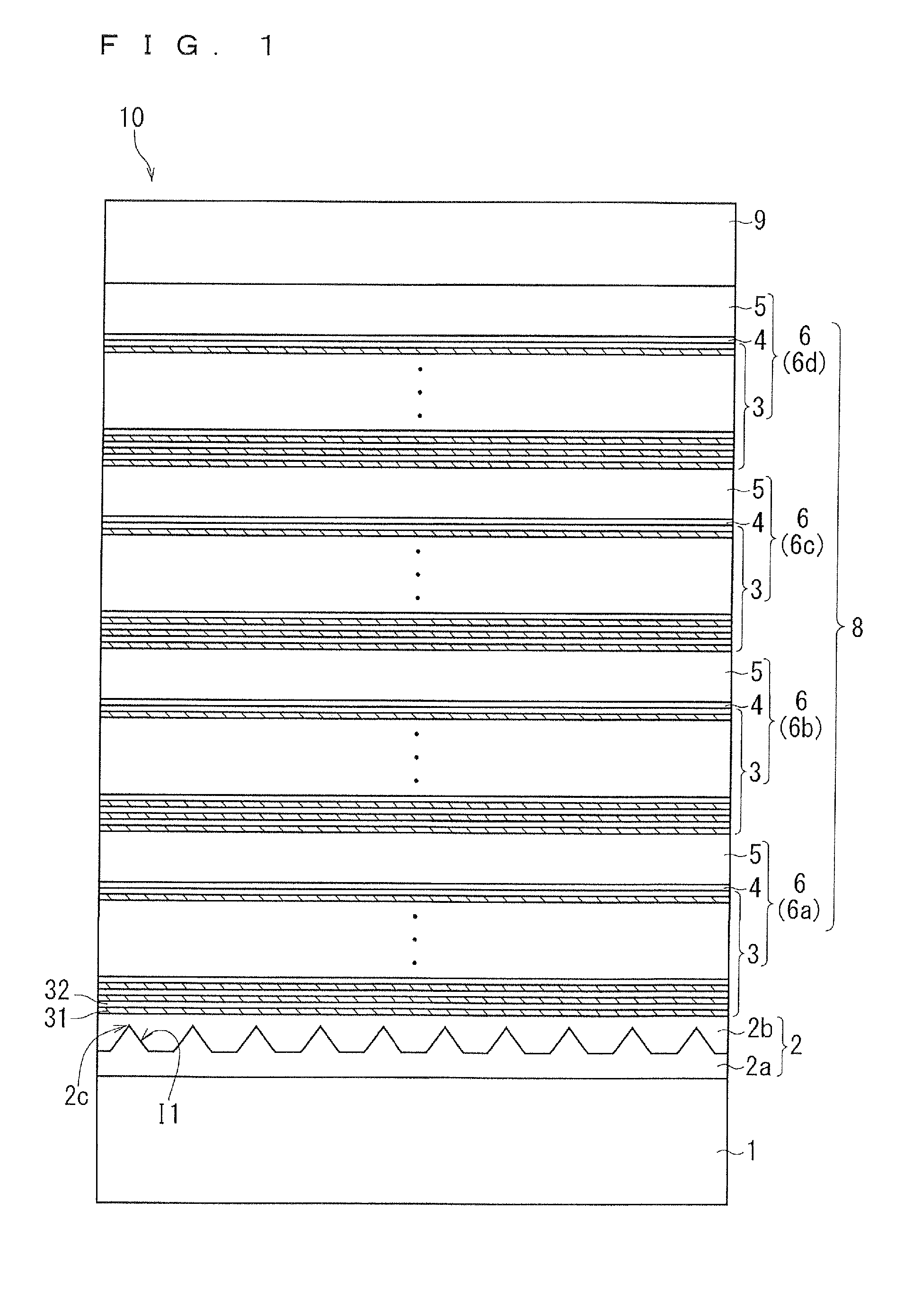

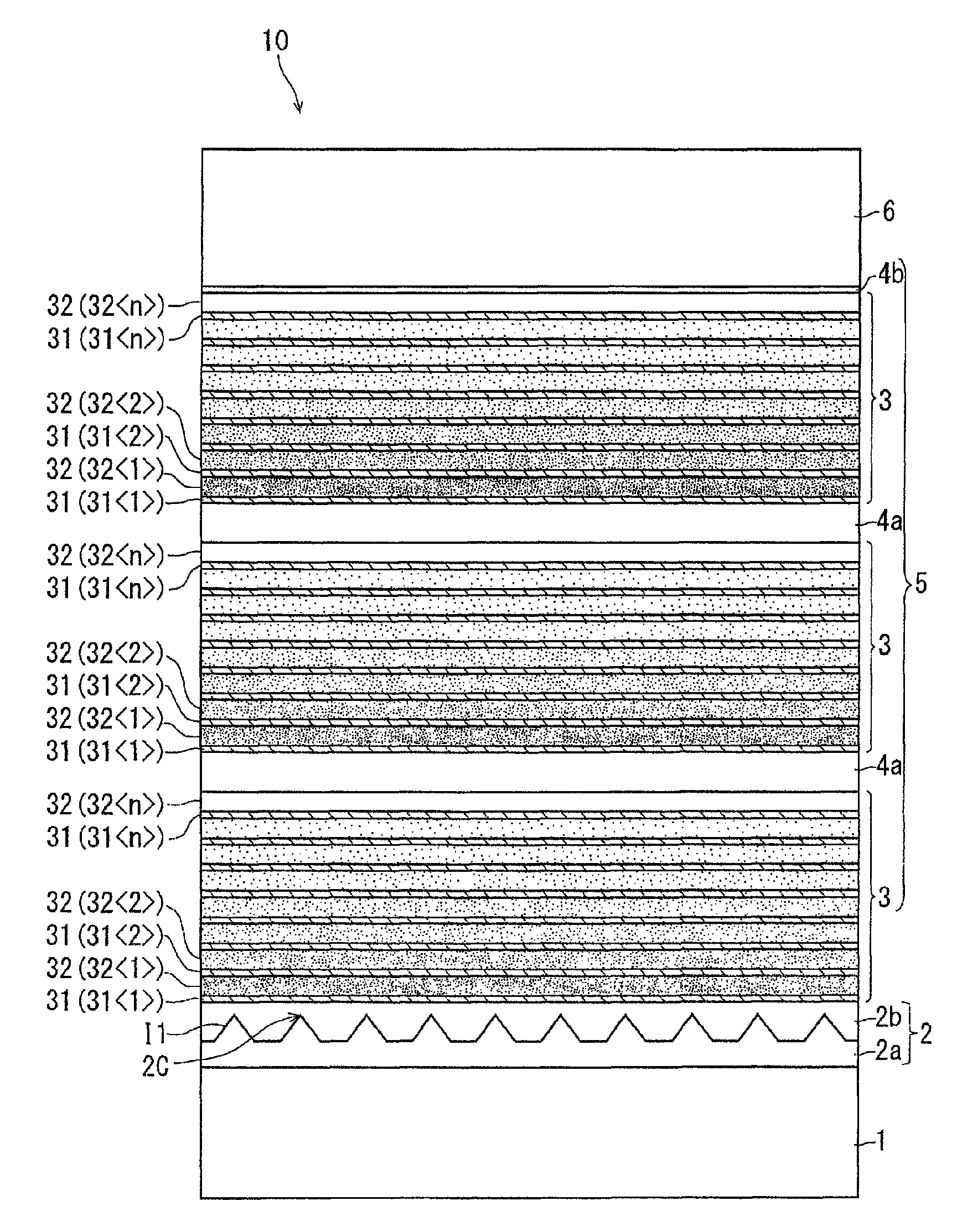

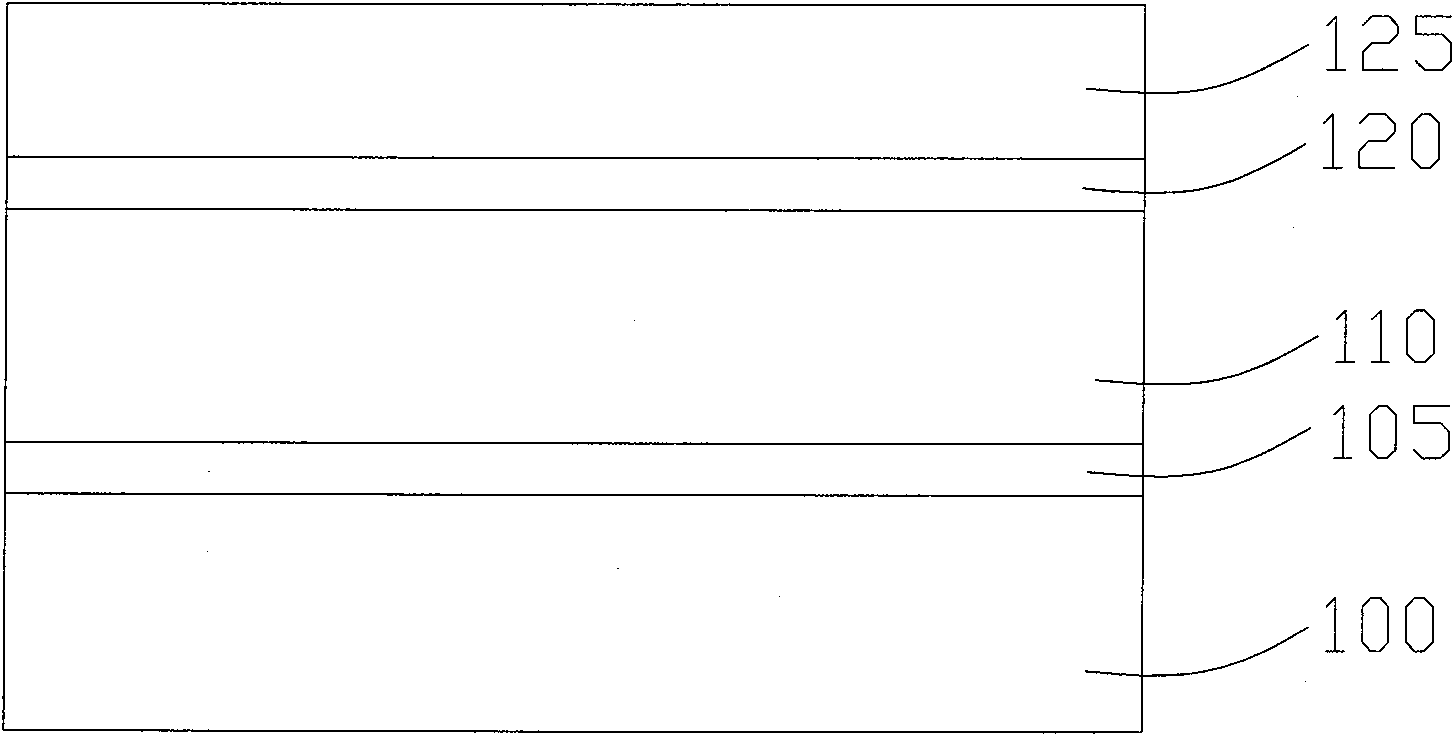

Epitaxial substrate and method for manufacturing epitaxial substrate

ActiveUS20120161152A1Improve crystal qualityImproved breakdown voltage characteristicsPolycrystalline material growthSemiconductor/solid-state device manufacturingInter layerCrack free

Provided is a crack-free epitaxial substrate having a small amount of warping, in which a silicon substrate is used as a base substrate. The epitaxial substrate includes a (111) single crystal Si substrate, a buffer layer, and a crystal layer. The buffer layer is formed of a first lamination unit and a second lamination unit being alternately laminated. The first lamination unit includes a composition modulation layer and a first intermediate layer. The composition modulation layer is formed of a first unit layer and a second unit layer having different compositions being alternately and repeatedly laminated so that a compressive strain exists therein. The first intermediate layer enhances the compressive strain existing in the composition modulation layer. The second lamination unit is a second intermediate layer that is substantially strain-free.

Owner:NGK INSULATORS LTD

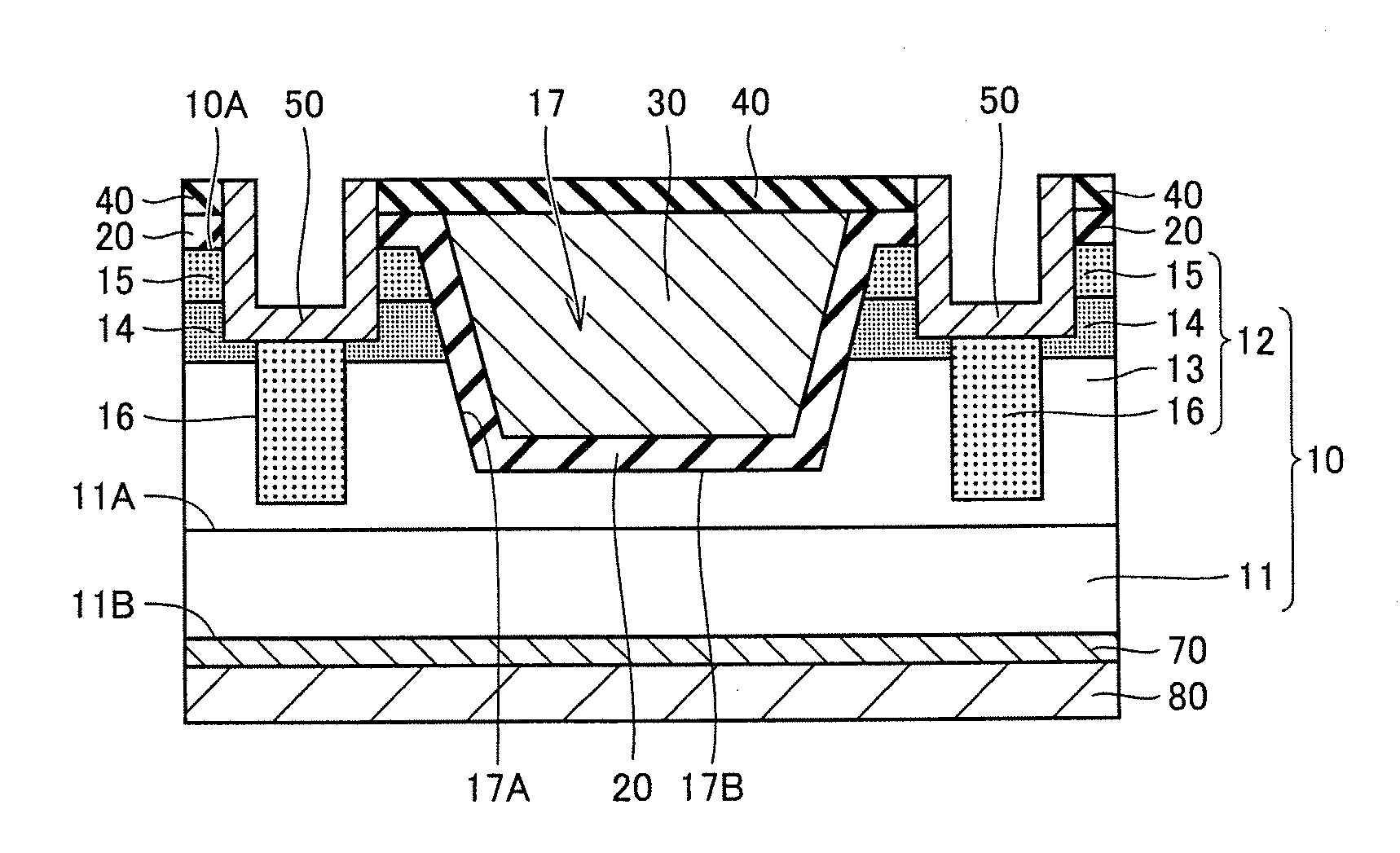

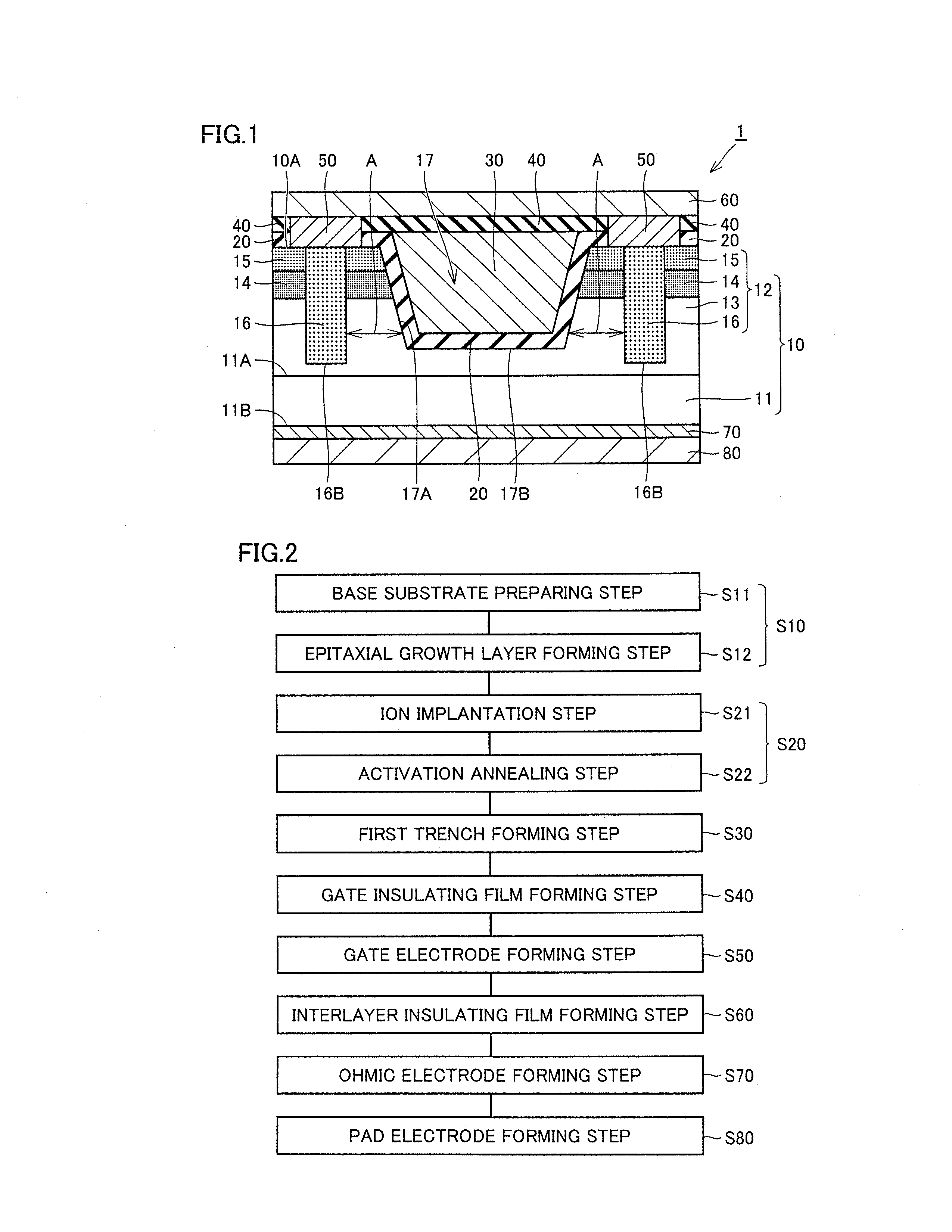

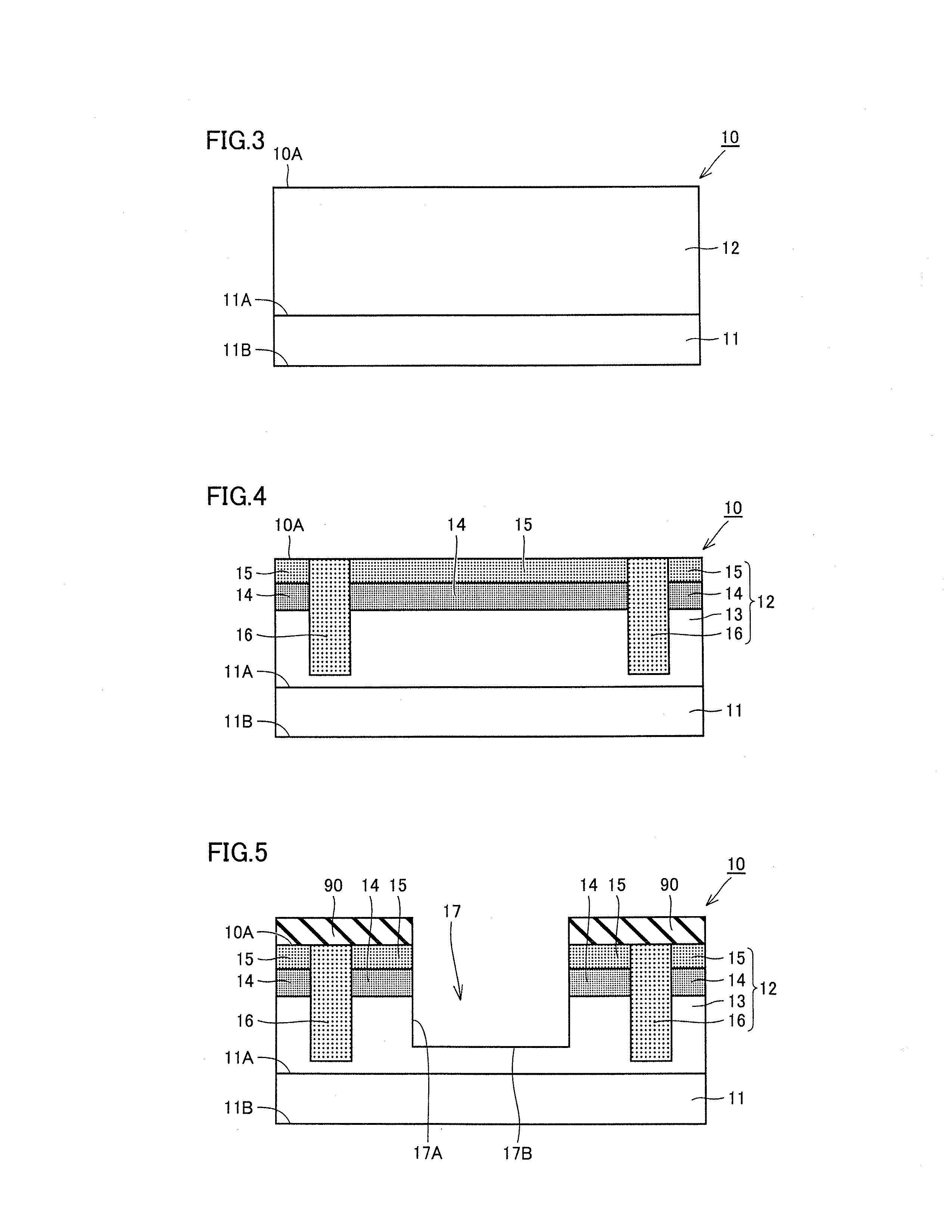

Semiconductor device and method for manufacturing same

ActiveUS20130181229A1Improved breakdown voltage characteristicsReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETBody region

A MOSFET includes: a substrate having a first trench formed therein, the first trench opening on a side of one main surface; a gate insulating film; and a gate electrode. The substrate includes an n type source region, a p type body region, an n type drift region, and a p type deep region making contact with the body region and extending to a region deeper than the first trench. The first trench is formed such that a distance between the wall surface and the deep region increases with increasing distance from the main surface of the substrate.

Owner:SUMITOMO ELECTRIC IND LTD

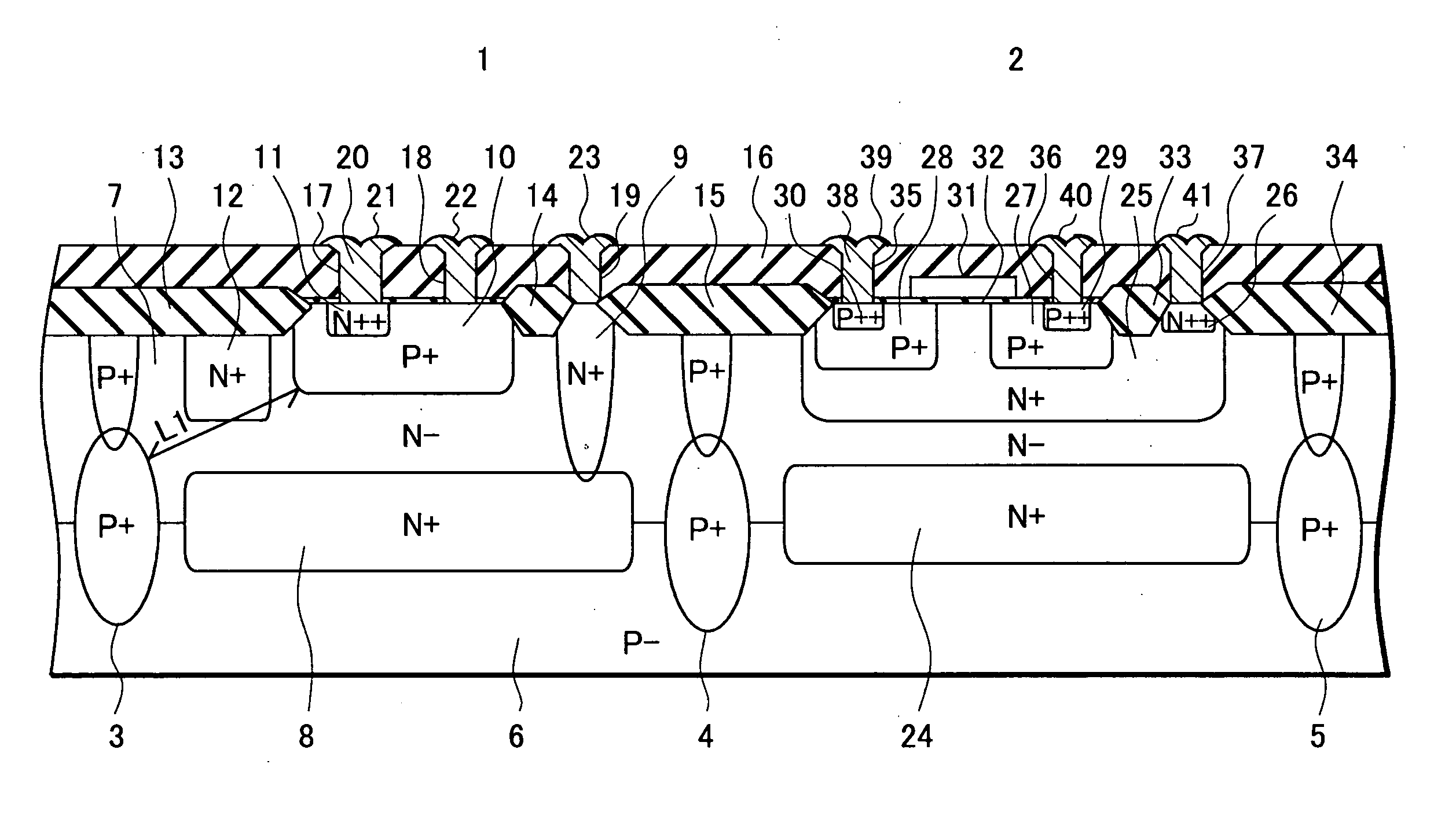

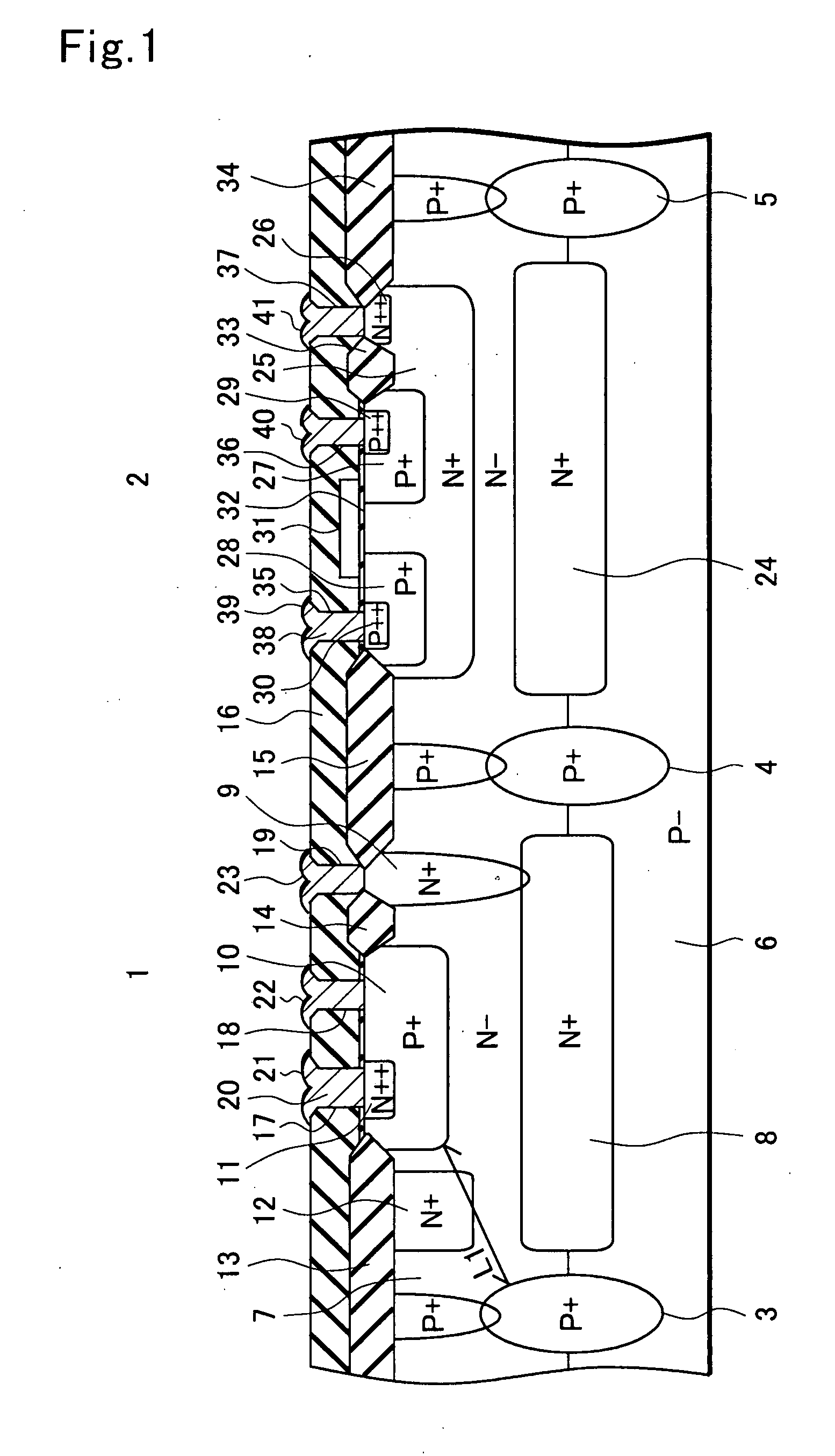

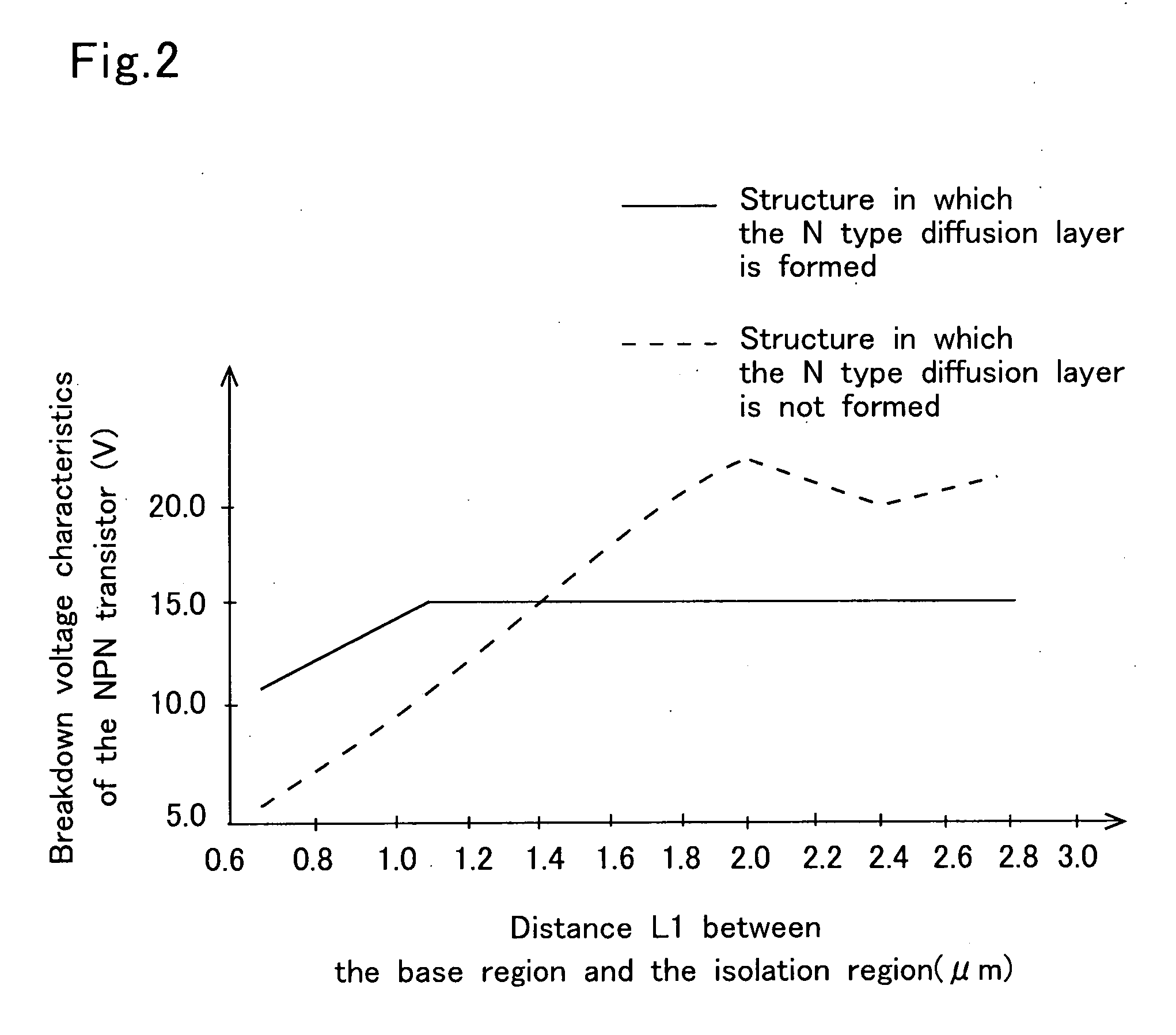

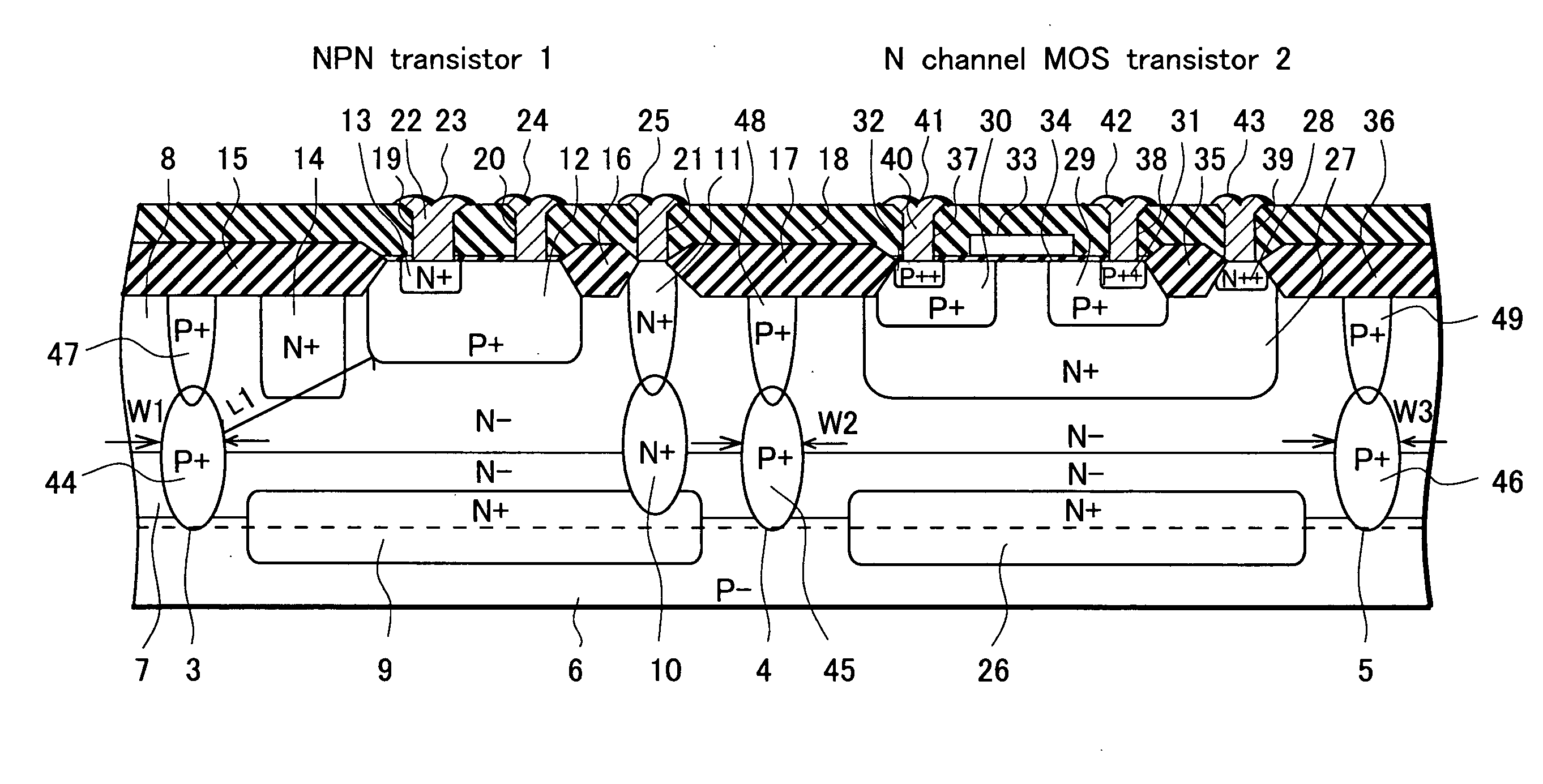

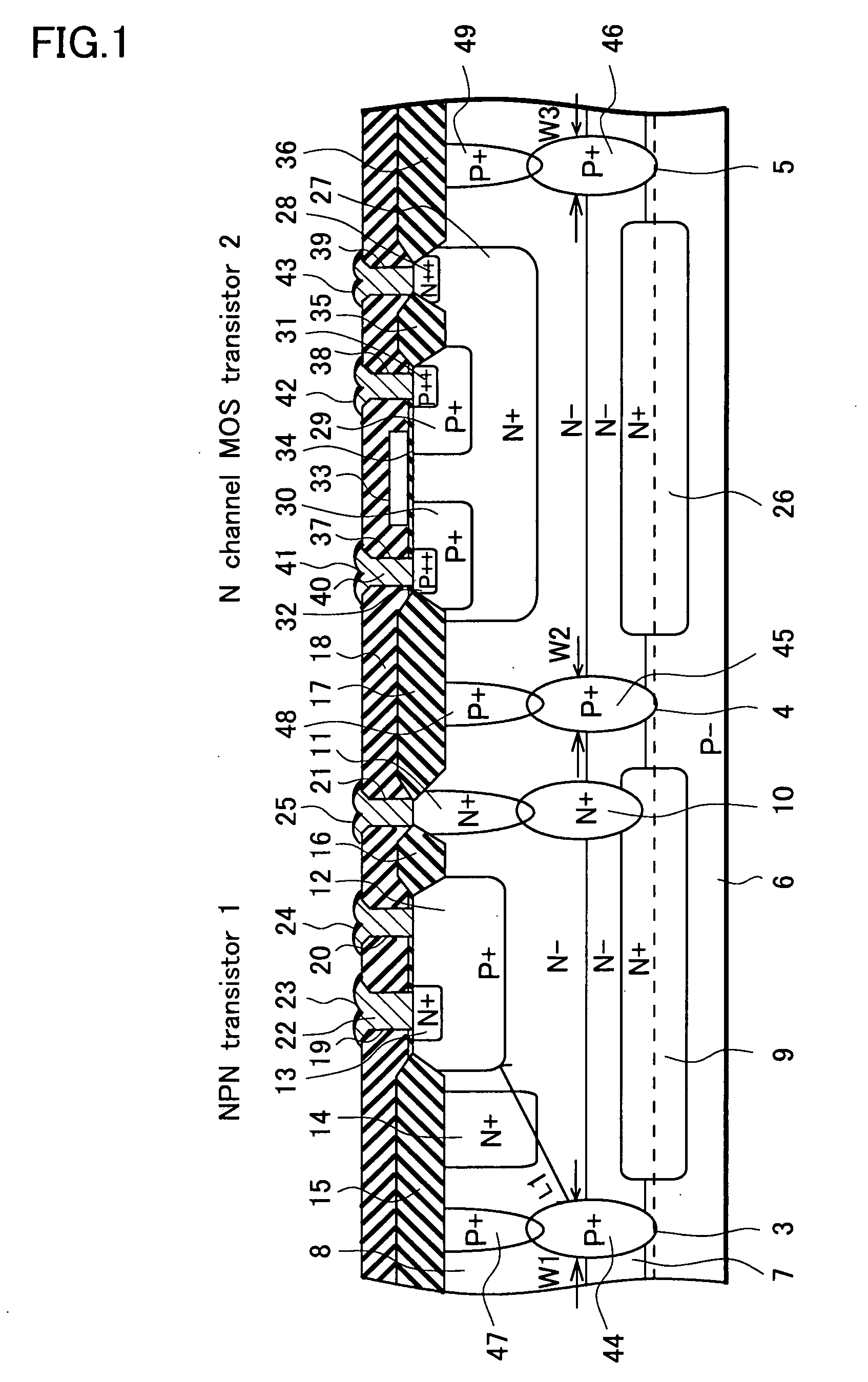

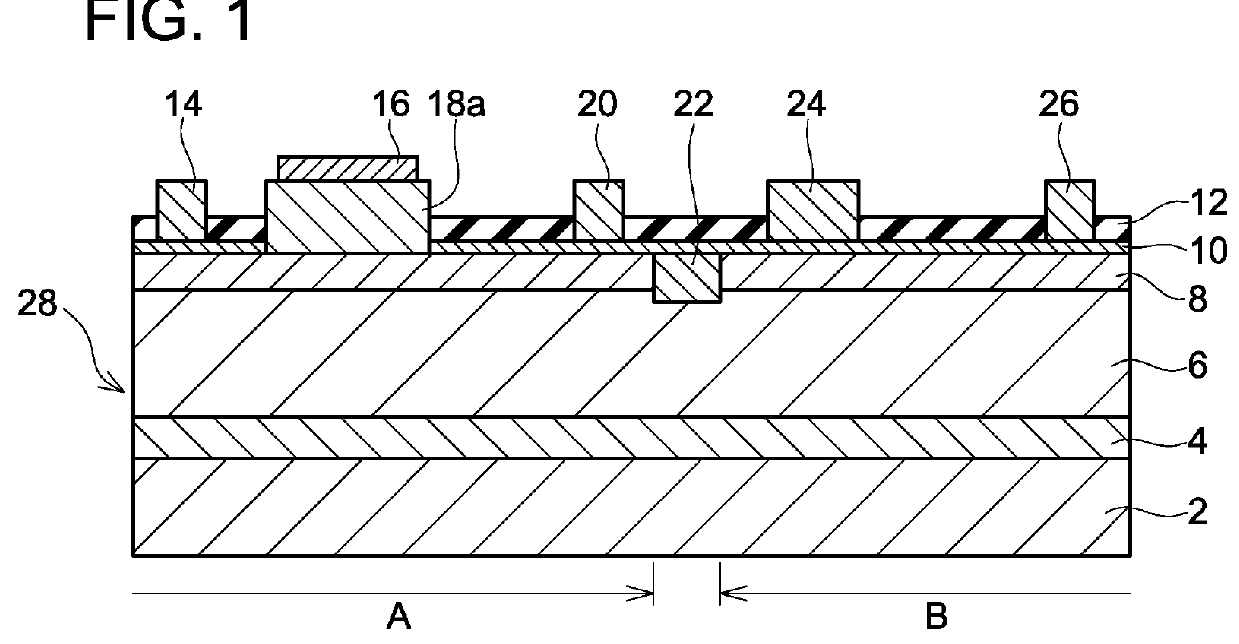

Semiconductor device and method of manufacturing the same

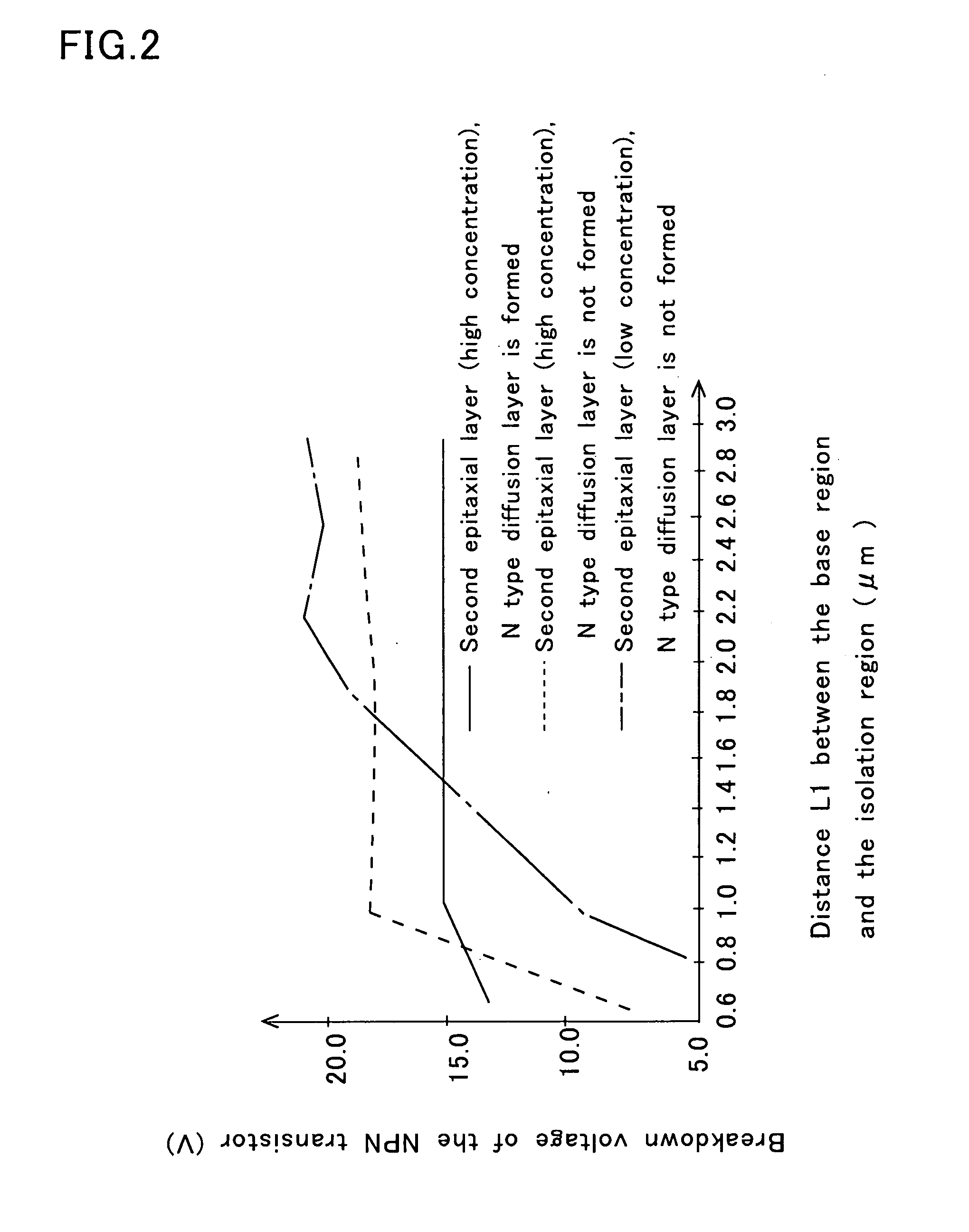

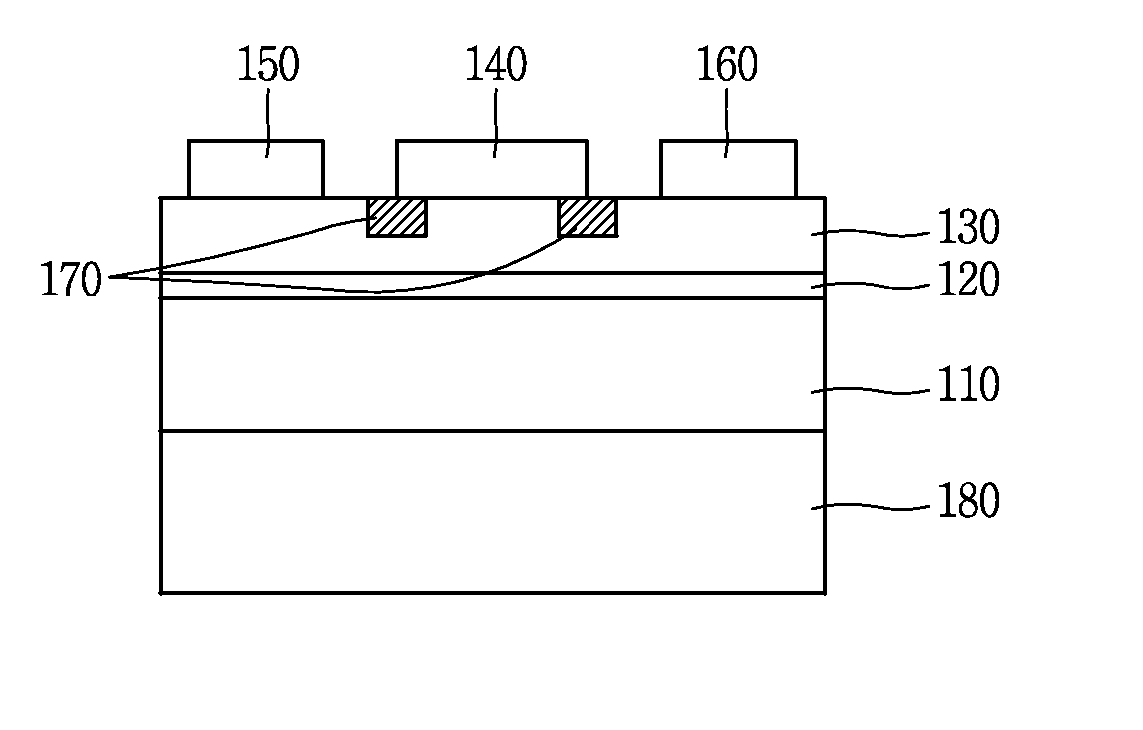

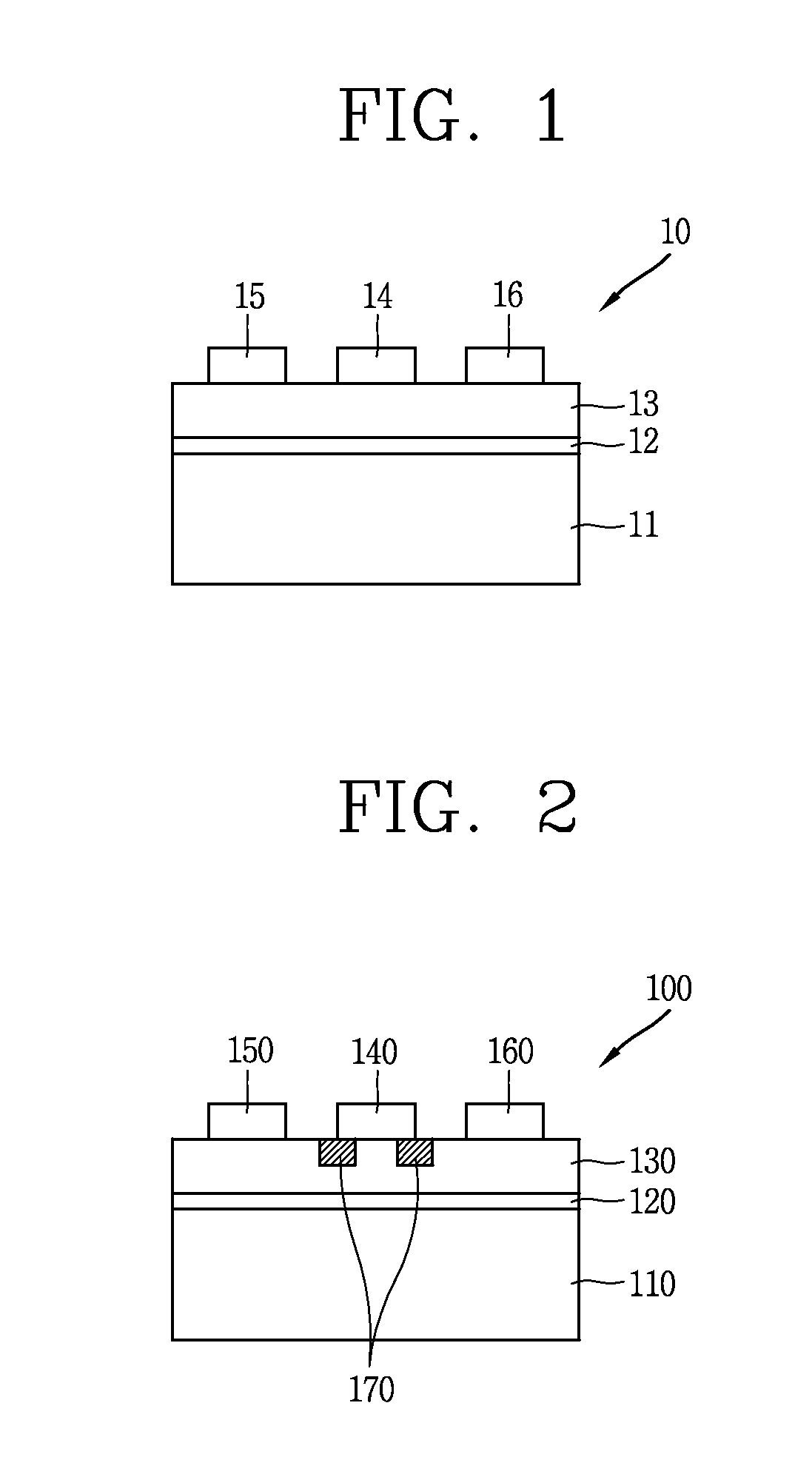

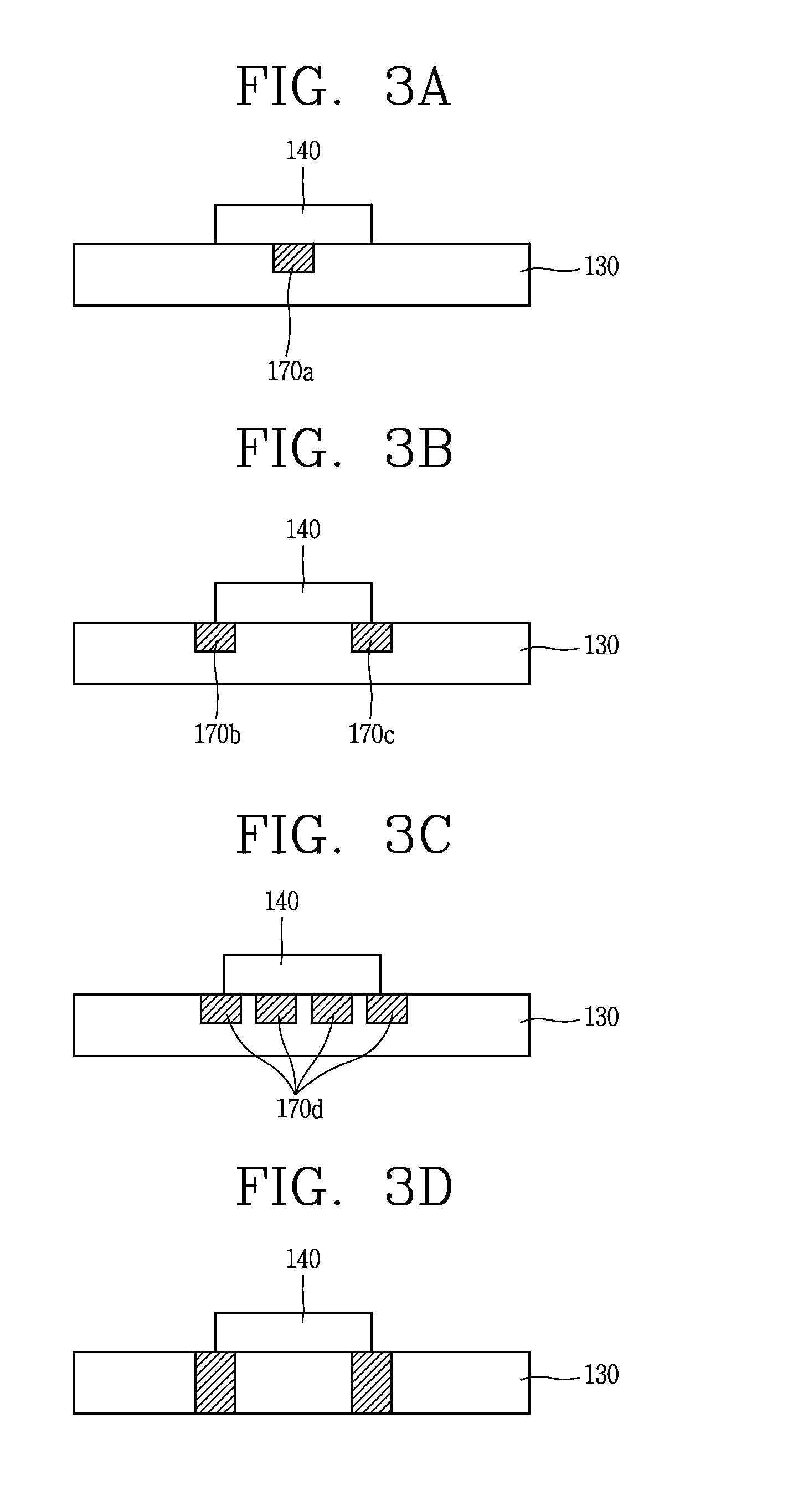

ActiveUS20070145530A1Improve breakdown voltageImproved breakdown voltage characteristicsTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

In a semiconductor device of the present invention, an epitaxial layer is formed on a P type single crystal silicon substrate. Isolation regions are formed in the epitaxial layer, and are divided into a plurality of element formation regions. An NPN transistor is formed in one of the element formation regions. An N type diffusion layer is formed between a P type isolation region and a P type diffusion layer which is used as a base region of the NPN transistor. This structure makes the base region and the isolation region tend not to be short-circuited. Hence, the breakdown voltage characteristics of the NPN transistor can be improved.

Owner:SEMICON COMPONENTS IND LLC

Synchronous electric motor drive system

ActiveUS8497648B2Prevents degradation of inverter efficiencyPrevents an increase of iron lossesTorque ripple controlAC motor controlElectricitySystems design

Owner:PANASONIC CORP

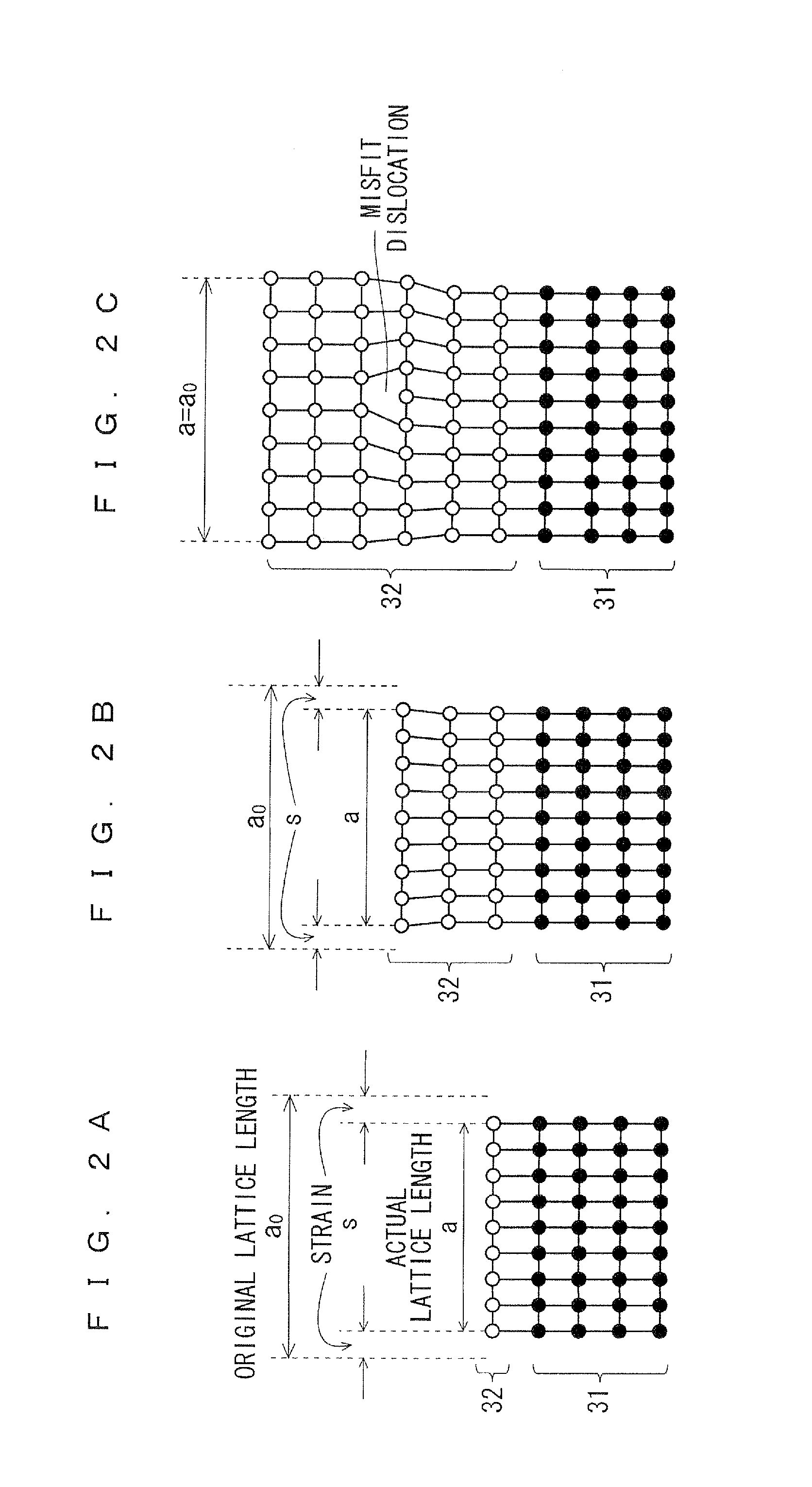

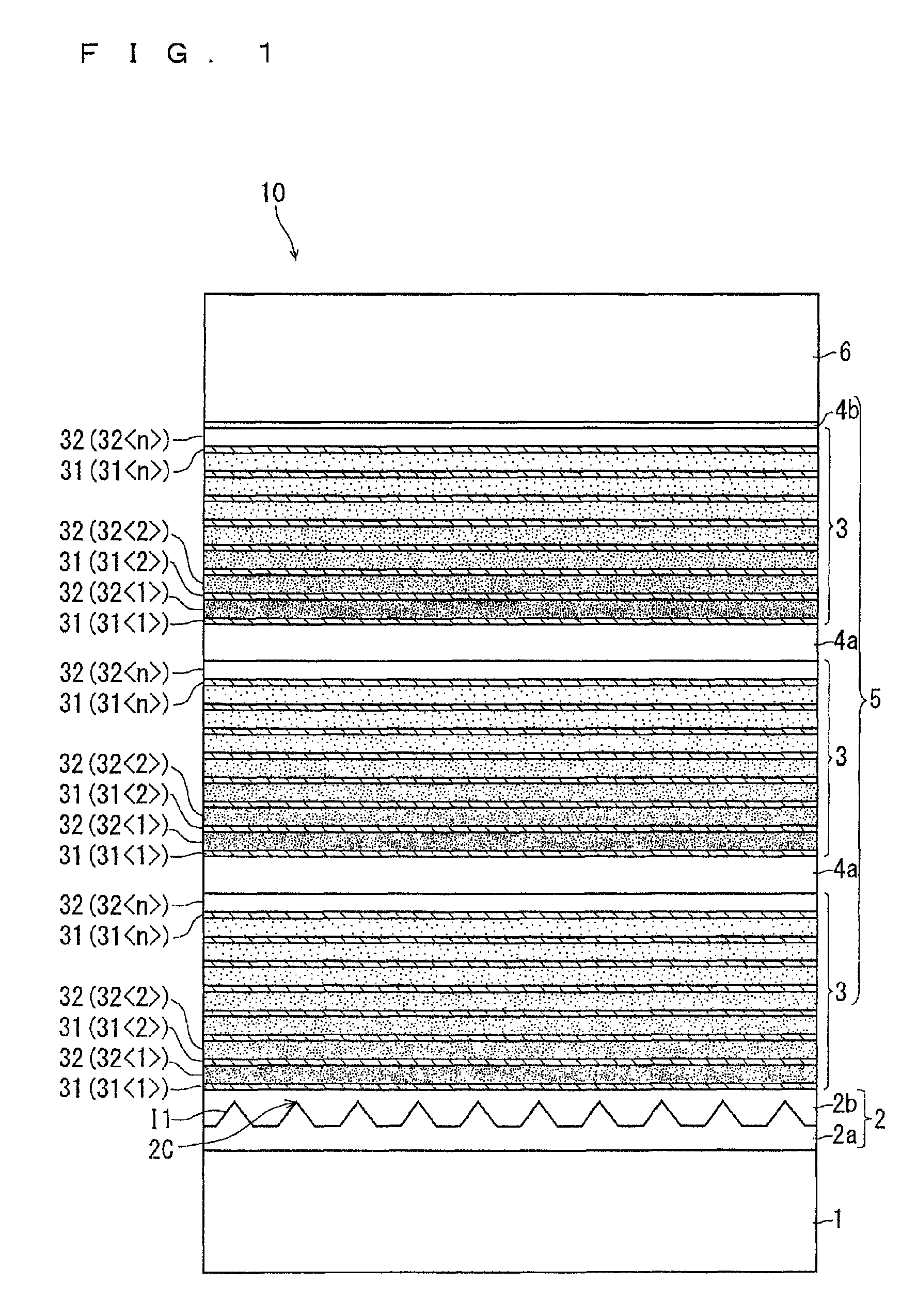

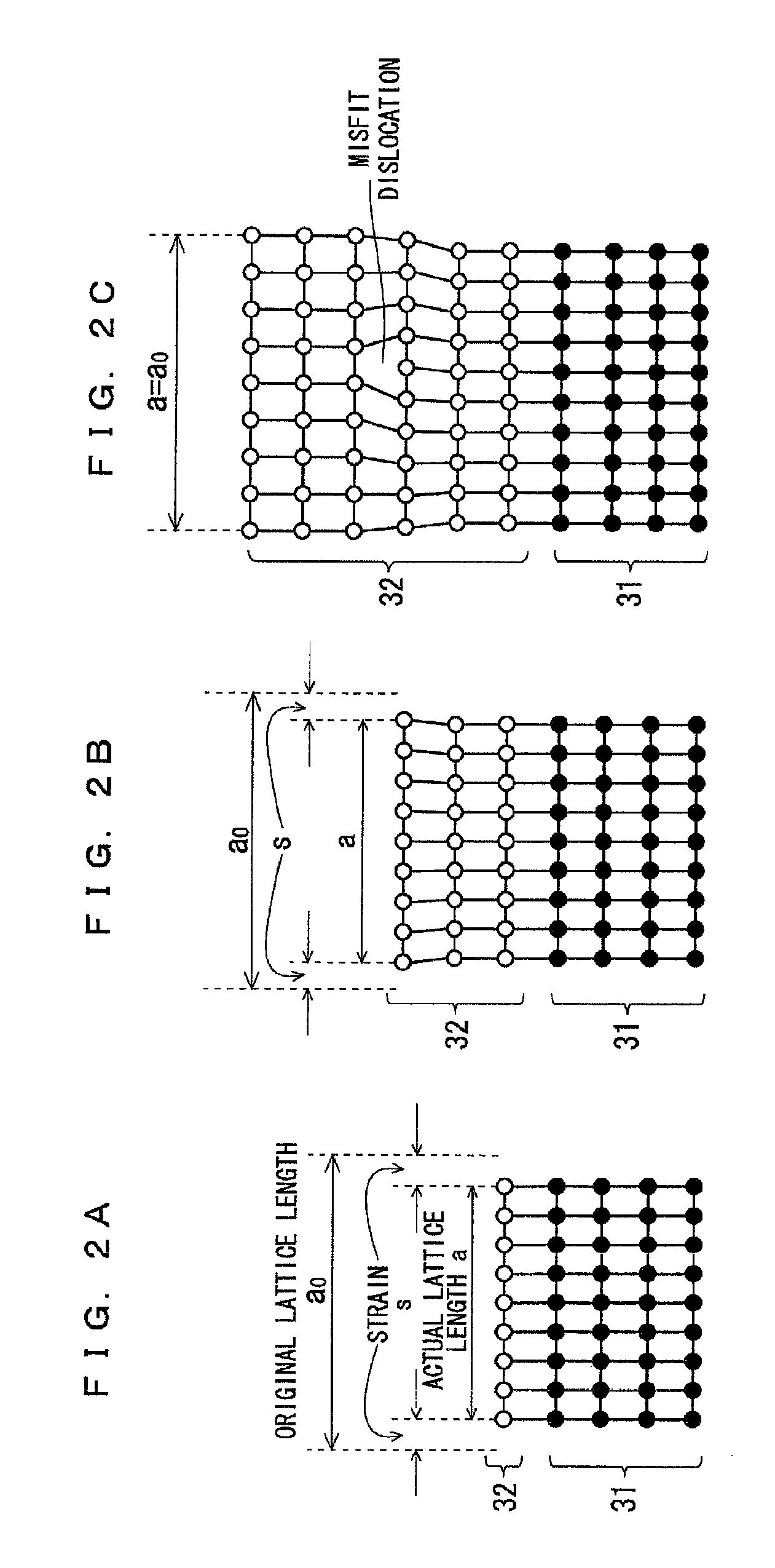

Epitaxial substrate and method for manufacturing epitaxial substrate

InactiveUS20130026488A1Improve breakdown voltageReadily availableTransistorPolycrystalline material growthGalliumSingle crystal

Provided is a crack-free epitaxial substrate having excellent breakdown voltage properties in which a silicon substrate is used as a base substrate thereof. The epitaxial substrate includes: a (111) single crystal Si substrate and a buffer layer including a plurality of composition modulation layers each formed of a first composition layer made of AlN and a second composition layer made of AlxGa1-xN (0≦x<1) being alternately laminated. The relationship of x(1)≧x(2)≧ . . . ≧x(n−1)≧x(n) and x(1)>x(n) is satisfied, where n represents the number of laminations of each of the first and the second composition layer, and x(i) represents the value of x in i-th one of the second composition layers as counted from the base substrate side. Each of the second composition layers is formed so as to be in a coherent state relative to the first composition layer.

Owner:NGK INSULATORS LTD

Epitaxial substrate and method for manufacturing epitaxial substrate

InactiveUS20130092953A1Improve crystal qualityImproved breakdown voltage characteristicsTransistorSemiconductor/solid-state device manufacturingEngineeringSingle crystal

Provided is a crack-free epitaxial substrate having a small amount of warping, in which a silicon substrate is used as a base substrate. The epitaxial substrate includes: a (111) single crystal Si substrate and a buffer layer formed of a plurality of lamination units being continuously laminated. The lamination unit includes: a composition modulation layer formed of a first and a second unit layer having different compositions being alternately and repeatedly laminated such that a compressive strain exists therein; a termination layer formed on an uppermost portion of the composition modulation layer, the termination layer acting to maintain the compressive strain existing in the composition modulation layer; and a strain reinforcing layer formed on the termination layer, the strain reinforcing layer acting to enhance the compressive strain existing in the composition modulation layer.

Owner:NGK INSULATORS LTD

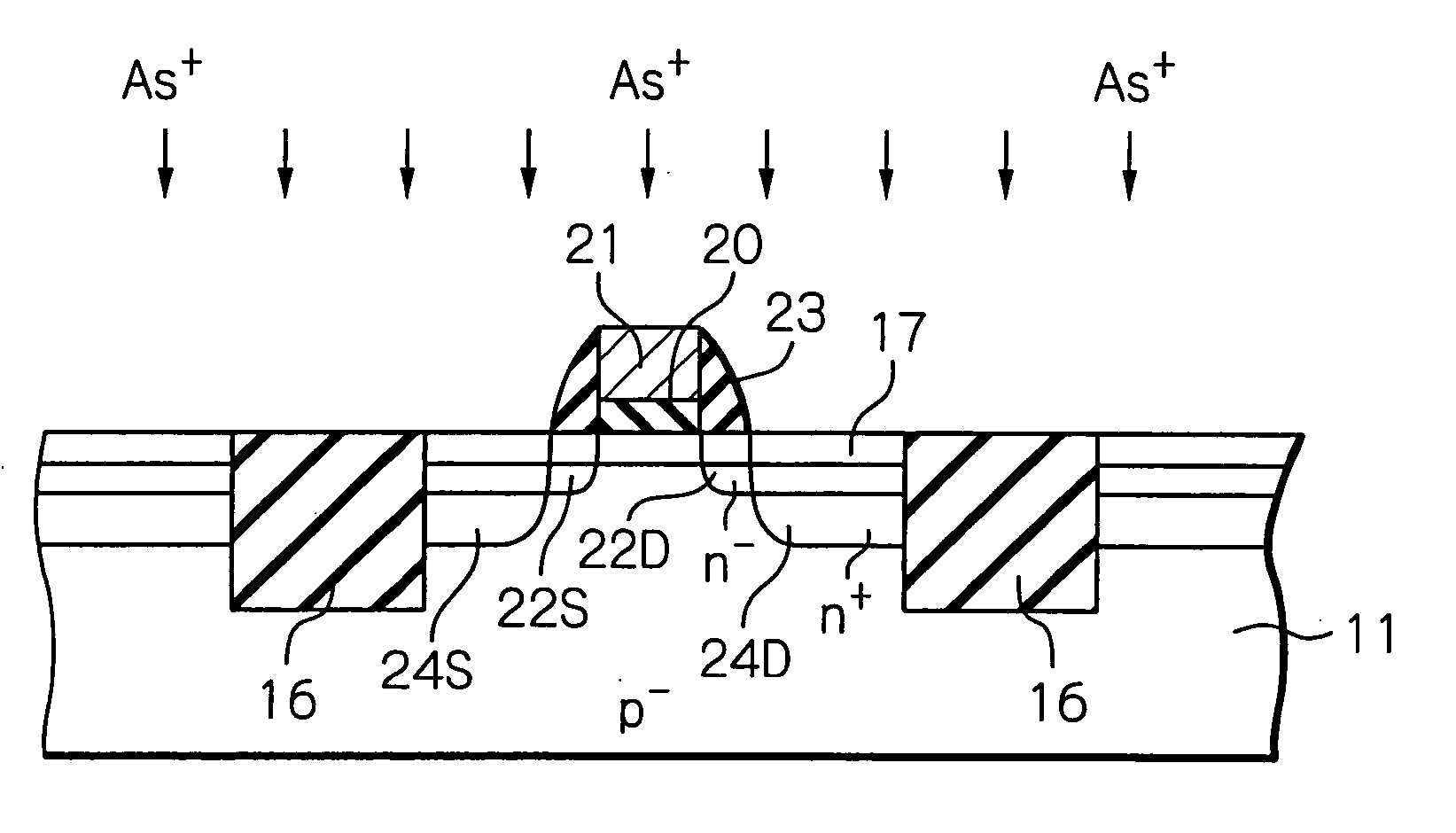

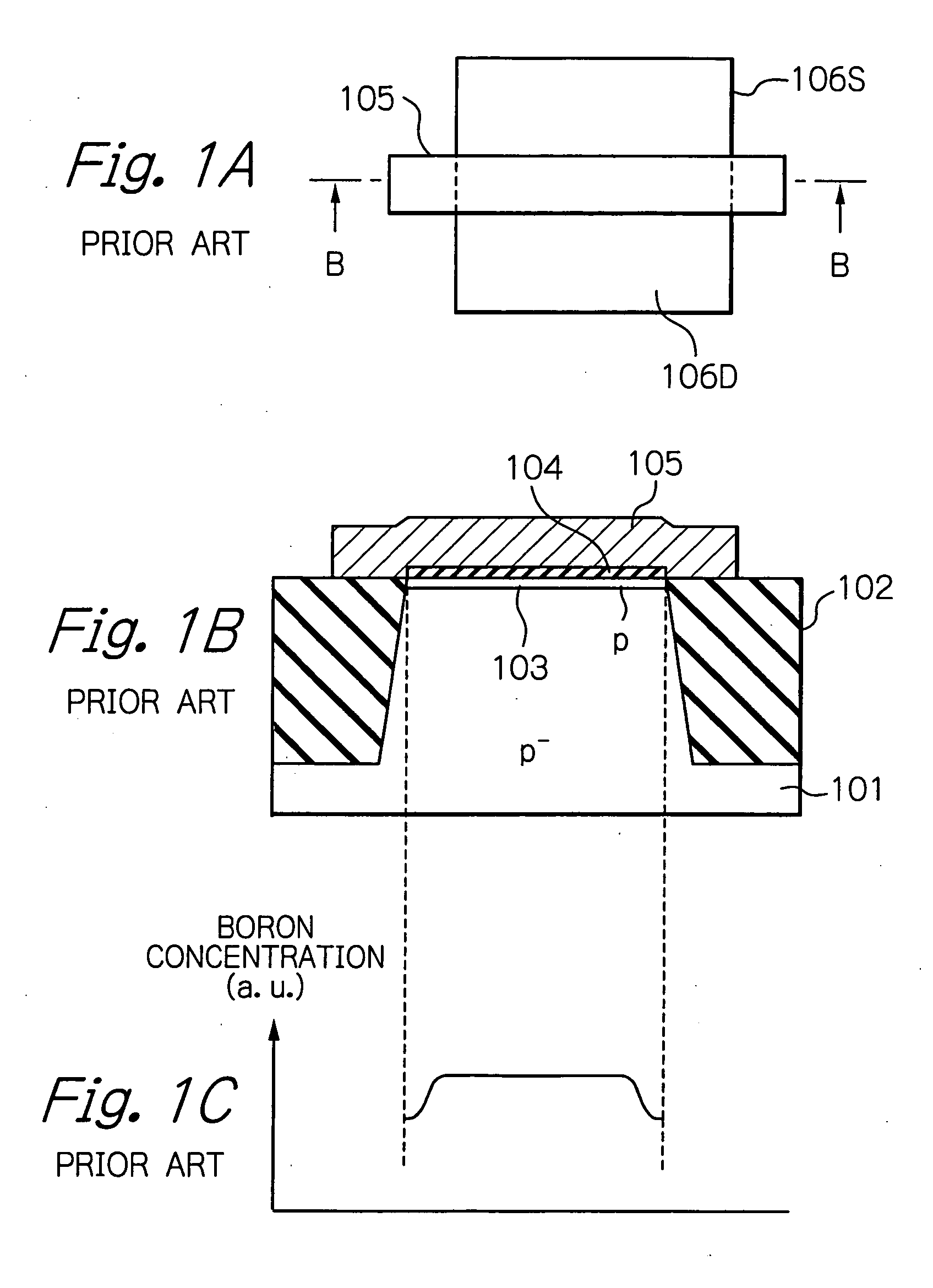

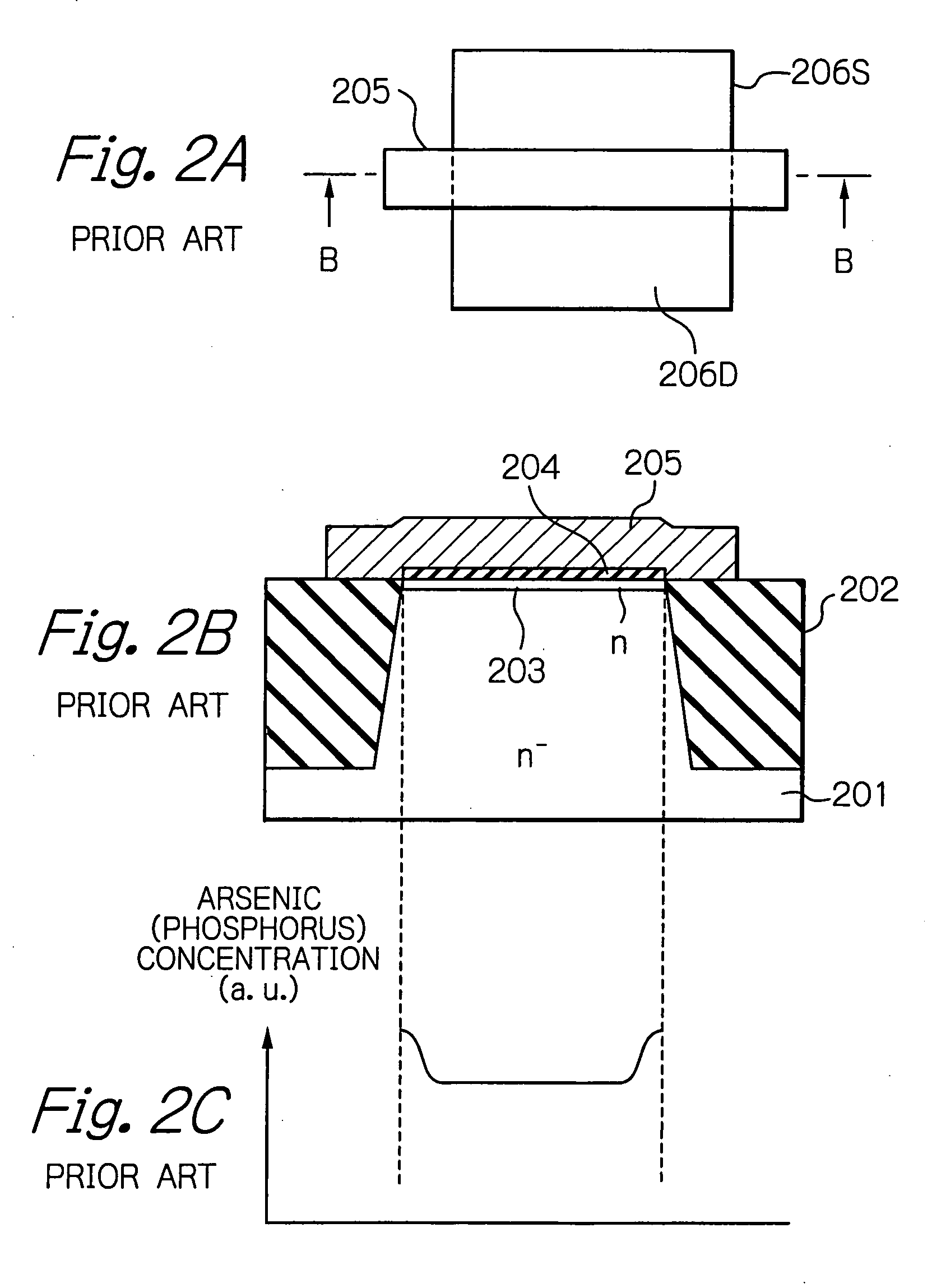

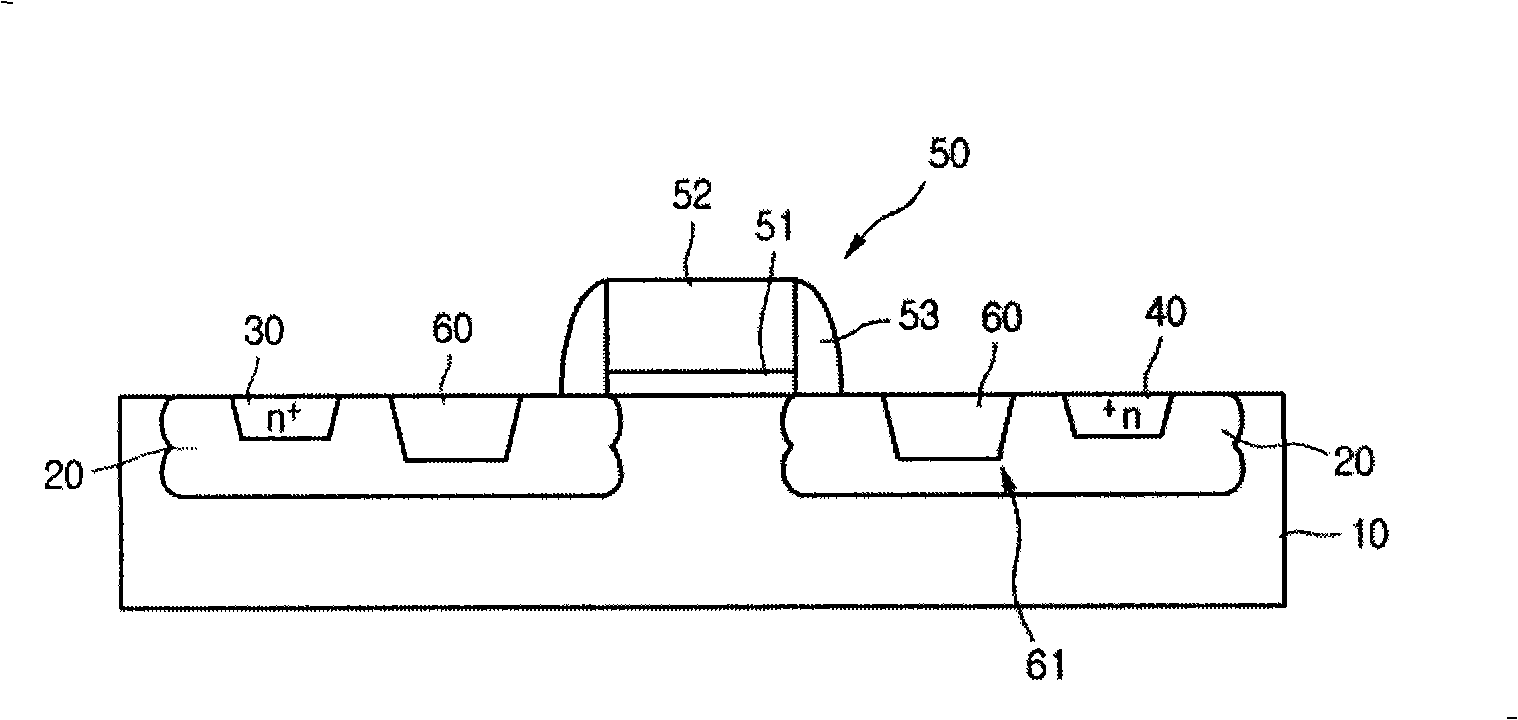

Method for manufacturing semiconductor device capable of improving breakdown voltage characteristics

InactiveUS20060240627A1Improved breakdown voltage characteristicsTransistorSolid-state devicesDevice materialIsolation layer

In a method for manufacturing a MOS transistor, a MOS transistor isolation layer is formed within a semiconductor substrate to surround an area for forming the MOS transistor in the semiconductor substrate. Then, first impurities are introduced into the area of the semiconductor substrate to adjust a threshold voltage of the MOS transistor. Also, second impurities are introduced into only a part of a periphery of the above-mentioned area adjacent to the MOS transistor isolation layer above which a gate electrode of the MOS transistor will be formed.

Owner:NEC ELECTRONICS CORP

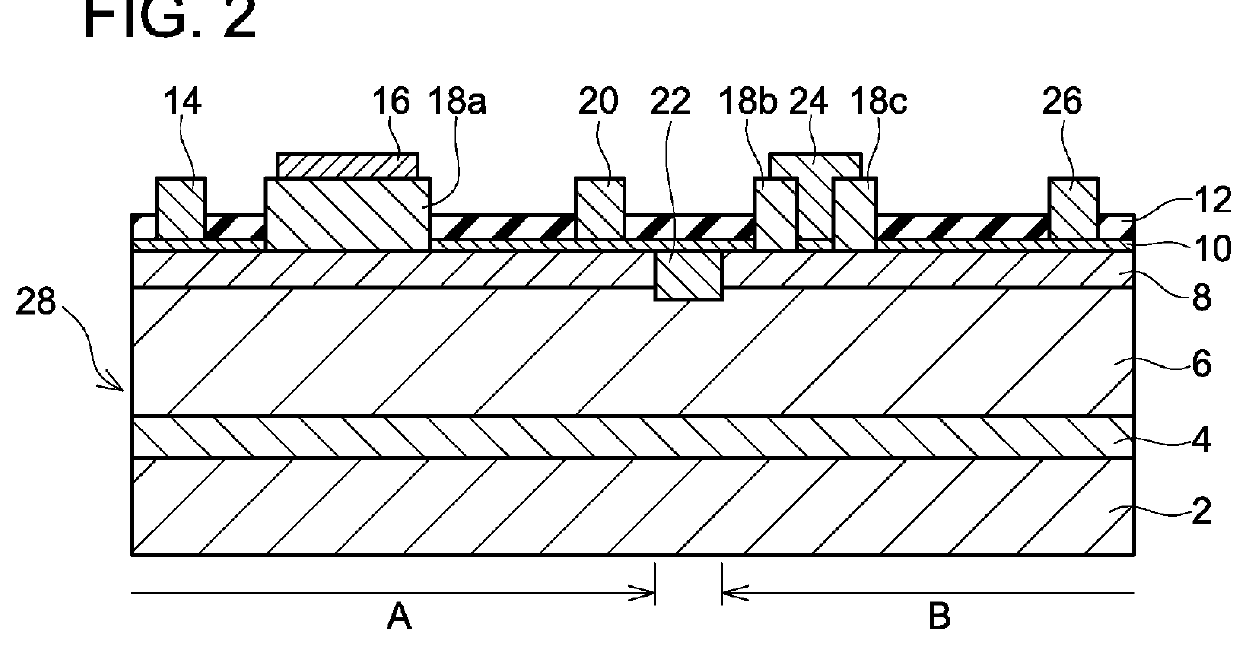

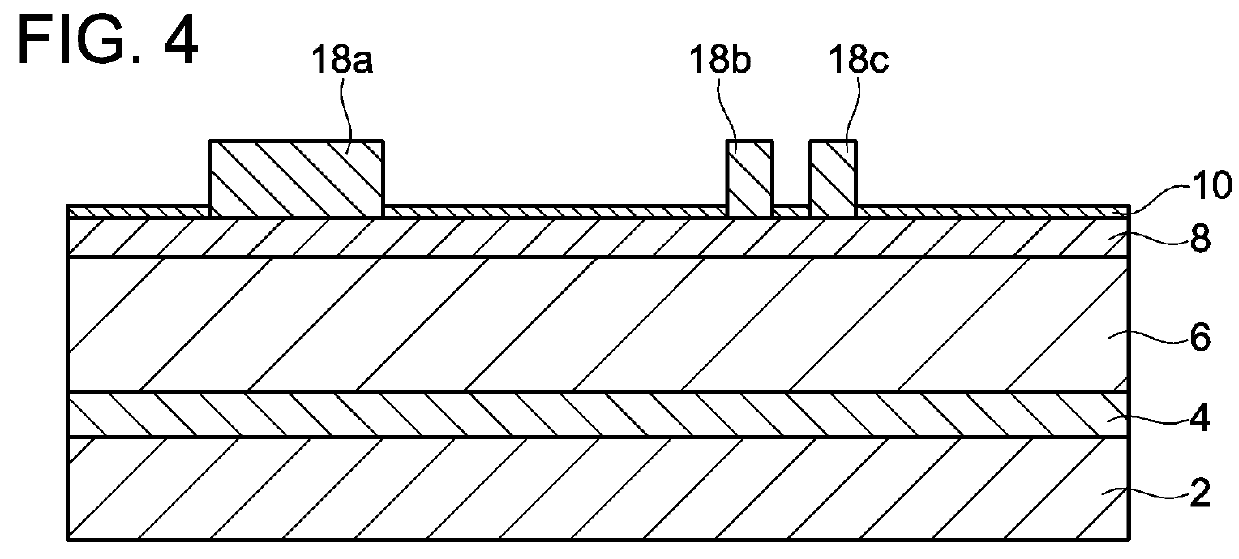

Semiconductor device and manufacturing method of the same

InactiveUS20070145520A1Improved breakdown voltage characteristicsDifficulty occurTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

In a semiconductor device of the present invention, two epitaxial layers are formed on a P type single crystal silicon substrate. One of the epitaxial layers has an impurity concentration higher than that of the other epitaxial layer. The epitaxial layers are divided into a plurality of element formation regions by isolation regions. In one of the element formation regions, an NPN transistor is formed. Moreover, between a P type diffusion layer, which is used as a base region of the NPN transistor, and a P type isolation region, an N type diffusion layer is formed. Use of this structure makes it hard for a short-circuit to occur between the base region and the isolation region. Thus, the breakdown voltage characteristics of the NPN transistor can be improved.

Owner:SEMICON COMPONENTS IND LLC

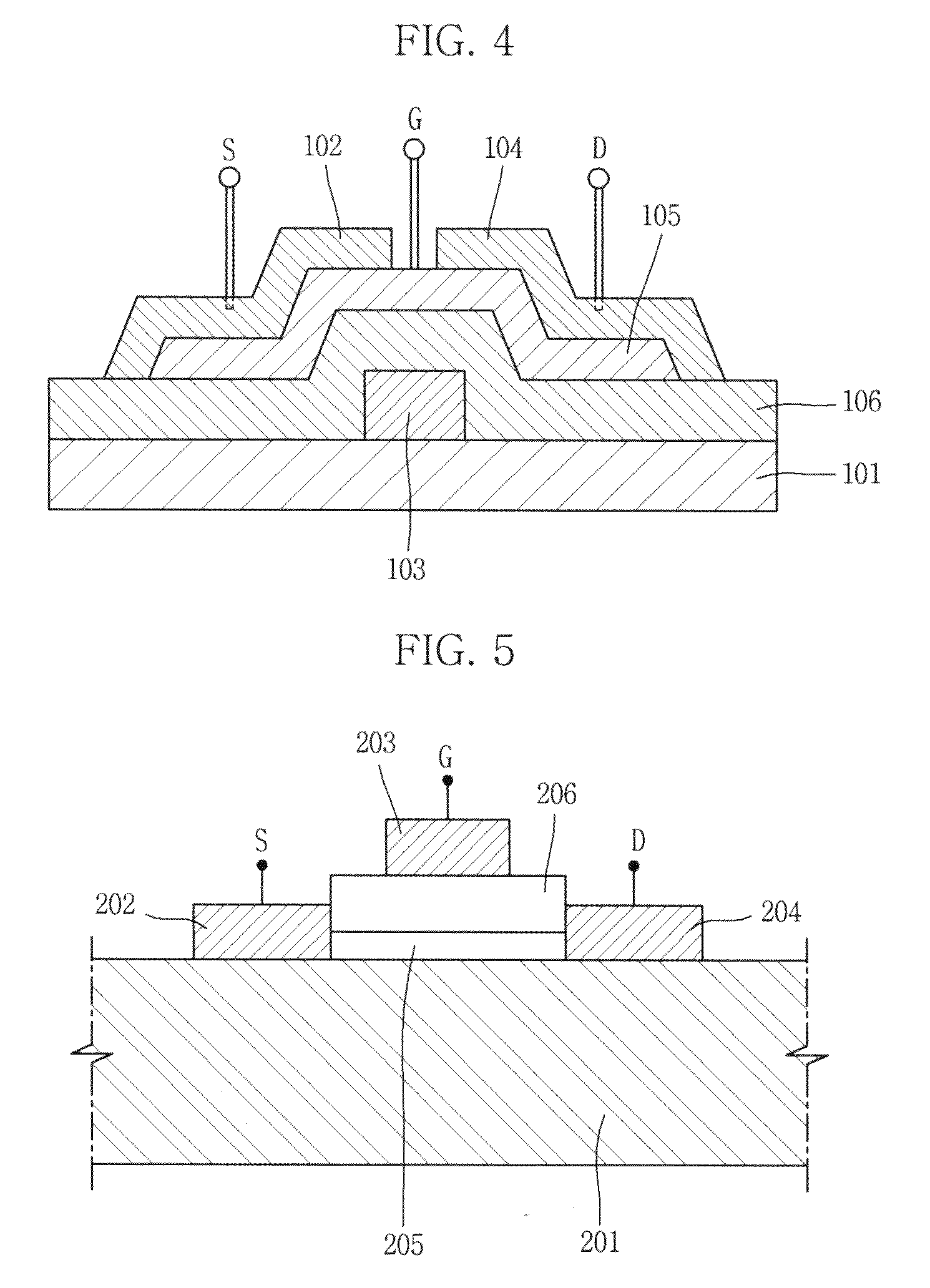

Nitride semiconductor device using selective growth and manufacturing method thereof

ActiveUS20130153921A1Reduce and remove leakage currentImproved breakdown voltage characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A semiconductor device including a first GaN layer, an AlGaN layer, a second GaN layer, a gate electrode, a source electrode, and a drain electrode sequentially stacked on a substrate, capable of improving a leakage current and a breakdown voltage characteristics generated in the gate electrode by locally forming a p type GaN layer on the AlGaN layer, and a manufacturing method thereof, and a manufacturing method thereof are provided.The semiconductor device includes: a substrate, a first GaN layer formed on the substrate, an AlGaN layer formed on the first GaN layer, a second GaN layer formed on the AlGaN layer and including a p type GaN layer, and a gate electrode formed on the second GaN layer, wherein the p type GaN layer may be in contact with a portion of the gate electrode.

Owner:LG ELECTRONICS INC

Semiconductor device and method of manufacturing the same

ActiveUS20160035719A1Avoid damageAvoid etch damageTransistorSolid-state devicesDevice materialElectrode Contact

Both a HEMT and a SBD are formed on a nitride semiconductor substrate. The nitride semiconductor substrate comprises a HEMT gate structure region and an anode electrode region. A first laminated structure is formed at least in the HEMT gate structure region, and includes first to third nitride semiconductor layers. A second laminated structure is formed at least in a part of the anode electrode region, and includes first and second nitride semiconductor layers. The anode electrode contacts the front surface of the second nitride semiconductor layer. At least in a contact region in which the front surface of the second nitride semiconductor layer contacts the anode electrode, the front surface of the second nitride semiconductor layer is finished to be a surface by which the second nitride semiconductor layer forms a Schottky junction with the anode electrode.

Owner:TOYOTA CENT RES & DEV LAB INC +1

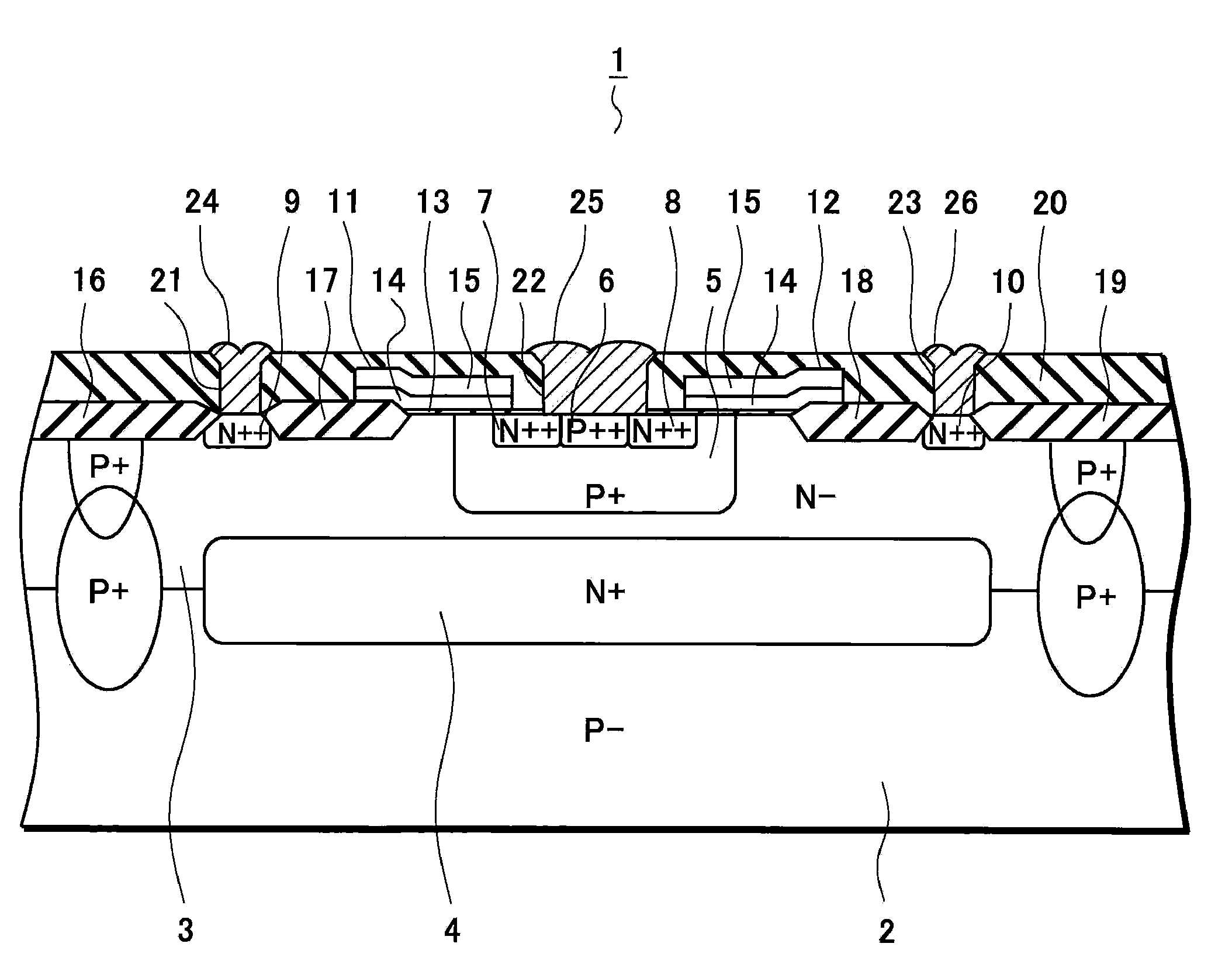

Semiconductor device and method of manufacturing the same

InactiveUS20080001185A1Improved breakdown voltage characteristicsReduce resistanceSemiconductor devicesElectrical resistance and conductancePeak value

In a semiconductor device, for example, a MOS transistor, of the present invention, a P type diffusion layer as a back gate region is formed in an N type epitaxial layer. An N type diffusion layer as a source region is formed in the P type diffusion layer. The P type diffusion layer is formed to have an impurity concentration peak deeper than the N type diffusion layers. This structure reduces a resistance value of a base region of a parasitic transistor, suppresses an increase in an electric potential of a base region in the MOS transistor, and thereby prevents the parasitic transistor from operating. Moreover, a breakdown voltage characteristic of the MOS transistor, which might be deteriorated by the operation of the parasitic transistor, is improved.

Owner:SANYO ELECTRIC CO LTD

Semiconductor device and method for fabricating the same

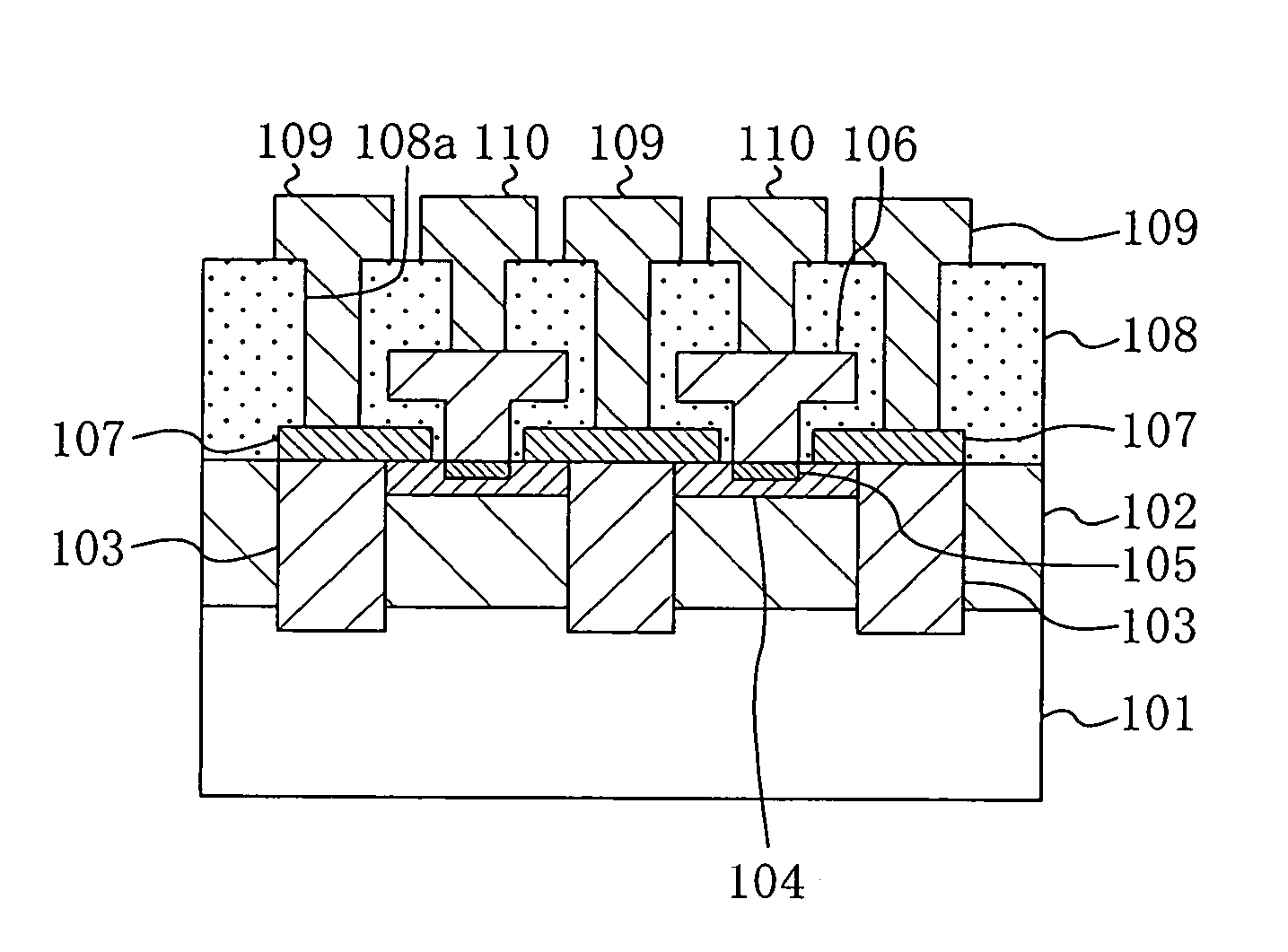

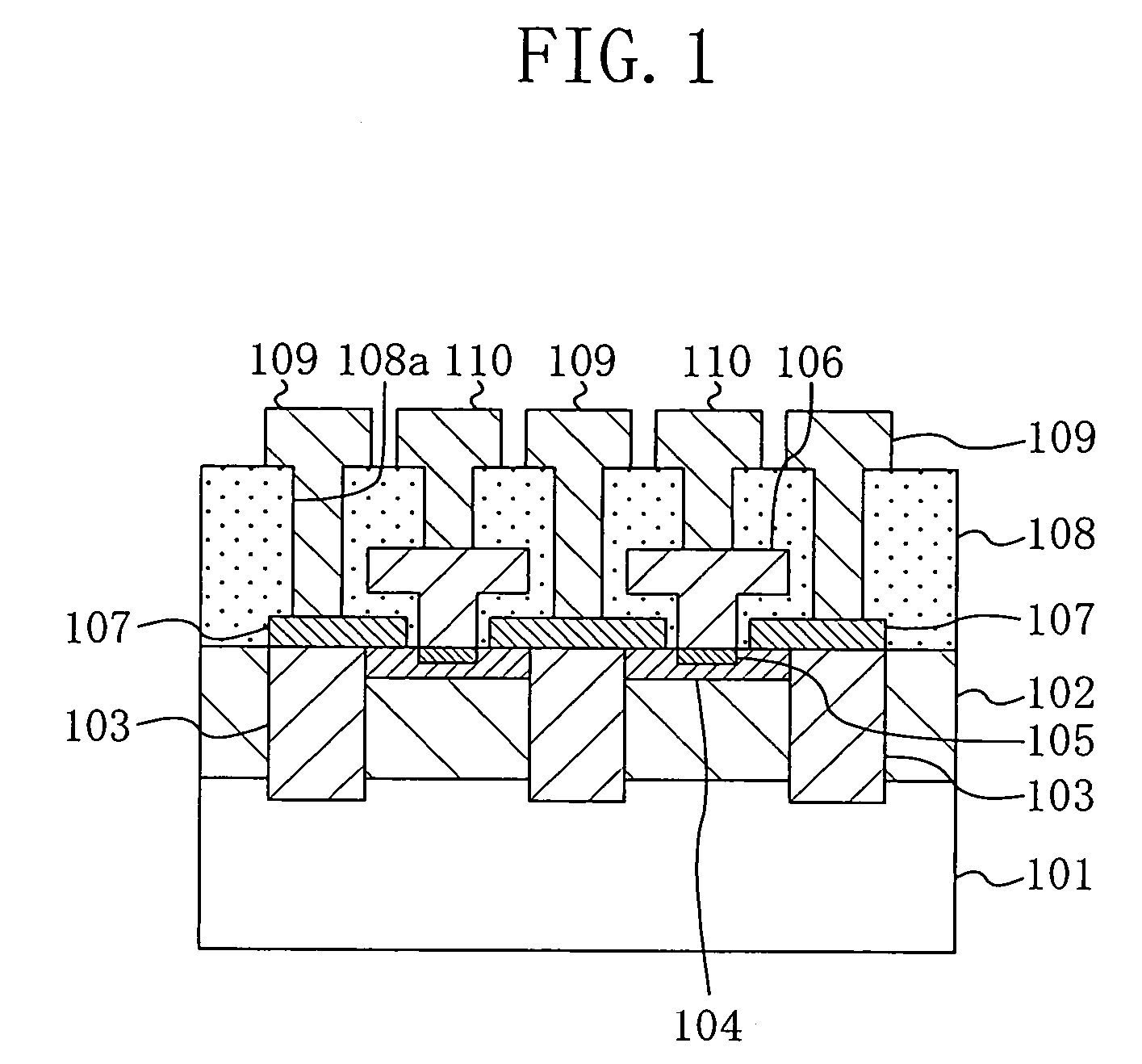

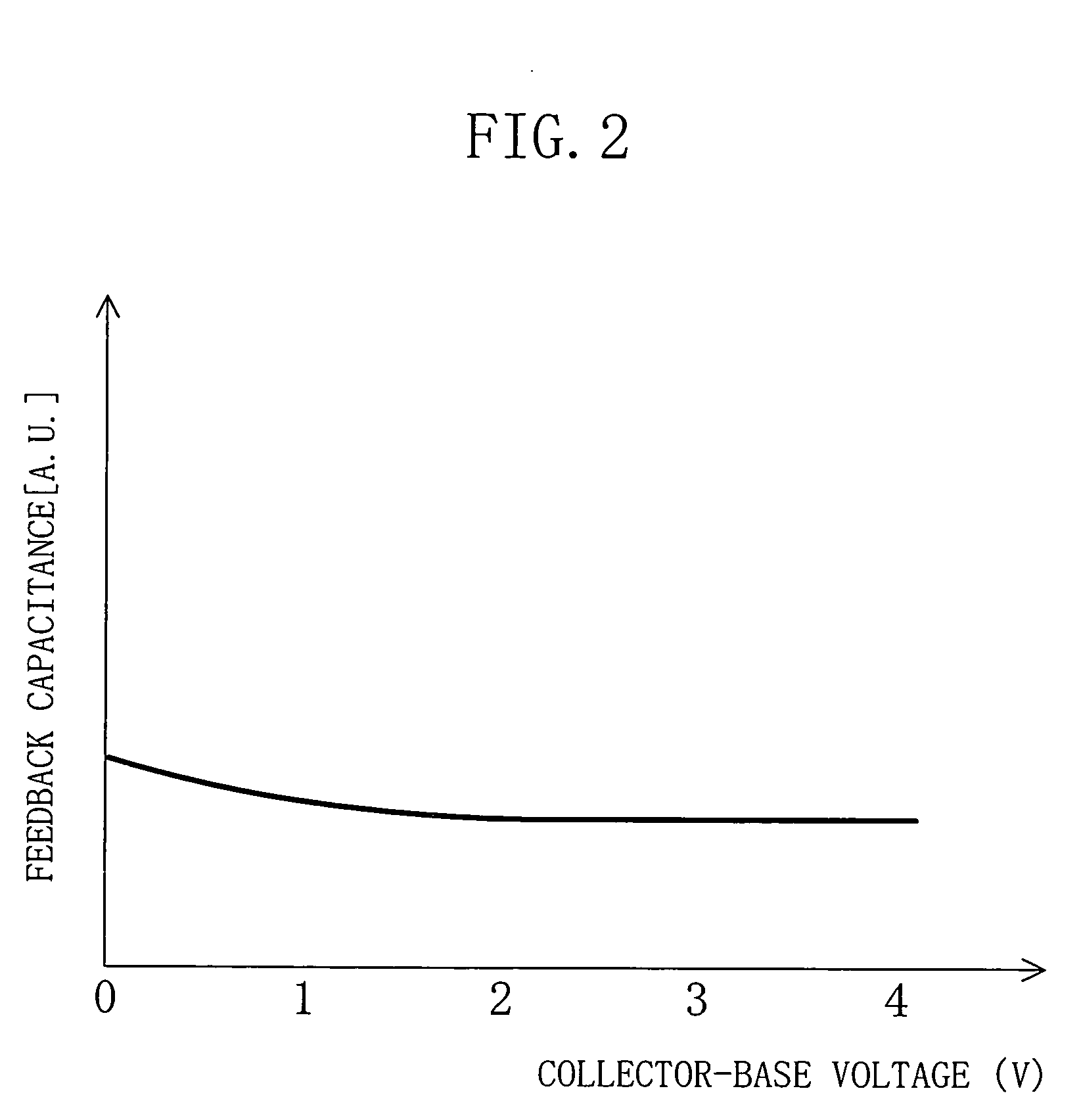

ActiveUS20050067672A1Avoid volatilityChange widthTransistorSemiconductor/solid-state device detailsHigh resistanceDevice material

A semiconductor device includes a semiconductor substrate of a first conductive type, a collector layer formed on the semiconductor substrate and made of a first semiconductor being of the first conductive type and having a higher resistance than that of the semiconductor substrate, an intrinsic base region having a junction surface with the collector layer and made of a second semiconductor of a second conductive type, and an emitter region having a junction surface with the intrinsic base region and made of a third semiconductor of the first conductive type. A periphery of the intrinsic base region is surrounded by an insulating region extending from the collector layer to the semiconductor substrate.

Owner:PANNOVA SEMIC

Epitaxial substrate and method for manufacturing epitaxial substrate

InactiveUS8648351B2Improved breakdown voltage characteristicsImprove breakdown voltageTransistorPolycrystalline material growthCrack freeSingle crystal

Provided is a crack-free epitaxial substrate having excellent breakdown voltage properties in which a silicon substrate is used as a base substrate thereof. The epitaxial substrate includes: a (111) single crystal Si substrate and a buffer layer including a plurality of composition modulation layers each formed of a first composition layer made of AlN and a second composition layer made of AlxGa1-xN (0≦x<1) being alternately laminated. The relationship of x(1)≧x(2)≧ . . . ≧x(n−1)≧x(n) and x(1)>x(n) is satisfied, where n represents the number of laminations of each of the first and the second composition layer, and x(i) represents the value of x in i-th one of the second composition layers as counted from the base substrate side. Each of the second composition layers is formed so as to be in a coherent state relative to the first composition layer.

Owner:NGK INSULATORS LTD

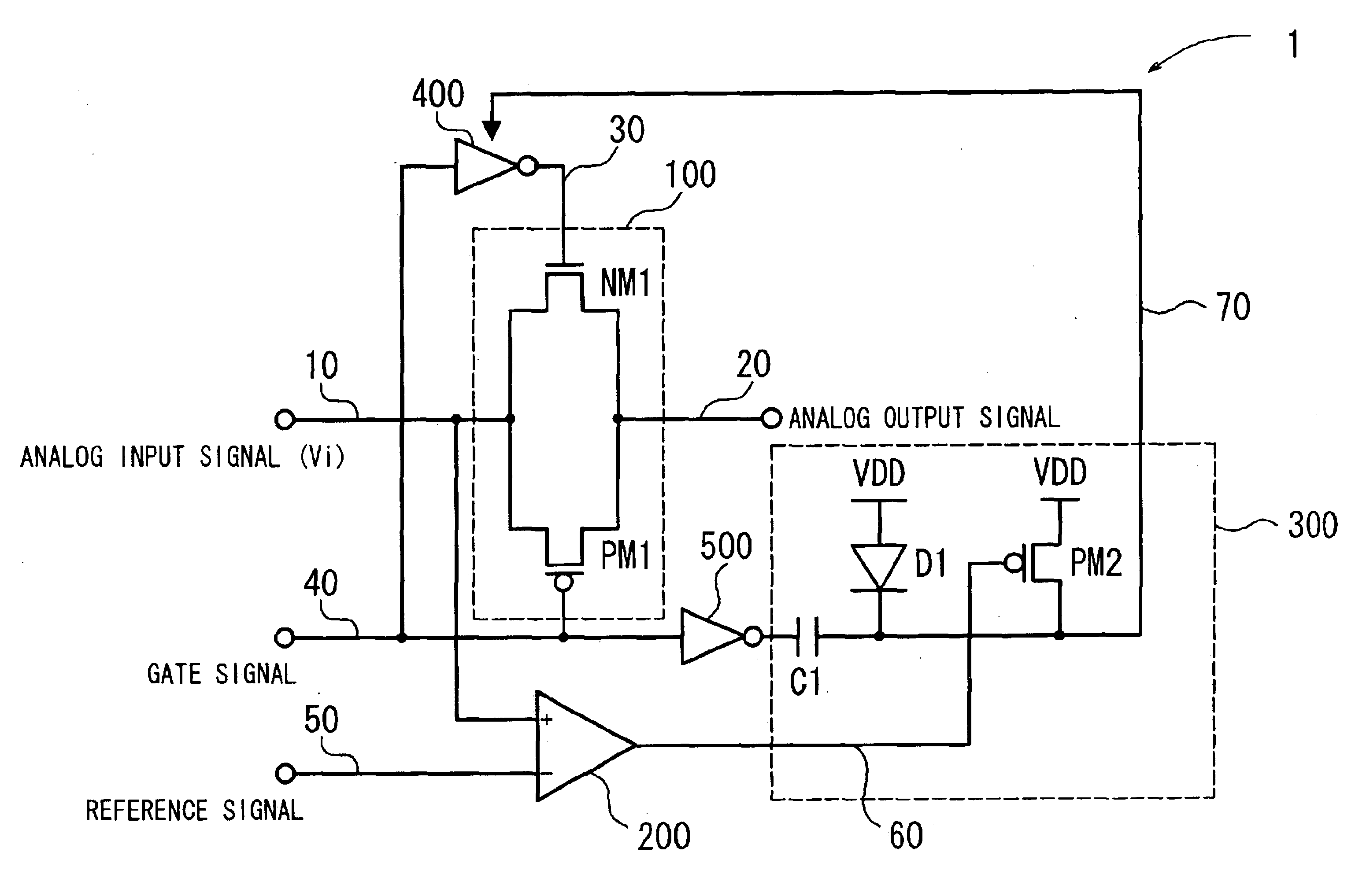

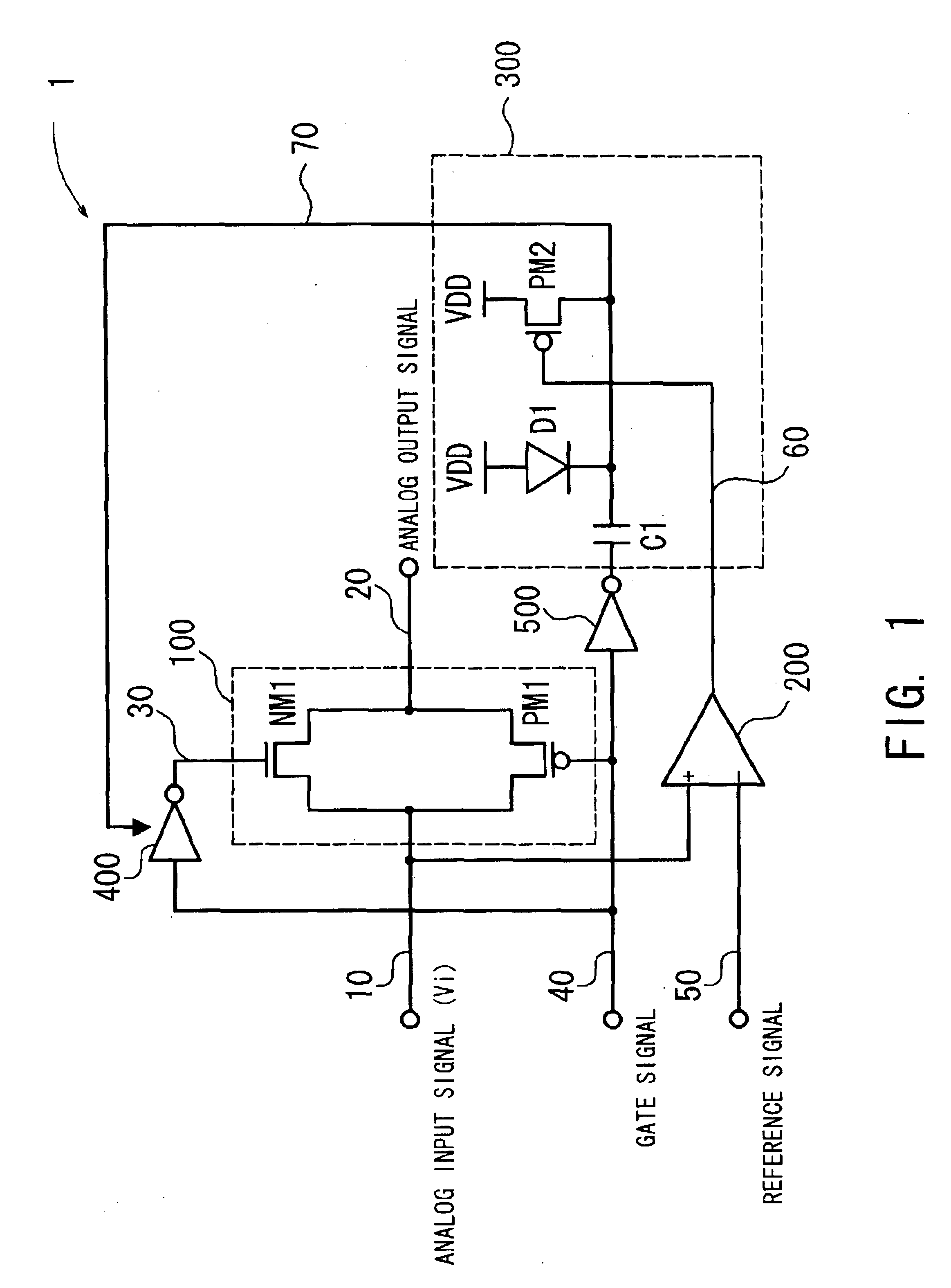

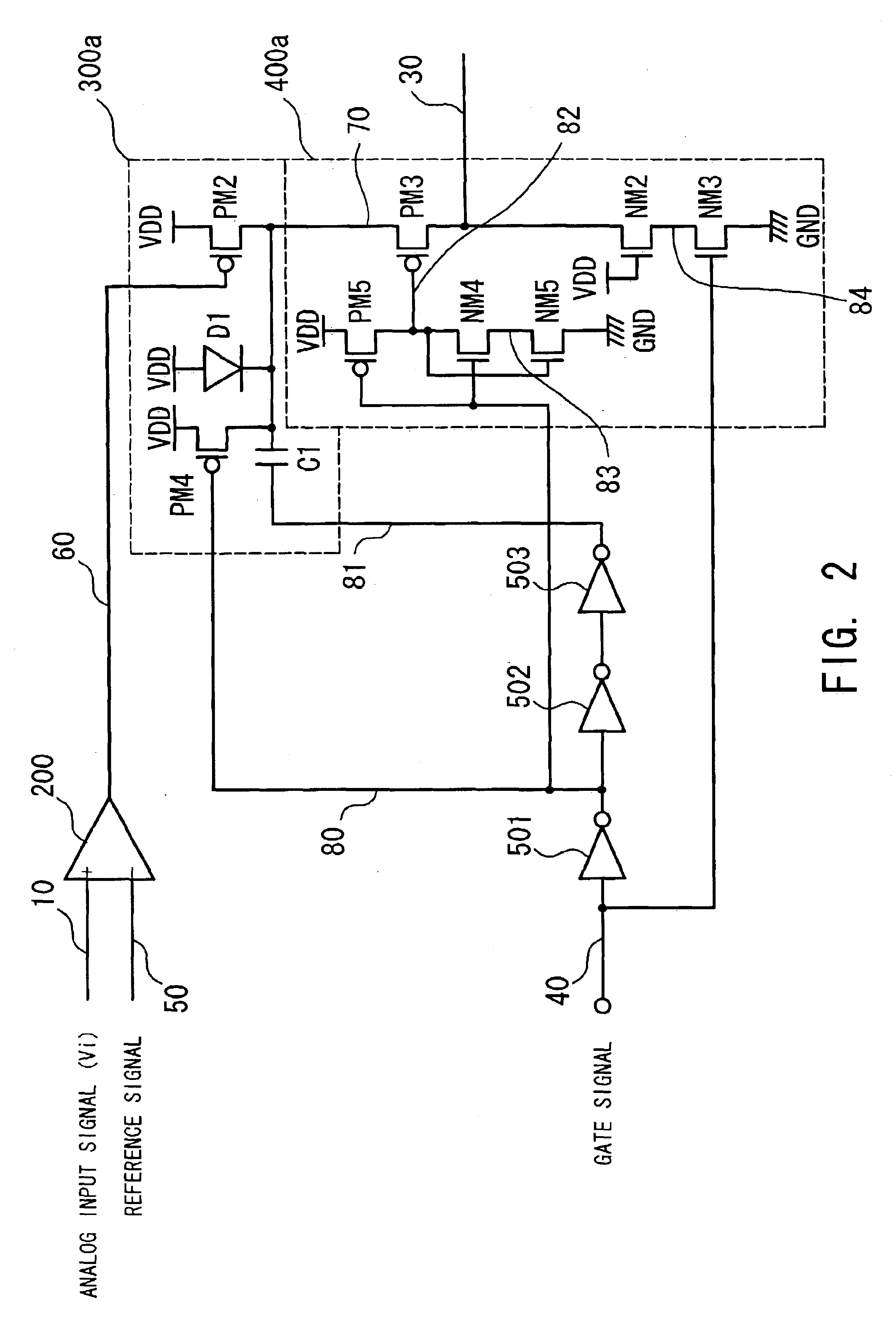

Analog switch circuit

InactiveUS6842063B2Raise the potentialImproved breakdown voltage characteristicsTransistorApparatus without intermediate ac conversionComparators circuitsAnalog signal

An analog switch circuit with superior breakdown voltage characteristics that can operate at a high speed at a low power supply voltage. The analog switch circuit includes a comparator circuit for inputting and comparing an analog input signal input to an analog switch section and a reference signal. If the input potential of the analog input signal is lower than the reference potential of the reference signal, a voltage boost circuit sets a potential of a gate of an n MOS transistor included in the analog switch section to a potential of positive power supply voltage. If the input potential of the analog input signal is higher than the reference potential of the reference signal, the voltage boost circuit boosts the potential of the gate to a potential higher than the potential of power supply voltage.

Owner:CYPRESS SEMICON CORP

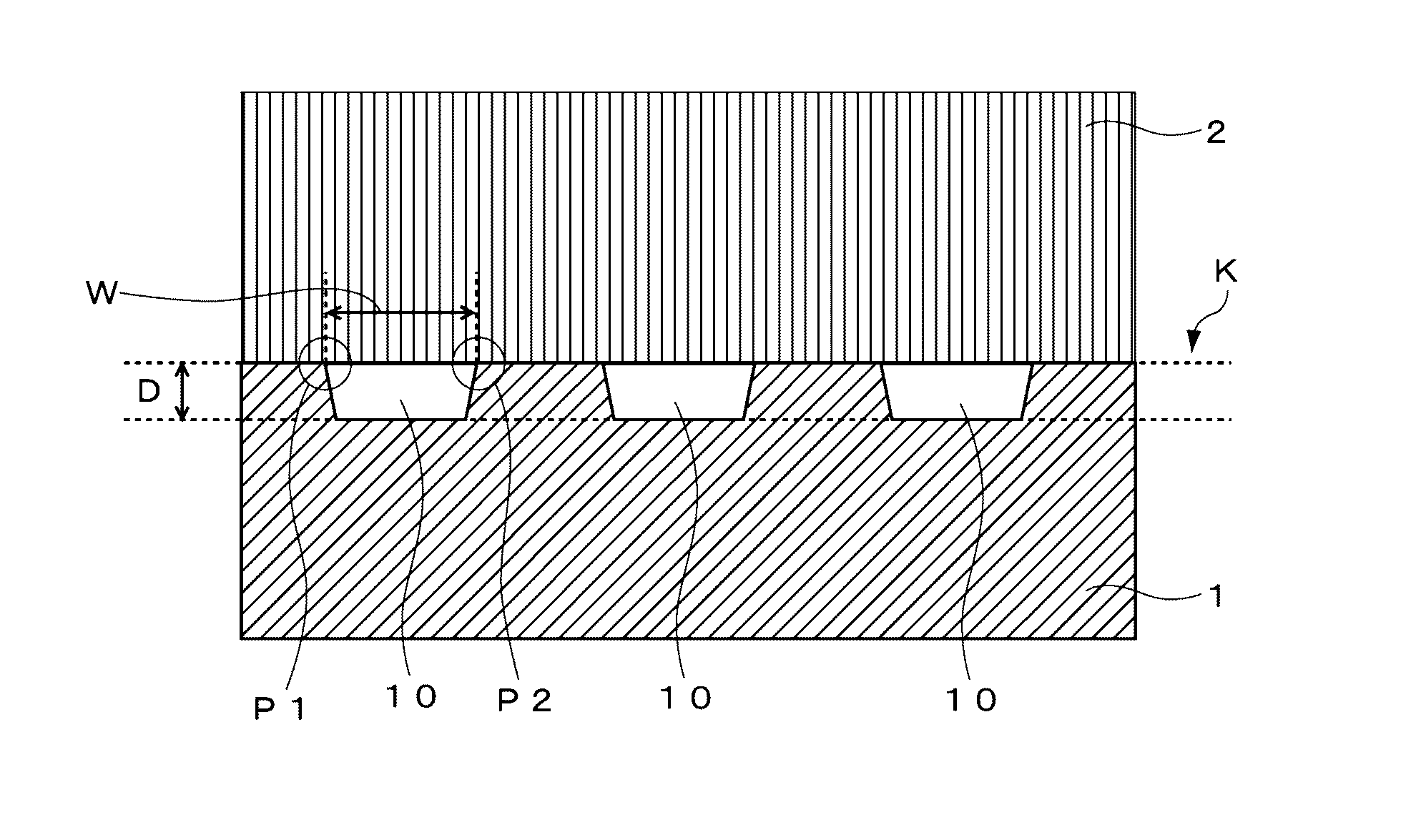

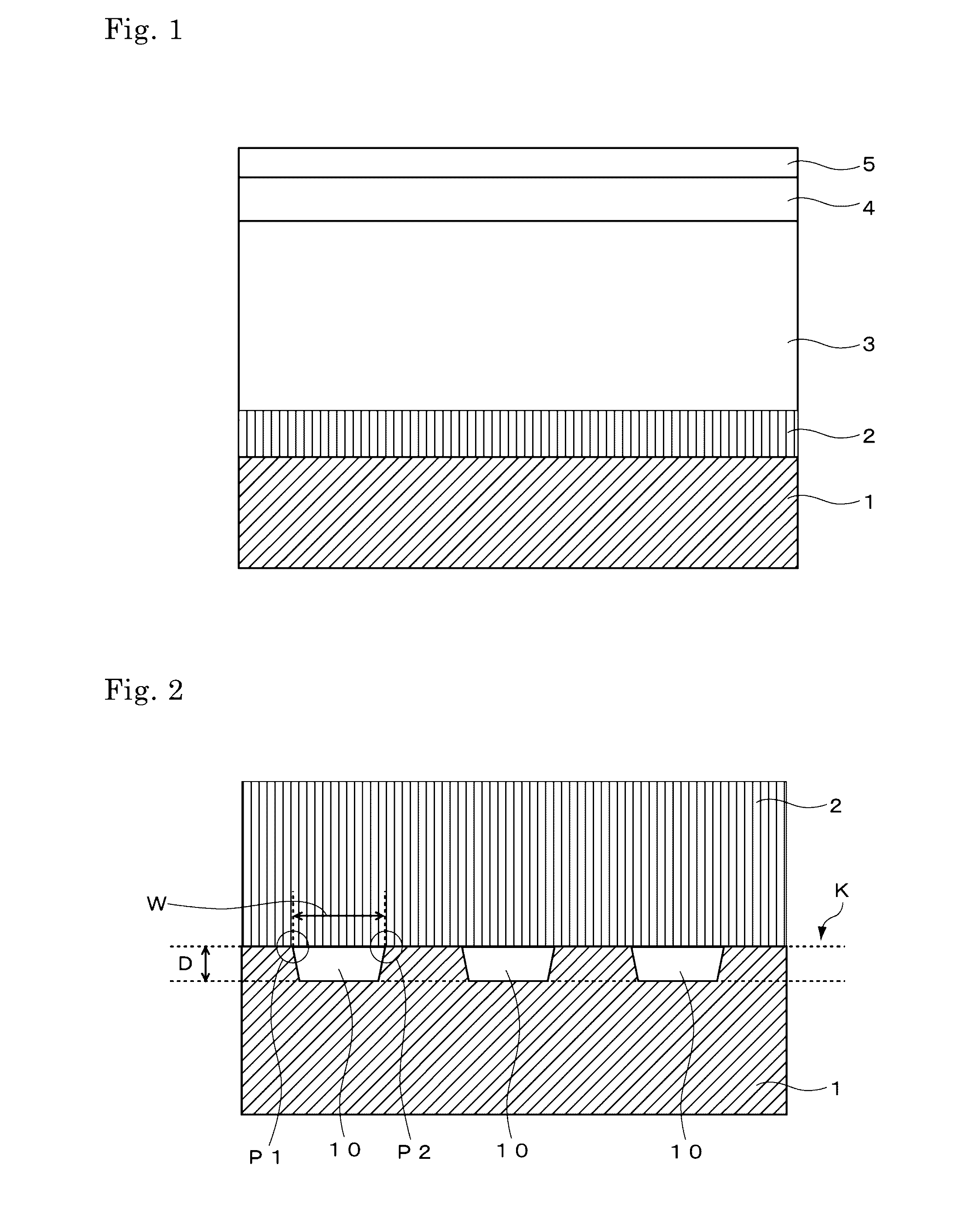

Nitride semiconductor substrate

ActiveUS20170011919A1Improved breakdown voltage characteristicsSimple structureSemiconductor/solid-state device manufacturingSemiconductor devicesPrincipal planeNitride semiconductors

The present invention provides a nitride semiconductor substrate having an initial nitride and a nitride semiconductor sequentially stacked on one principal plane of a base substrate, wherein the nitride semiconductor substrate comprises recesses depressed from an interface between the base substrate and the initial nitride toward the base substrate along one arbitrary cross section; the recesses each have a diameter of 6 nm or more and 60 nm or less and are formed at a density of 3×108 pieces / cm2 or more and 1×1011 pieces / cm2 or less; and the recess preferably has a depth of 3 nm or more and 45 nm or less from the interface between the base substrate and the initial nitride toward the base substrate.

Owner:COORSTEK INC

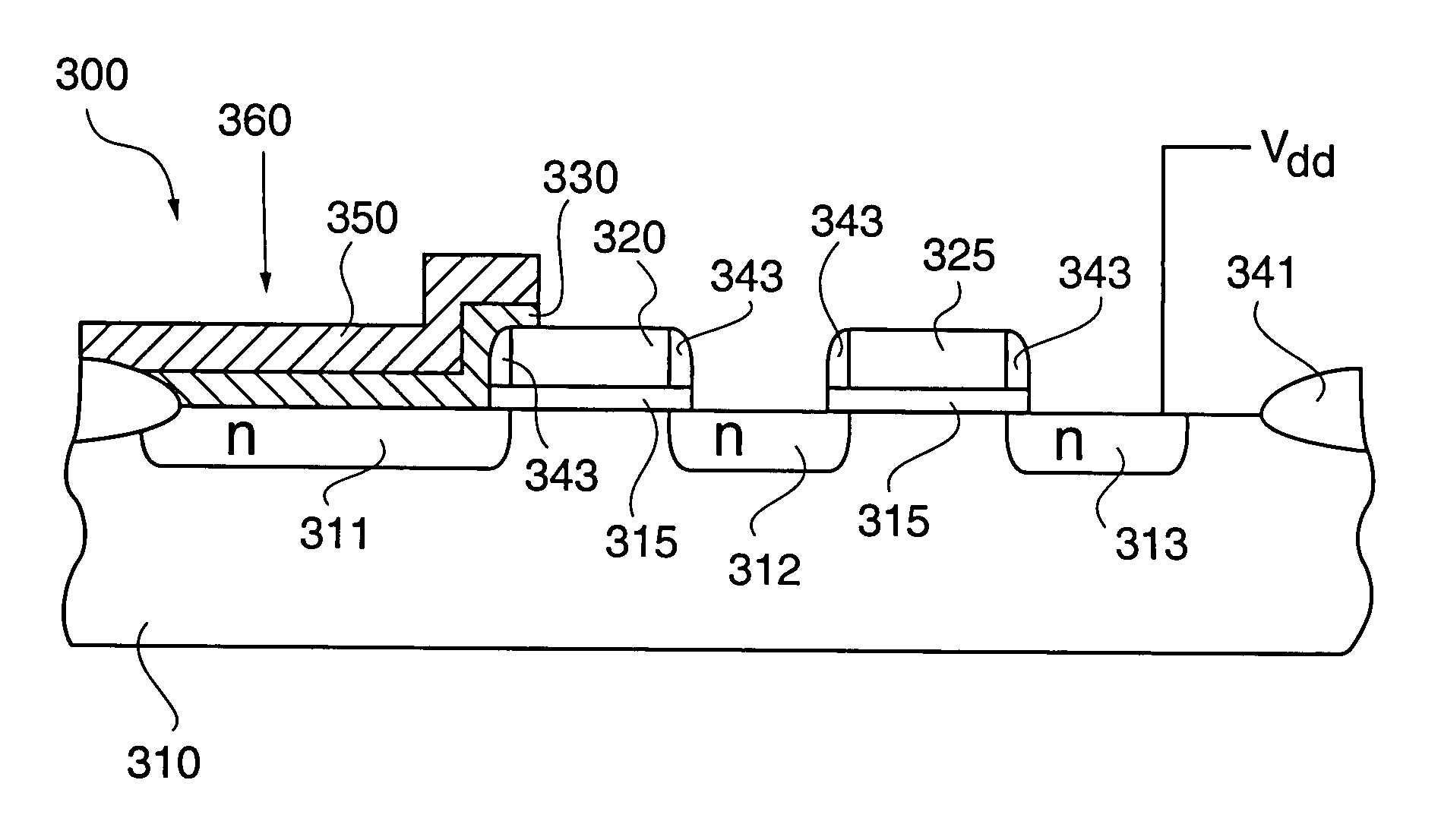

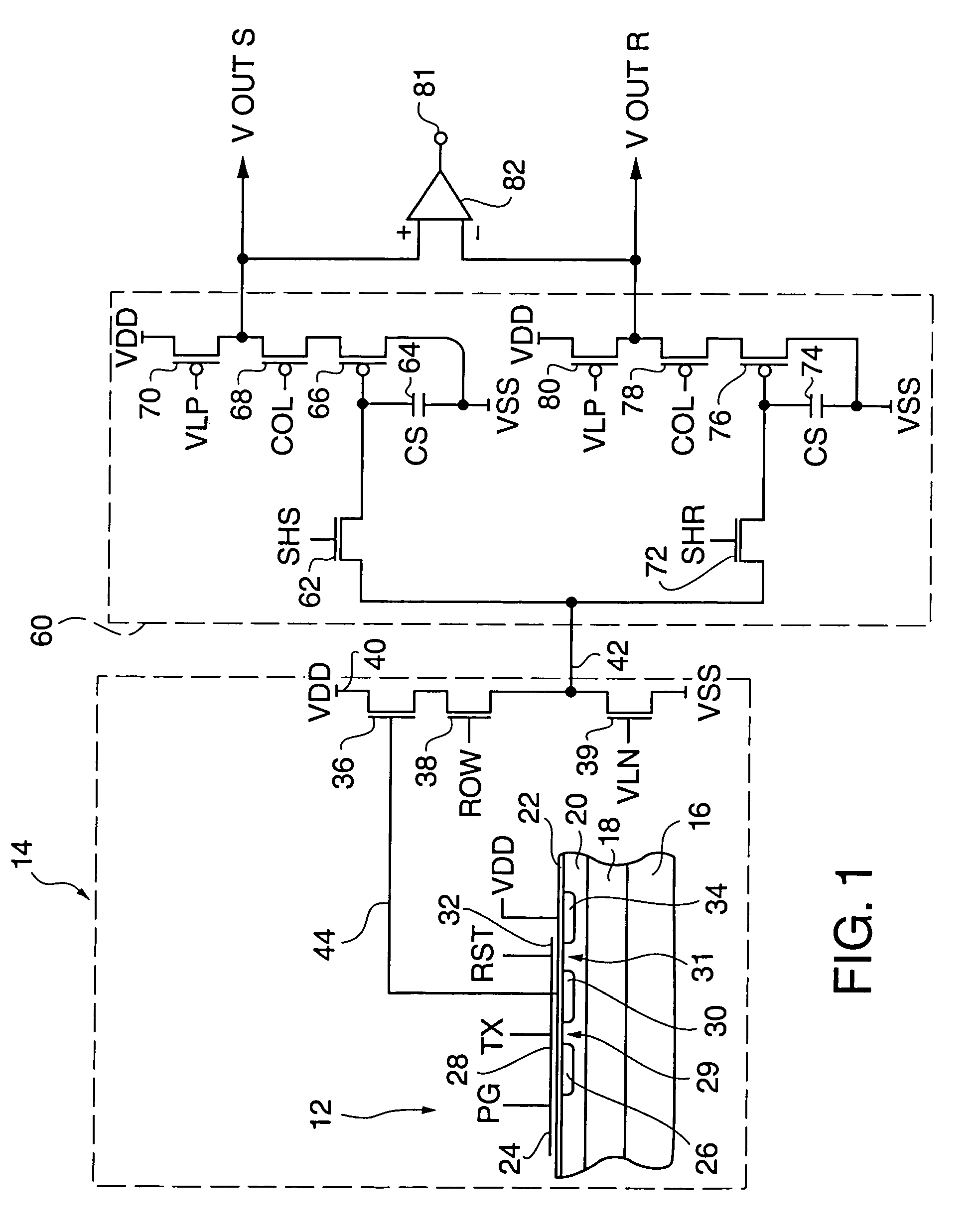

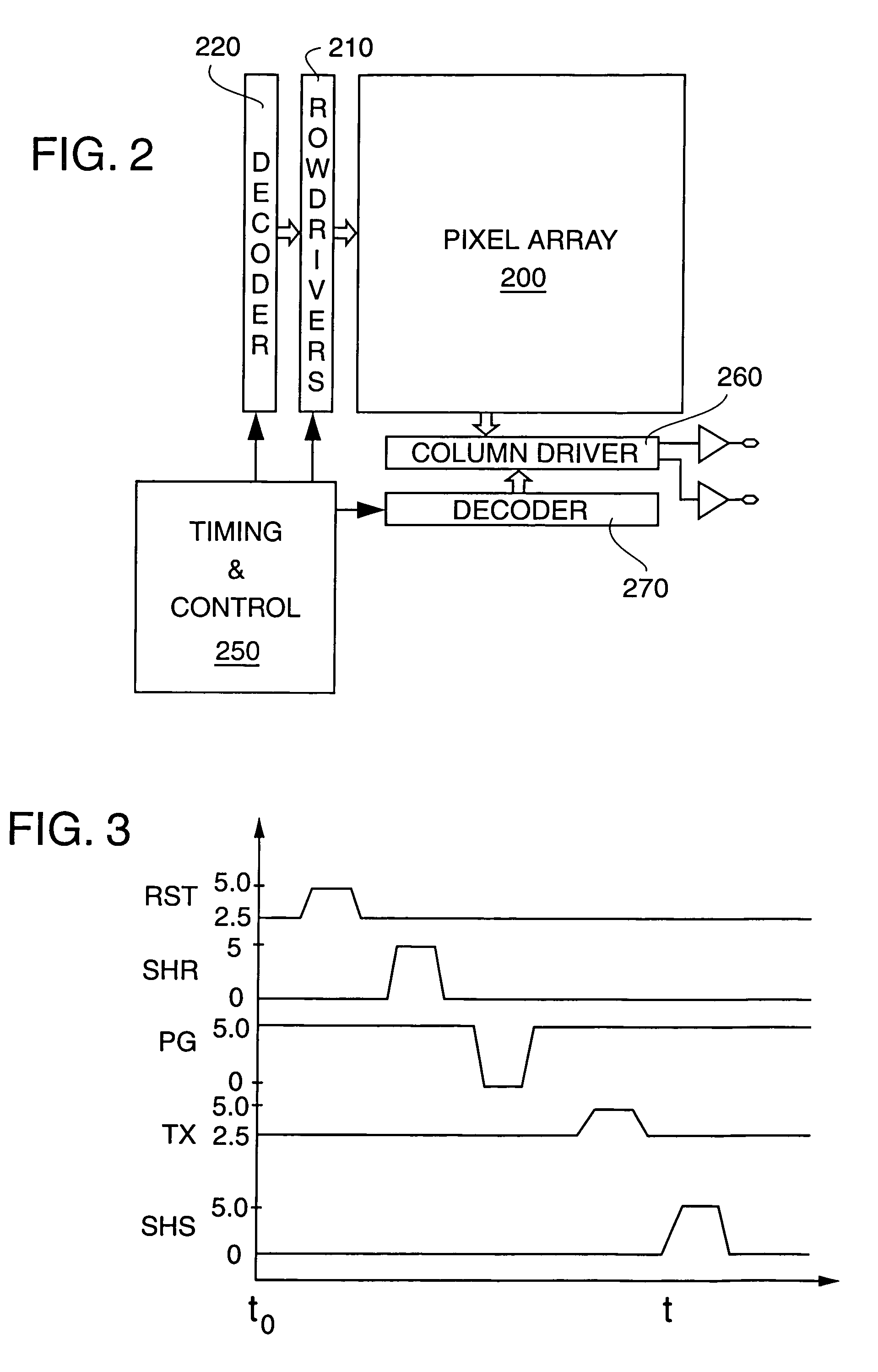

CMOS imager having a nitride dielectric

InactiveUS7791116B1Increase capacitanceImproved breakdown voltage characteristicsSolid-state devicesDiodeCapacitanceGrating

An imaging device formed as a CMOS semiconductor integrated circuit includes a nitrogen containing insulating material beneath a photogate. The nitrogen containing insulating material, preferably be one of a silicon nitride layer, an ONO layer, a nitrode / oxide layer and an oxide / nitrode layer. The nitrogen containing insulating layer provides an increased capacitance in the photogate region, higher breakdown voltage, a wider dynamic range and an improved signal to noise ratio. The invention also provides a method for fabricating a CMOS imager containing the nitrogen containing insulating layer.

Owner:MICRON TECH INC

Method for etching semiconductor structure and method for forming metal interconnection layer

InactiveCN101640174ADoes not affect line widthAvoid rough edgesSemiconductor/solid-state device manufacturingMetal interconnectSemiconductor structure

The invention provides a method for etching a semiconductor structure and a method for forming a metal interconnection layer. The method for etching the semiconductor structure comprises the steps of:providing a semiconductor substrate, wherein the substrate is provided with a patterned photoresist layer; taking the photoresist layer as a mask to perform plasma etching on the substrate, wherein aplasma etching process at least adopts three fluorocarbon compounds as etching gas; and removing the photoresist layer to form a semiconductor structure. The adoption of the method for etching the semiconductor structure can effectively improve the roughness of line edges of grooves formed by etching. The adoption of the method for forming the metal interconnection layer can effectively improve the roughness of the line edges of the grooves formed by etching, form the metal interconnection layer with straight line edges, and further improve the breakdown voltage characteristics of semiconductor devices.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

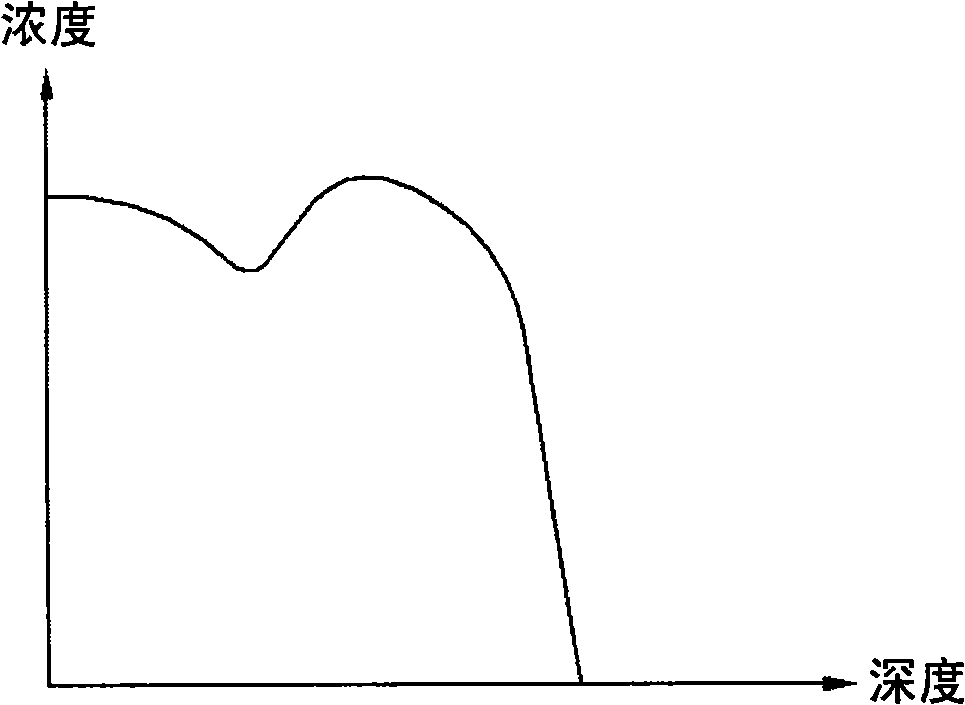

Semiconductor device and manufacturing method thereof

InactiveCN101335298AImproved breakdown voltage characteristicsPrevent impact ionizationTransistorSemiconductor/solid-state device manufacturingHigh voltage transistorsIonization

The invention discloses a semiconductor device that can be used as a high voltage transistor. The semiconductor device can include a gate electrode on a semiconductor substrate, drift regions in the substrate at opposite sides of the gate electrode, a source region in one of the drift regions and a drain region in the other of the drift regions, and a shallow trench isolation (STI) region in a portion of the drift region between the gate electrode and the drain region. The portion of the drift region below the STI region can have a doping profile in which the concentration of impurities decreases from the concentration at the lower surface of the STI region, and then increases, and then again decreases. The invention improves puncture voltage characteristic of the semiconductor device, and collision ionization in the semiconductor device can be avoided.

Owner:DONGBU HITEK CO LTD