Phase transformation memory and manufacturing method thereof

A manufacturing method and phase change technology, which are applied in the field of memory, can solve the problems of difficulty in controlling the thickness and doping concentration of N+ doped regions and N- doped regions, prone to breakdown, and difficult to shrink in size, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

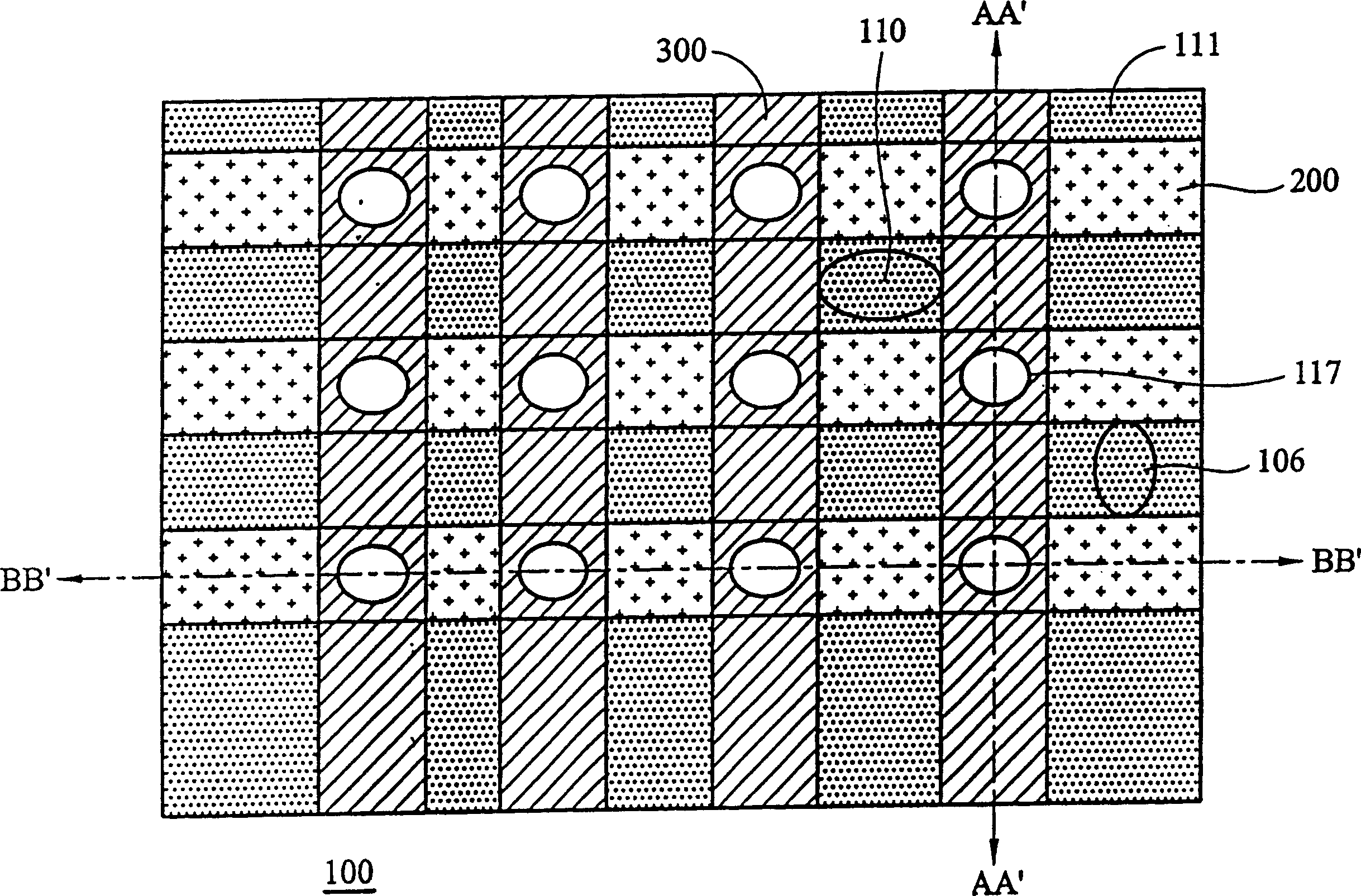

[0011] First, please refer to figure 2 , showing a top view of a phase change memory structure according to an embodiment of the present invention. The phase change memory structure includes a semiconductor substrate 100; an insulating layer 111 is formed on the semiconductor substrate 100, and the insulating layer 111 can be an oxide layer. The phase change memory structure includes a P+ doped region 117 , a word line 200 , a bit line 300 , a first shallow trench isolation structure 106 , and a second shallow trench isolation structure 110 .

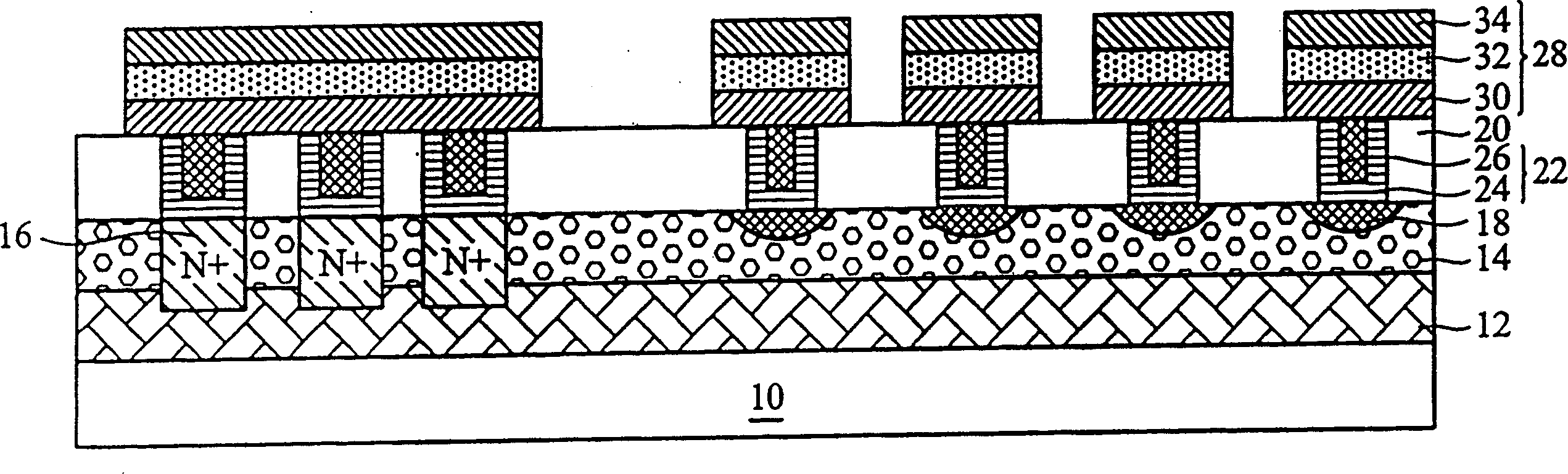

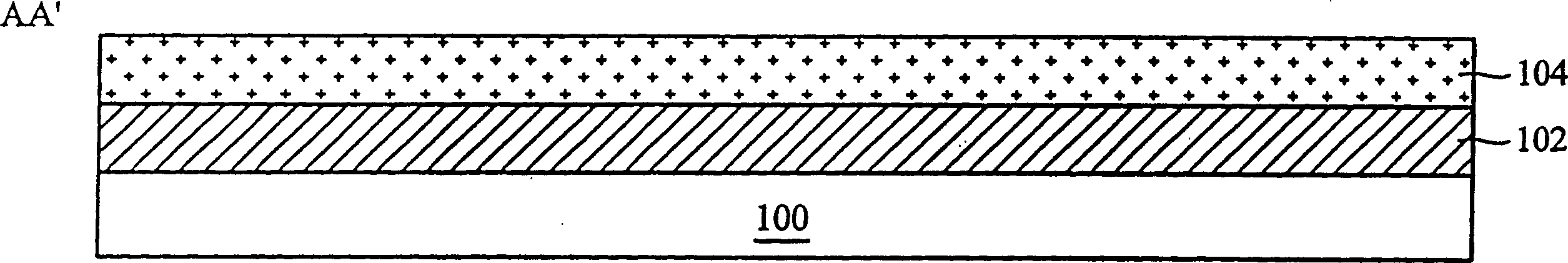

[0012] Figure 3 to Figure 4 show based on figure 2 The AA' profile, Figure 5 to Figure 8 show based on figure 2 The BB' profile. Please refer to image 3 , the embodiment of the present invention firstly provides a semiconductor substrate 100 , an N+ epitaxial layer 102 and an N− epitaxial layer 104 are successively formed on the semiconductor substrate 100 . The N+ epitaxy layer 102 and the N- epitaxy layer 104 can be forme...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More