Test method and system for testing internal eye diagram of chip

A technology of internal signals and test methods, applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., can solve problems such as errors and inaccurate test results, and achieve the effect of low cost of use, convenient parameter adjustment, and guaranteed consistency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments.

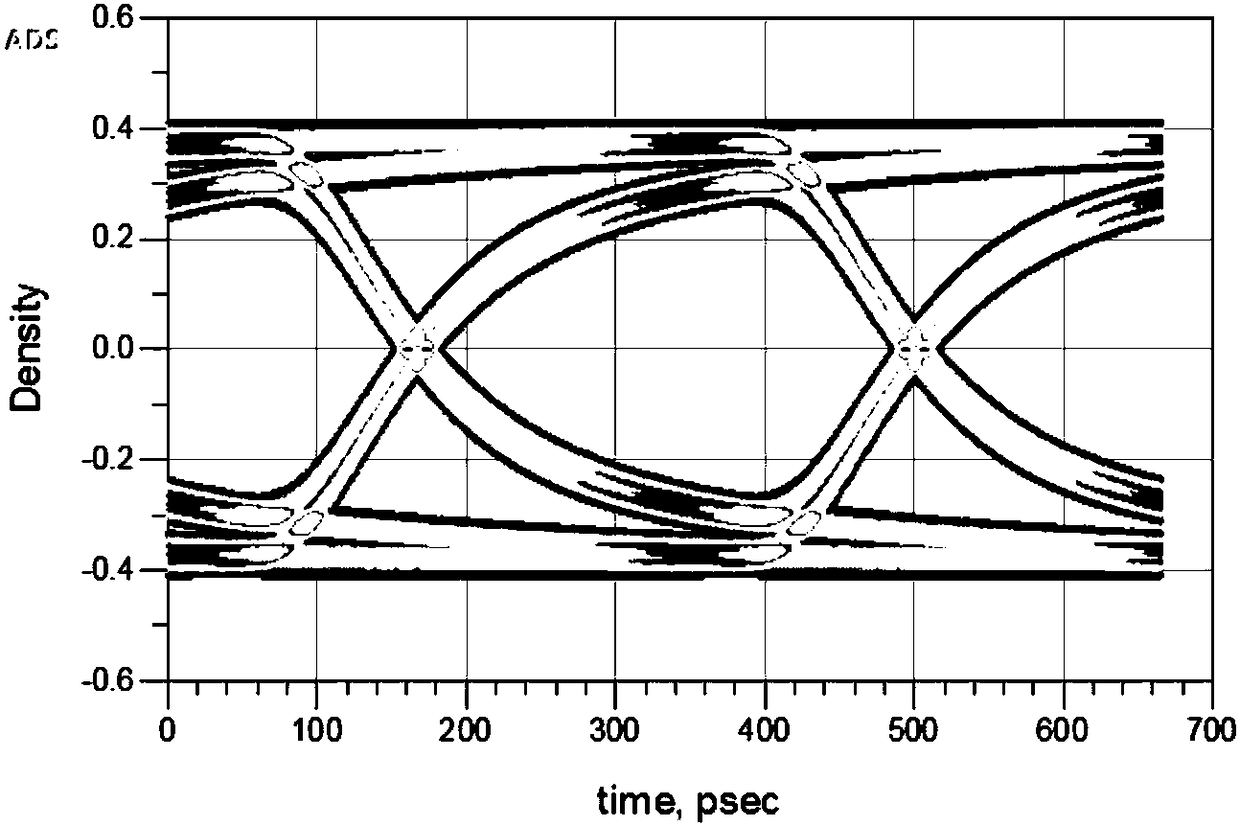

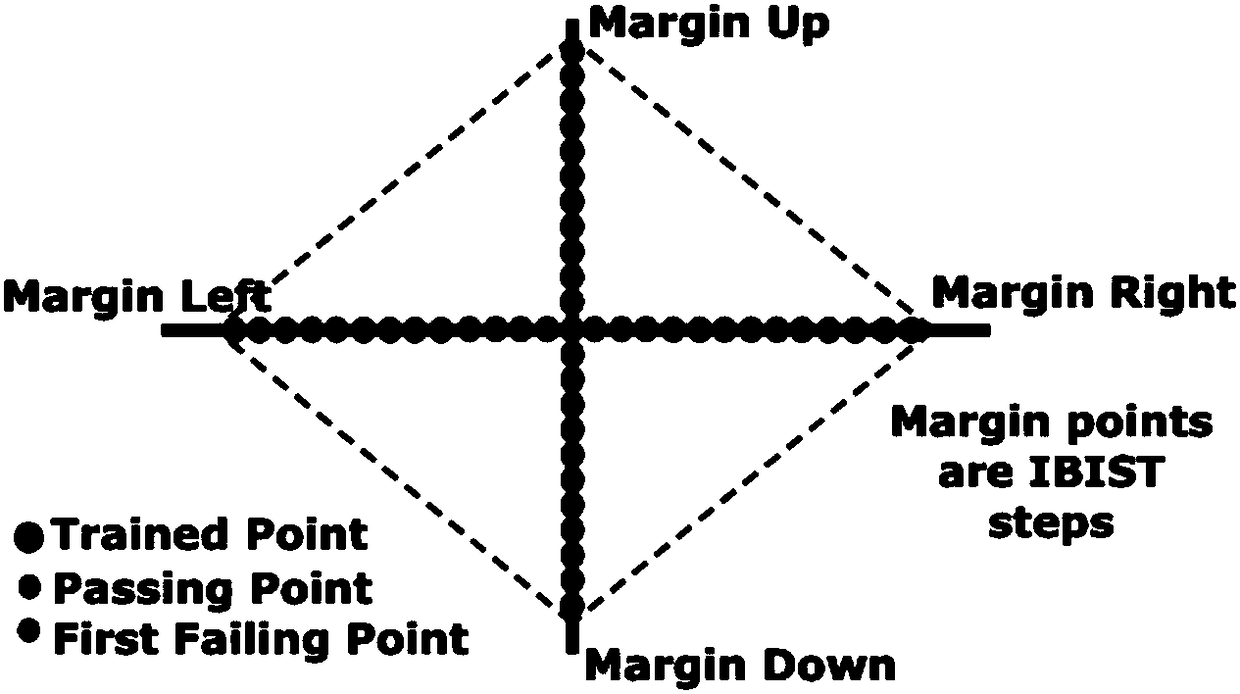

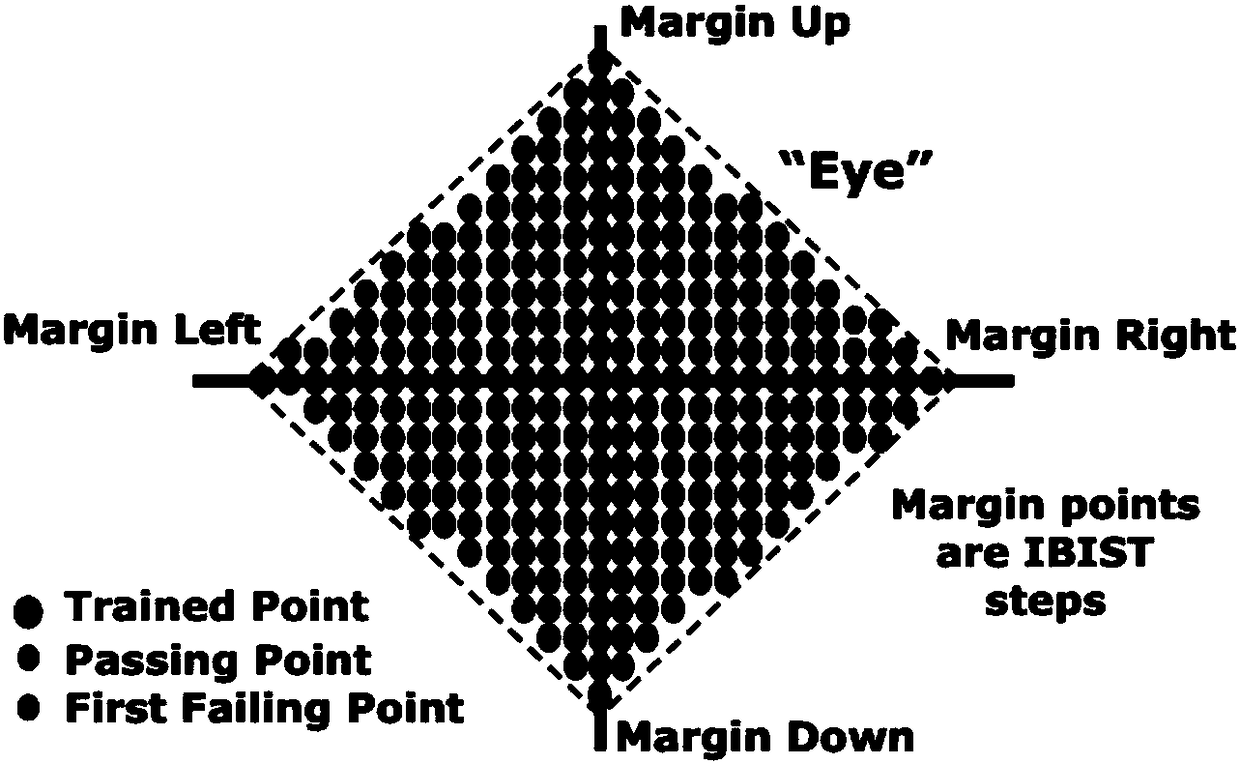

[0025] Such as Figure 1-Figure 3 As shown, this embodiment discloses a test method for testing the internal signal eye diagram of the chip, including the following steps:

[0026] S1. Lap the test platform, and input a reference voltage signal and a clock signal at the receiving end of the chip to be tested to obtain sampling points;

[0027] S2. Adjust the phase of the clock signal and the size of the reference voltage signal to change the position of the sampling point, and test the acquired sampling point to obtain a boundary sampling point whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More