Delay-locked loop with wide frequency input range

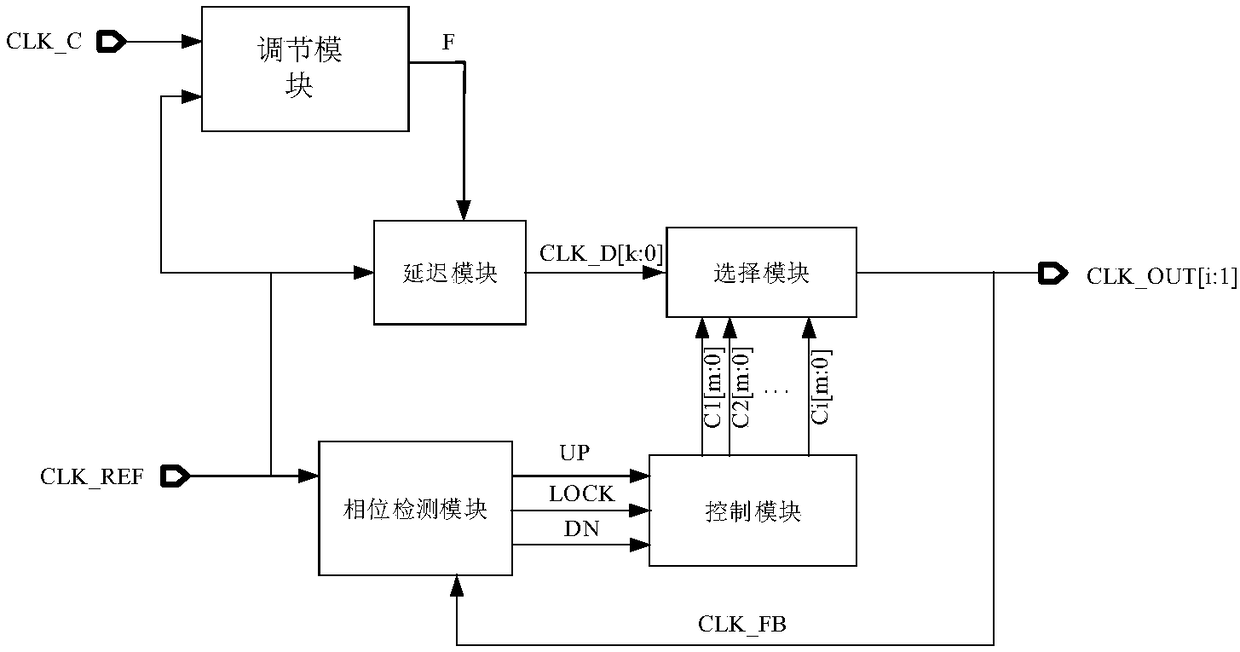

A delay-locked loop and input range technology, applied in the field of delay-locked loops, can solve the problems of poor reusability of DLL and limited operating frequency range of DLL, and achieve the effect of improving the operating frequency range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

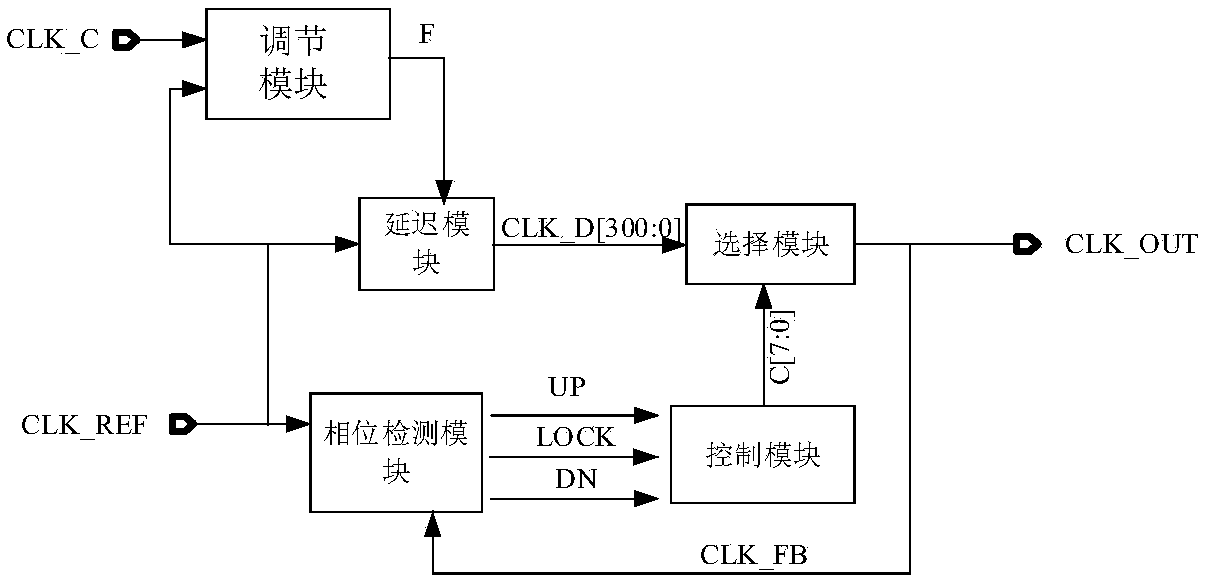

[0026] image 3 gives a based on figure 1 Schematic diagram of a 4-phase delay-locked loop structure with i=1, k=300, and m=7, in which the trigger edges of all modules are rising edges, and m+1 represents the number of bits in binary representation corresponding to Ci.

[0027] The final clock locked by the delay-locked loop is CLK_OUT, the control word corresponding to this clock is C[7:0] in turn, and CLK_OUT is the feedback clock CLK_FB.

[0028] The input and output of the selection module always maintain the following relationship:

[0029] CLK_OUT_OUT=CLK_D[a], a=C[7:0]; and a∈[0,300].

[0030] Among them, CLK_C is the counting clock, CLK_REF is the reference clock, the cycle of CLK_C is recorded as Tc, the cycle of CLK_REF is recorded as Tr, and the clock satisfies Tc

[0031]When the delay phase-locked loop works normally and the frequency of CLK_REF remains unchan...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap