Processor chip simulator and power failure test method

A processor and emulator technology, applied in electrical digital data processing, software testing/debugging, instruments, etc., can solve the problems of power-off of the simulated chip, inability to view and export the chip status, and destroy the chip status, so as to improve the development Efficiency, convenient development and debugging, and the effect of ensuring the authenticity of simulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

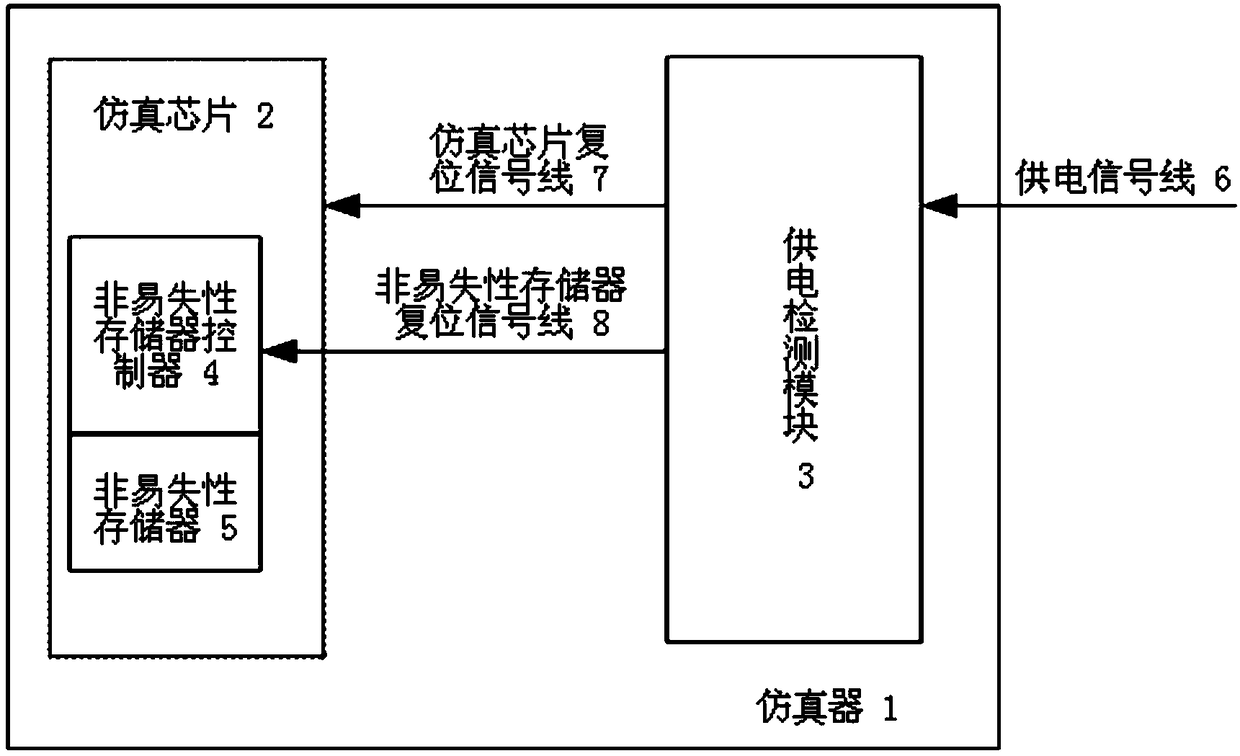

[0014] Such as figure 1 As shown, the processor chip emulator 1 includes, in the following embodiments: a power supply detection module 3 and an emulation chip 2 . There is a nonvolatile memory controller 4 and a nonvolatile memory memory 5 in the emulation chip 2, and the nonvolatile memory controller 4 and the nonvolatile memory 5 are jointly equivalent to realize the nonvolatile memory function and performance. The power supply detection module 3 receives and detects external power supply to the processor chip through the power supply signal line 6 . The power supply detection module 3 is connected with the simulation chip 2 through the simulation chip reset signal line 7, and is connected with the non-volatile memory controller 4 in the simulation chip 2 through the non-volatile memory reset signal line 8 .

[0015] The power supply detection module 3 monitors the external excitation environment in real time through the power supply signal line 6, and judges the externa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More