Storage component testing method and device

A technology of storage components and test methods, applied in static memory, instruments, etc., can solve problems such as single test method, inability to provide coverage, address traversal sequence, read and write operation sequence address space cannot be flexibly configured, etc. Simplify configuration steps and improve test coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

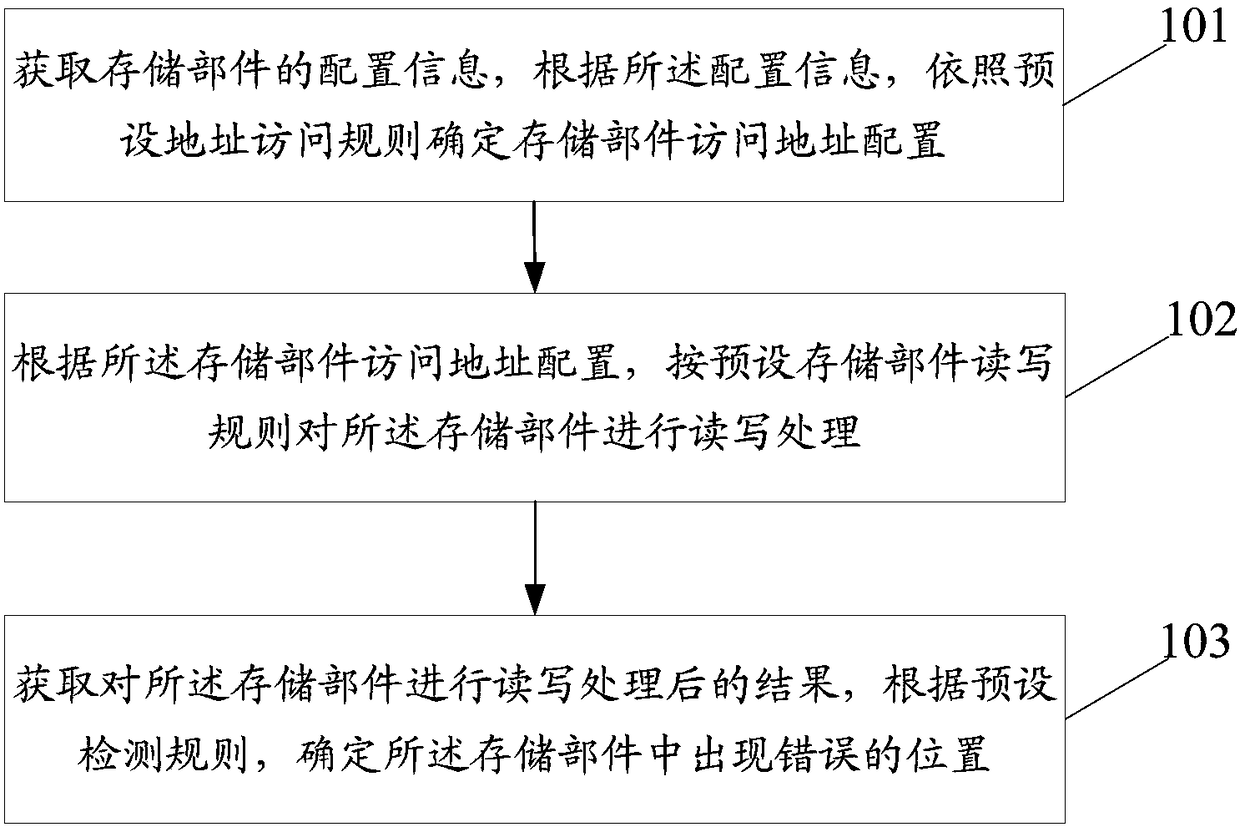

[0043] In the embodiment of the present invention, the configuration information of the storage component is acquired, and according to the configuration information, the storage component access address configuration is determined according to the preset address access rules; according to the storage component access address configuration, the storage component is read and written according to the preset storage component access address configuration The storage component performs read and write processing; obtains the result of the storage component after the read and write processing, and determines the location of the error in the storage component according to a preset detection rule.

[0044] The present invention will be described in further detail below in conjunction with the examples.

[0045] The storage component testing method provided by the embodiment of the present invention, such as figure 1 As shown, the method includes:

[0046] Step 101: Obtain the configu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More