A clock tree synthesis method and computer-readable storage medium

A clock tree synthesis and clock technology, used in computer-aided design, computing, instrumentation, etc., can solve problems such as timing violations, different lengths, clock delay deviations, etc., to improve accuracy, speed up, and shorten design cycles. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the purpose, technical solution and advantages of the present invention more clear, the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

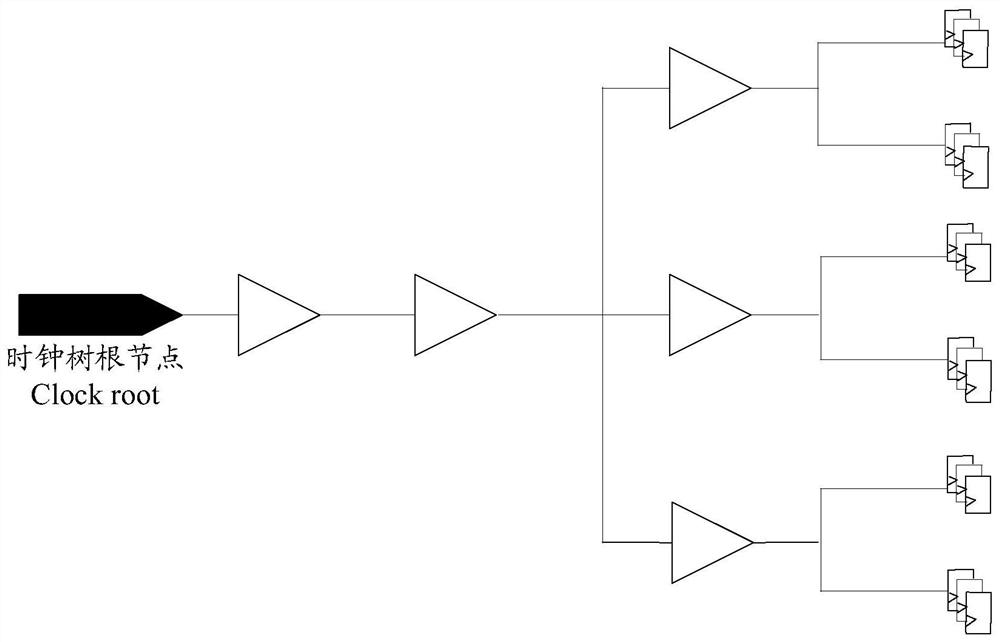

[0033] There are usually a large number of registers in a chip design, and the register is a sequential unit triggered by the clock edge, which cannot be separated from the clock signal. The clock signal must drive all the registers related to it, and the time when the clock signal arrives at the register is called clock latency (Clock Latency), such as figure 1 As shown in , an ideal clock tree balance is that the clock delay to each register is equally large.

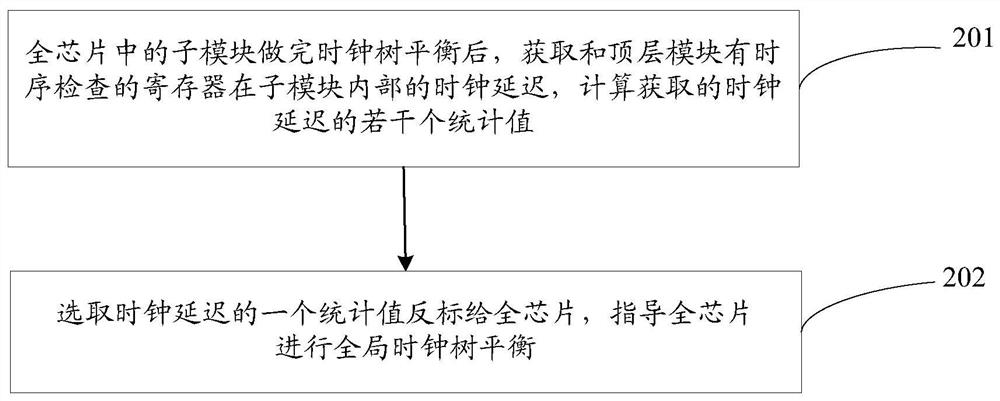

[0034] Such as figure 2 Shown, according to a kind of clock tree synthesis method of the present invention, com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More