A high-reliability SiC MOSFET device

A reliability and device technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of large leakage current in the blocking state, achieve good short-circuit capability, suppress excessive electric field, and avoid bipolar degradation problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

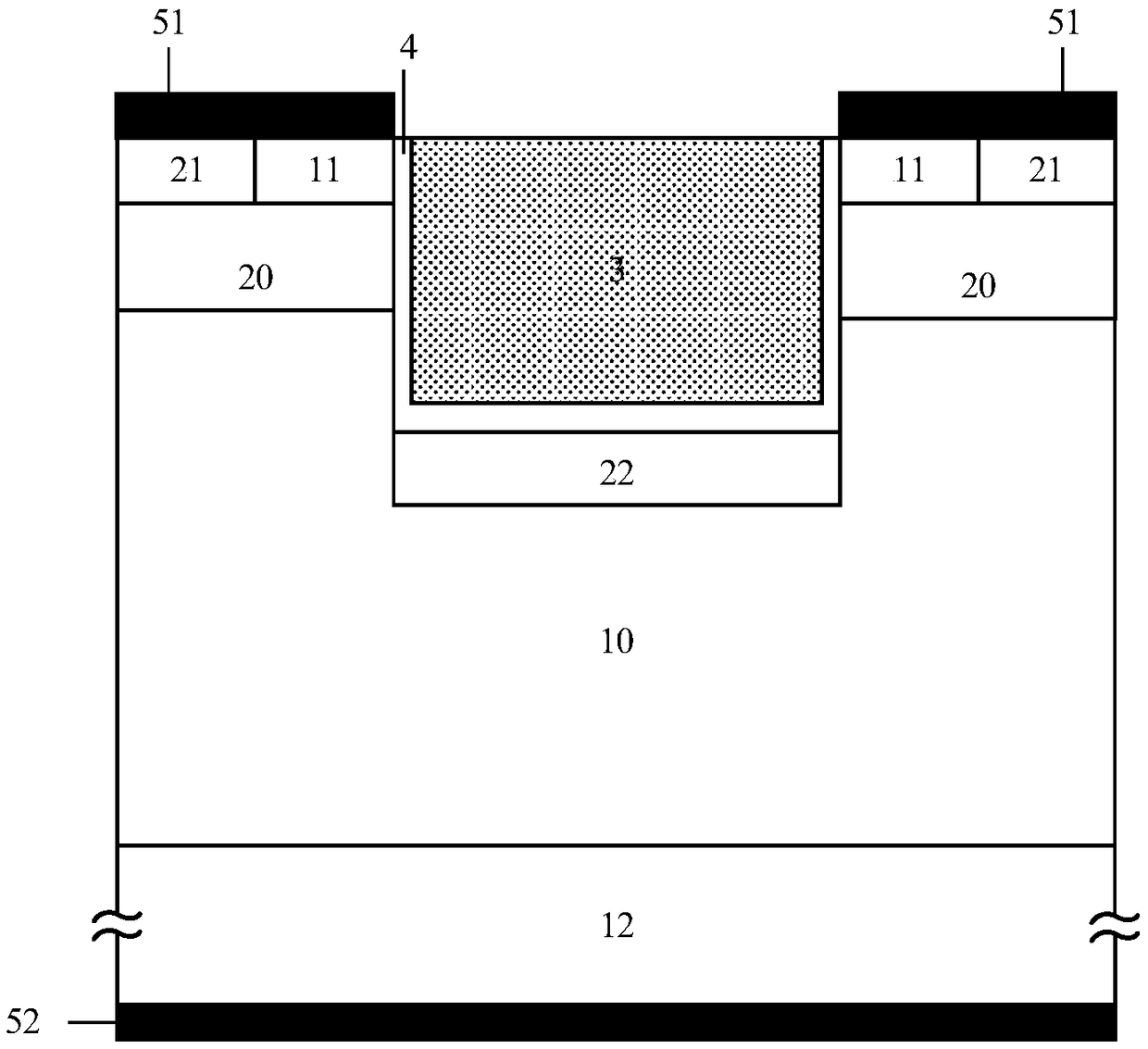

Embodiment 1

[0030] Such as figure 2 As shown, the high-reliability SiC MOSFET device of this embodiment includes: an N-type substrate 12, an N-type epitaxial layer 10 located above the N-type substrate 12, and a P-body region 20 located on the left above the N-type epitaxial layer 10 , the P+ contact region 21 and the N+ contact region 11 located above the P-body region 20, the oxide layer 4 and the gate 3 located on the right side of the P-body region 20, the Schottky contact electrode 53 located below the gate 3, and the The deep P-well region 22 on the right side above the N-type epitaxial layer 10, wherein the deep P-well region 22 tightly wraps the right side of the oxide layer 4, the right side of the Schottky contact electrode 53 and part of the lower side; the P+ contact region 21 and the N+ Contact region 11 forms source 51 through ohmic contact, deep P-well region 22 forms source 51 through ohmic contact, N-type substrate 12 under the device forms drain 52 through ohmic contact...

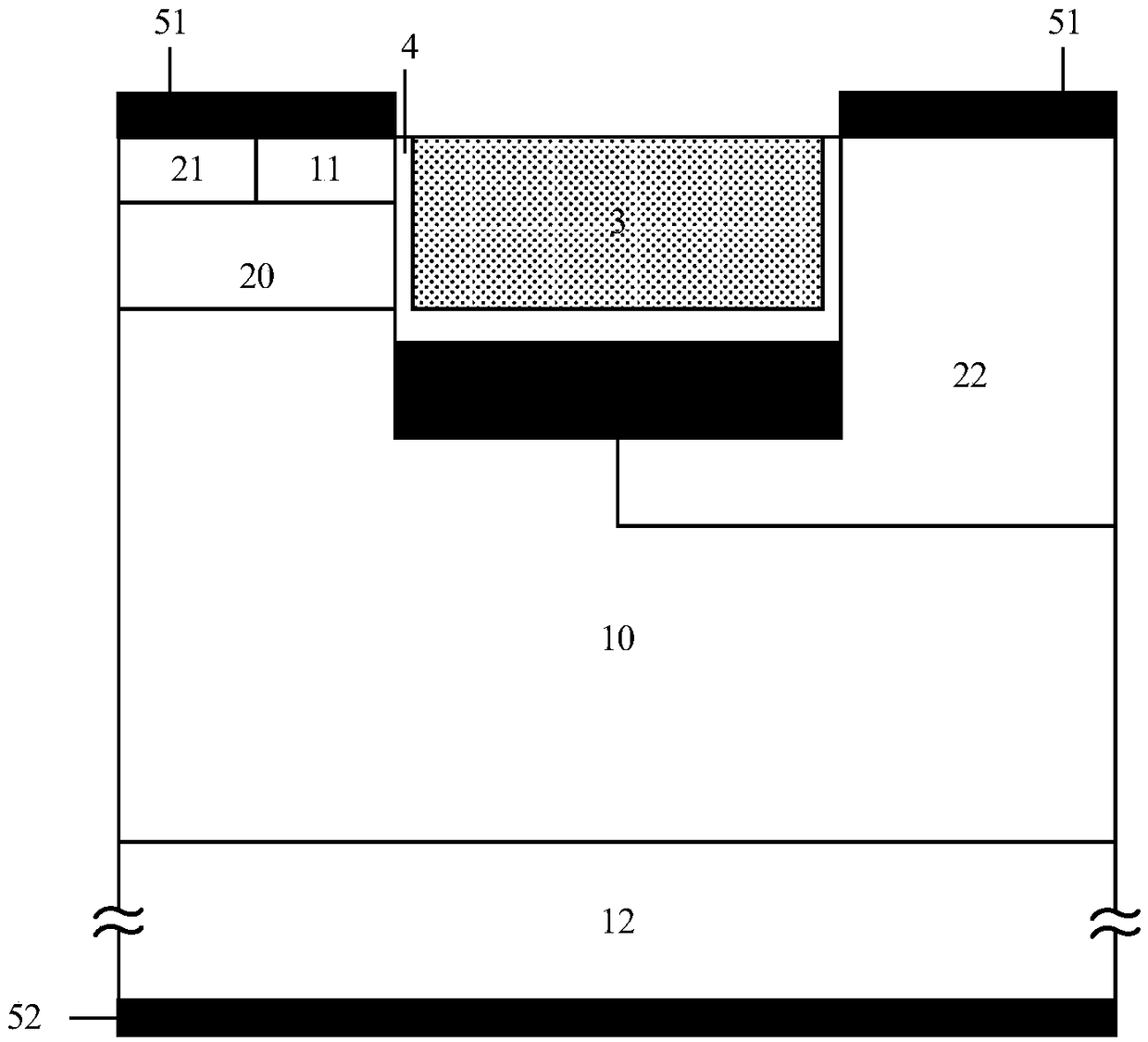

Embodiment 2

[0037] Such as image 3 As shown, the difference between the device structure of this embodiment and Embodiment 1 is that the gate 3 is split into two side gates, and the middle of the side gates is filled with an oxide layer 4 .

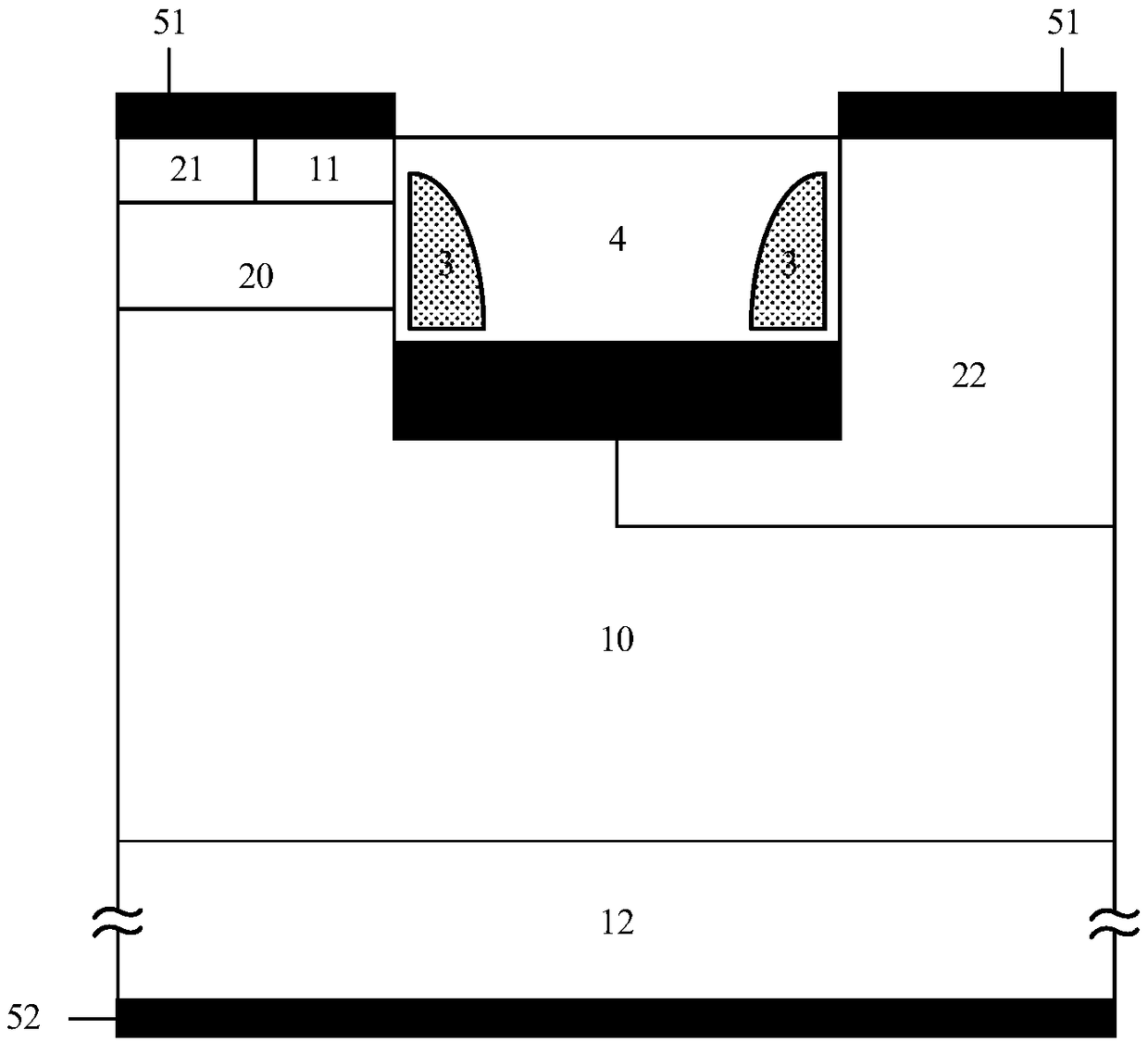

Embodiment 3

[0039] Such as Figure 4 As shown, the main difference between this embodiment and Embodiment 1 is that the gate 3 is split into two side gates, and the middle of the side gates is filled with a metal electrode, and at the same time, the source electrode 51 and the Schottky contact electrode 53 are connected to form the same area. This area is the metal electrode 54 . An oxide layer 4 is filled between the metal electrode 54 and the gate 3 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More