Array substrate and liquid crystal display panel

An array substrate, liquid crystal technology, applied in instruments, nonlinear optics, optics, etc., can solve problems such as affecting light transmittance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

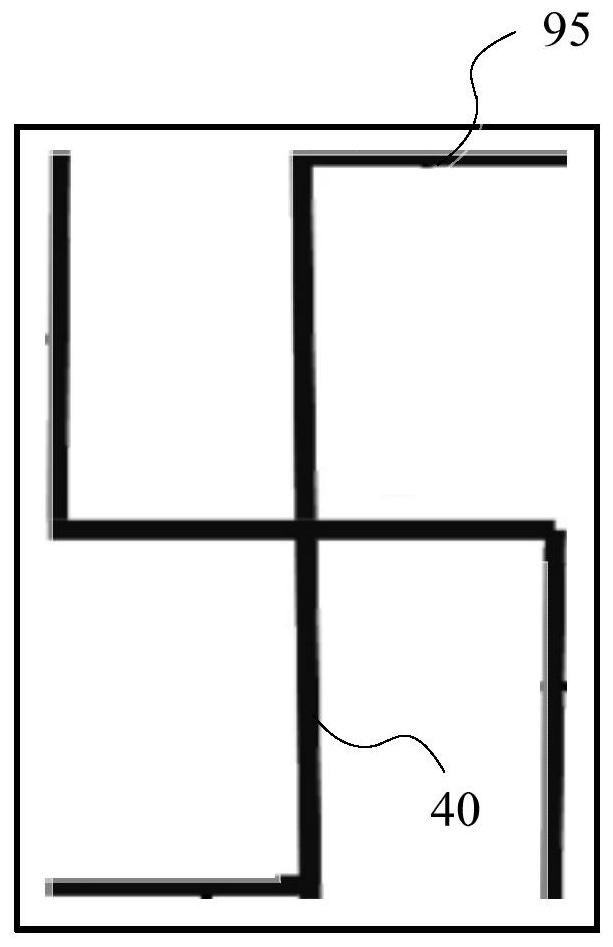

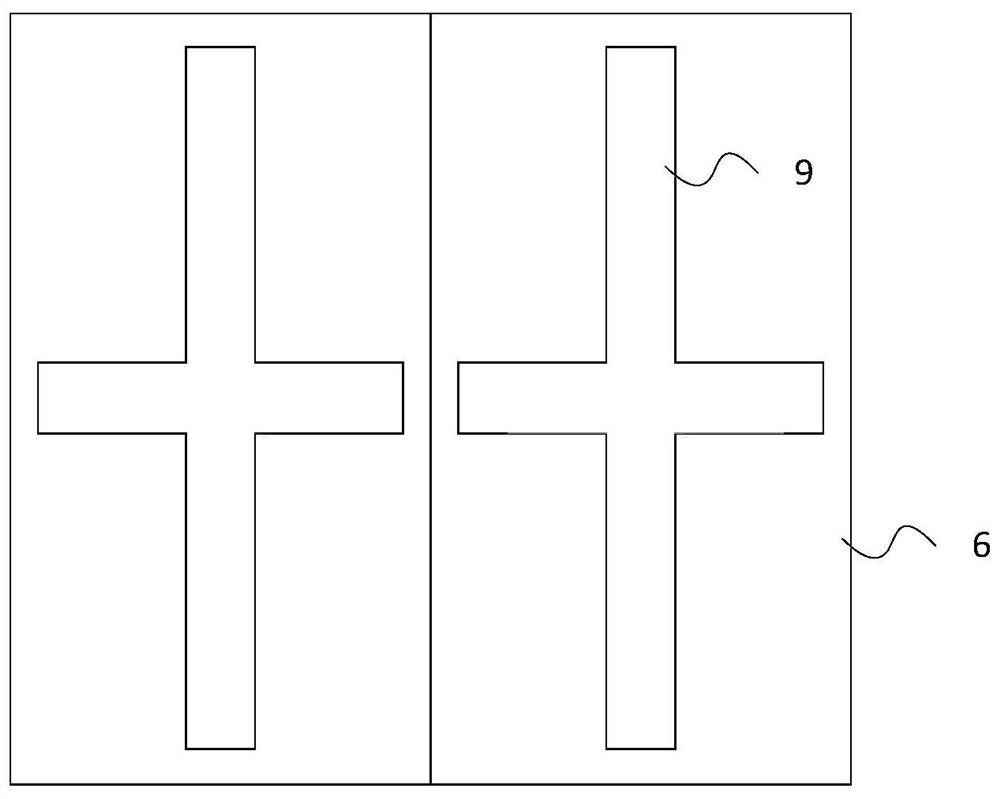

[0044] image 3 It is a schematic plan view of the part corresponding to the first region in the array substrate provided by Embodiment 1 of the present invention. Figure 4 A cross-sectional view of a part corresponding to the first region in the array substrate provided by Embodiment 1 of the present invention. In order to illustrate how to reduce the generation of dark lines, image 3 , Figure 4 Only the schematic diagram of the part corresponding to the two first regions 6 (sub-pixel units) in the array substrate is shown.

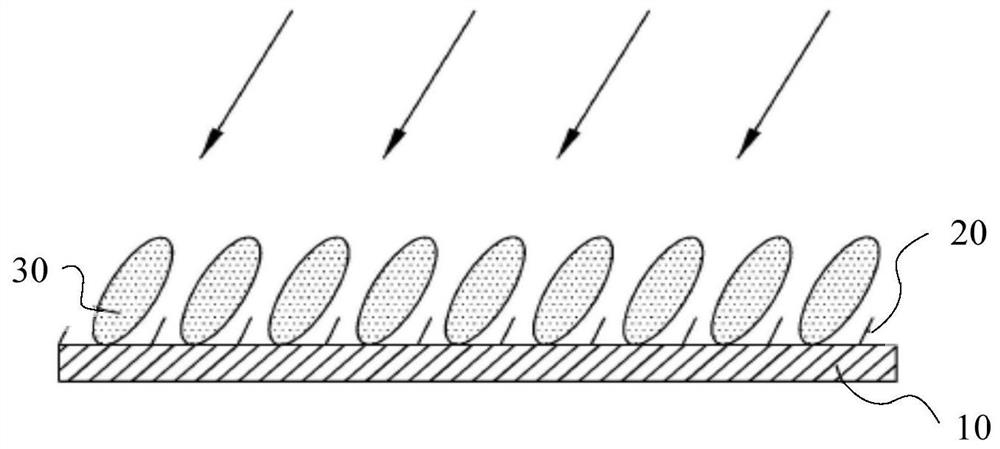

[0045] Such as image 3 , 4 As shown, the array substrate 1 of this embodiment includes an insulating layer 2 and an indium tin oxide semiconductor layer 3 disposed on the insulating layer 2, the upper side of the indium tin oxide semiconductor layer 3 is in contact with the liquid crystal 4, and the array substrate 1 further includes A plurality of sub-pixel units 5 located under the insulating layer 2, the indium tin oxide semiconductor layer 3...

Embodiment 2

[0053] On the basis of the first embodiment, this embodiment improves the arrangement of the first groove in the first embodiment above. Other parts are the same as those in Embodiment 1, and will not be repeated here.

[0054] Figure 6 A cross-sectional view of a part corresponding to the first region in the array substrate provided by Embodiment 2 of the present invention. Such as Figure 6 As shown, the first groove 9 runs through the ITO semiconductor layer 3 . This method is applied to the situation where the thickness of the indium tin oxide semiconductor layer 3 is relatively thin. At this time, in order to ensure sufficient edge effects on the liquid crystal molecules, it is necessary to form the corresponding part of the indium tin oxide semiconductor layer 3 and the first groove 9 It is a hollow cross.

[0055] In addition, compared with the case where the first groove 9 does not penetrate the indium tin oxide semiconductor layer 3, it needs to etch the surface ...

Embodiment 3

[0058] On the basis of the second embodiment, this embodiment further improves the groove portion in the second embodiment. The remaining parts are the same as those in Embodiment 2, and will not be repeated here.

[0059] Figure 7 A cross-sectional view of a part corresponding to the first region in the array substrate provided by Embodiment 3 of the present invention. Such as Figure 7 As shown, on the basis that the first groove 9 in the second embodiment penetrates the indium tin oxide semiconductor layer 3, a plurality of second grooves are formed on the surface of the insulating layer 2 that is in contact with the indium tin oxide semiconductor layer 3. Groove 92 , the projection of the plurality of second grooves 92 on the normal direction of the array substrate 1 coincides with the plurality of first grooves 9 . This method is applied to the situation where the thickness of the indium tin oxide semiconductor layer 3 is relatively thin. At this time, in order to ens...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More