Fast interrupt control system and method for RISC-V architecture

A RISC-V and control system technology, applied in the direction of program control design, program startup/switching, instruments, etc., can solve the problems of poor interrupt efficiency, lack of 8051 secondary interrupt nesting, and hardware nesting mechanism, etc. Accelerate response speed, simplify interrupt control logic, and increase flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

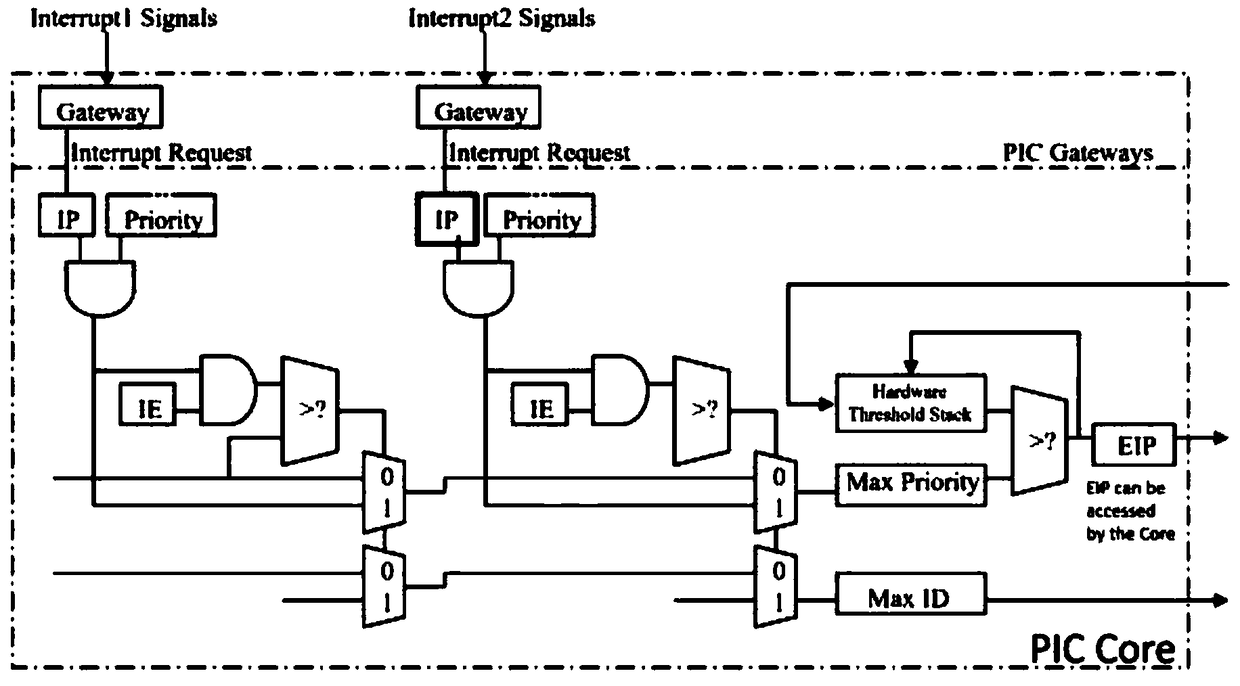

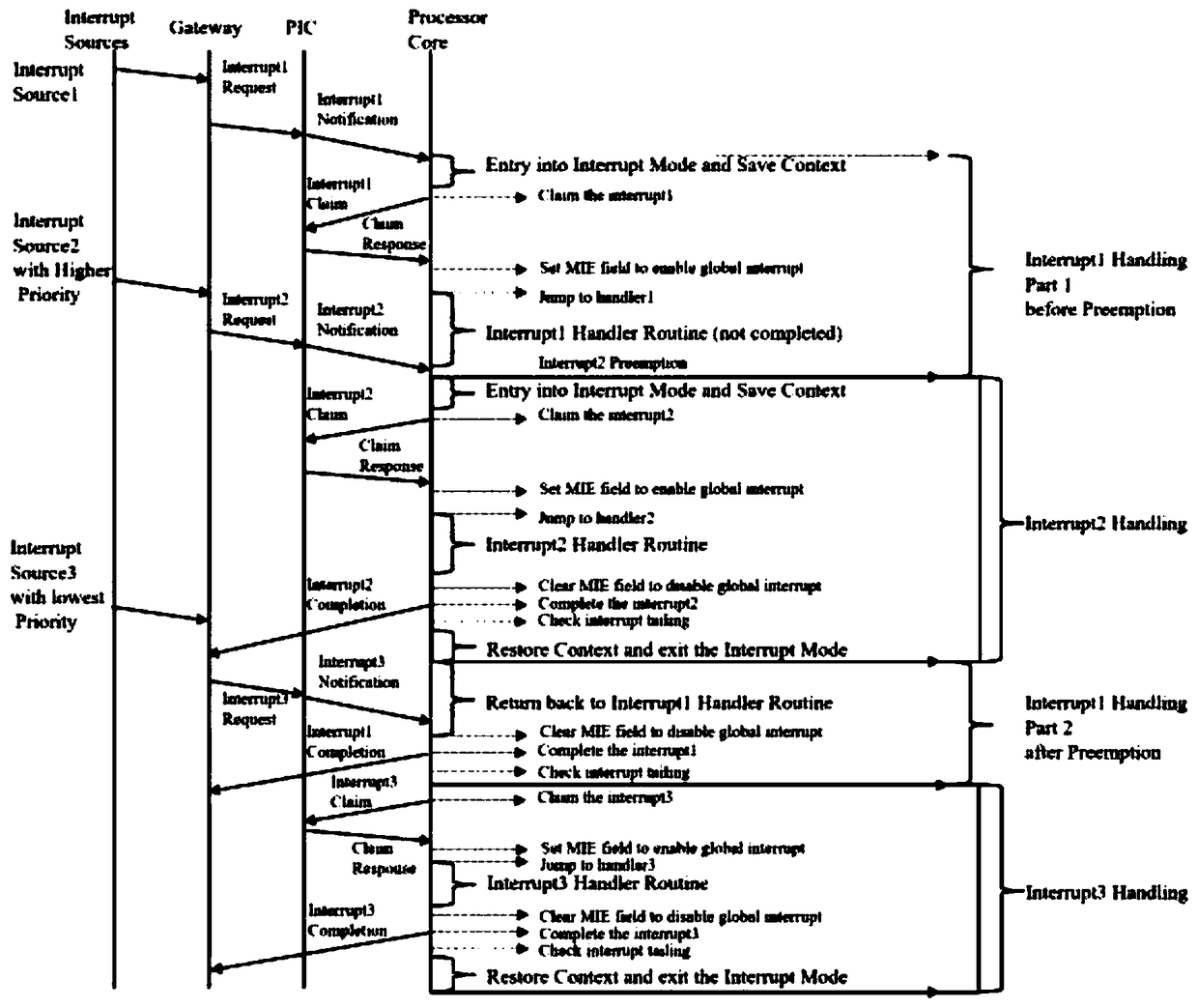

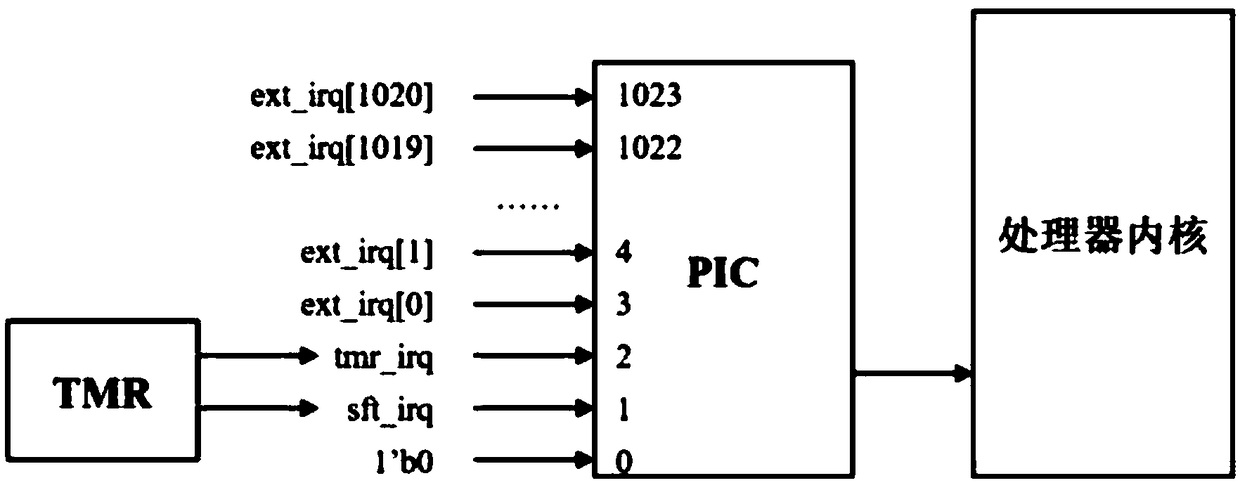

[0044] The present invention provides a fast interrupt control system and method for RISC-V architecture. Its working principle is to control the interrupt request by setting a fast interrupt control (PIC: Private Interrupt Controller) system between the interrupt source and the interrupt target. At the same time, by increasing the readable EIP register of the processor core, the mechanism of interrupt tail biting is realized, so as to solve the problem of implementing the interrupt nesting mechanism in the RISC-V architecture and improve the efficiency of interrupt processing.

[0045] The present invention will be described in further detail below in conjunction with examples and specific implementation methods.

[0046] Such as figure 1 As shown, a fast interrupt control ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More