A channel phase alignment circuit and method

A phase alignment and channel technology, applied in the direction of synchronous signal speed/phase control, electrical components, digital transmission systems, etc., can solve the problem of large serial-to-parallel conversion delay, difficult multi-channel data transmission merger processing, parallel clock phase offset Uncertainty and other problems, to achieve good precision control, good process portability and flexibility, and reduce the effect of serial-parallel conversion delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

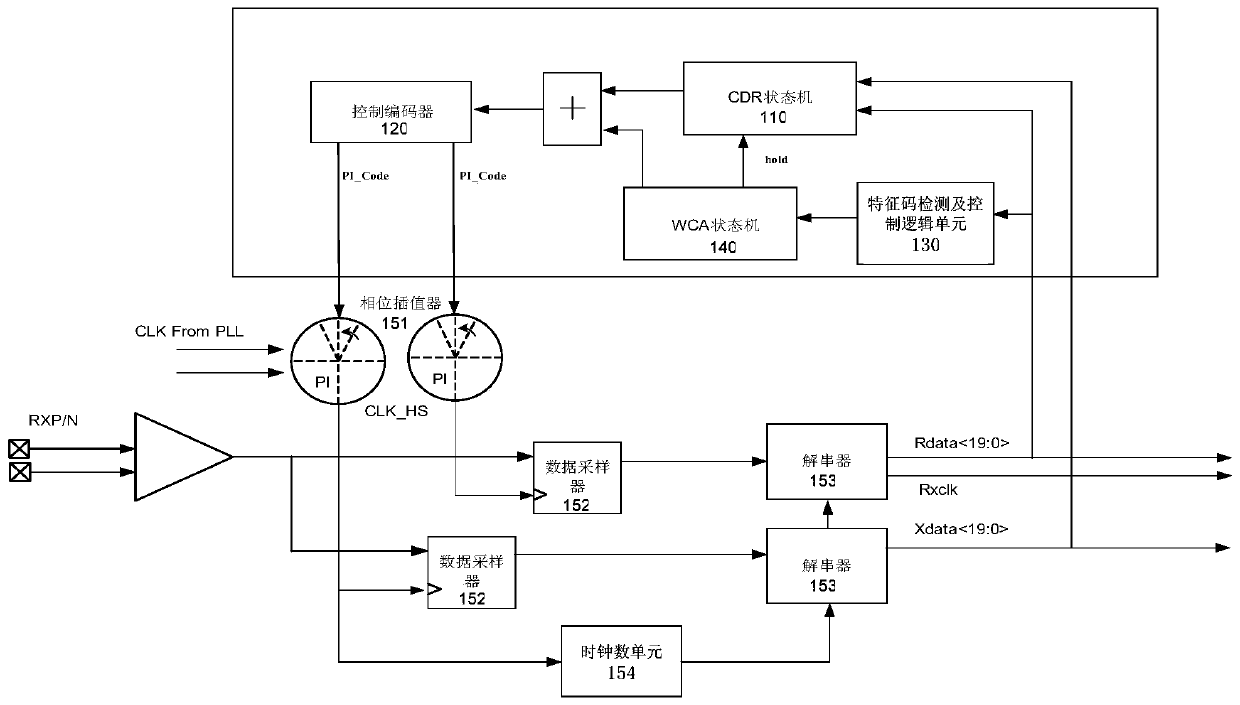

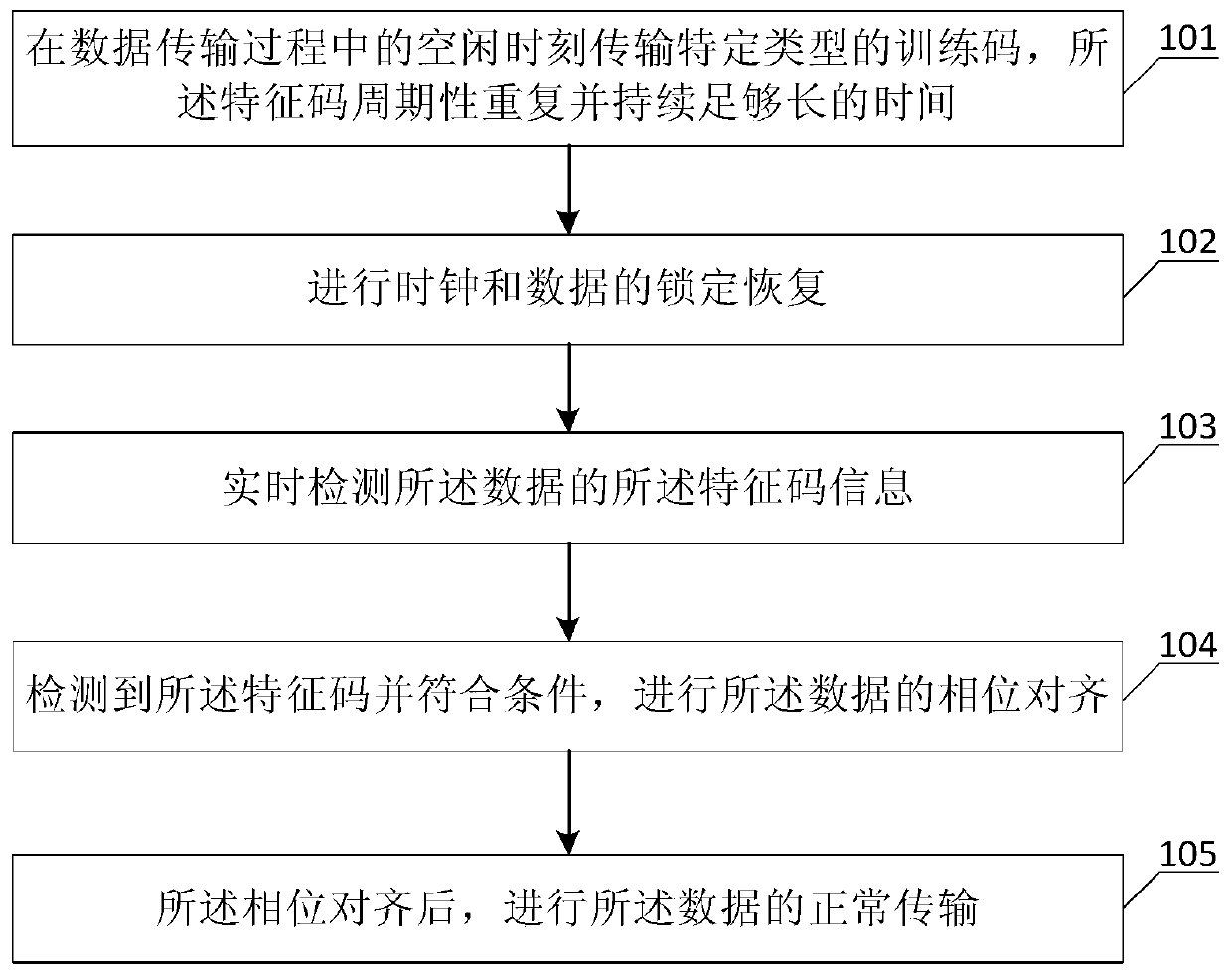

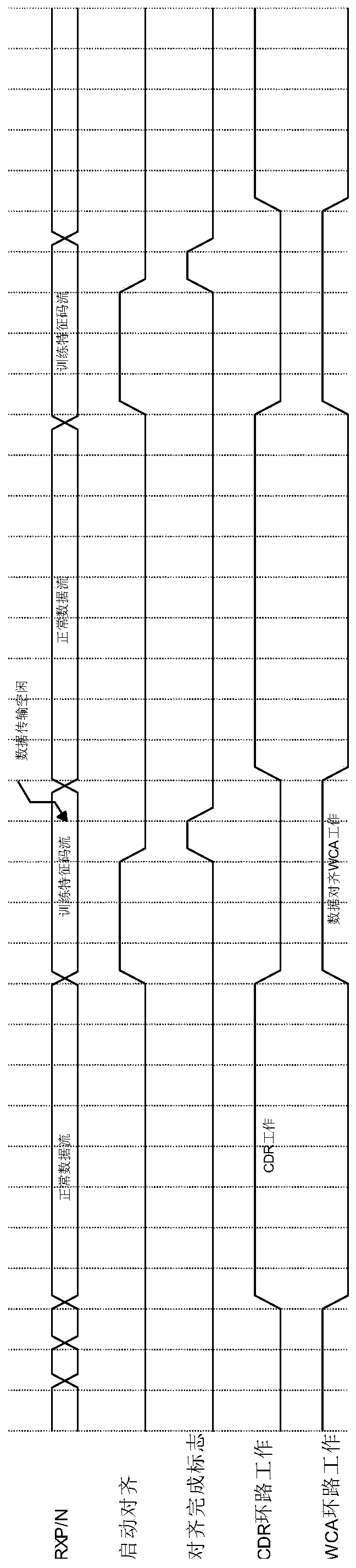

[0042] figure 1 It is a structural block diagram of a channel phase alignment circuit according to the present invention, such as figure 1 As shown, the channel phase alignment circuit of the present invention includes: a CDR state machine 110, a control encoder 120, a signature detection and control logic unit 130 and a WCA state machine 140, wherein,

[0043] The CDR state machine 110 is used for the clock and data recovery control algorithm to obtain the phase correspondence between the high-speed sampling clock and the data. Among them, the algorithm includes operations such as voting and filtering.

[0044] Preferably, the high-speed serial data enters the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More