SDI (Serial Digital Interface) high-quality synchronous de-interlacing system and method

A de-interlacing and high-quality technology, applied to TV system parts, TVs, standard conversion, etc., can solve the problems of SDI input signal can not be synchronized, picture and video are not synchronized, and there is no unified synchronization information, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

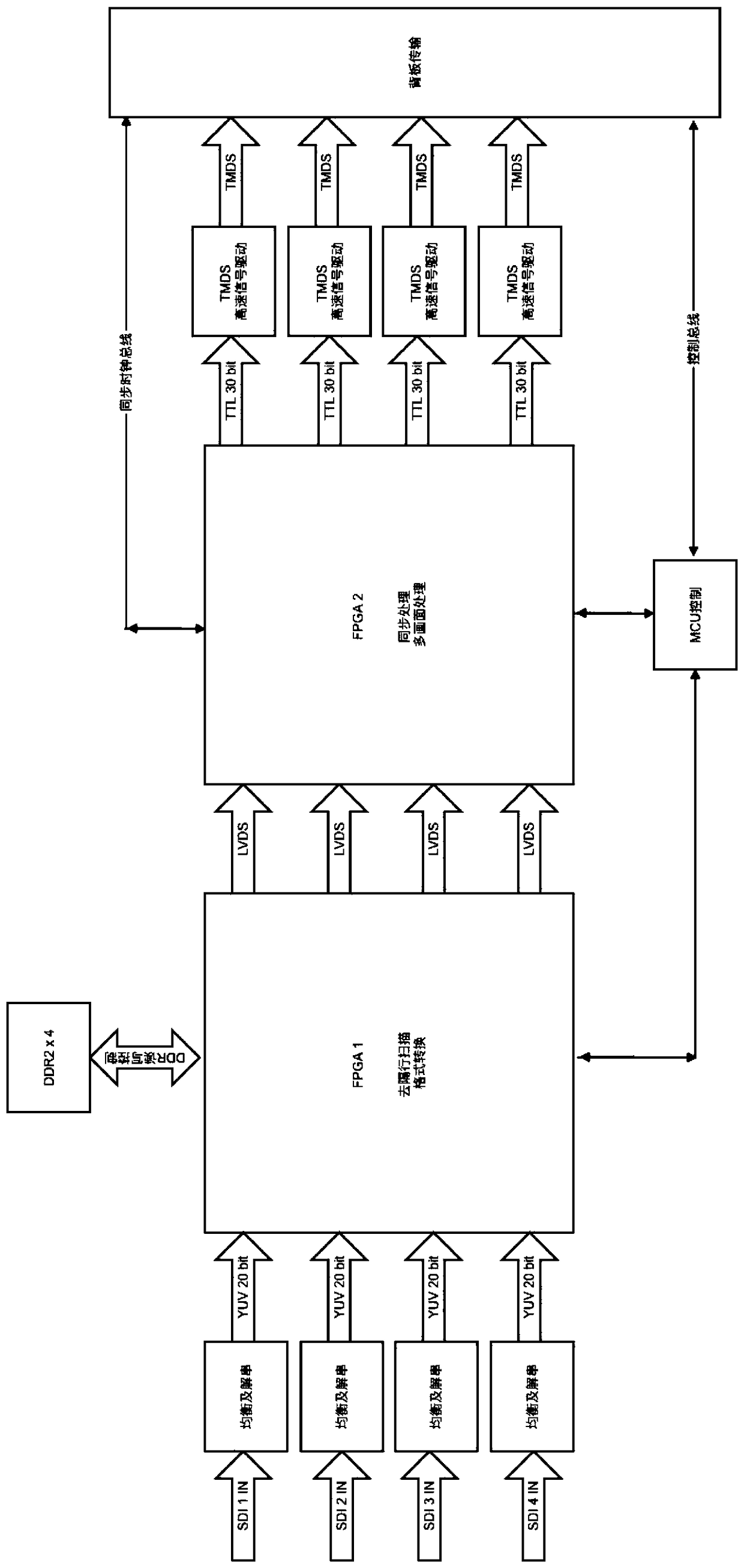

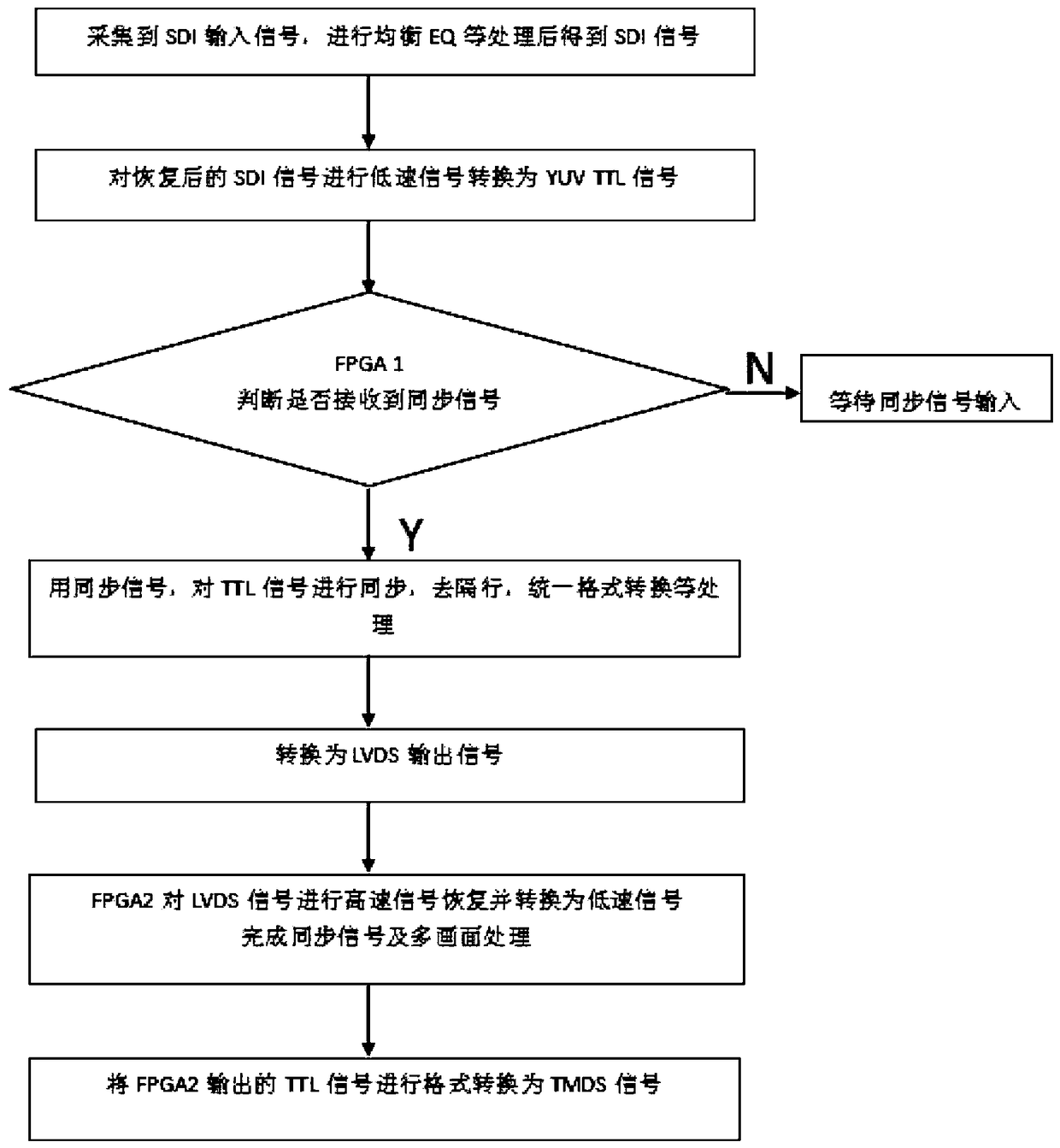

[0028] Such as figure 1 As shown, the present invention discloses an SDI high-quality synchronous deinterlacing system, which includes an equalization and deserialization module, a first FPGA module, a second FPGA module, an MCU control module, a clock IC, a synchronous clock bus, and a backplane transmission module.

[0029] Among them, the equalization and deserialization module is realized by the IT6604 chip, and its input terminal is connected to the SDI input interface to input the high-speed SDI signal after long-distance transmission, and the output terminal is connected to the first FPGA module. The equalization and deserialization module is used for equalizing the high-speed SDI module, converting the equalized high-speed SDI signal into a low-speed YUV format TTL signal, and transmitting the TTL signal to the first FPGA module.

[0030] The signal input end of the first FPGA module is connected to the output end of the equalization and deserialization module, the cl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More