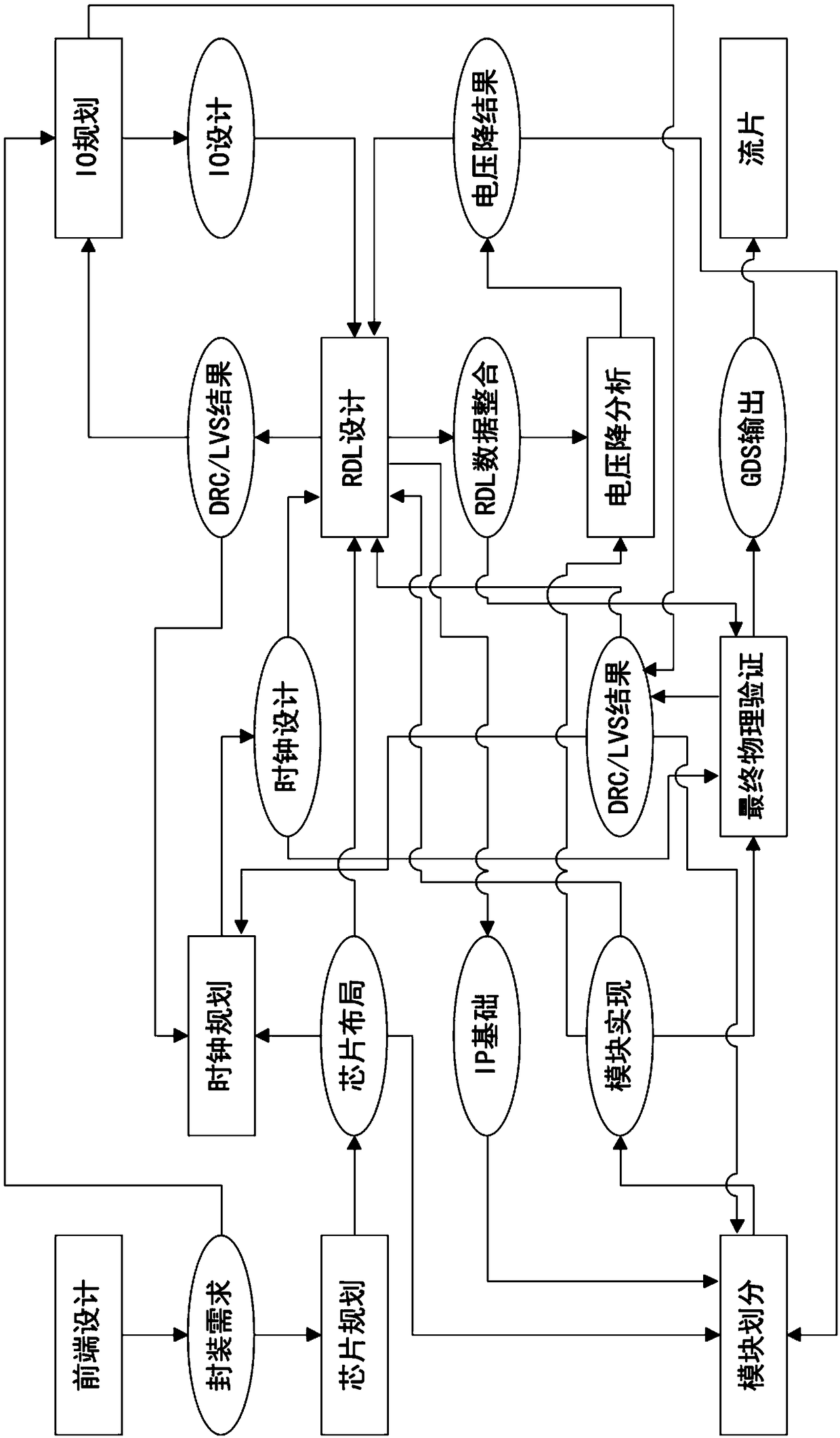

Efficient RDL design method for back-end semi-custom design of integrated circuits

A custom design and integrated circuit technology, applied in CAD circuit design, calculation, electrical digital data processing, etc., can solve problems such as increasing design difficulty and complexity, long iteration time, and inability to design advanced and efficient designs, and achieve shortened design cycle, avoid ineffective work, and reduce the effect of design iterations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

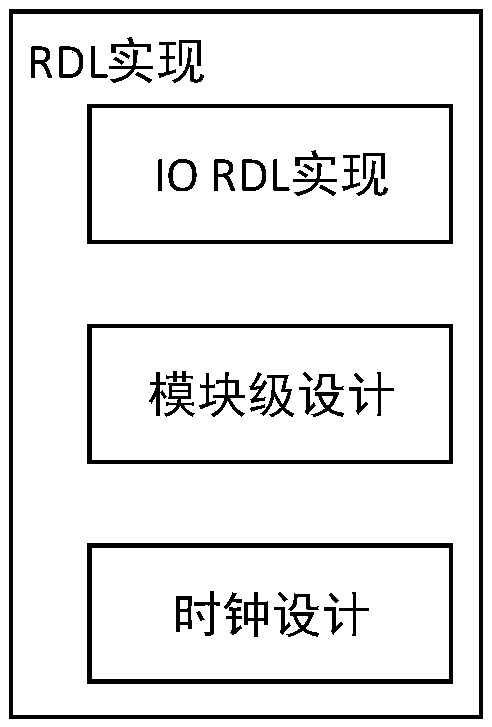

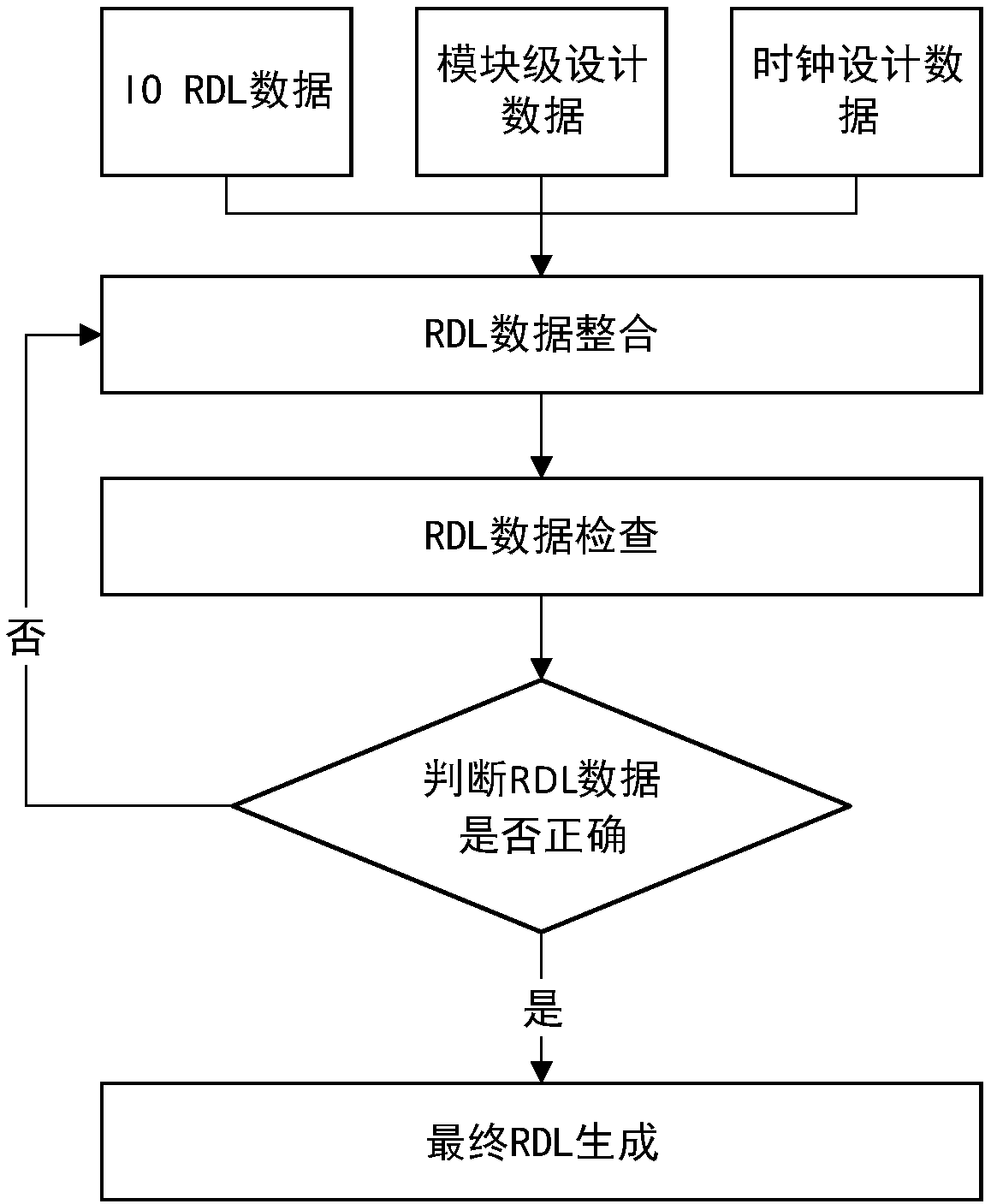

[0026] The present invention discloses a high-efficiency RDL design method for integrated circuit back-end semi-custom design. The specific implementation of the present invention will be further described below in combination with preferred embodiments.

[0027] It is worth mentioning that those skilled in the art should note that the "RDL" (Redistribution Layer) involved in the patent application of the present invention is defined as "redistribution layer"; the "GDS" involved in the patent application of the present invention is defined as a A kind of "data format during chip production"; "LVS" involved in the patent application of the present invention is defined as "comparison between layout and schematic diagram"; "DRC" involved in the patent application of the present invention is defined as "design rule check"; The "IP" involved in the patent application of the present invention is defined as "intellectual property rights"; the "IO" involved in the patent application of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com