D-latch resistant to double-node flipping

A dual-node inversion and latch technology is applied in the direction of reliability improvement, modification, delay compensation, etc., which can solve the problems of fault tolerance that cannot be realized by dual-node inversion, poor resistance to dual-node inversion, and long propagation delay time. Achieve the effect of improving the ability of single node and anti-dual node inversion, reducing power consumption and fewer devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0050] It should be noted that, in the case of no conflict, the embodiments of the present invention and the features in the embodiments can be combined with each other.

[0051] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

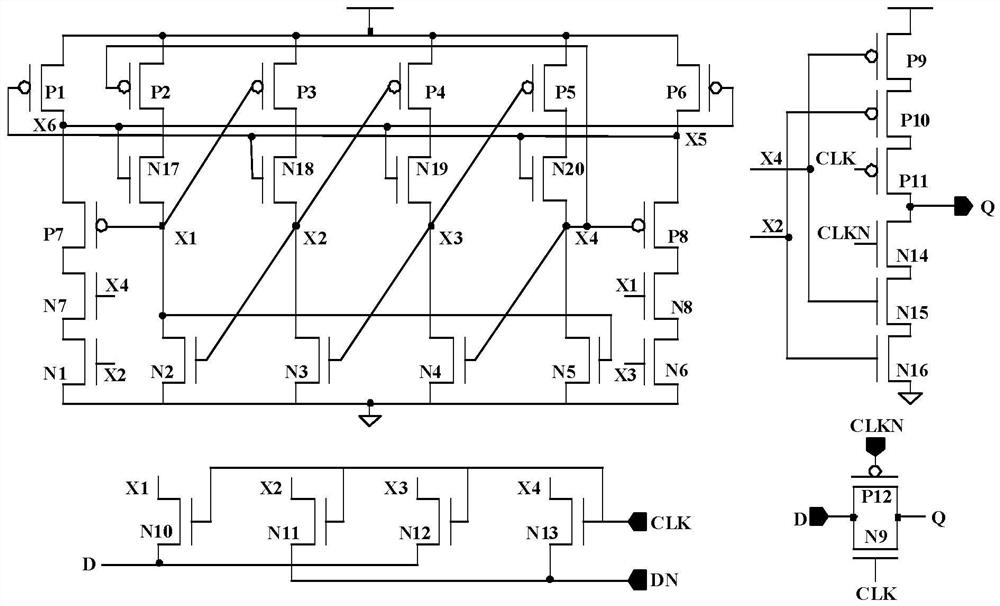

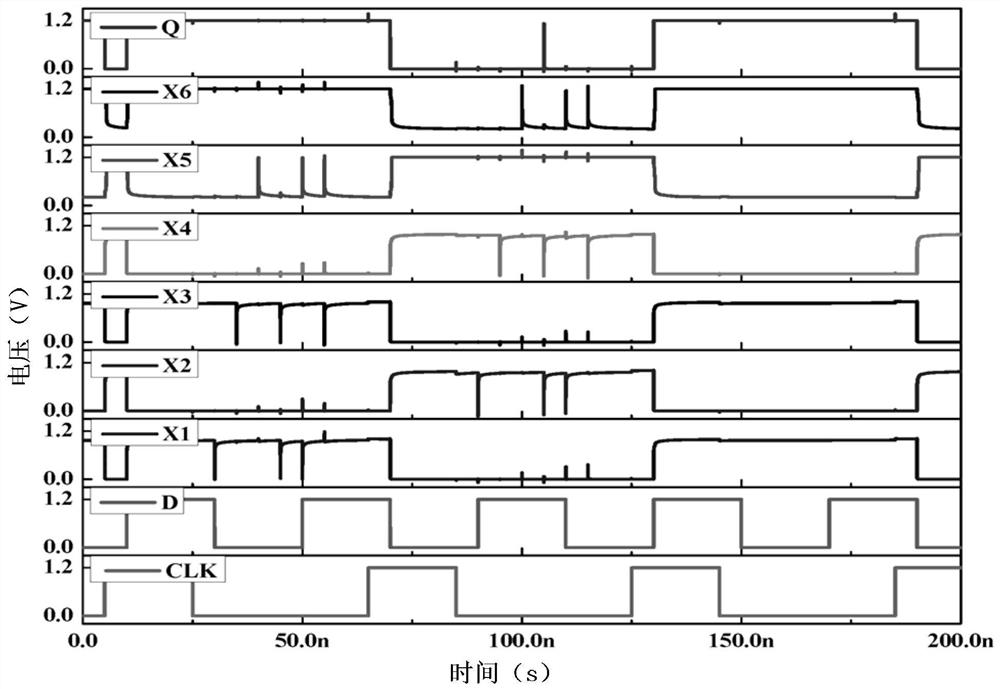

[0052] see figure 1 Describe this embodiment mode, the anti-double-node flipping D latch described in this...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More