Patents

Literature

100results about How to "To achieve fault tolerance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

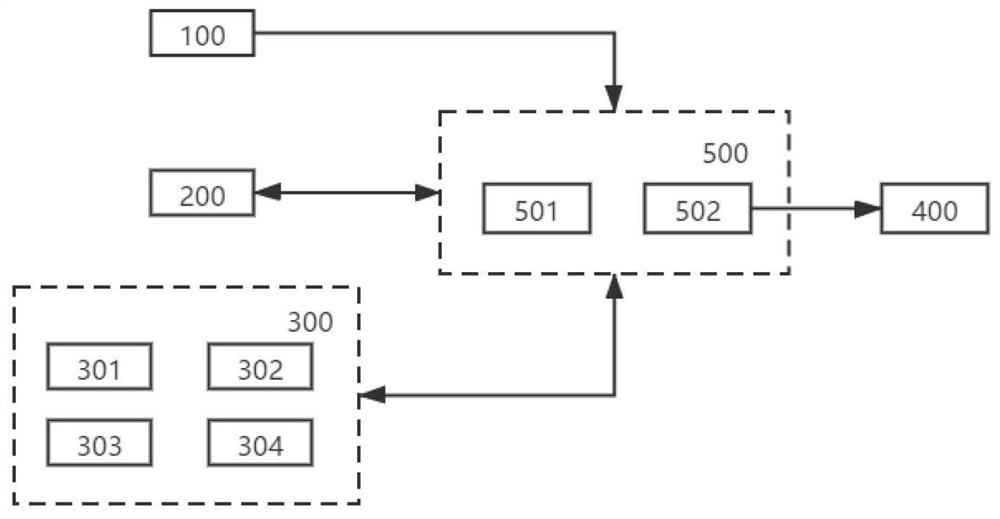

Failure detection and fault tolerance method and failure detection and fault tolerance system for real-time cloud platform

ActiveCN103716182ANo loss of stateComprehensive detection effectData switching networksFault toleranceReal time services

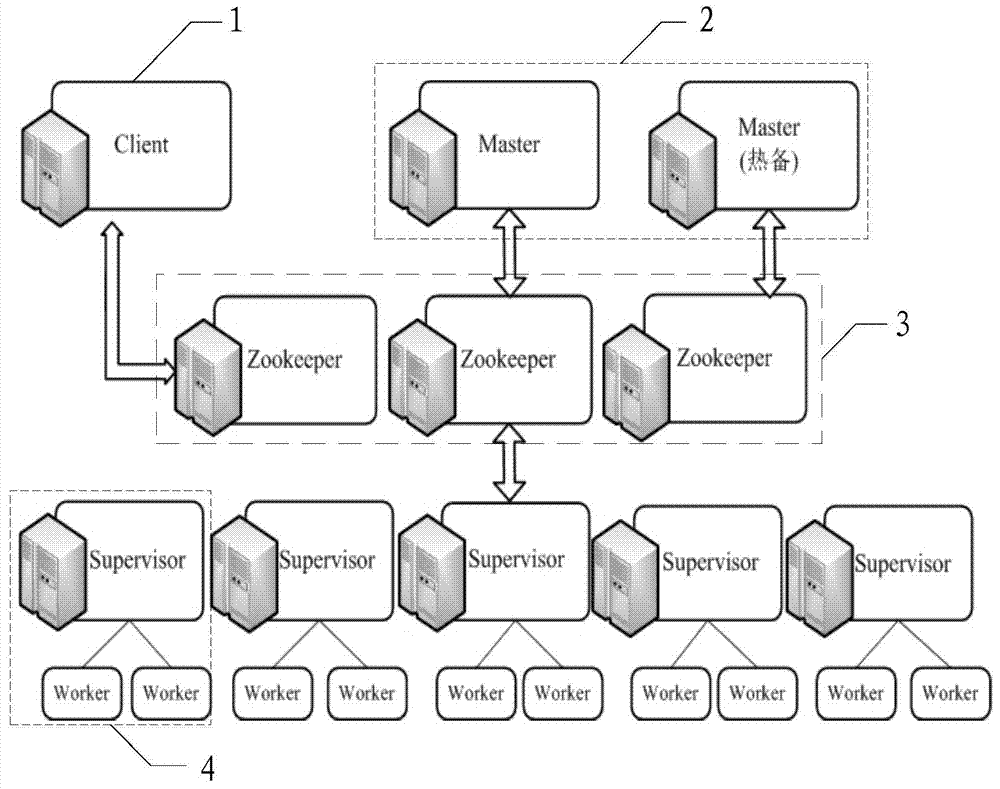

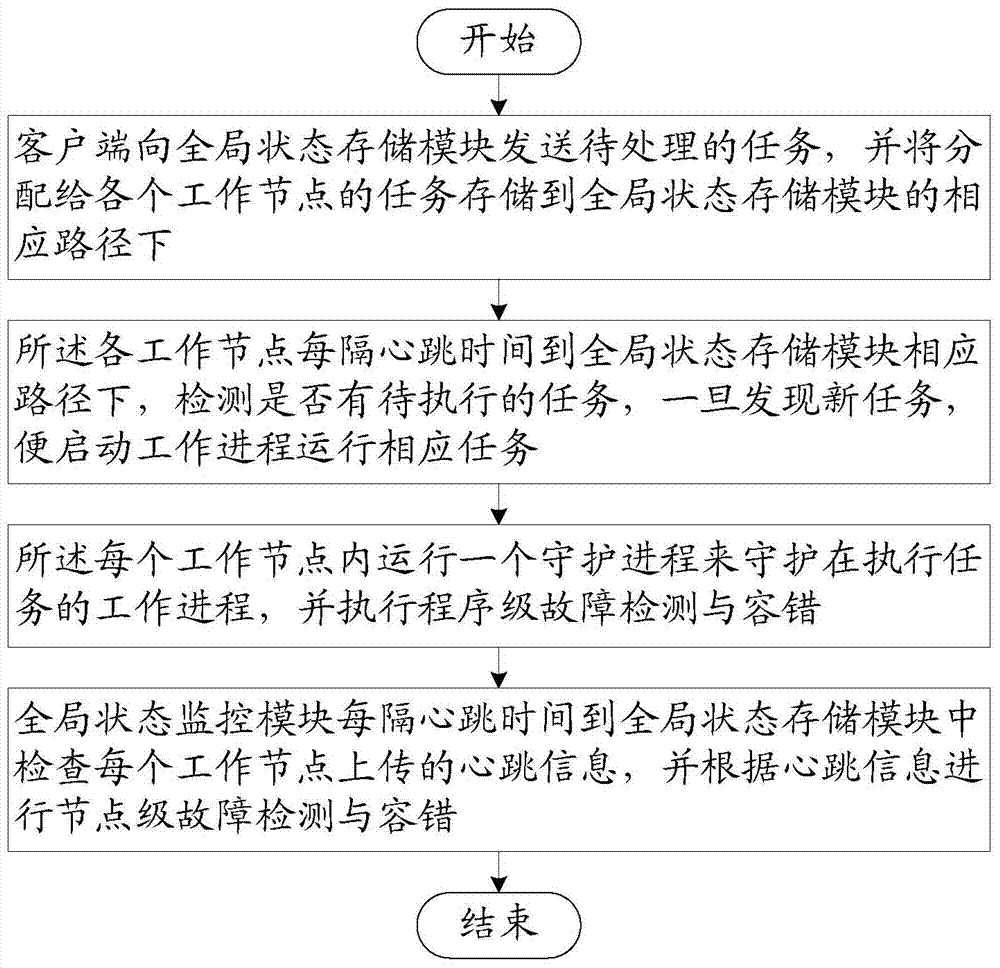

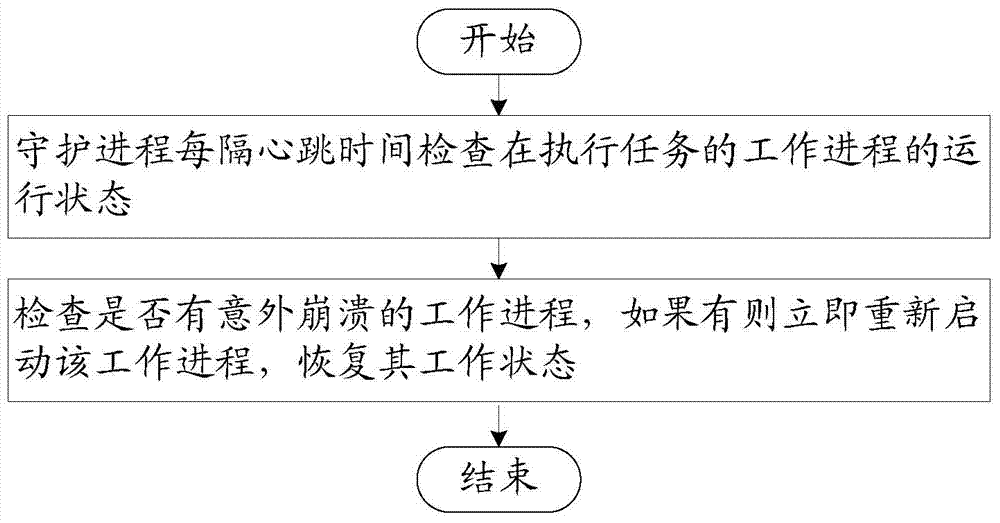

The invention relates to a failure detection and fault tolerance method and a failure detection and fault tolerance system for a real-time cloud platform. The system comprises a client used for sending a command, summiting a task and storing tasks assigned to working nodes in corresponding paths, a global state monitoring module used for monitoring the operation state of the working nodes, carrying out node-level failure detection and fault tolerance according to heartbeat information uploaded by the working nodes and performing migration of a task in a failure node, a global state storage module used for storing the working state and heartbeat information of the global state monitoring module and the working nodes, and working nodes used for performing a task, running a daemon process to guard a work process and performing program-level failure detection and fault tolerance. State information of a whole cluster is all stored in a Zookeeper system, a stateless architecture of the nodes is realized, a node failure does not cause state loss, the system has a perfect failure detection and fault tolerance mechanism, multilevel fault tolerance is realized, and uninterrupted operation of real-time services is guaranteed.

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

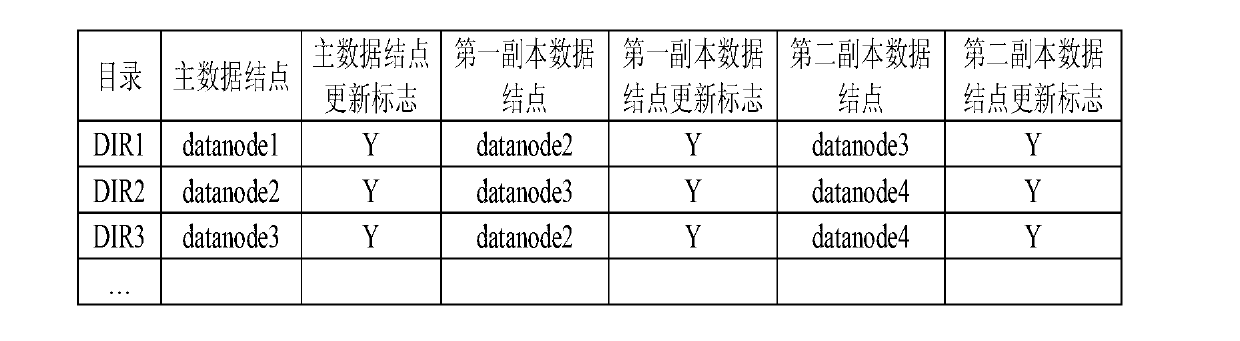

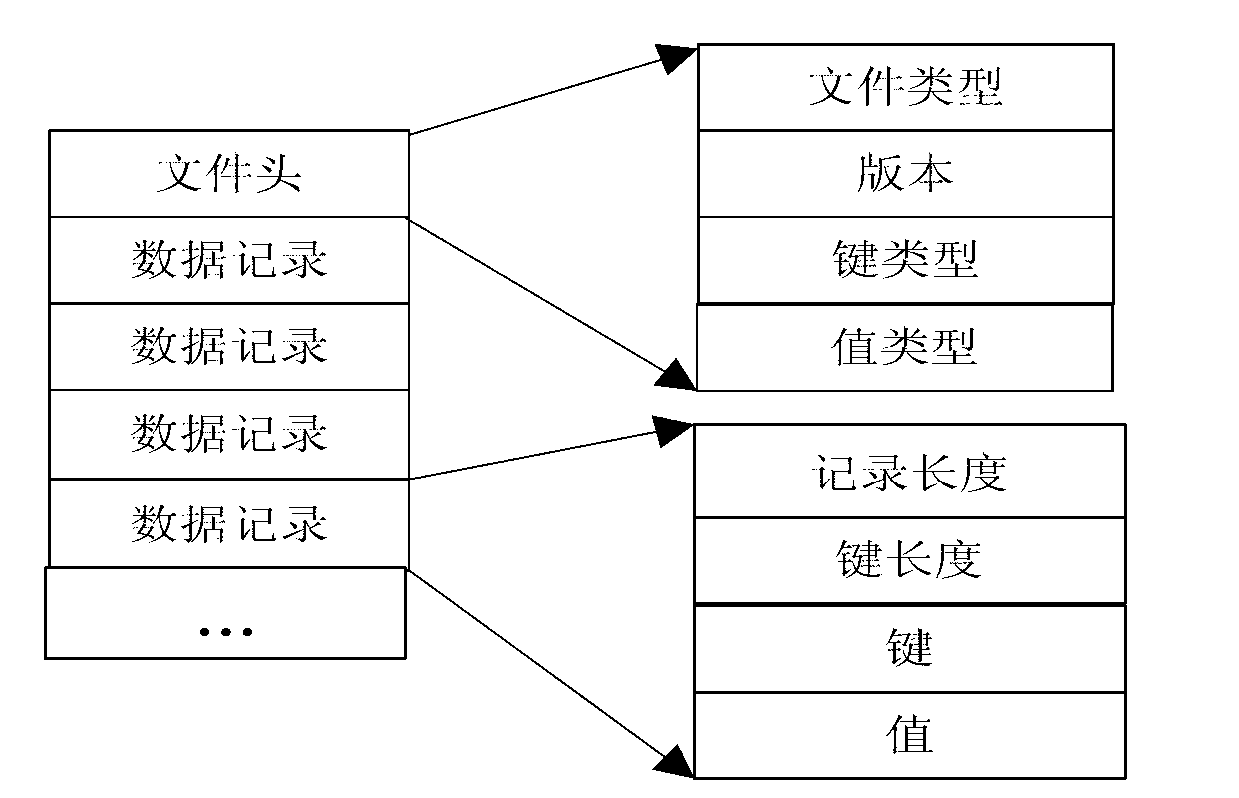

Method for storing mass of small files on basis of master-slave distributed file system

ActiveCN103020315ATo achieve fault toleranceSolve the problem when storing a large number of small filesSpecial data processing applicationsDistributed File SystemData file

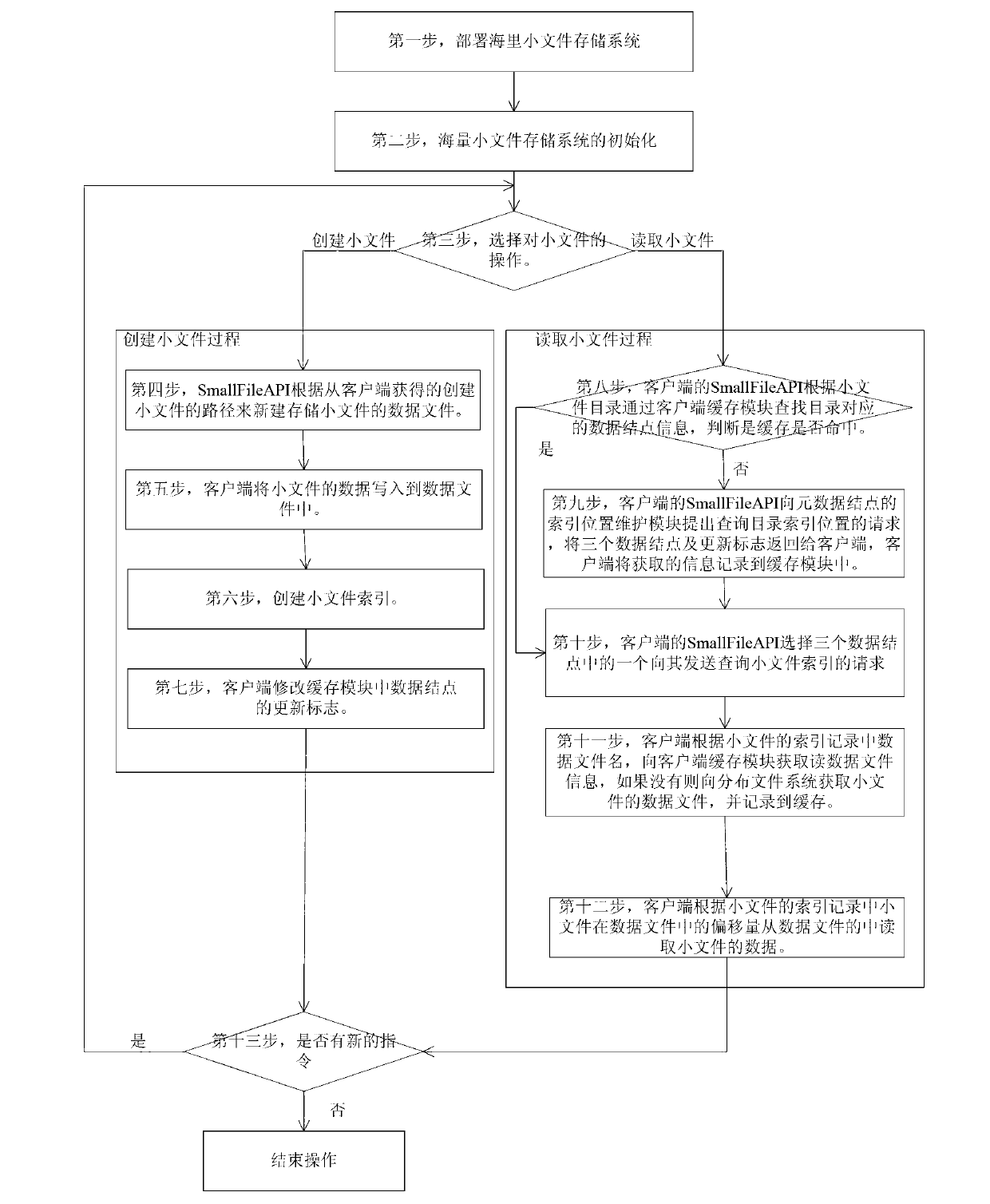

The invention discloses a method for storing a mass of small files on the basis of a master-slave distributed file system, and aims to solve the problem about storing the mass small files in the master-slave distributed file system. The technical scheme includes that the method includes that a mass small file storage system is deployed and initialized, and then small files are created and read by a SmallFileAPI (small file-application program interface) of a client side according to a command received from a keyboard. When the small files are created by a system, the SmallFileAPI creates data files of the small files according to small file paths obtained from the client side, writes in small file data and simultaneously creates small file indexes at data nodes; when the small files are read by the system, data node information corresponding to a parent directory is acquired according to the small file paths, an index request is transmitted to any of the data nodes, and finally the small file data are read from the data files according to index information. By the aid of the method, the problem about mass of storage metadata of the mass of small files is solved, writing efficiency of the mass small file storage system is improved, and reliability of the system is guaranteed.

Owner:NAT UNIV OF DEFENSE TECH

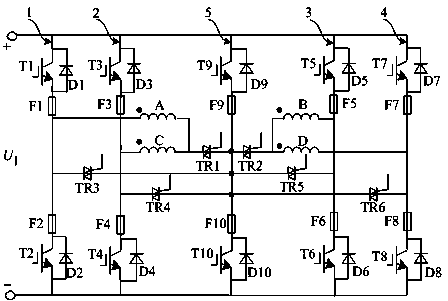

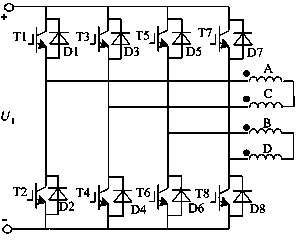

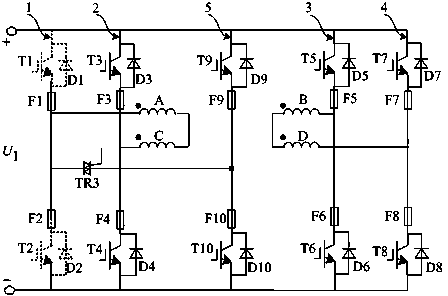

Four-phase brushless DC (direct current) motor fault-tolerant power converter and control method thereof

ActiveCN103812319ATo achieve fault toleranceMultiple Redundant Phase WindingsElectronic commutation motor controlPower conversion systemsDC - Direct currentControl engineering

The invention discloses a four-phase brushless DC motor fault-tolerant power converter and a control method thereof. The four-phase brushless DC motor fault-tolerant power converter comprises five inverting bridge arms, six bidirectional thyristors and ten fuses, a four-phase winding is connected to the midpoints of four of the bridge arms after forming two mutually-isolated channels, and the fifth bridge arms is a redundant bridge arm and only works during fault-tolerant operation; every power tube on every bridge arm is connected in series with a corresponding fuse, which can protect the system from being burnt due to short circuit faults and can convert the short circuit faults into open circuit faults for fault tolerance when the short circuit fault occur. The midpoint of every bridge arm is connected with a bidirectional thyristor for achieving fault tolerance of the power tubes; the neutral point of the winding and the midpoint of the fifth bridge arm are also connected with one bidirectional thyristor for achieving fault tolerance of the winding. The four-phase brushless DC motor fault-tolerant power converter is applicable to a four-phase permanent-magnetic brushless DC motor and a double-salient motor and can achieve open circuit and short circuit fault tolerance of power tubes and windings.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

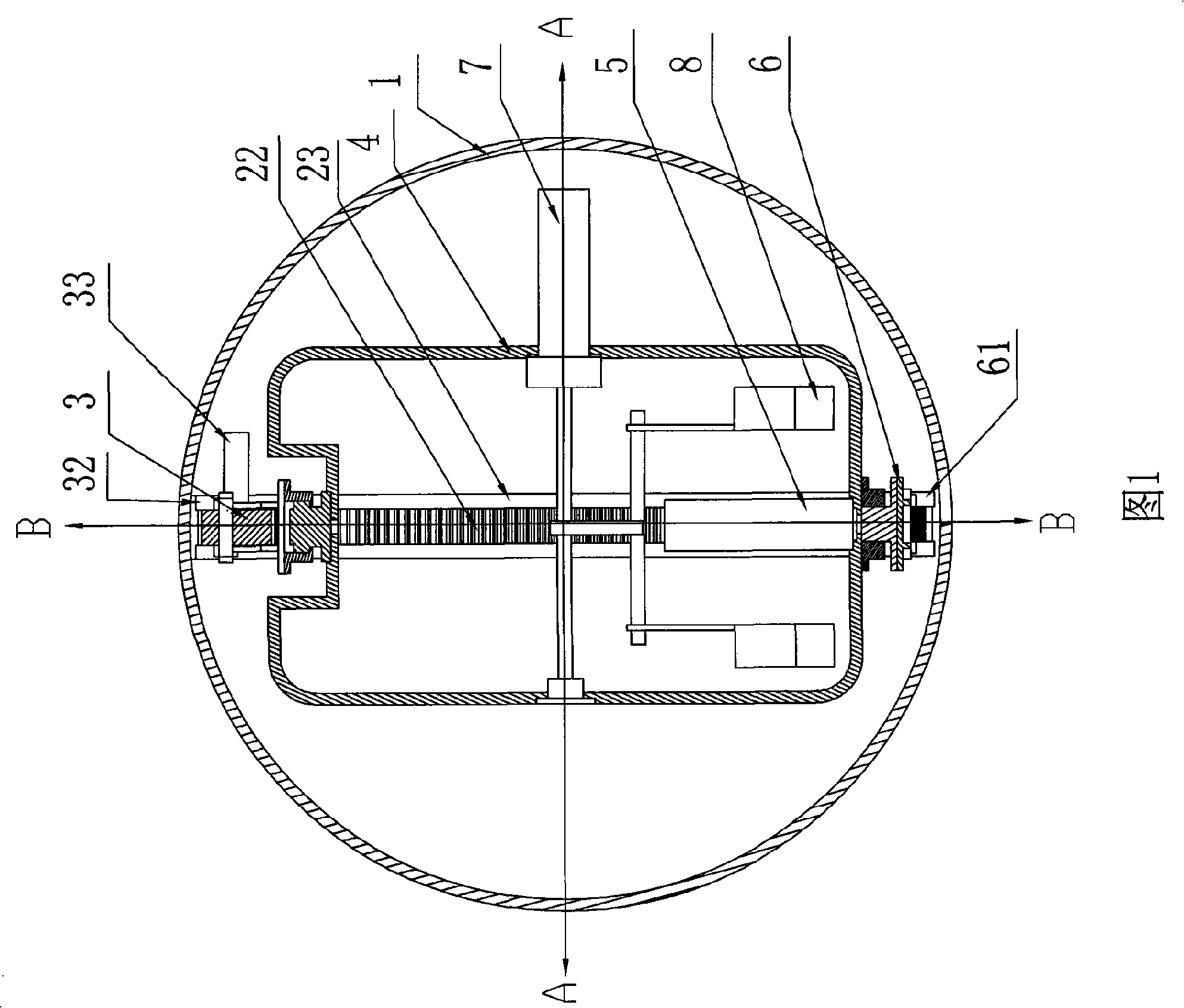

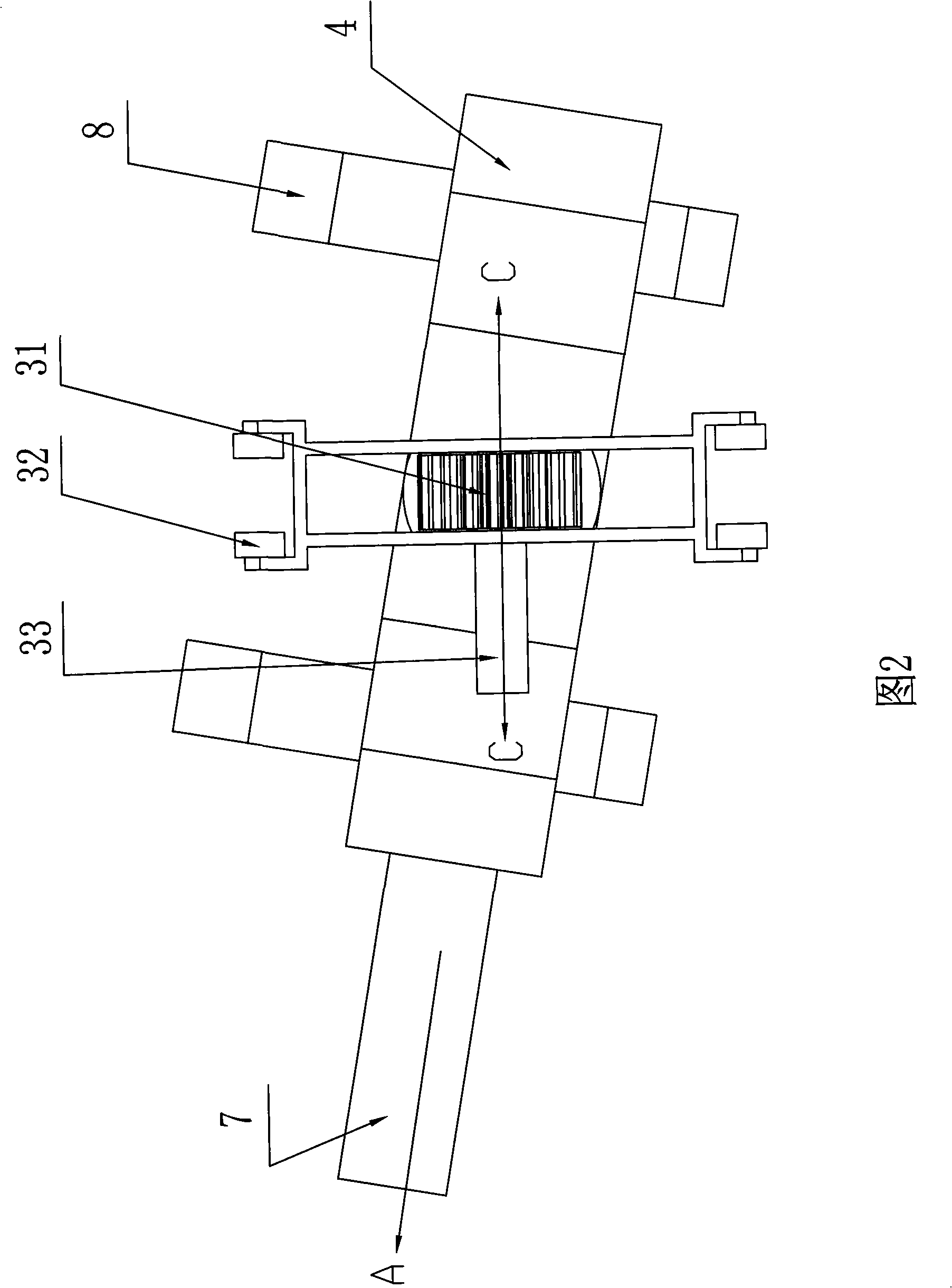

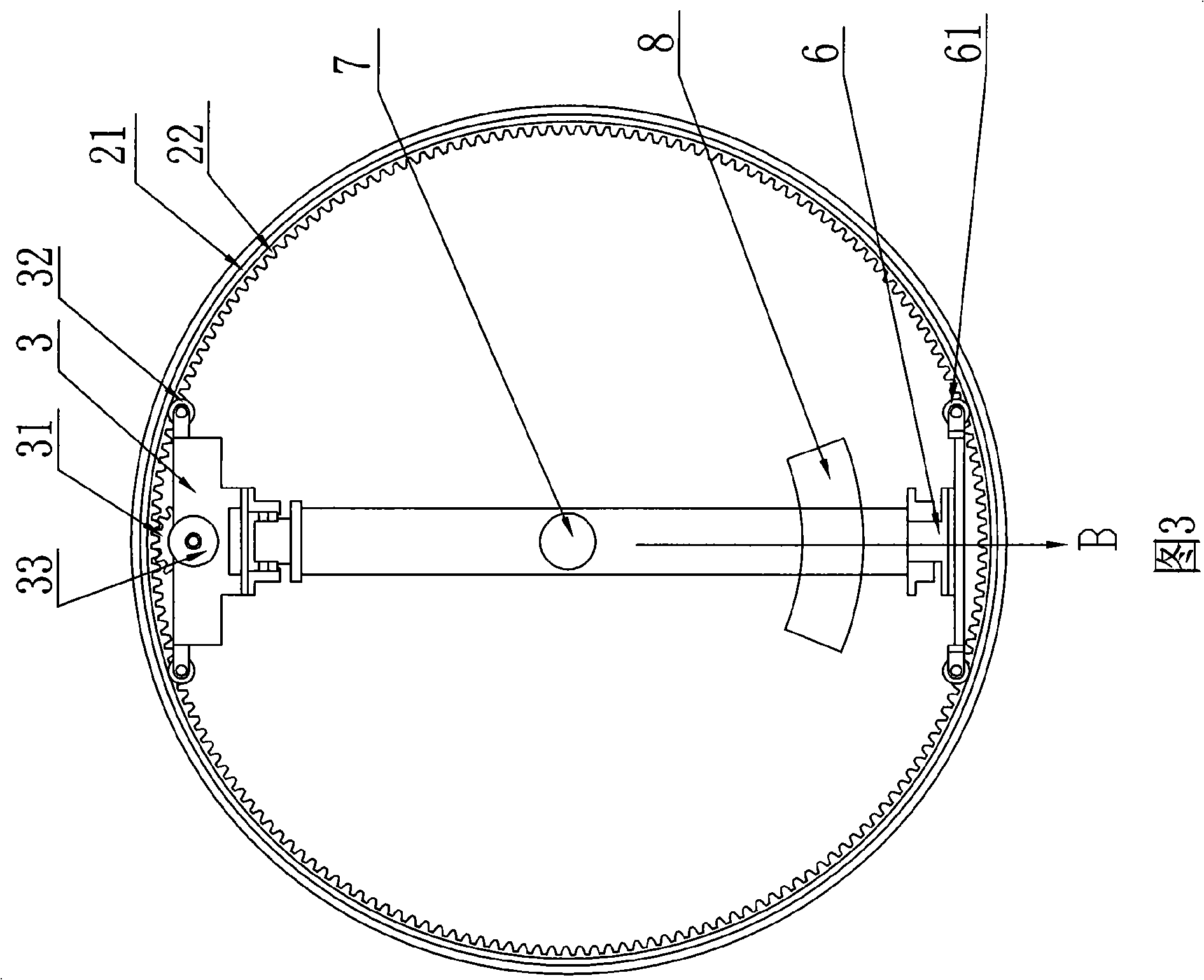

Three-drive spherical robot

InactiveCN101318526AFlexible movementAchieving Motion RedundancyVehiclesConfiguration designMotor drive

The invention discloses a three-drive spherical robot which comprises a circle spherical shell and a drive motor; wherein, a track is arranged on the inner surface of the spherical shell; an annular rack is arranged on the inner surface of the track; a walking bracket is connected with the track by a road wheel engaged with the rack; a walking bracket guide wheel is arranged on the walking bracket as well; the walking bracket is provided with a track motor and comprises a spherical frame as well; one end of the spherical frame is connected with the walking bracket by a bearing and the other end is connected with a rotating bracket by a long axis motor; a short-axis motor is axially arranged at the spherical frame; a heavy pendulum is axially arranged at the short-axis motor; the rotating bracket is connected with the track by the guide wheel arranged at the walking bracket. The three-drive spherical robot not only moves flexibly, but also realizes motion redundancy; under the situation that one of a track axis motor drive or a short axis motor drive goes wrong, the rest two drives can still be used for realizing omnidirectional rolling, namely realizing the system fault tolerance by a configuration design.

Owner:BEIJING UNIV OF POSTS & TELECOMM

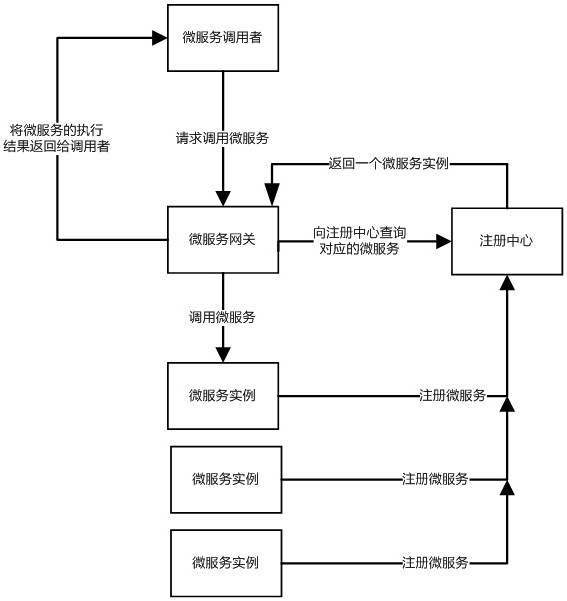

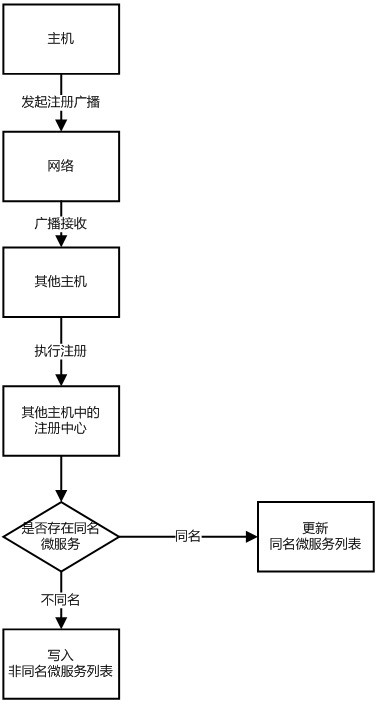

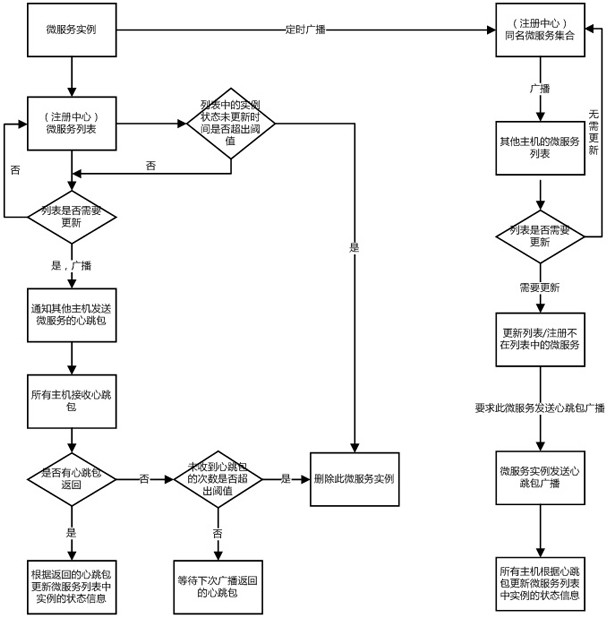

Distributed micro-service registration and calling method based on broadcast

ActiveCN111615066AImprove usabilityAchieve consistencyNetwork traffic/resource managementBroadcast service distributionEngineeringService information

The invention discloses a distributed micro-service registration and calling method based on broadcast. The method comprises the following steps that a registration center is registered in each host deployed with micro-service; when a new micro-service is registered in a certain host, the host sends a registration broadcast to the network to notify other hosts in the network to update the micro-service list in the registration center; when a caller calls the micro-service, the caller initiates a query broadcast to the network; the host deployed with the homonymous micro-service initiates a response to the network, and provides the current load condition of the host and the deployed micro-service information; and after receiving the response, the caller selects a proper host through the load balancer according to the current load conditions of different hosts, transmits a request parameter to the selected host, and calls the micro-service. According to the invention, a distributed and decentralized micro-service registration mechanism is adopted, so that registration and calling of other micro-services are not influenced after one registration node is offline due to a fault, and theavailability of the micro-services is improved.

Owner:OCEAN UNIV OF CHINA

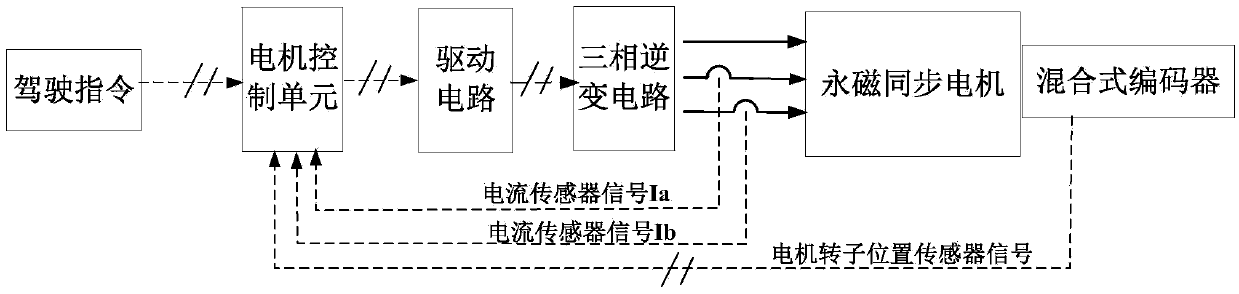

Fault monitoring and fault-tolerant control method for electric vehicle driving system

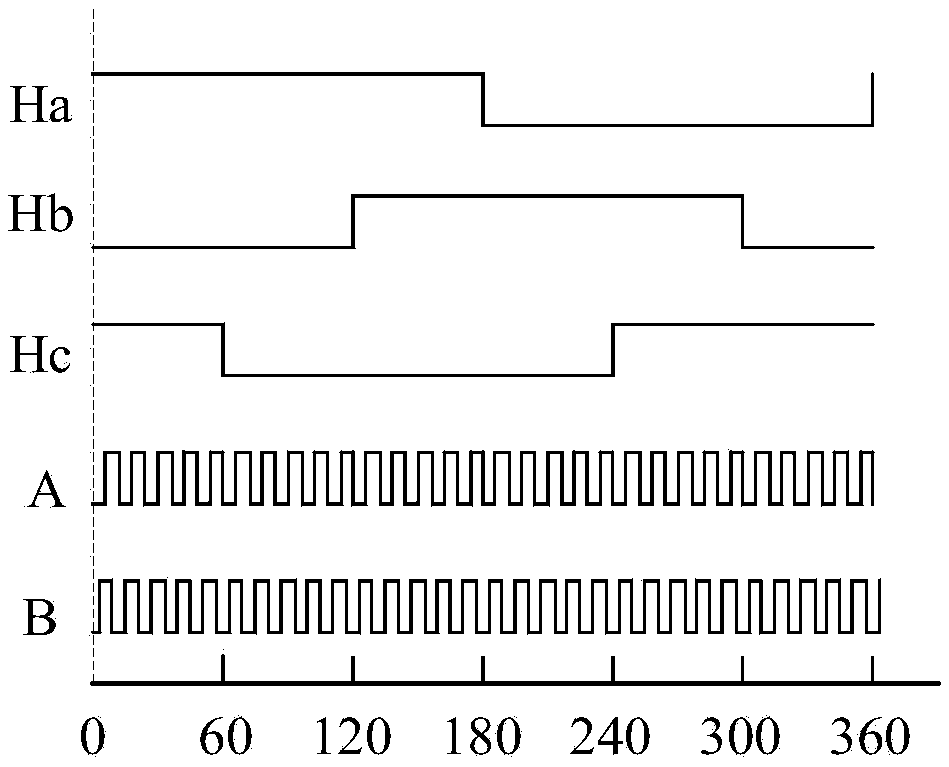

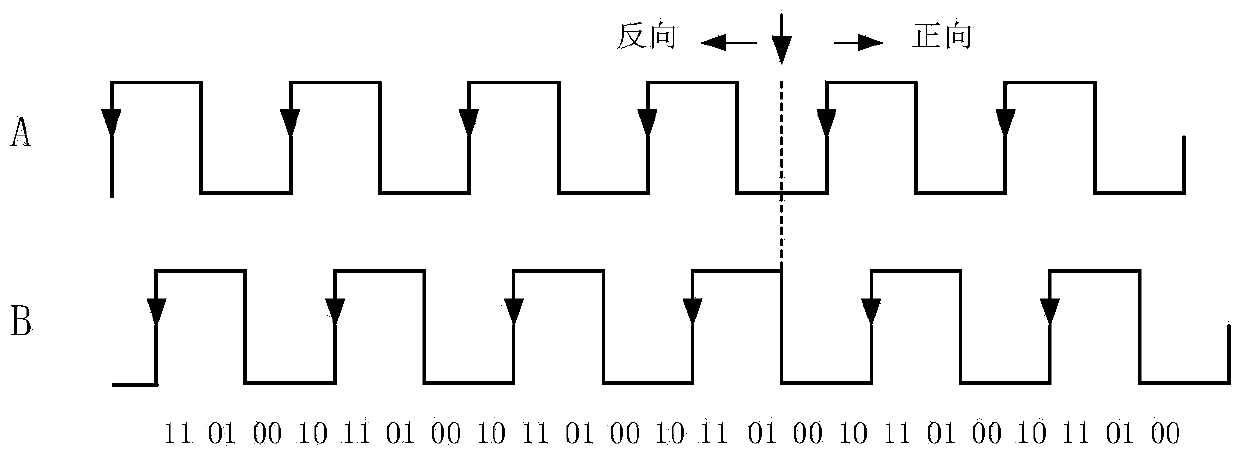

InactiveCN105375833AAccurate absolute position informationAccurate calculationElectronic commutatorsHybrid typePulse control

The invention discloses a fault monitoring and fault-tolerant control method for an electric vehicle driving system. The method overcomes the problem that incremental signals A and B of a magnetoelectric hybrid type encoder fail to cause that the driving system loses accurate position information. The method comprises the following steps: firstly, judging the initial rotor position of a permanent magnet synchronous motor by a motor control unit; secondly, controlling motor start-up in a six-pulse control mode according to the initial rotor position by the motor control unit; thirdly, judging whether the height of any path of level in the levels of absolute signals HA, HB and HC of the magnetoelectric hybrid type encoder changes by the motor control unit, entering a fourth step if the change occurs, if not, returning to the second step; fourthly, obtaining accurate rotor absolute position information according to the absolute signal level change edge of the magnetoelectric hybrid type encoder; fifthly, collecting the current state Q(n) of the incremental signals of the magnetoelectric hybrid type encoder by the motor control unit; ......; and ninthly, carrying out space vector calculation by utilizing the rotor position information calculated in the seventh step or the eighth step by the motor control unit so as to complete a one-time timer interruption task.

Owner:JILIN UNIV

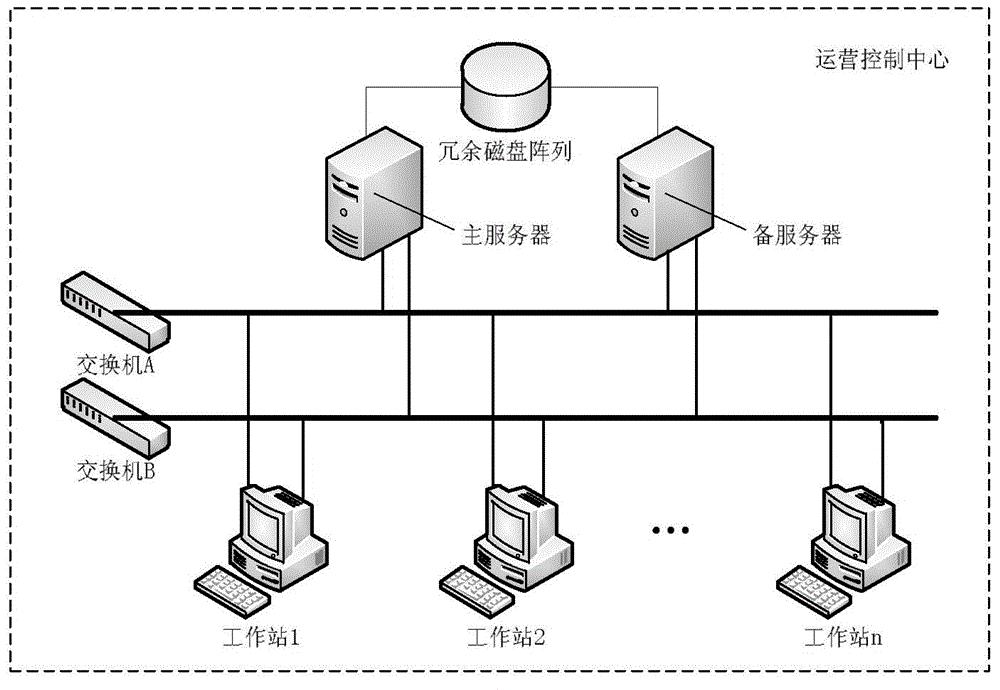

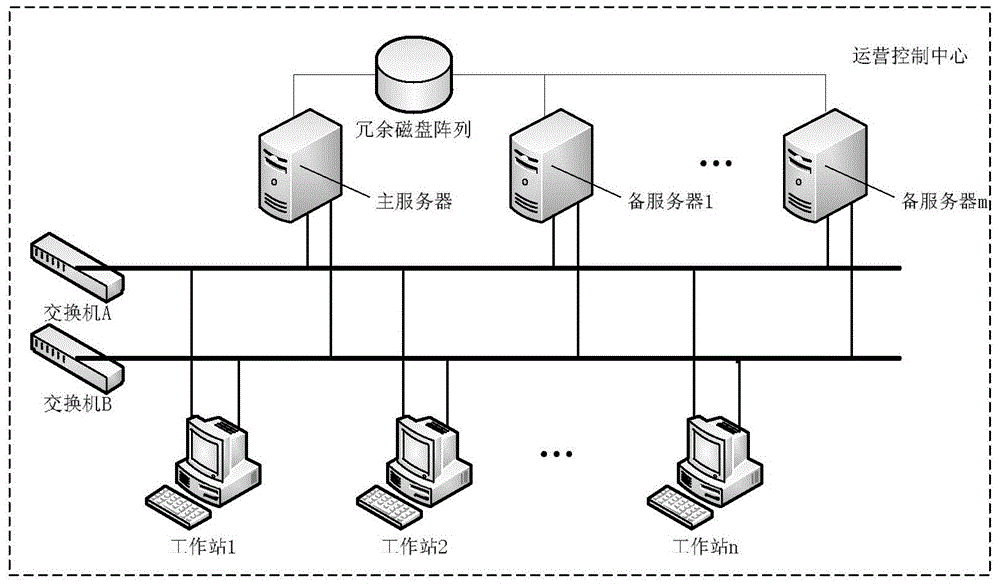

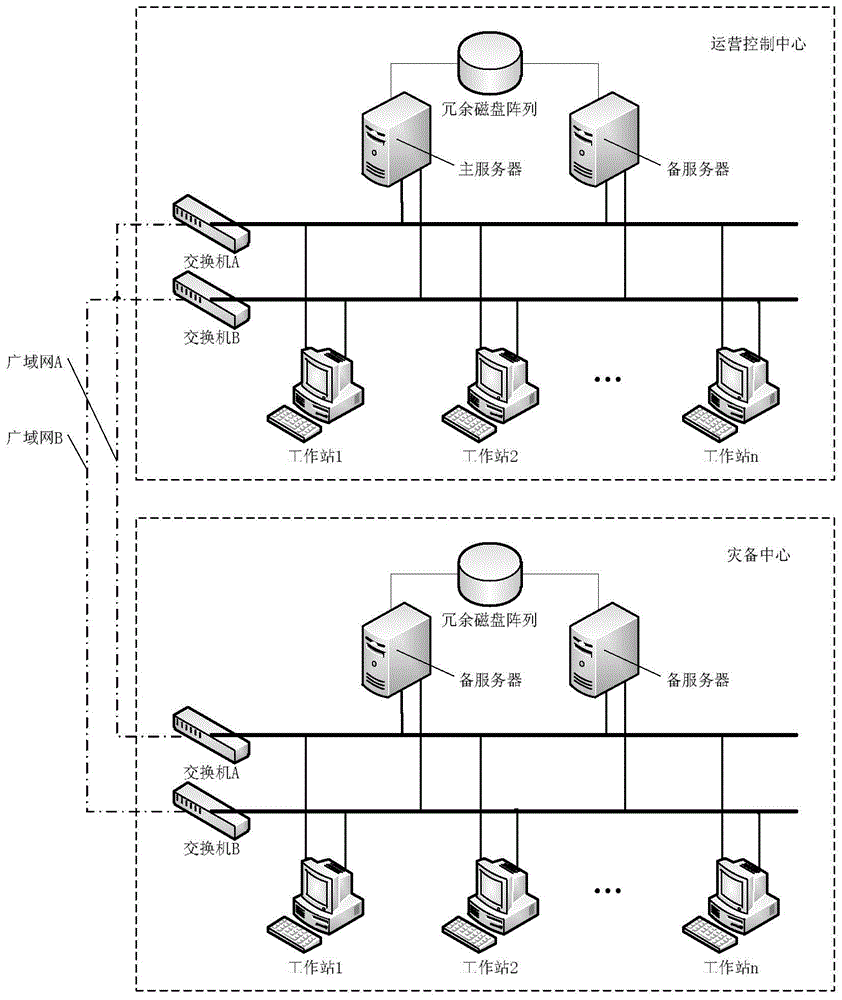

Distributed redundancy real-time database framework based on hybrid communication

ActiveCN103559104ATo achieve fault toleranceGuaranteed reliabilityTransmissionSpecial data processing applicationsData synchronizationFault tolerance

The invention discloses a distributed redundancy real-time database framework based on hybrid communication. According to the framework, aiming at the characteristics that in a rail traffic monitoring system, the data scale is huge, the monitoring data has the internal semantic association, a work station is mainly used for real-time data inquiry, and the like, various proper strategies are respectively adopted in various aspects of redundancy real-time database distribution and synchronization, fault tolerance and the like, data with different properties are respectively transmitted in real time through the hybrid use of unicast communication and multicast communication, and the problem of repaid increase of synchronous communication data volume caused by scale expansion and other problems are solved. The time sequence consistency requirement of the internal semantic association of monitoring data on the real-time database synchronization is met through adopting reasonable strategies, the fault tolerance in the distributed redundancy real-time database framework is effectively realized, and the redundancy of a distributed real-time database in the monitoring system is more effectively realized. Compared with an ordinary double-redundancy framework, the distributed redundancy real-time database framework has the advantages that the reliability and the availability of the real-time database is more powerfully ensured, and the foundation is laid for the stable operation of the rail traffic monitoring system.

Owner:南京国电南自轨道交通工程有限公司

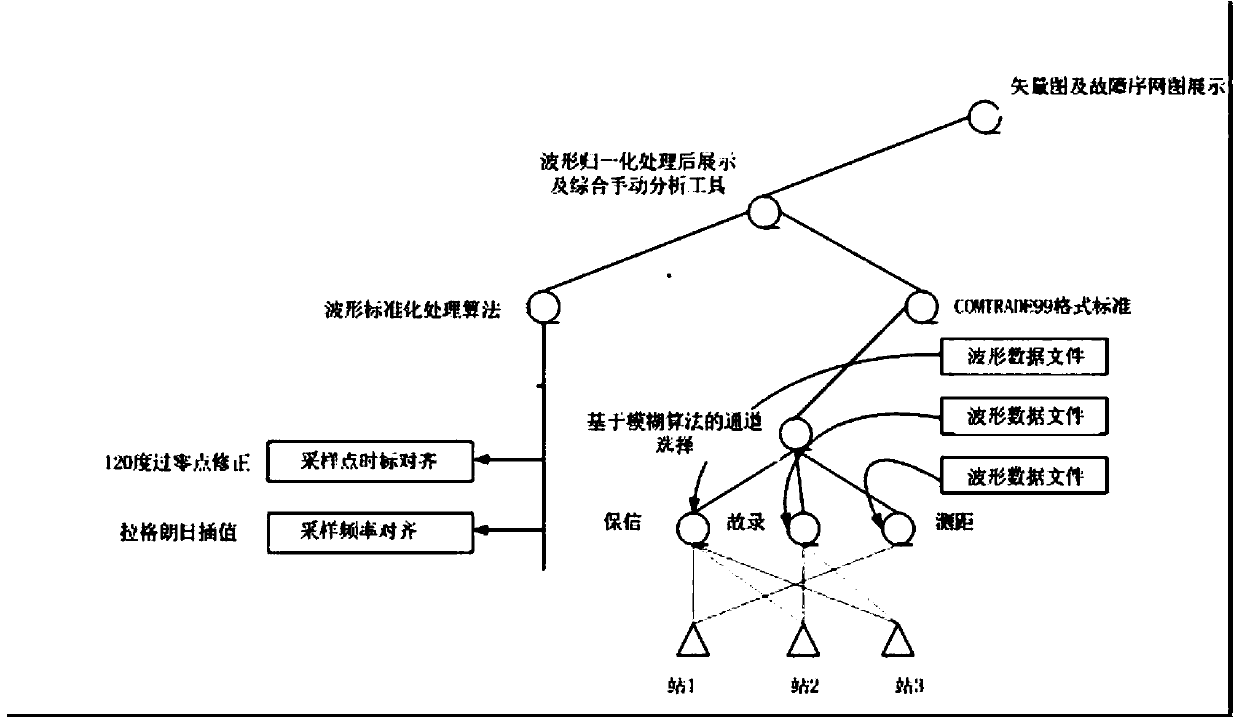

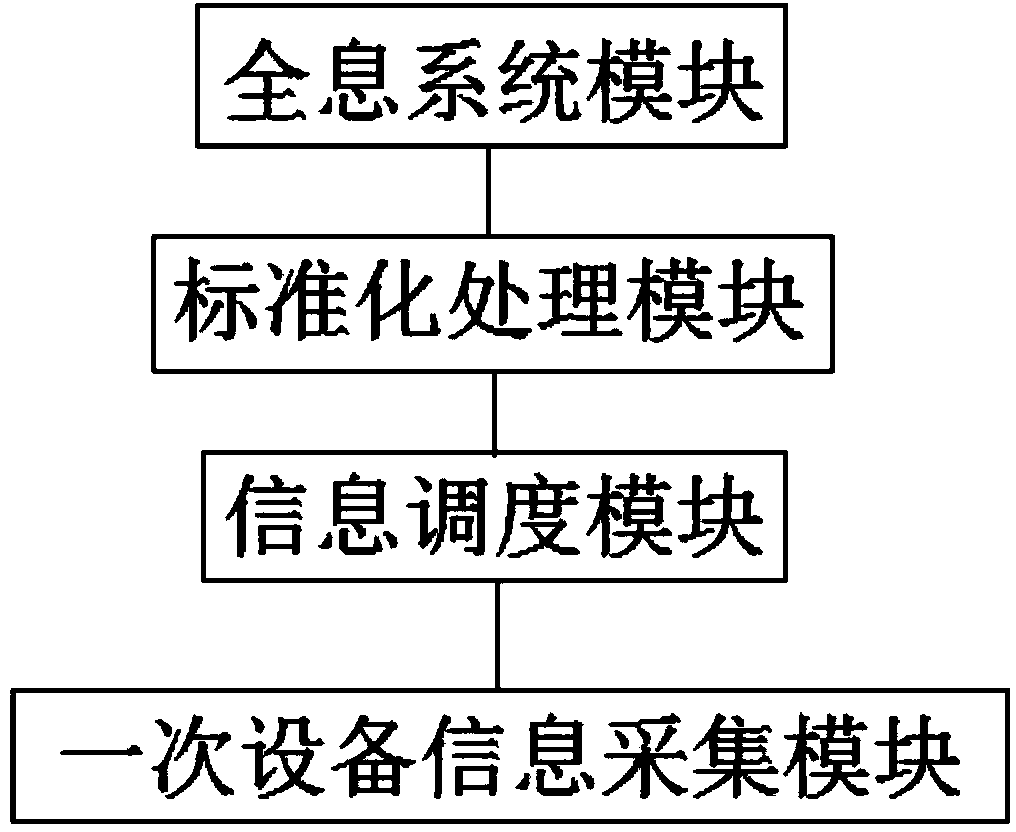

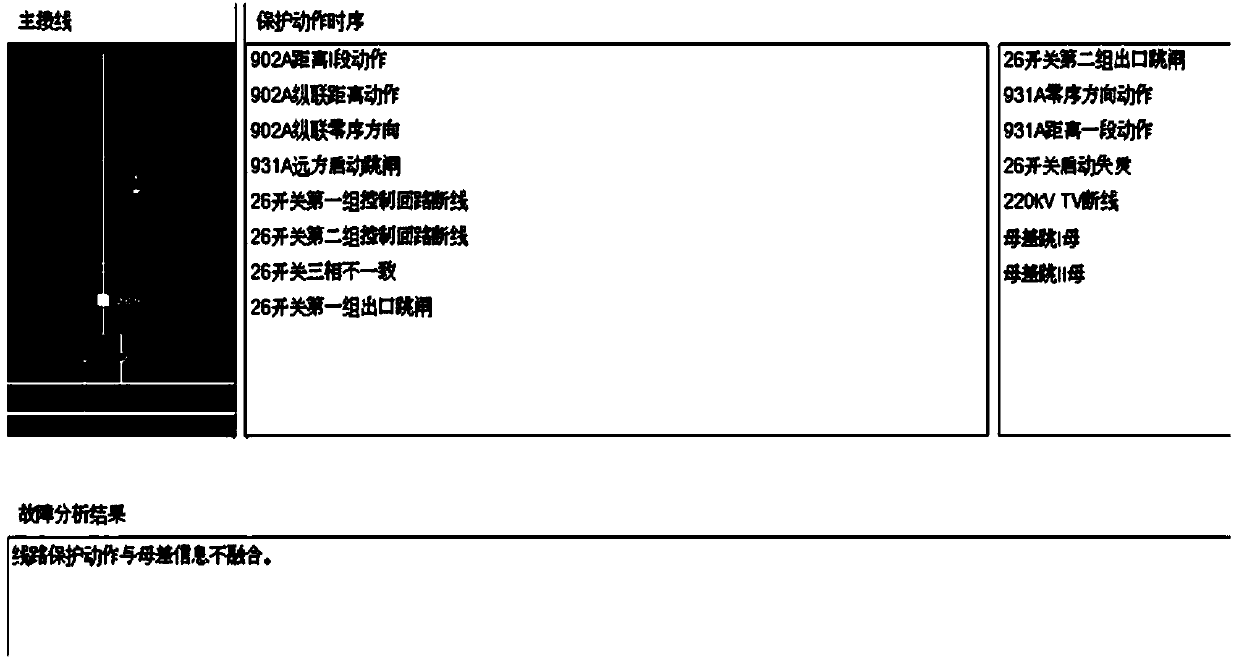

Fault hologram system based on standardization processing technology and method thereof

InactiveCN103812220AEffectively integrate different data informationTo achieve fault toleranceCircuit arrangementsInformation technology support systemProcess dynamicsData treatment

The invention discloses a fault hologram system based on standardization processing technology and a method thereof. The fault hologram system based on the standardization processing technology is used to widely, comprehensively, and synthetically display fault transient processes in a station from a perspective of fault increment reflection, facilitates timely and accurate fault condition understanding, scientifically analyzes fault reasons, rapidly judges occurring positions, natures and severity degrees of faults, and optimizes the power grid fault treatment process. The fault hologram system is developed by using data treatment techniques of data automation fusion and the like, is based on a multipoint region fault information synthesis analyzing thought after the faults, unifies and standardizes treatment methods through wave shapes, sampling point time scales and sampling frequency, achieves whole process dynamic display of data in different data sources on the same timer axis, uses booting logic based on combination of sampling characteristic value and switching value gallery attributes, automatically locks a fault sampling gallery, synthesizes the faults onto a fault analysis platform for normalization treatment, and improves fault treatment efficiency.

Owner:STATE GRID CORP OF CHINA +2

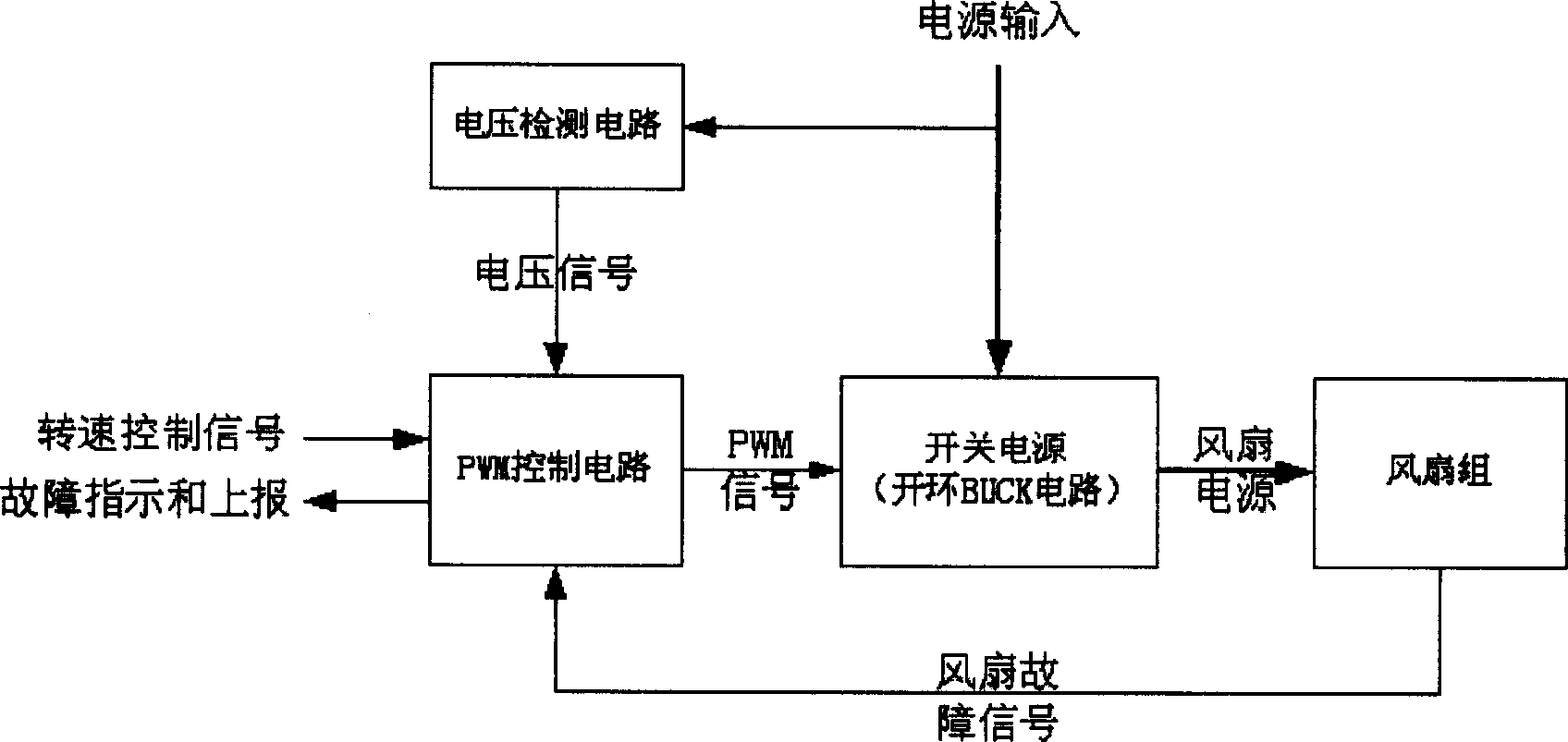

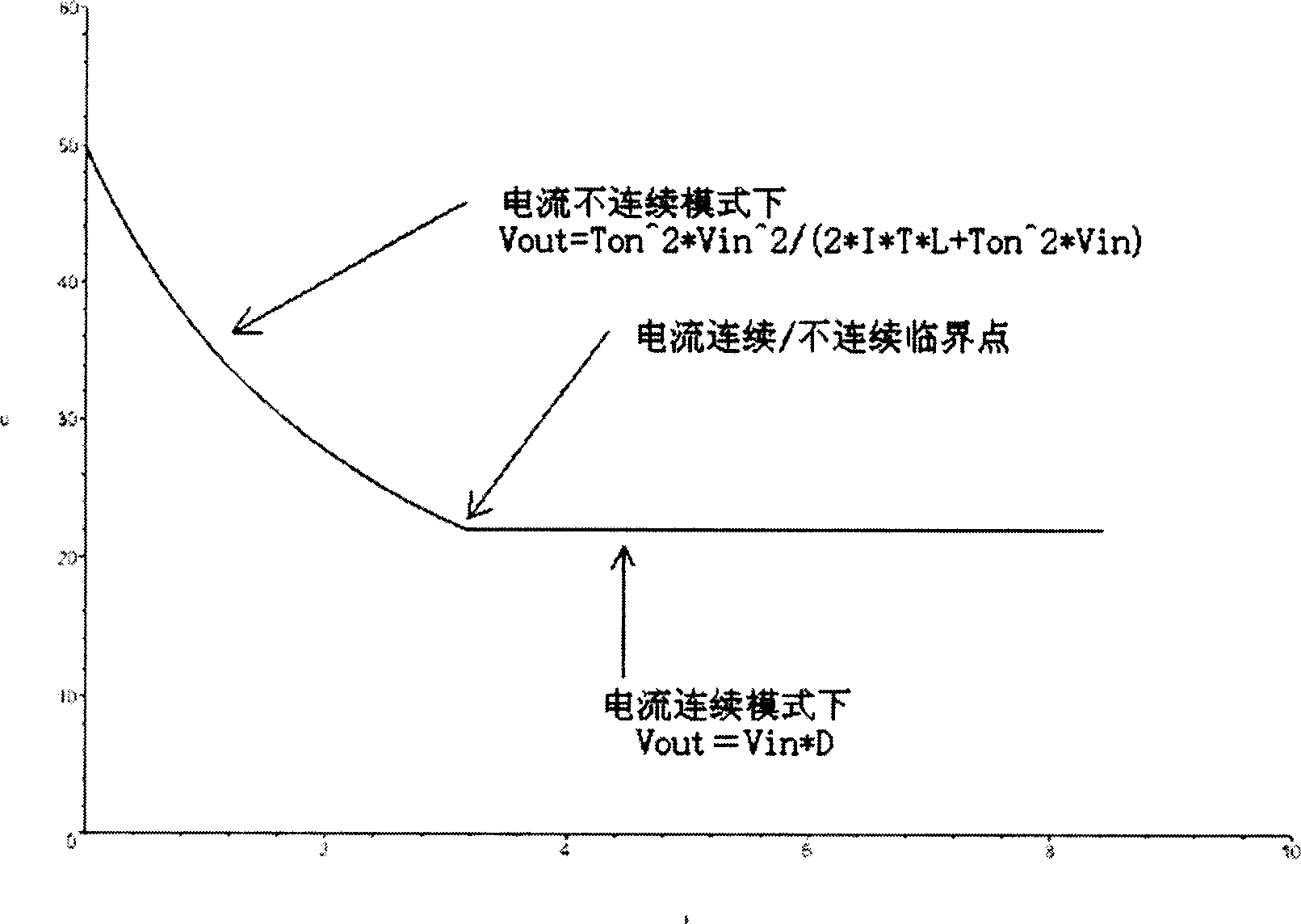

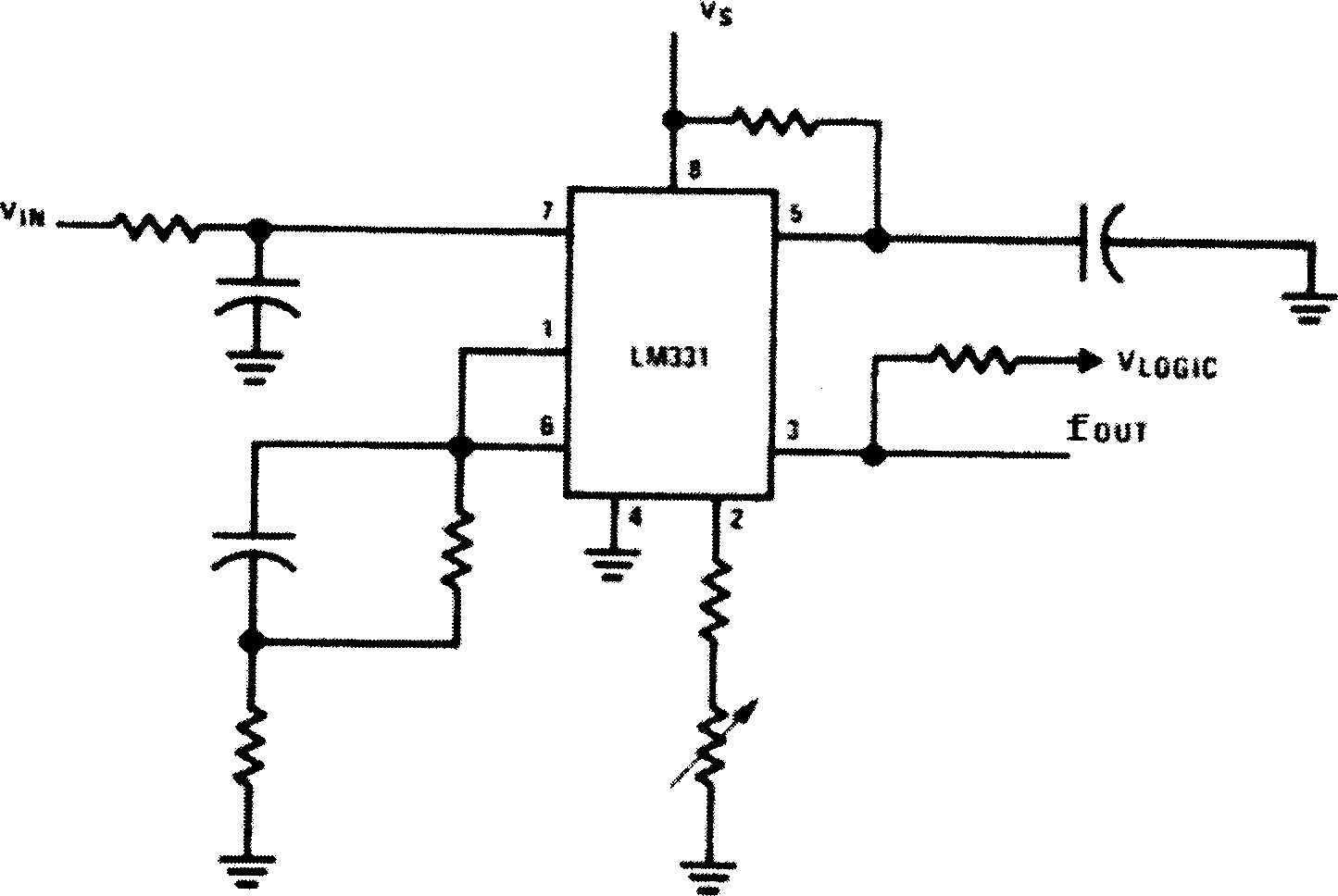

Speed regulating fan system with fault-tolerant capacity

ActiveCN1913334AReduce power consumptionReduce noiseElectric motor controlField or armature current controlElectricityControl signal

This invention relates to a fan regulation system with an error-tolerance ability including an input voltage testing circuit, a PWM circuit, a switch supply circuit and a fan set, in which, the control signal of rotation speed of the system and tested voltage signal control the output of the PWM waveforms, control the switch devices of a switch supply circuit and output a suitable voltage to the fan set, when the fan is tested to be faulty, the duty ratio of the PWm waveform can be adjusted.

Owner:ZTE CORP

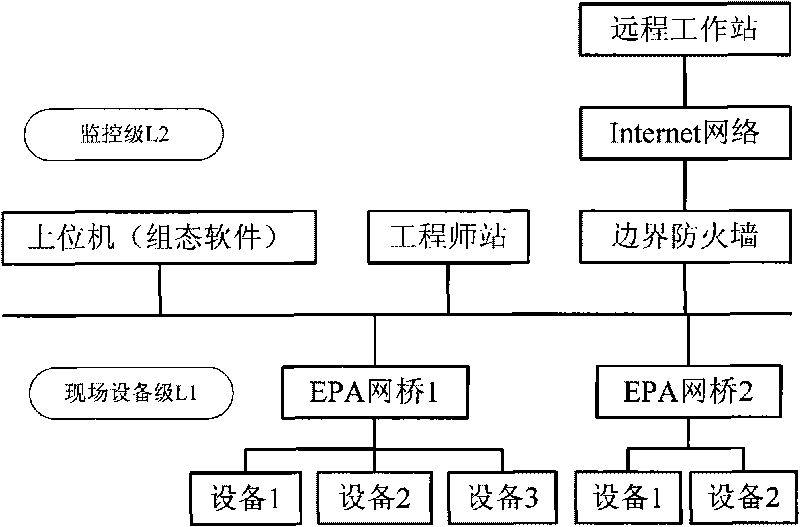

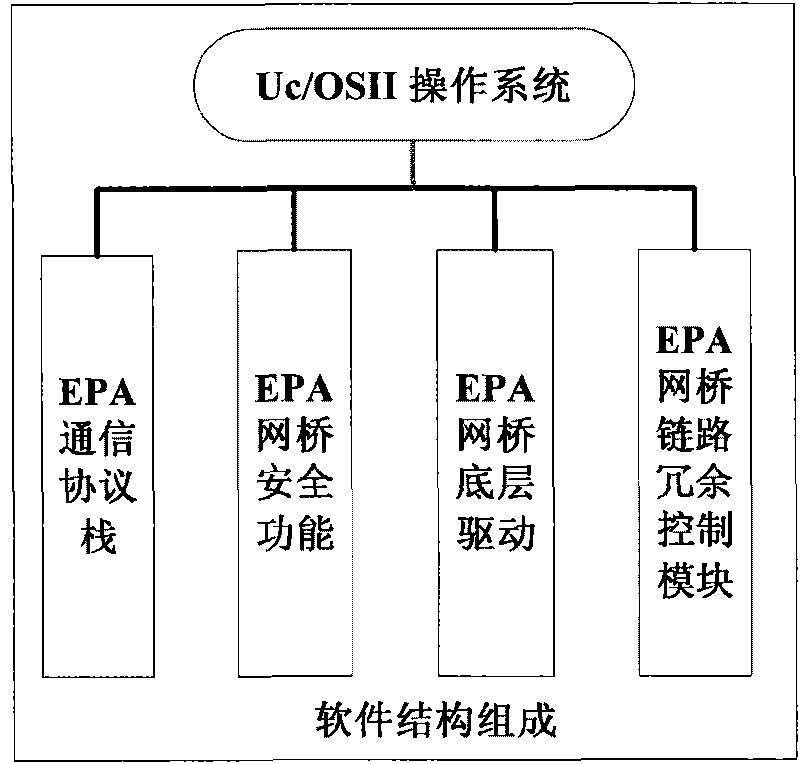

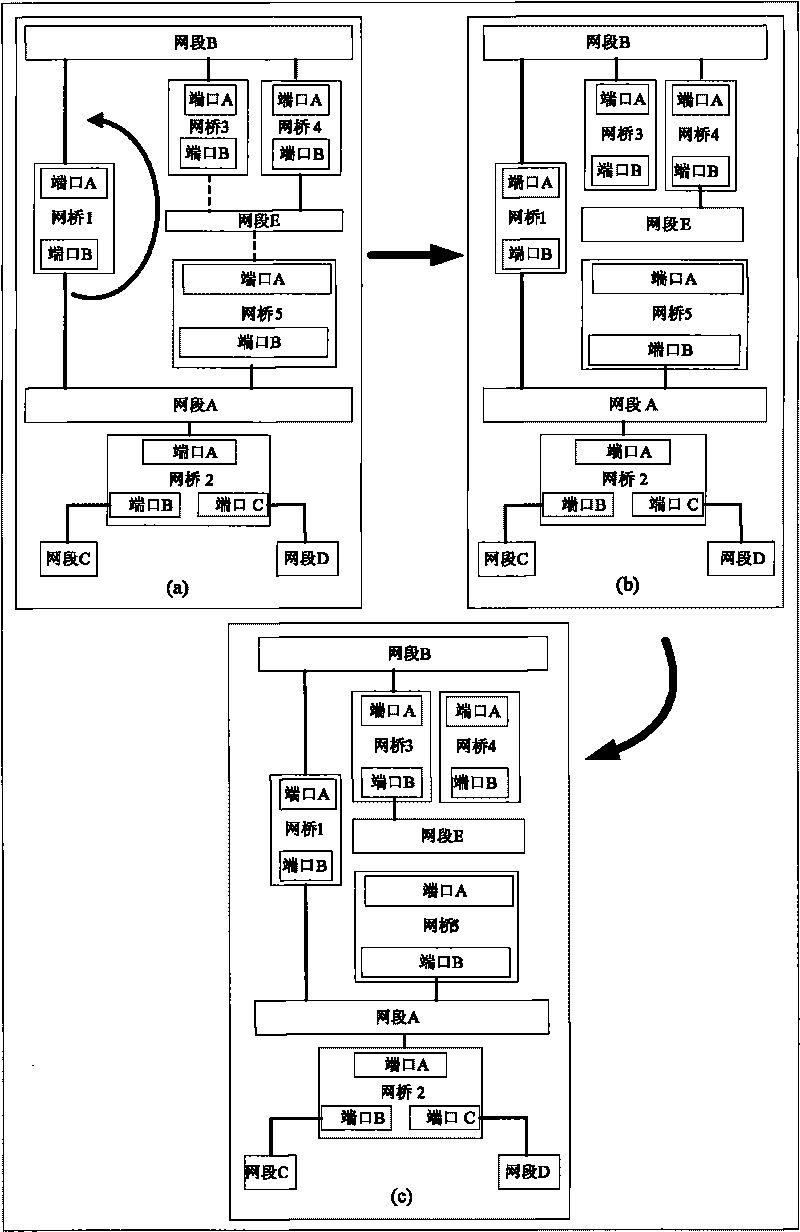

Link redundant control method based on EPA network bridge

ActiveCN101764706AImprove reliabilityReliable packet processing and forwardingError preventionData switching networksTelecommunications linkReal time data transmission

The invention seeks protection for a realizing method of link redundant control of an EPA network bridge and relates to the field of industrial field control. The invention realizes an EPA network link redundant function and a redundant managing function on the EPA network bridge. The method adopts an STP spanning tree algorithm to realize the link redundant function and to analyze network paths. If a loop exists in the network, the most robust link is selected as a communication link, the others are redundant backup links, a network bridge port which is connected with the redundant backup links in the loop is set to a blocking state, and the network is pruned to a non-loop tree topologic structure. The redundant link managing function provided by the invention uses an STP redundant managing protocol to manage the communication link automatically, thus improving the reliability, stability and robustness of the whole EPA network. The method is suitable for industrial Ethernet of high reliability and high real-time data transmission.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

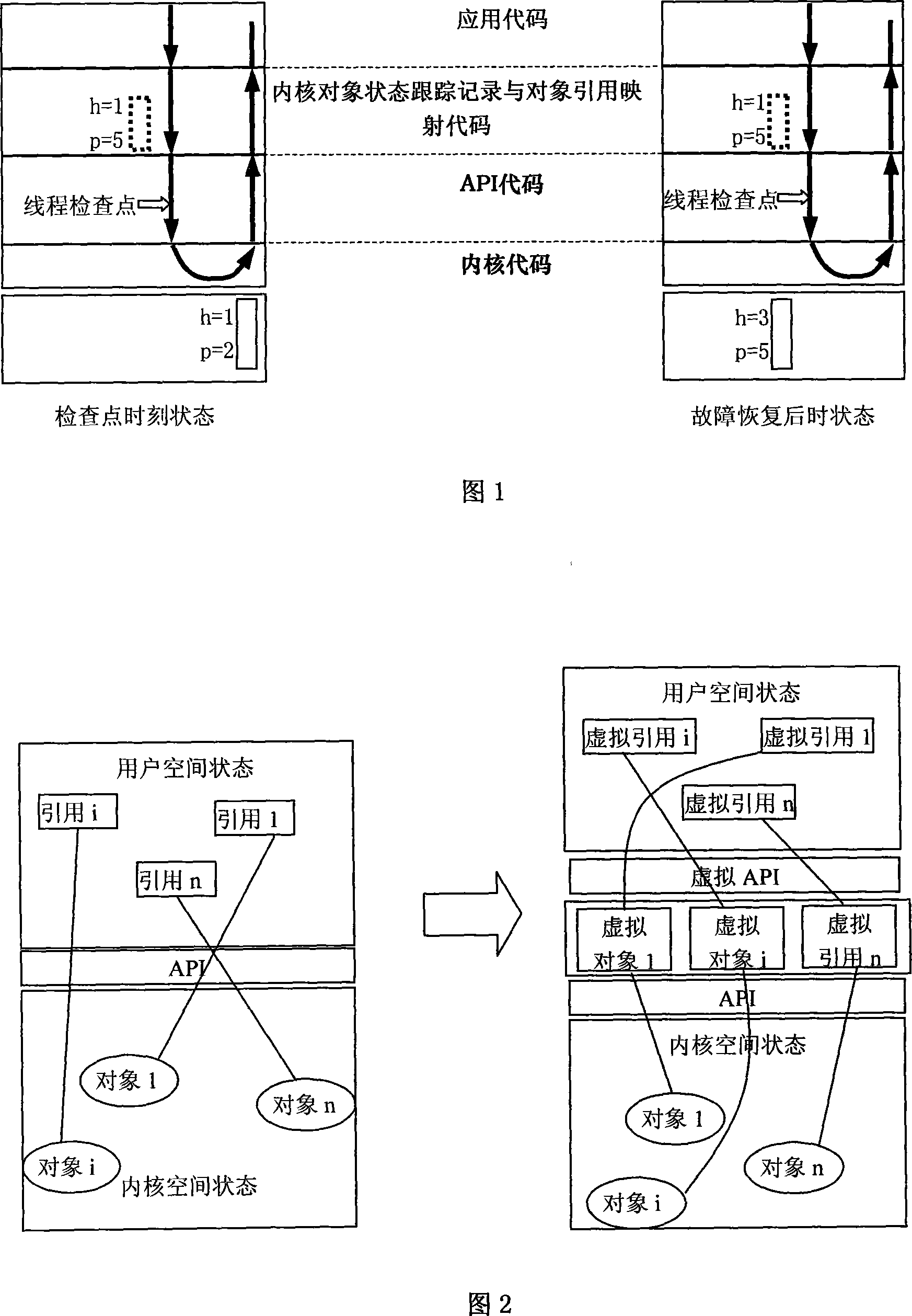

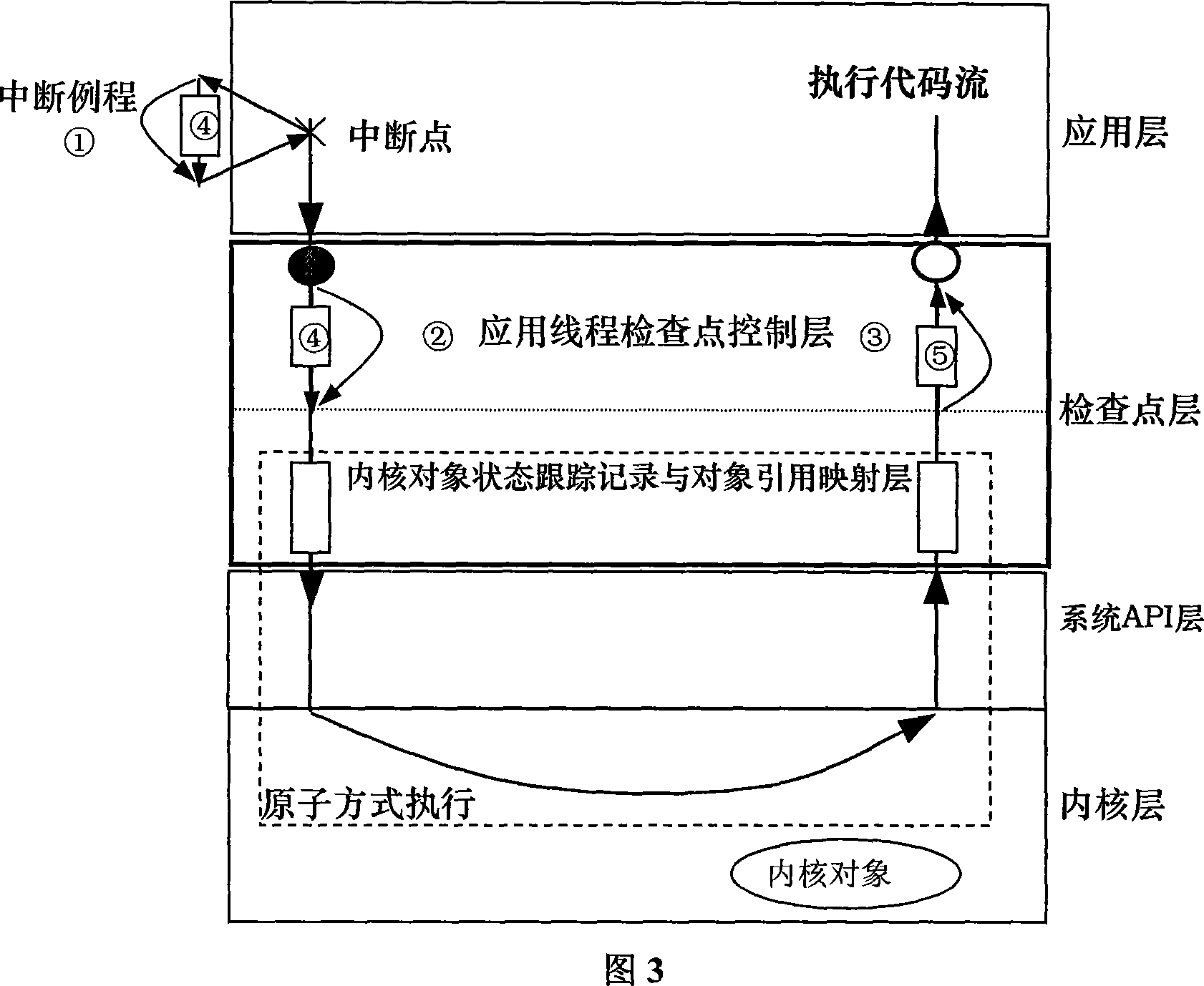

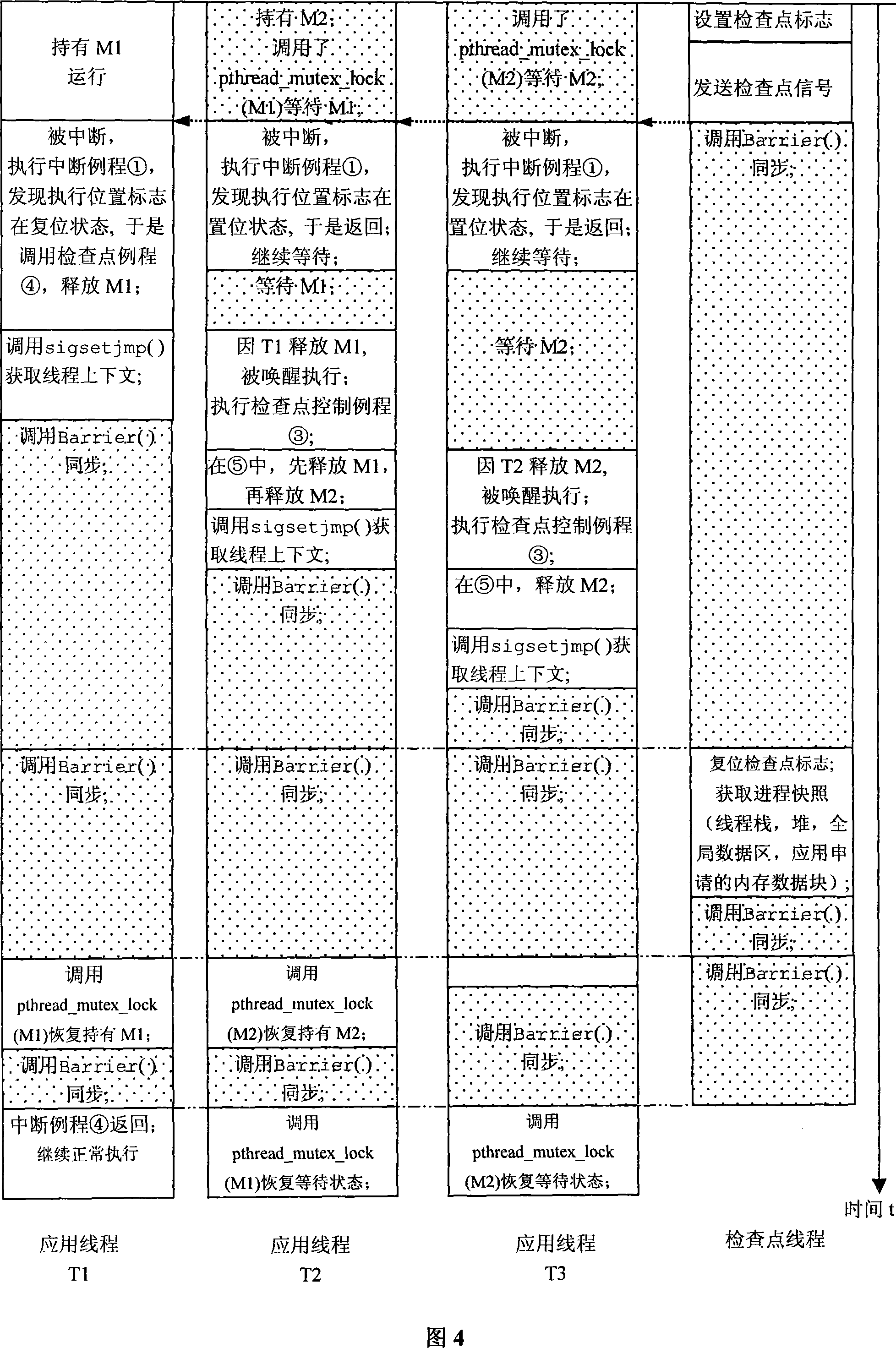

Method for implementing checkpoint of Linux program at user level based on virtual kernel object

InactiveCN101093453AImplement debugTo achieve load balancingMultiprogramming arrangementsSoftware testing/debuggingCheck pointControl layer

A method for realizing user grade of Linux program check point based on virtual kernel object includes inserting check point layer between application layer and system API layer, forming check point layer by application linear program check point control layer and mapping layer of kernel object state track-recording to object quotation, repositioning call of application layer on system APZ to check point layer, executing position flag on application linear program-setting, controlling check point of application linear program not to be dropped into said mapping layer and system API layer as well as kernel layer.

Owner:HUNAN UNIV

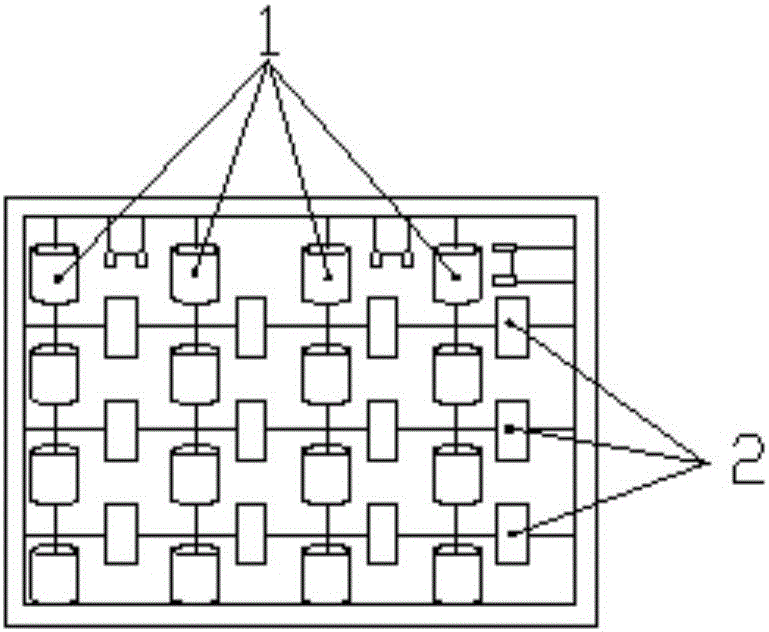

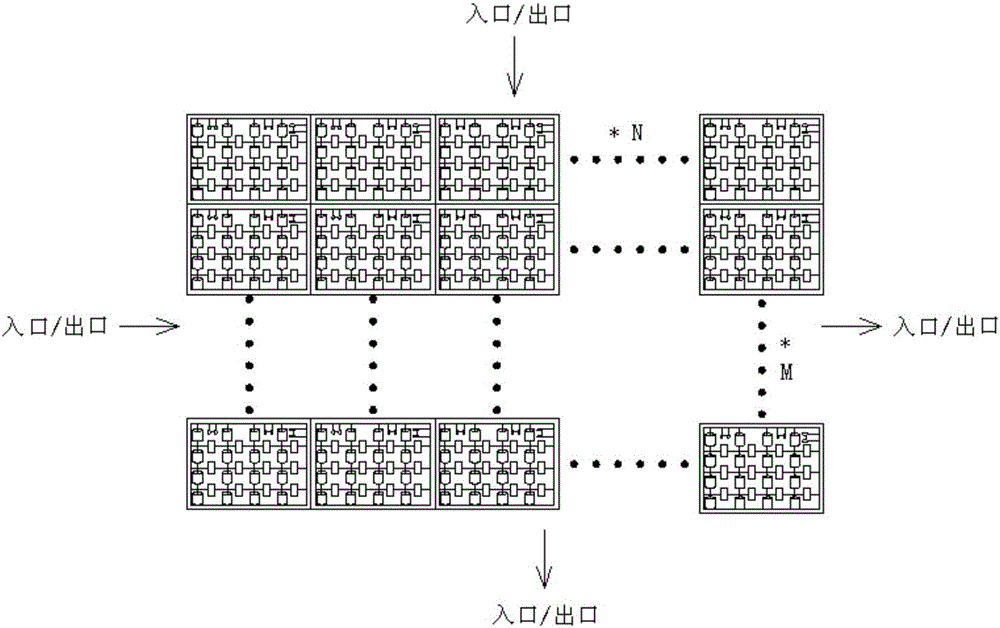

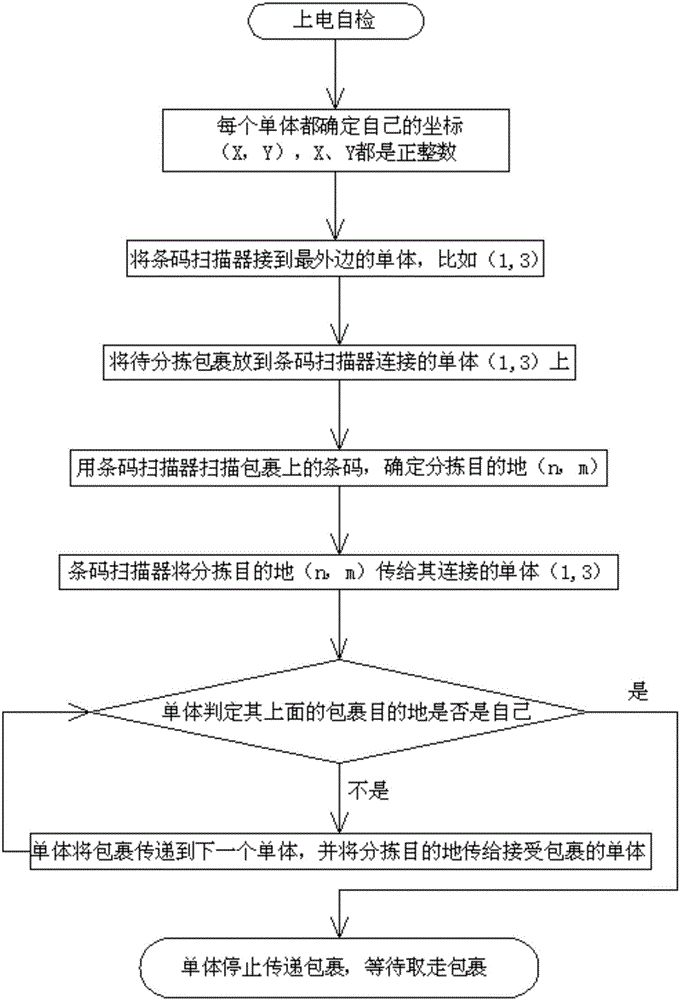

Array logistics automatic sorting equipment and working method thereof

PendingCN106733678ALower requirementIncrease flexibilitySortingCommunication interfaceLogistics management

The invention discloses array logistics automatic sorting equipment and a working method thereof. The sorting equipment comprises multiple sorting monomers arranged in an array form; the adjacent sorting monomers realize connection and communication through communication interfaces; the sorting monomers include main bodies and controllers; the main bodies are provided with moving devices for driving packages to move; the controllers are connected with the moving devices, and are used for receiving sorting instructions and controlling actions of the moving devices according to the sorting instructions; and the controllers of the adjacent sorting monomers can realize data transmission to transfer the sorting instructions. The invention further discloses the working method of the sorting equipment. The sorting equipment and the working method thereof can realize multi-point loading and multi-point sorting identification, improves the sorting efficiency, is convenient to expand, and is low in field requirement.

Owner:SF TECH

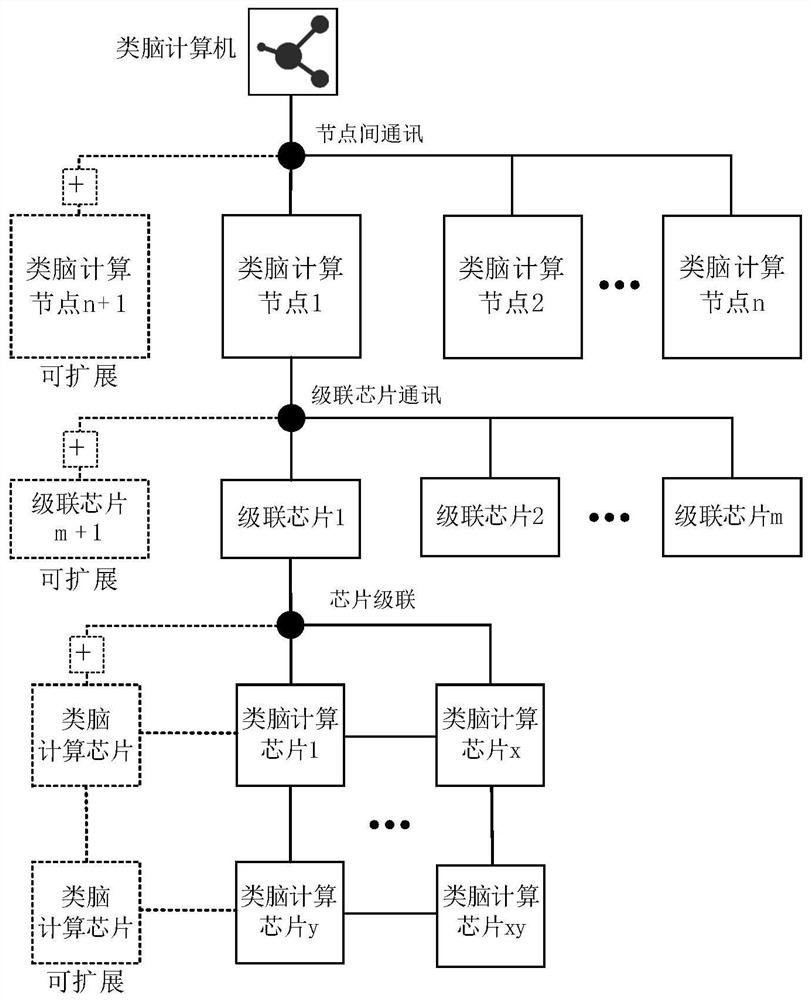

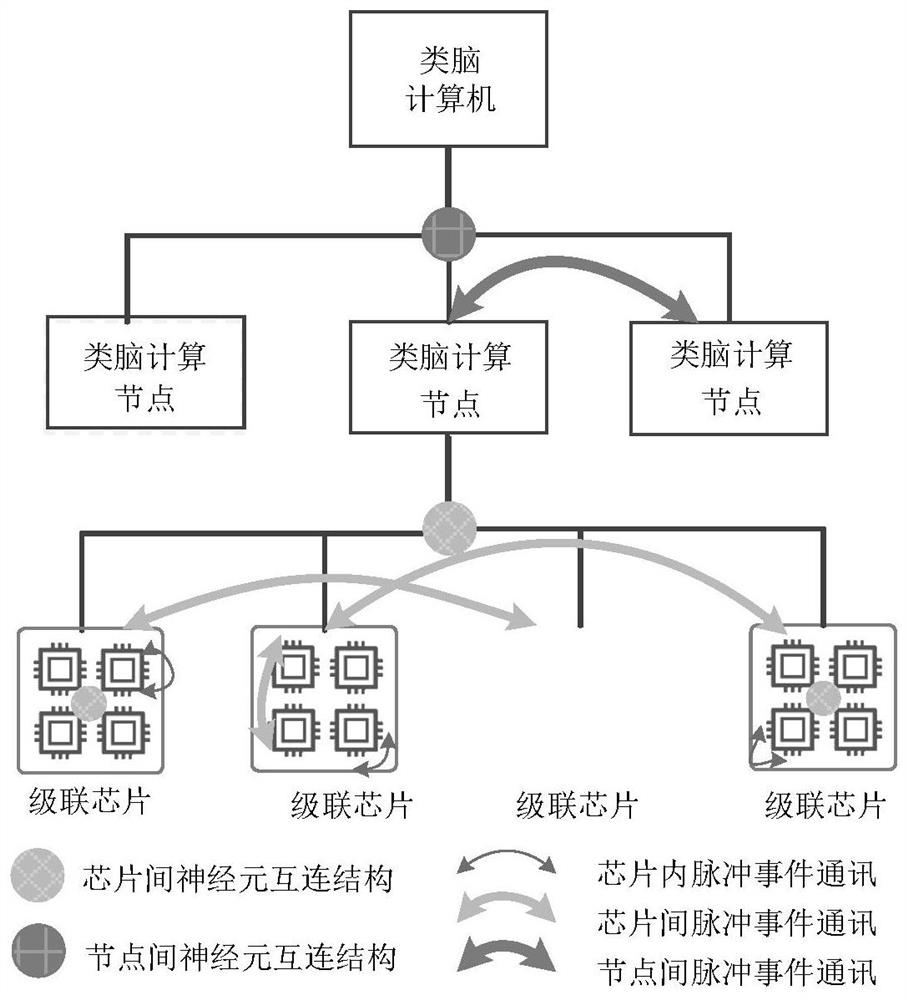

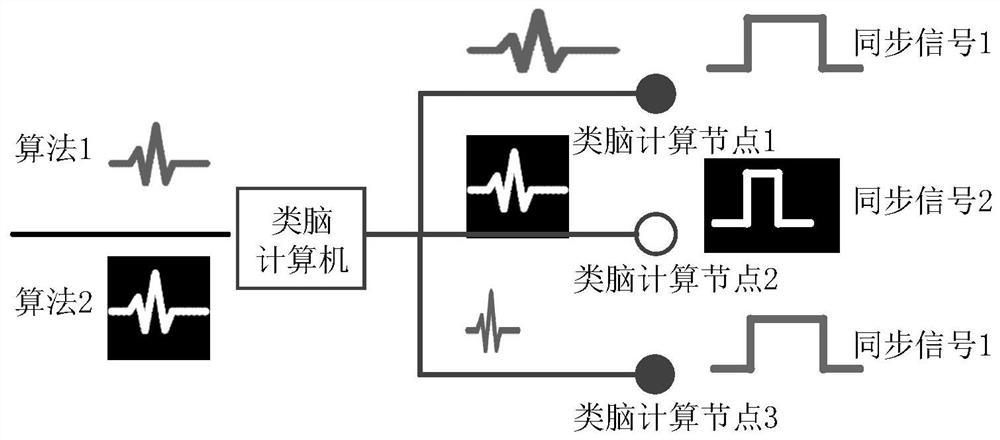

Brain-like computer supporting hundred million neurons

ActiveCN112270407ATo achieve fault toleranceRealize inferential computingEnergy efficient computingPhysical realisationFault toleranceComputer architecture

The invention discloses a brain-like computer supporting hundred million neurons. The brain-like computer comprises a hierarchical expansion system architecture and system architecture internal calculation process control. The system architecture comprises a plurality of brain-like computing chips which are managed in a hierarchical organization mode and used for achieving computing tasks, each brain-like computing chip comprises computing neurons and synaptic resources and forms a neural network, and pulse events among the computing neurons in the system architecture are transmitted in a hierarchical transmission mode; the calculation process control comprises parallel processing of calculation tasks in the control system architecture, management of synchronization time in the control system architecture and reconstruction of the neural network in the control system architecture to realize fault tolerance and robustness management of calculation neurons and synaptic resources. The brain-like computer can support hundreds of millions of spiking neural network reasoning calculation of the neuron scale.

Owner:ZHEJIANG UNIV

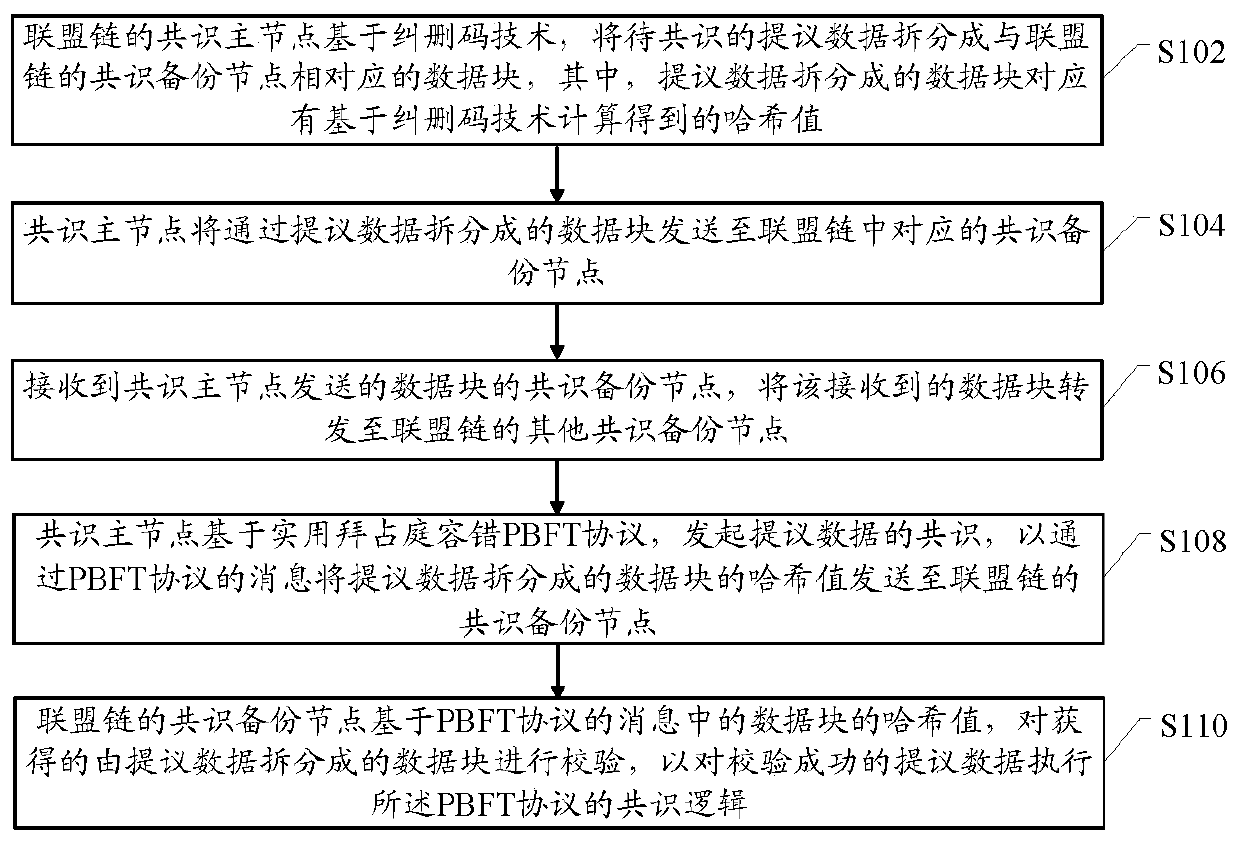

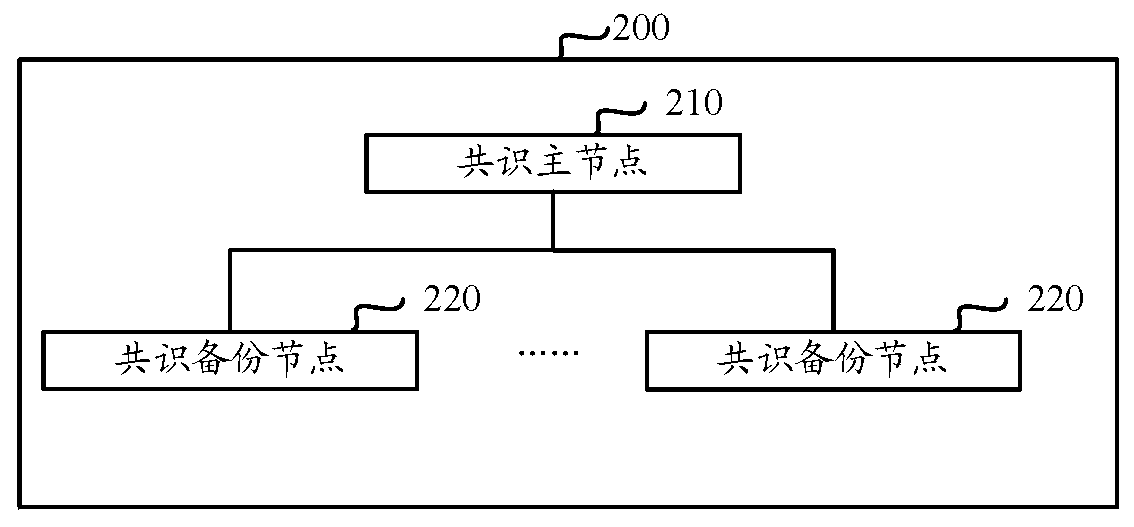

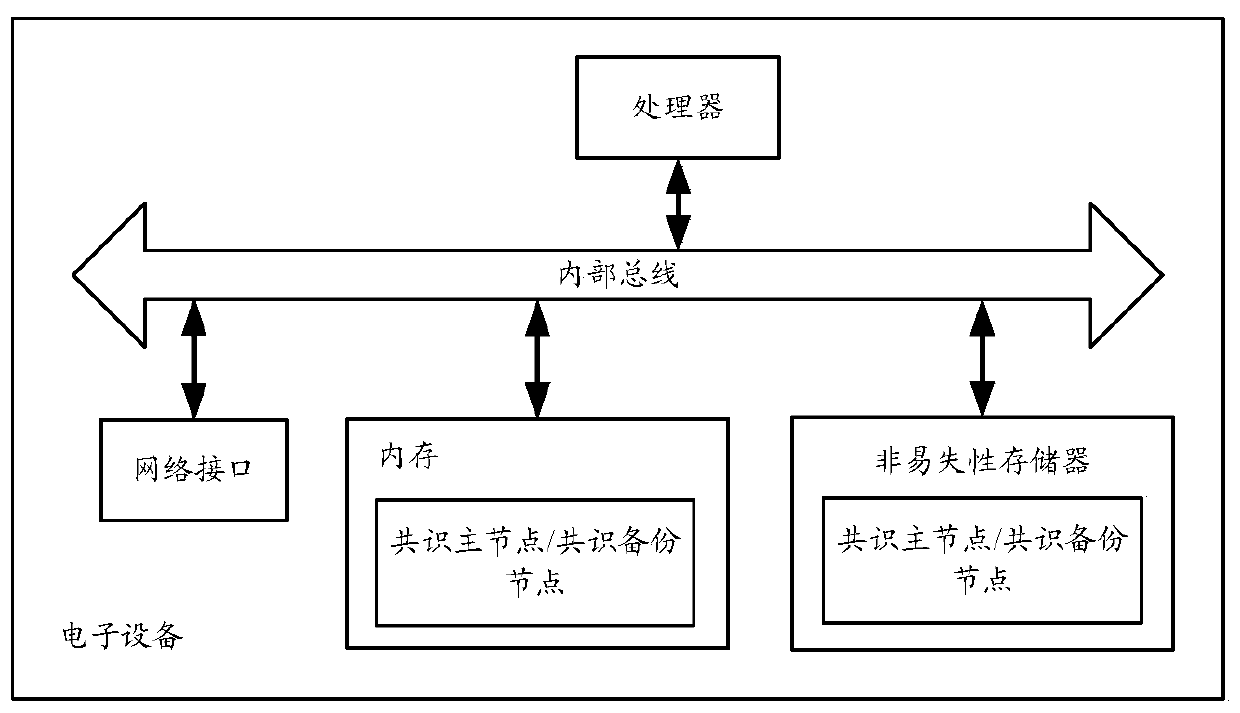

Alliance chain consensus method and alliance chain system

ActiveCN111526219ATo achieve fault toleranceAvoid uploadingUser identity/authority verificationForward error control useVIA protocolConsensus method

The embodiment of the invention provides an alliance chain consensus method and an alliance chain system. The method comprises the steps that a consensus main node splits proposed data to be consensusinto data blocks corresponding to consensus backup nodes based on an erasure code technology, and the data blocks split from the proposed data correspond to hash values obtained through calculation based on the erasure code technology; the consensus master node sends the data blocks split by the proposed data to the corresponding consensus backup nodes, receives the consensus backup node of the data block sent by the consensus main node, and forwards the data block to other consensus backup nodes; the consensus master node initiates consensus of the proposed data based on a practical Byzantine fault-tolerant PBFT protocol so as to send hash values of data blocks obtained by splitting the proposed data to the consensus backup node through a message of the PBFT protocol; the consensus backup node verifies the obtained data blocks split by the proposed data based on the hash values of the data blocks in the message of the PBFT protocol so as to execute the consensus logic of the PBFT protocol on the proposed data which is successfully verified.

Owner:ALIPAY (HANGZHOU) INFORMATION TECH CO LTD

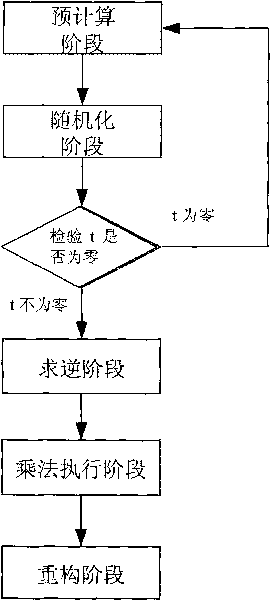

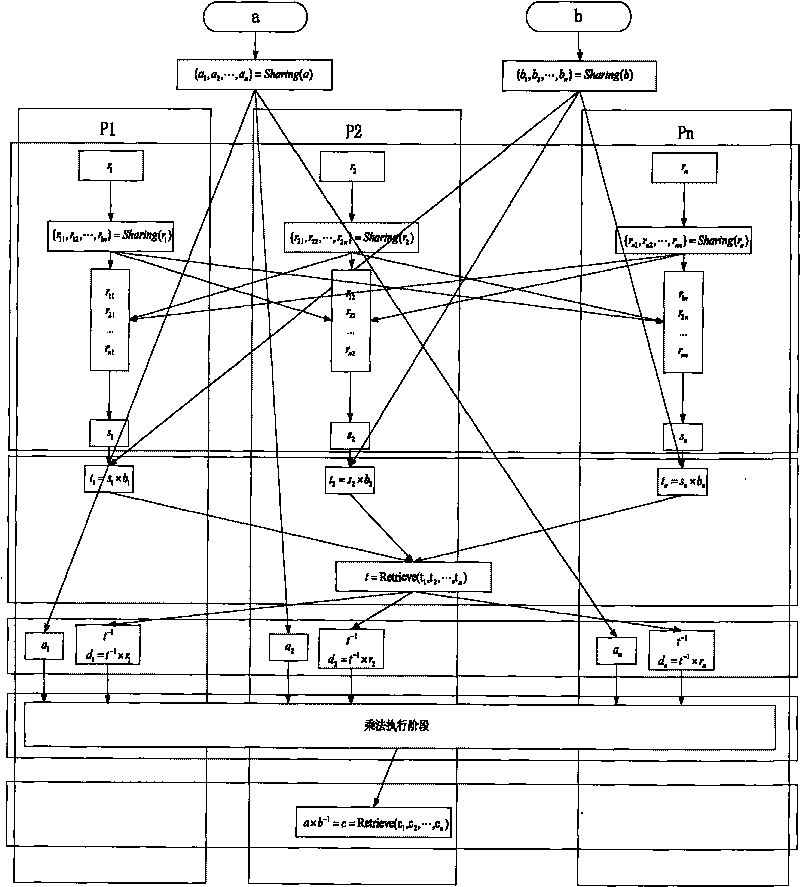

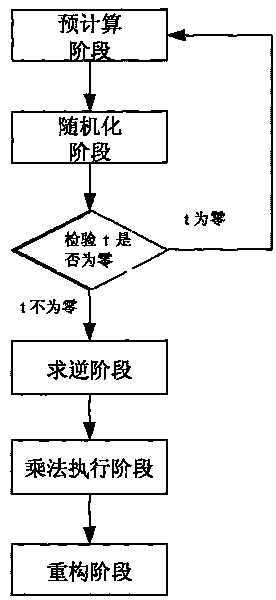

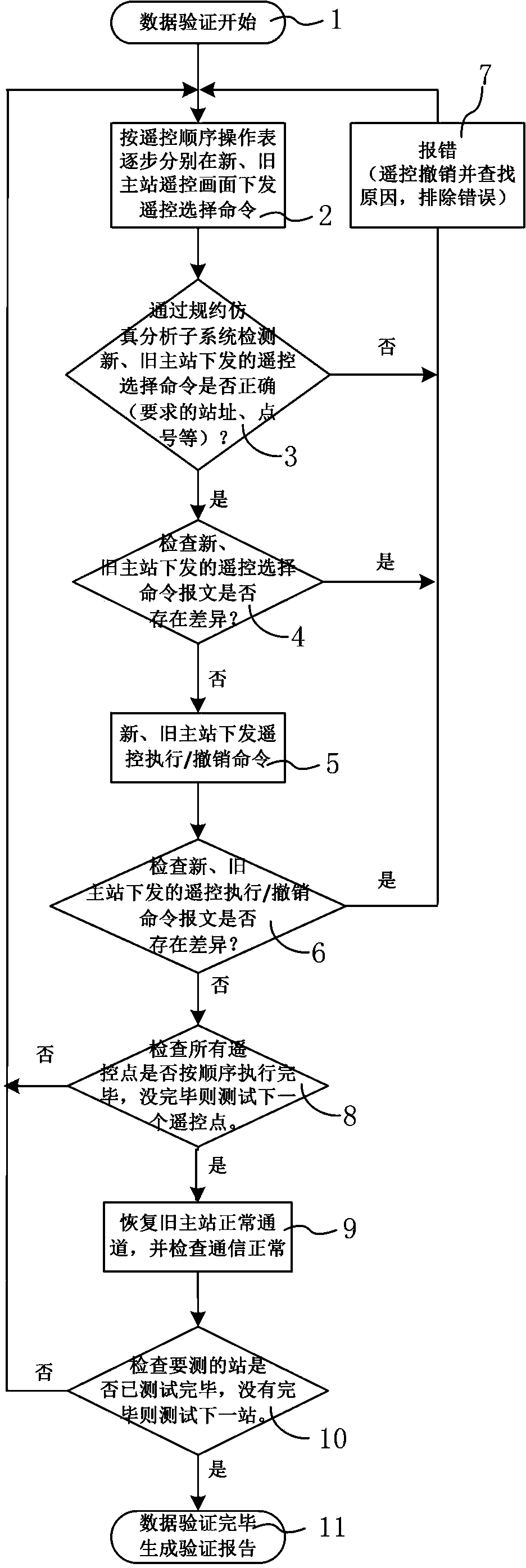

Construction method of division protocol based on cryptology in distributed computation

InactiveCN101729554AEasy to implementReduce computational complexityKey distribution for secure communicationFault toleranceCipher

The invention discloses a construction method of a division protocol based on cryptology in distributed computation, belonging to the field of information safety. The formation method is characterized in that (1) each member who participates in the computation dependently selects a random number and sends the shared value of the random number to all parties for local hybrid operation so as to obtain a public random shared value; (2) each member randomizes the sharing of an input secret value b by using the public random shared value and reconstructs the randomizing value of the secret value btogether; (3) each member inspects whether a randomizing result of the secret value b is inverse or not, if so, the member solves an inverse element of the randomizing value of the secret value b andthen de-randomizes the inverse element to obtain the inverse sharing of the secret value b by utilizing the public random shared value; (4) each member utilizes the obtained inverse sharing of the secret value b and a sharing executive multiplication protocol of a secret value a to obtain the sharing of the a / b; and (5) each member reconstructs a real computing result by mutually exchanging the obtained sharing of the a / b. The invention has the characteristics of high efficiency, fault tolerance and safety.

Owner:PEKING UNIV

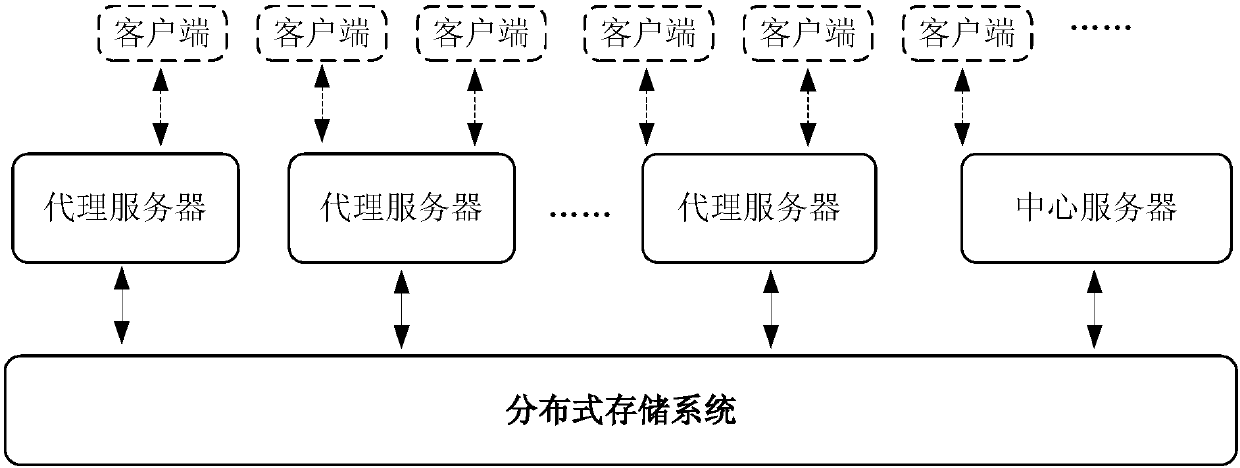

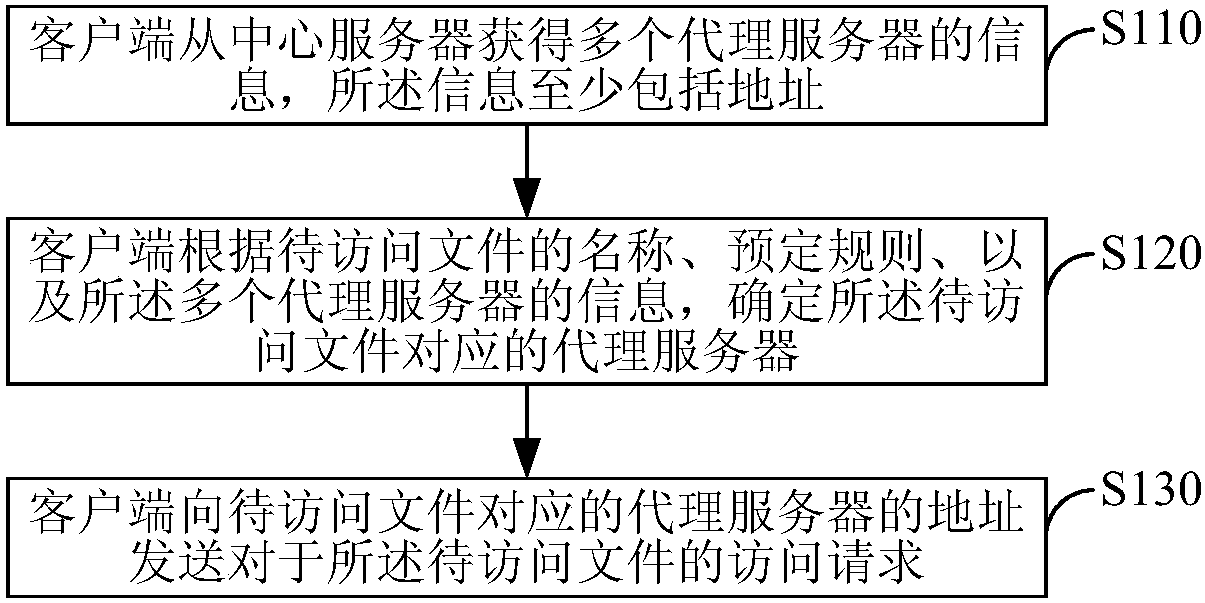

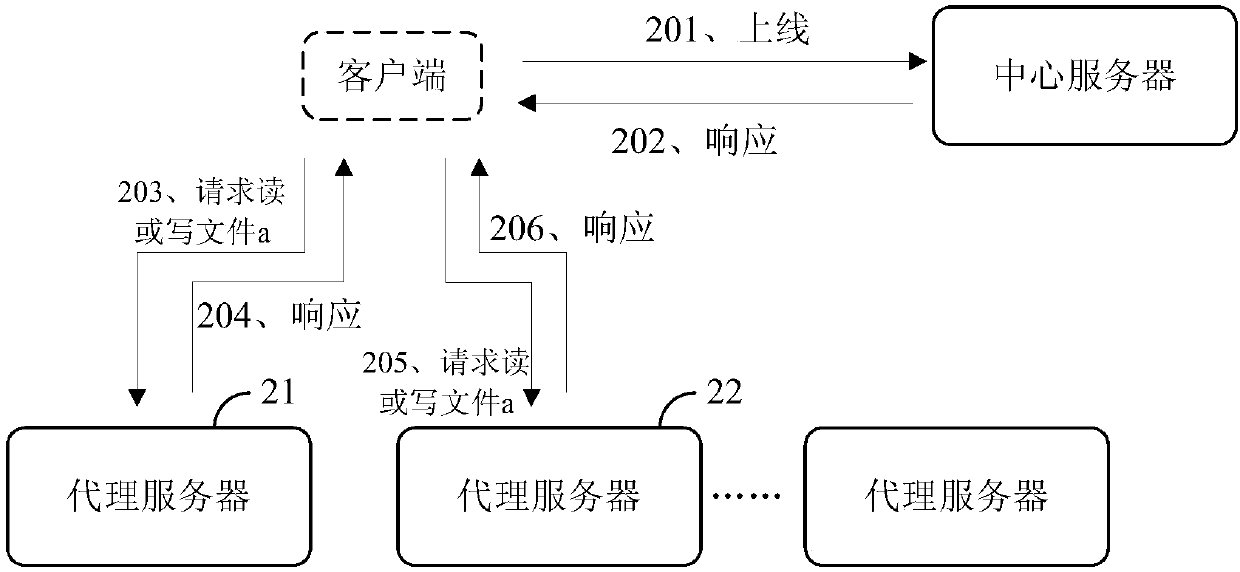

File access method, device and system and electronic equipment

ActiveCN107920101ARelieve pressureReduce access latencyTransmissionSpecial data processing applicationsAccess methodClient-side

The invention discloses a file access method, device and system and electronic equipment. The method is used in a system which comprises at least one central server, at least one client, and a plurality of proxy servers. The method comprises the steps that the client obtains the information of the proxy servers from the central server; the client determines the proxy server corresponding to a to-be-visited file according to the name of the to-be-visited file, predetermined rules and the information of the proxy servers; the client transmits an access request of the to-be-visited file to the proxy server corresponding to the to-be-visited file. The method can alleviate the pressure on the central server, and improves the access efficiency of a distributed storage system.

Owner:ALIBABA GRP HLDG LTD

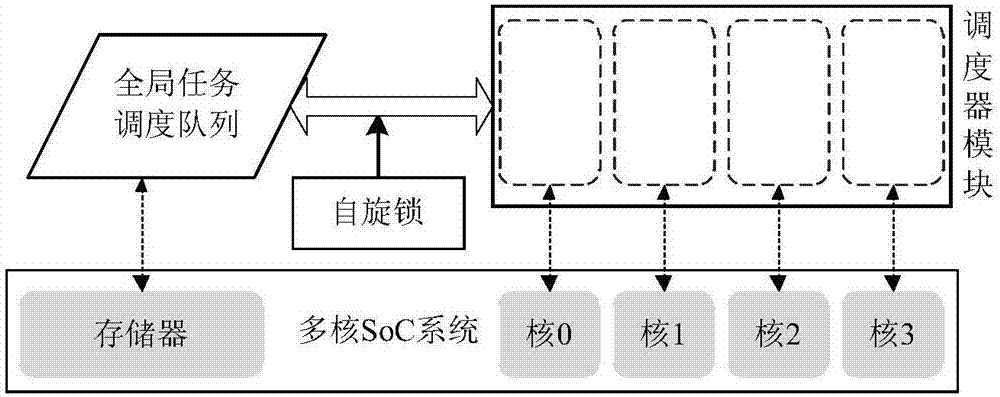

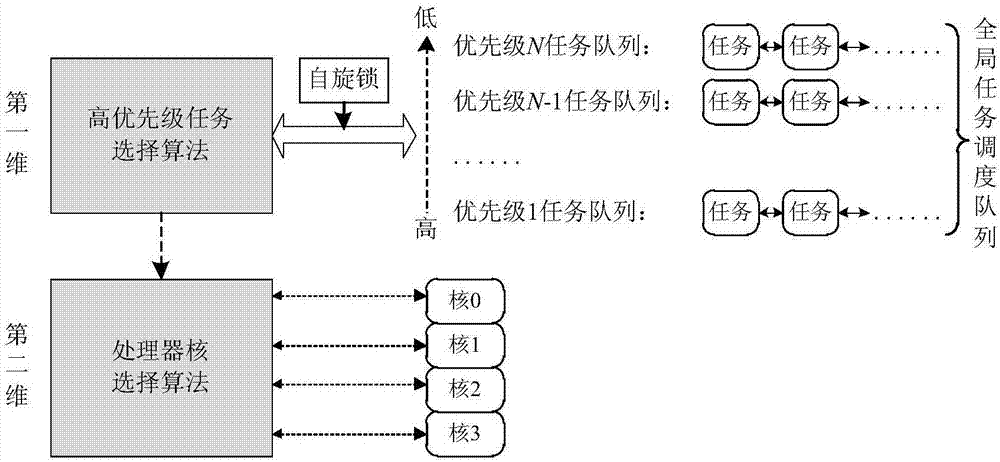

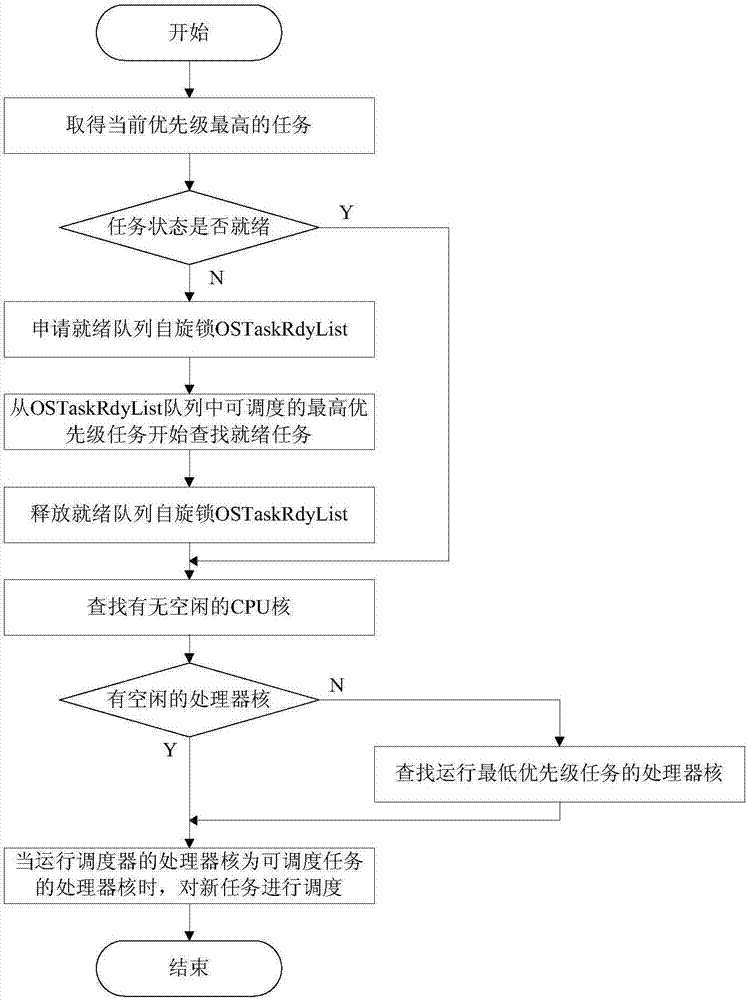

Parallel scheduling method for satellite-borne multi-core SoC (System on a Chip) task-level load balance

ActiveCN107463442AImprove performanceAvoid inconsistenciesResource allocationParallel computingSpin locks

The invention puts forward a parallel scheduling method for satellite-borne multi-core SoC (System on a Chip) task-level load balance. The method comprises the following steps that: a multi-core TCB (Task Control Block) is taken as a node to construct a global task scheduling queue; when a scheduler module is initialized, four idle tasks with a lowest priority are created and are added into a global task scheduling queue OSTaskRdyList; the scheduler module is operated in parallel on a plurality of processor cores of the multi-core SoC system; the scheduler module adopts a spin lock to access the global task scheduling queue OSTaskRdyList, and a task T1 with a highest current priority is obtained from the global task scheduling queue OSTaskRdyList; and the scheduler module searches an idle processor core or operates the processor core of the task of the lowest priority, and the task with the highest priority is scheduled to the processor core. By use of the method, the problem that multiple tasks are subjected to balanced distribution and parallel operation on the multi-core SoC is solved, and the calculating and processing efficiency of the multi-core SoC is drastically improved.

Owner:BEIJING INST OF CONTROL ENG

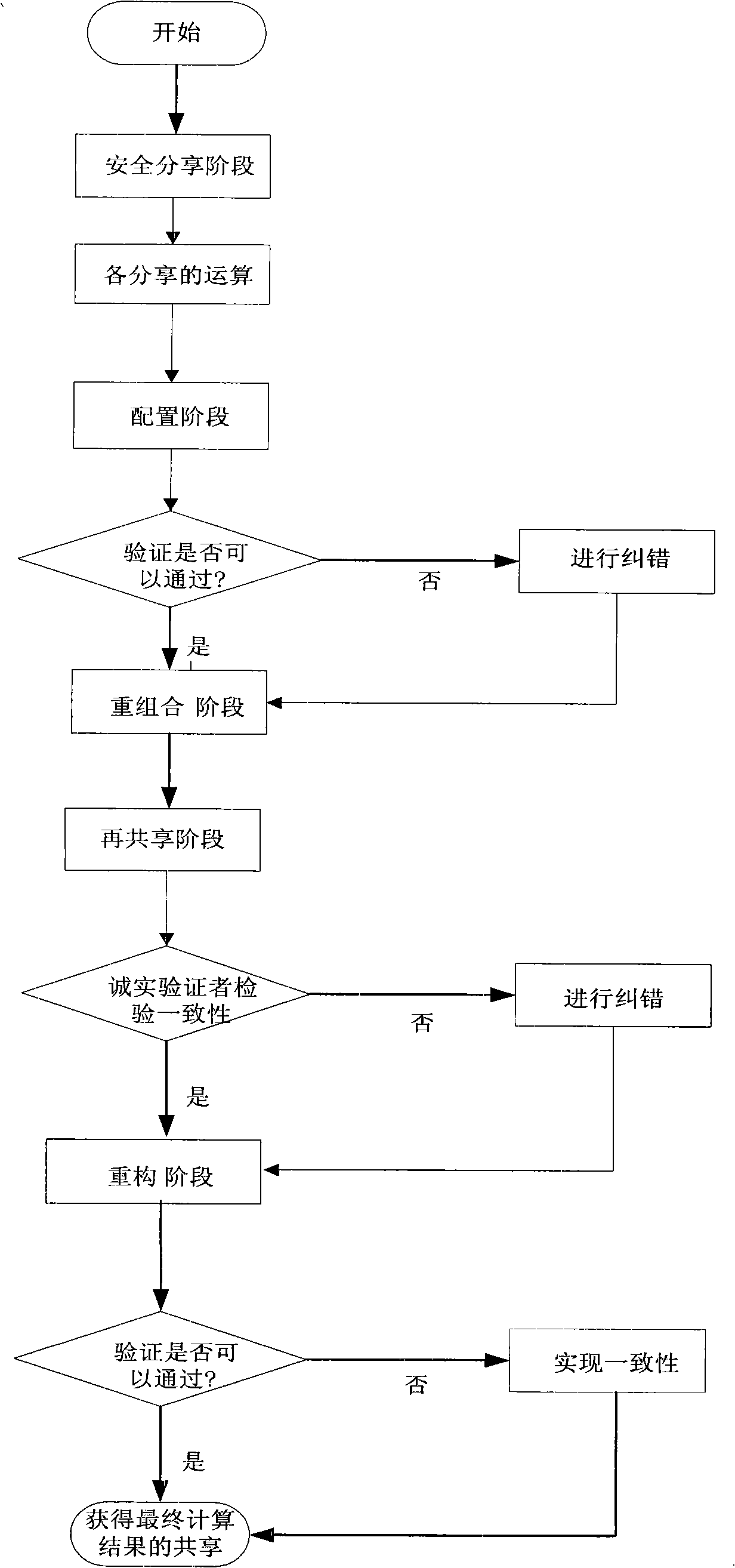

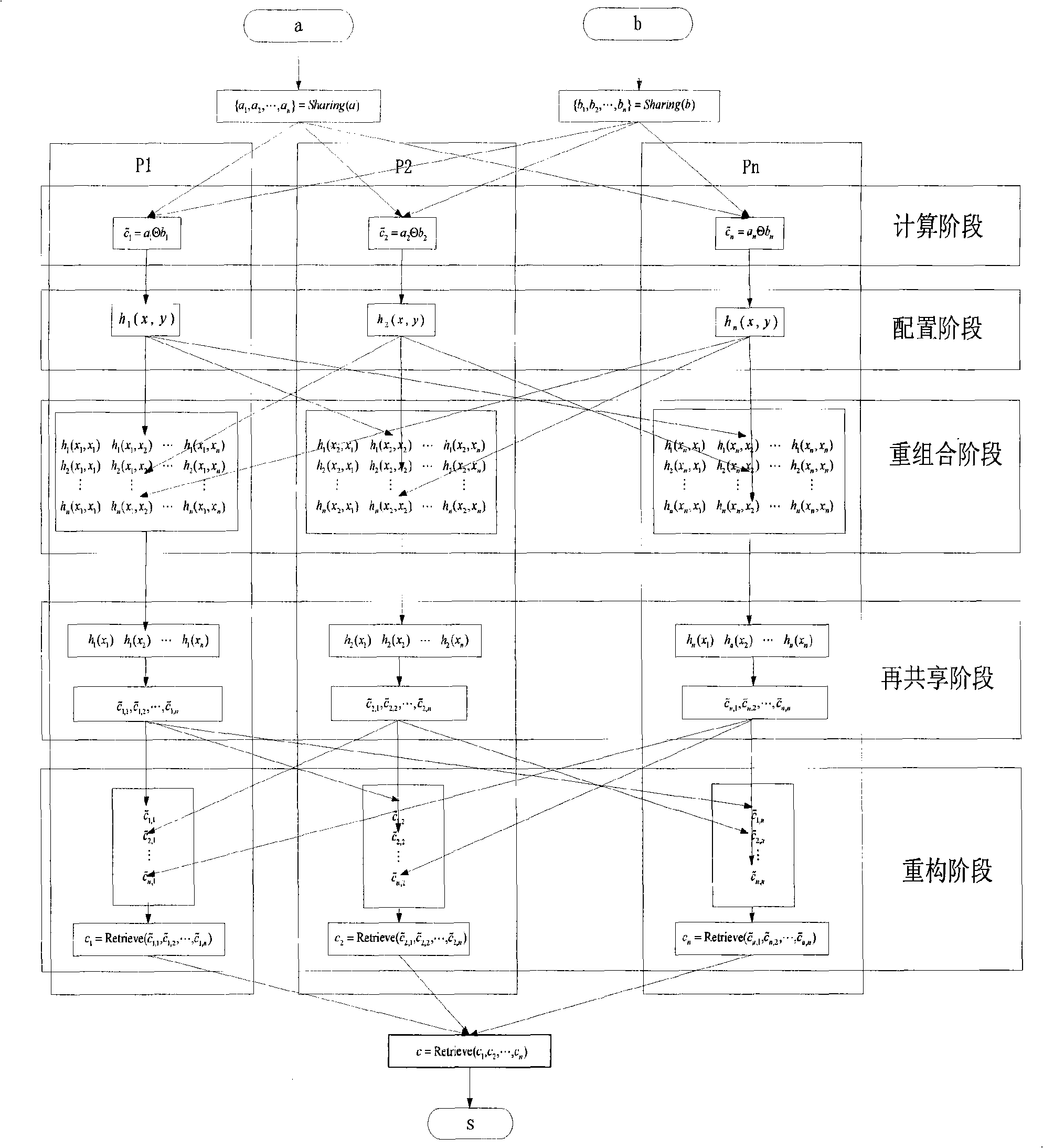

Cryptography distributed calculation and step-by-step verification method with fault-tolerant function

InactiveCN101325596AAchieve efficiencyTo achieve fault toleranceError preventionAccess structureTheoretical computer science

The invention discloses a fault tolerant cryptography distributed computing and multiple step testing method which belongs to the distributed computing field. The method comprises: 1) each member carries out the shared operation separately; 2) every member generates stochastic polynomial according to the required access structure and exchanges the datum induced from the stochastic polynomial; 3) every member generates combined stochastic polynomial by the received stochastic polynomial data together; 4) the result of step1) is re-shared by the combined stochastic polynomial and the re-shared result is distributed to every member; 5) each member further combines and reconstructs the receives re-shared data to gains the final result and a new re-share; 6) every member reconstructs the true result by exchanging the new re-share. The invention is a fault-tolerant and high efficient method with protocol safety, solves the problems of mass traffic and low efficiency in traditional algorithm and assures the continuity in secure computation.

Owner:PEKING UNIV

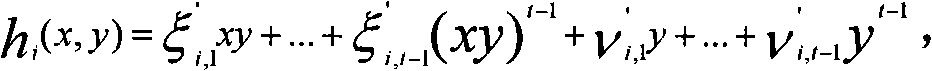

Migration data verification method for power dispatching automation system

The invention discloses a migration data verification method for a power dispatching automation system. The migration data verification method comprises the steps of selecting a new master station and an old master station corresponding to service migration of the power dispatching automation system, selecting some to-be-verified substation in the old master station, disconnecting a normal communication channel of the to-be-verified substation and the old master station and establishing a corresponding analog substation, enabling remote control points to be selected in the new master station and the old master station for the analog substation and serve as current remote control points, sequentially issuing a remote control selection command, a remote control execution command or a remote control revocation command according to the current remote control points, collecting original data of issued commands of the current new master station and the current old master station through the analog substation, checking and comparing the original data to finish data verification of every remote control point, and finally restoring the normal communication channel of the to-be-verified substation and the old master station. The migration data verification method can guarantee migration of the power dispatching automation system between the new master station and the old master station, and has the advantages of being quick in verification speed, high in verification efficiency, good in verification accuracy, and simple and practical.

Owner:STATE GRID CORP OF CHINA +1

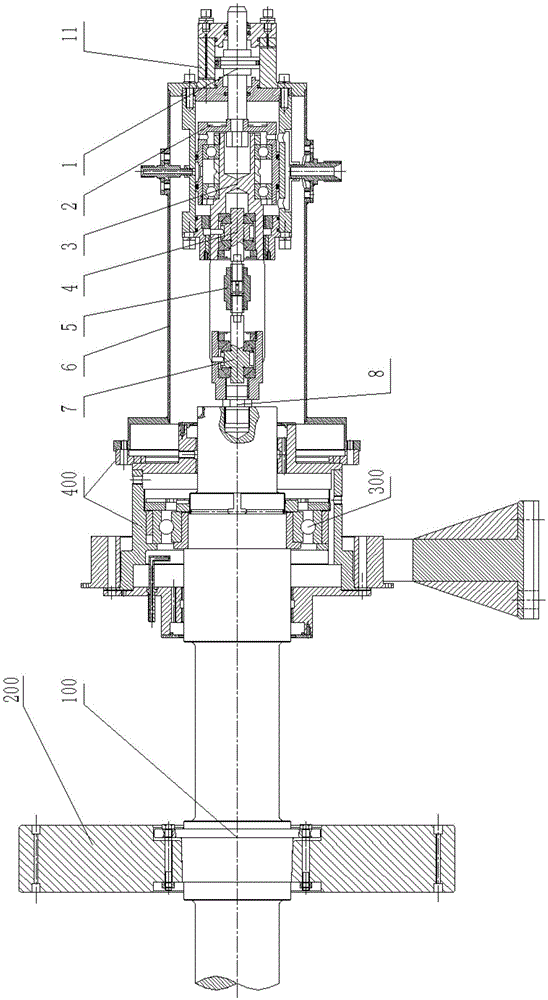

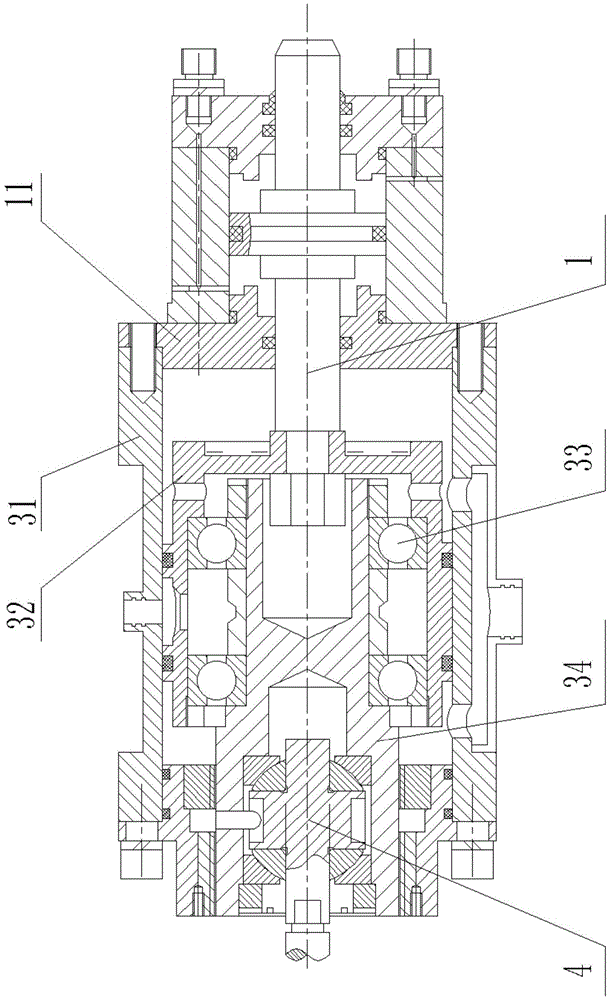

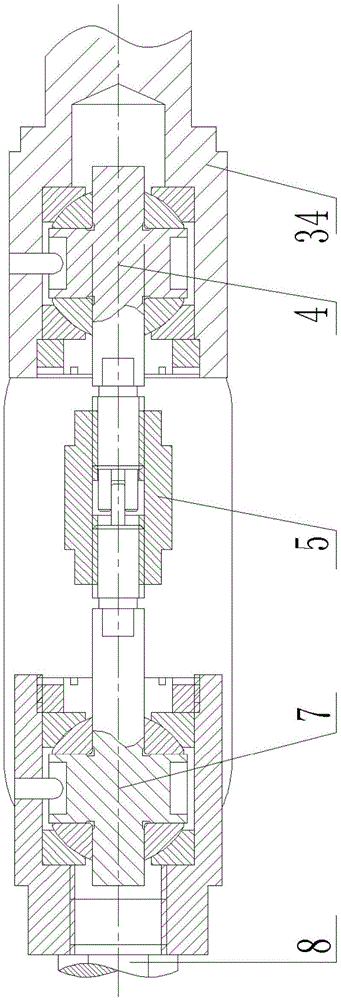

Rotating part axial force loading system comprising rotor and stator difference axis fault-tolerant ability

The invention relates to a rotating part axial force loading system comprising a rotor and stator difference axis fault-tolerant ability. A rotor is arranged on a rotor test device, a test bearing sleeves on outside of the rotor, and is arranged in a bearing pedestal. The system comprises an actuator cylinder, a forcemeter, a rotor and stator convertor, a first universal ball joint connecting rod, a coupling, a second universal ball joint connecting rod, a convert bolt and a load-bearing frame. The actuator cylinder brings an acting force to transmit the acting force to the rotor and stator convertor, the first universal ball joint connecting rod, the coupling, the second universal ball joint connecting rod and the convert bolt in order, and finally, the acting force is transmitted to the rotor and the test bearing. The loading system has simple structure and stable load, and the load system can realize the shaft rotation with the difference axis fault-tolerant ability through the rotor and stator convertor.

Owner:AECC SHENYANG ENGINE RES INST

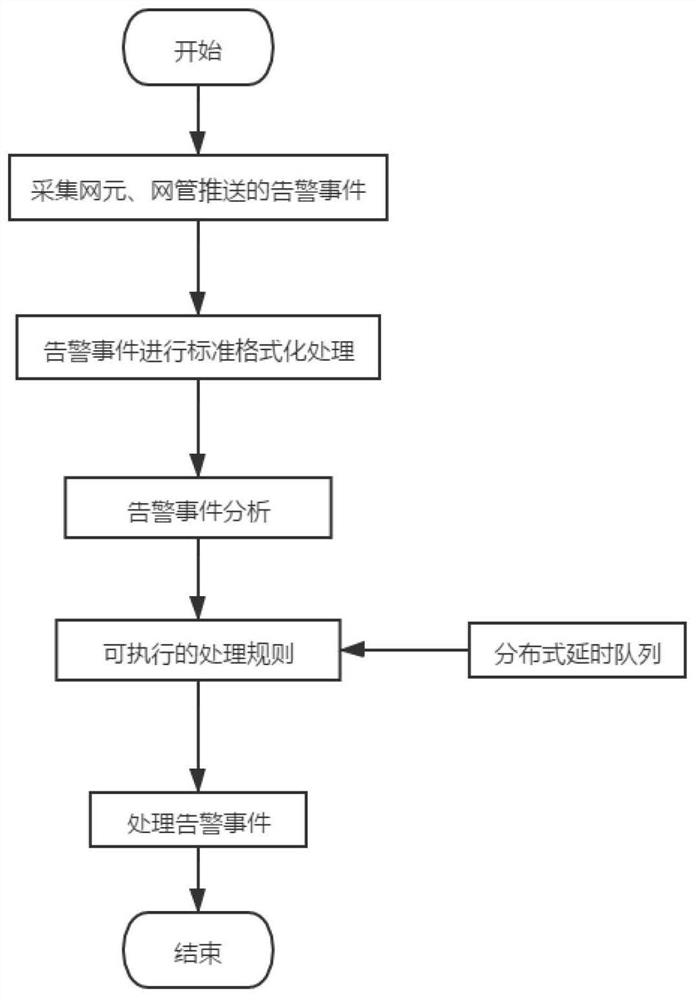

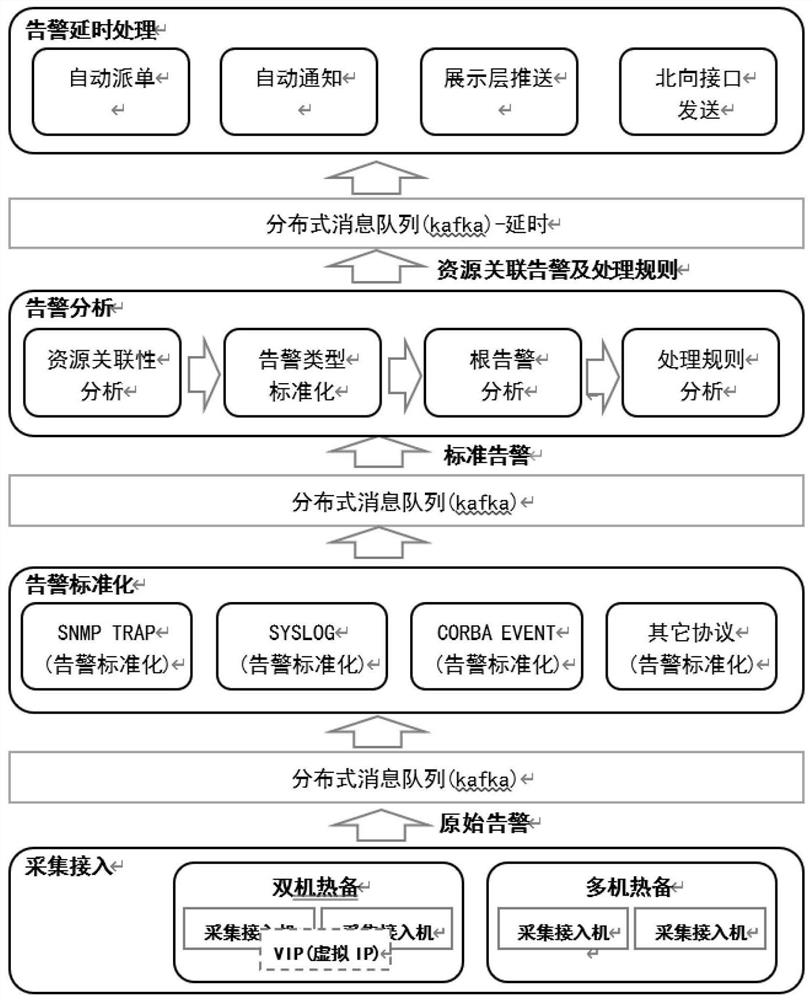

High-availability distributed real-time alarm processing method and high-availability distributed real-time alarm processing system

ActiveCN112671560ATo achieve fault toleranceAchieve concurrencyData switching networksManufacturing computing systemsMessage queueAlarm message

The invention discloses a high-availability distributed real-time alarm processing method and a high-availability distributed real-time alarm processing system. The method comprises the following steps of: acquiring alarm events pushed by a network element and a webmaster and sending the alarm events to a message queue; performing standard formatting processing on the alarm event, and converting the alarm event into the same data format; analyzing the standardized alarm event, and generating a most total executable processing rule; and unifying the sequence of all alarms by using a distributed delay queue to realize the processing of the alarm event. Real-time alarm processing is layered, the alarm receiving process and the alarm processing process are separated, the alarm receiving capacity is maximized, a large number of alarms appearing instantly can be better handled, and alarm messages are received and are not lost. A high-throughput distributed persistent message queue is adopted, so that the alarm can be reliably stored and buffered.

Owner:广东电力通信科技有限公司

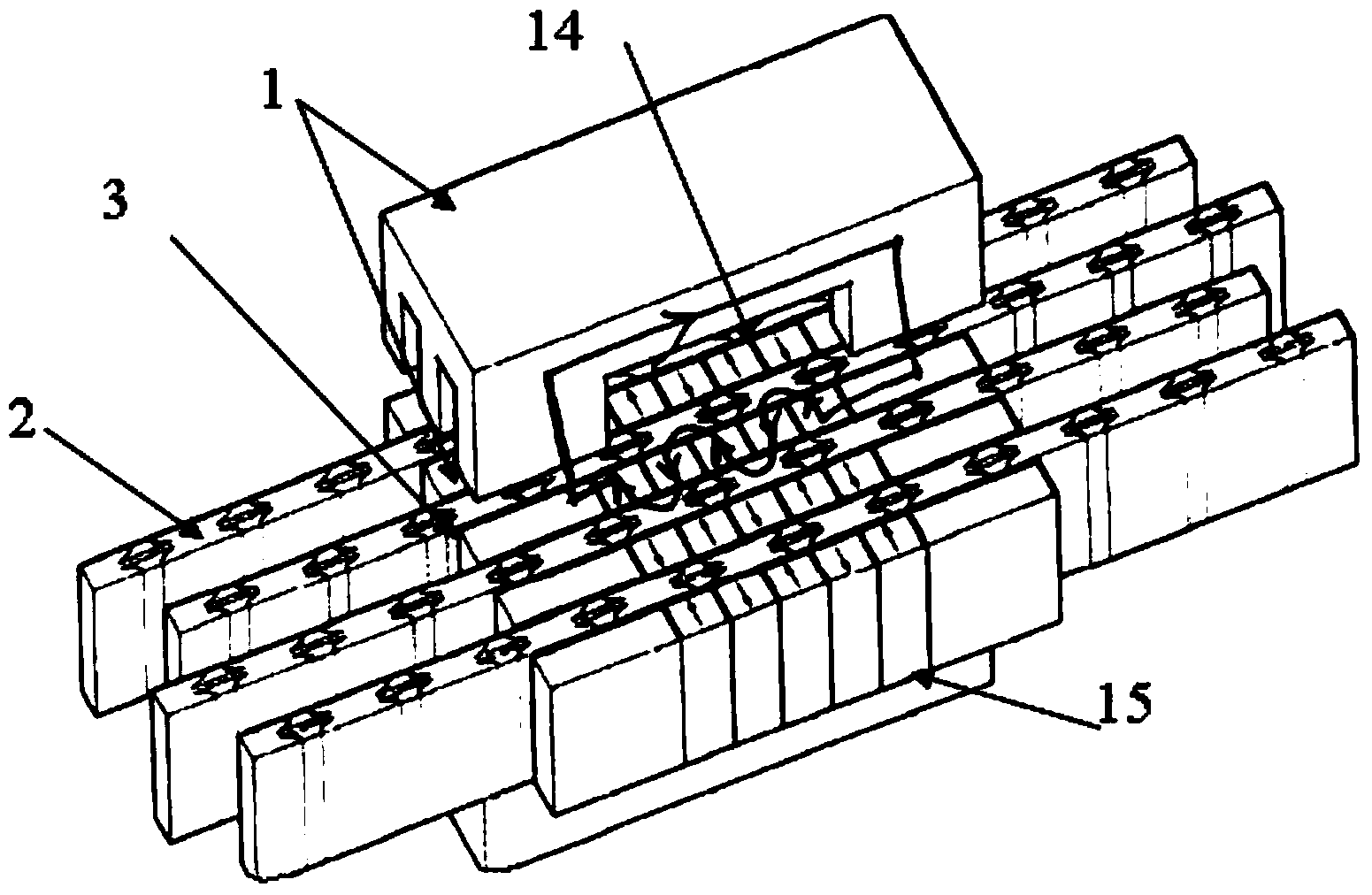

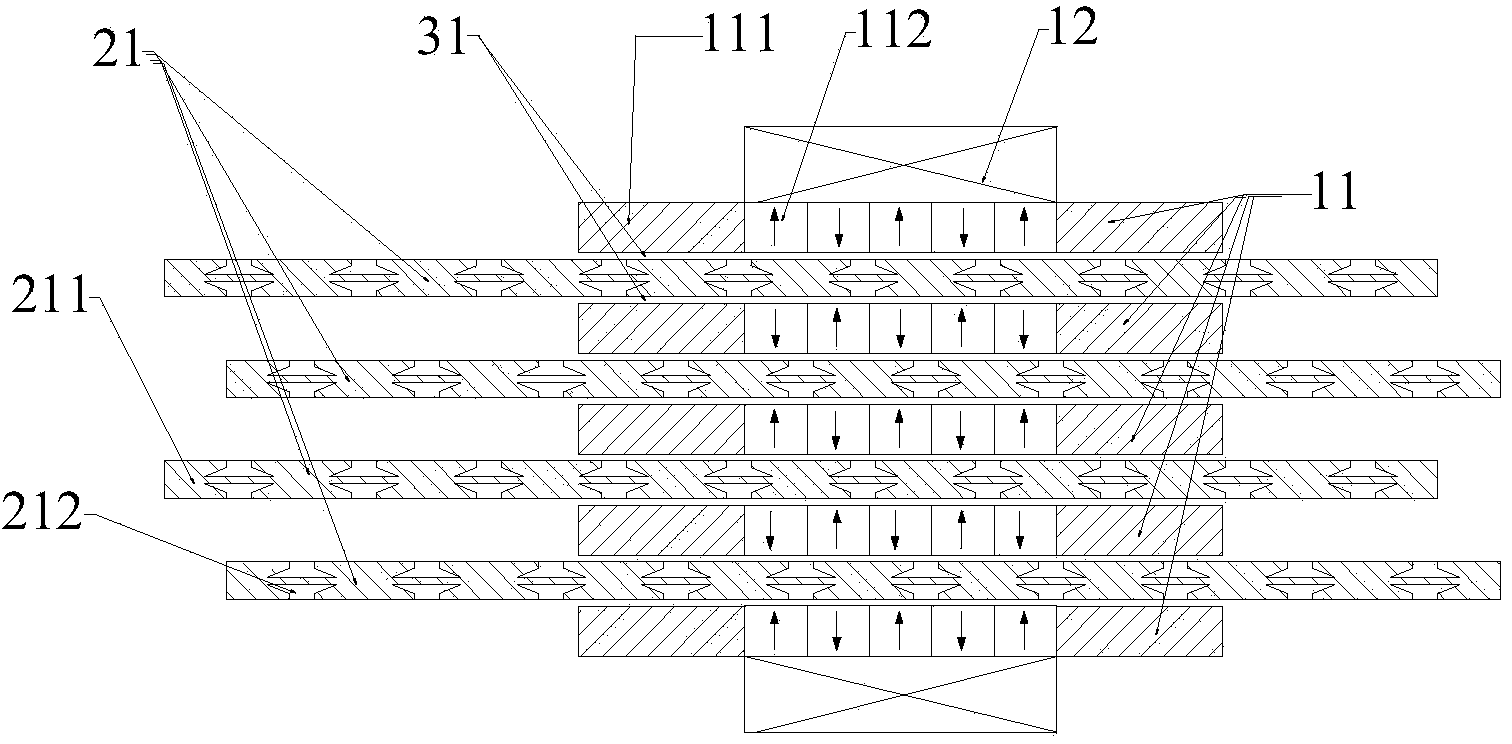

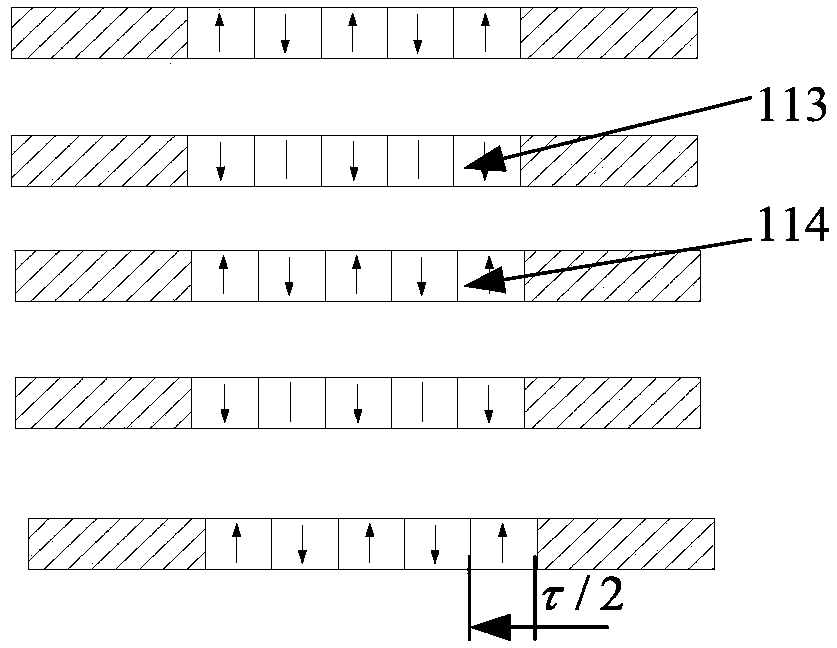

Three-dimensional magnetic flux permanent magnet linear motor of multi-air-gap independent winding structure

InactiveCN103915971AIncrease thrust densityIncrease the air gap areaPropulsion systemsElectric machinePermanent magnet linear motor

The invention provides a three-dimensional magnetic flux permanent magnet linear motor of a multi-air-gap independent winding structure and belongs to the technical field of motors. The three-dimensional magnetic flux permanent magnet linear motor comprises a primary assembly, a secondary assembly and multiple air gaps. The primary assembly comprises n primary units and armature windings, and the primary units are arranged perpendicular to the horizontal direction. An array composed of 2m+1 permanent magnets arrayed in a polarity staggering mode is arranged on each primary unit, the width of each permanent magnet is T / 2 (T is polar distance), and two rectangular grooves are formed by annular magnetic permeability iron cores arranged at the two ends of each permanent magnet and the permanent magnet, and the armature windings are arranged in two grooves in the vertical direction and are the same in phase. The secondary assembly is composed of n-1 secondary units, wherein the secondary units and the primary units are arrayed perpendicular to the horizontal direction in a staggered mode, and non-magnetic-permeability grooves or magnetism isolation bridges are arranged periodically arranged on secondary unit iron cores. The non-magnetic-permeability grooves of the adjacent secondary units are staggered by T / 2 distance in the horizontal direction. The motor is provided with 2n-2 air gaps. A three-dimensional magnetic circuit is adopted for the motor, high electromagnetic loads can be effectively achieved, and the motor has the advantages of being high in thrust density and reliability.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

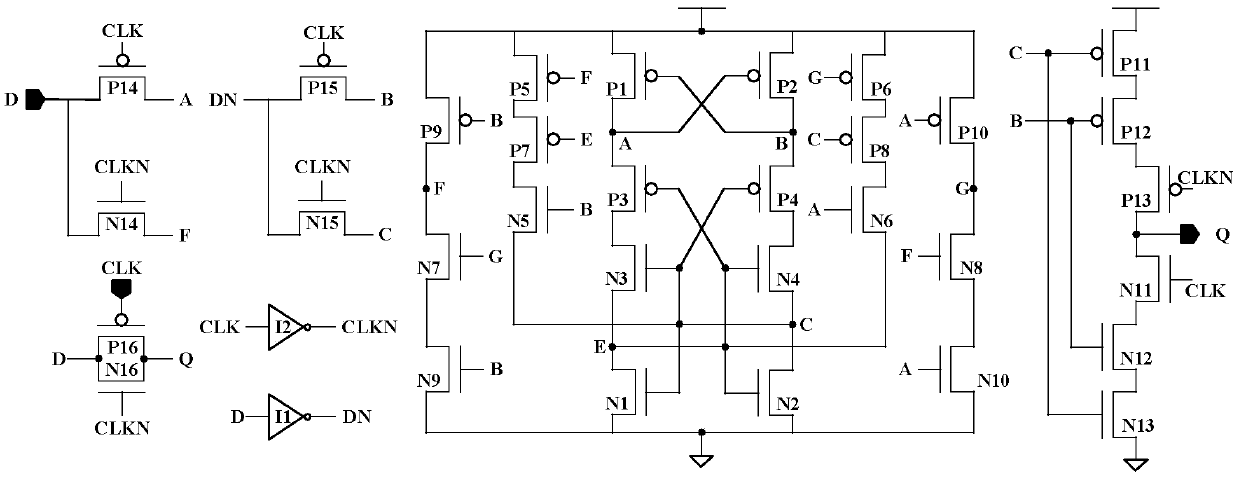

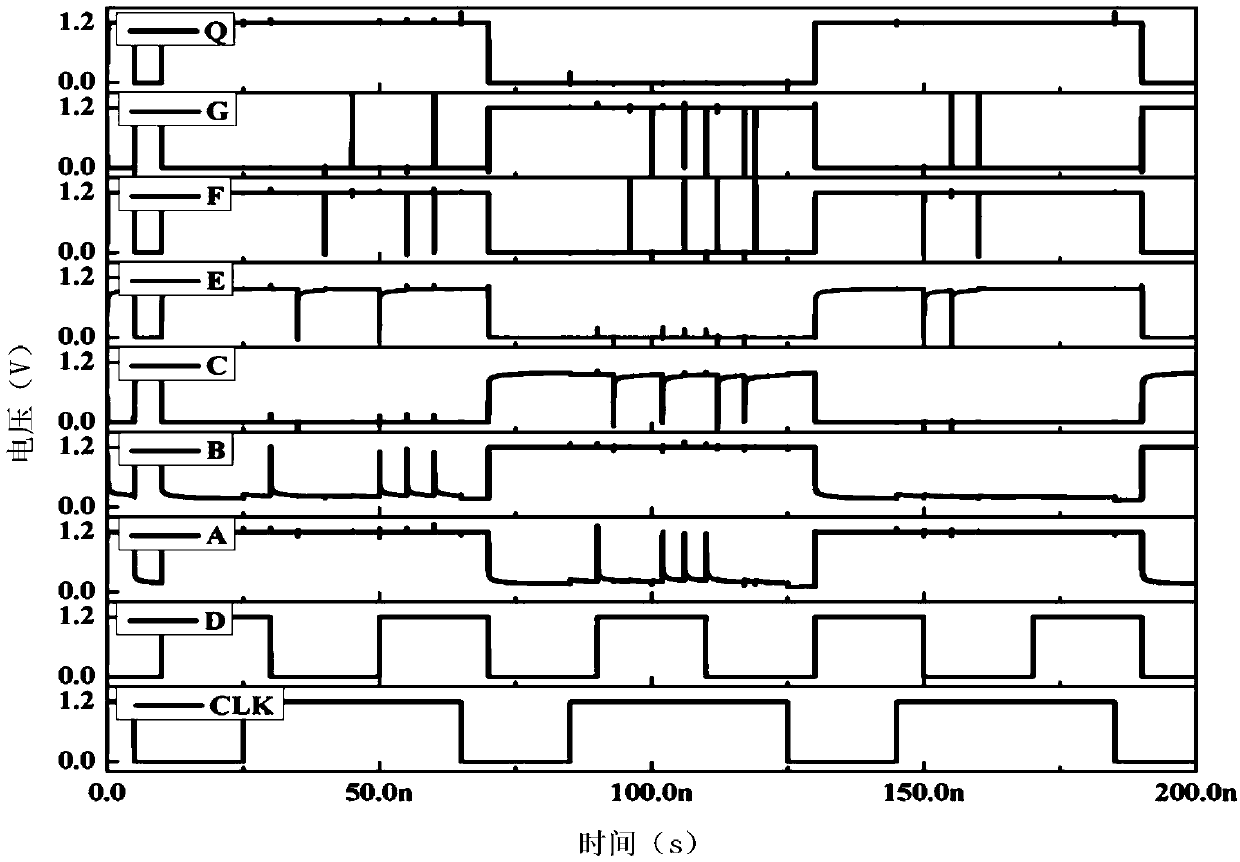

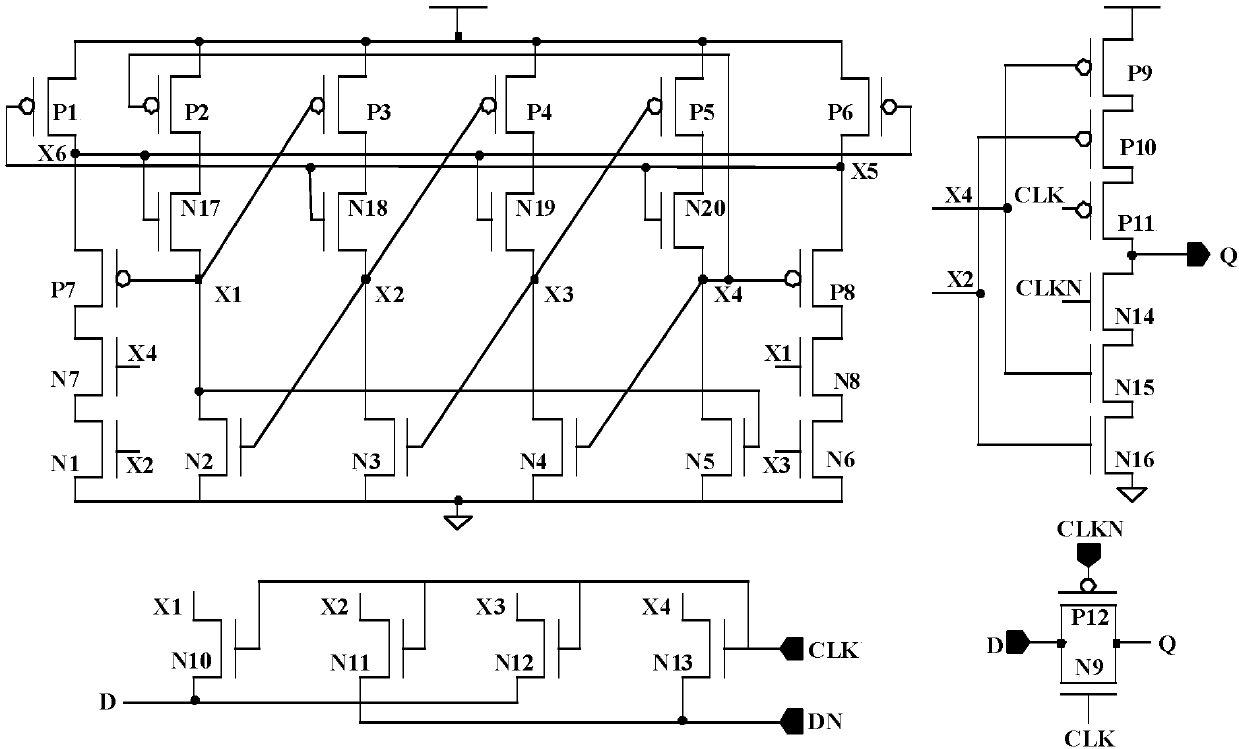

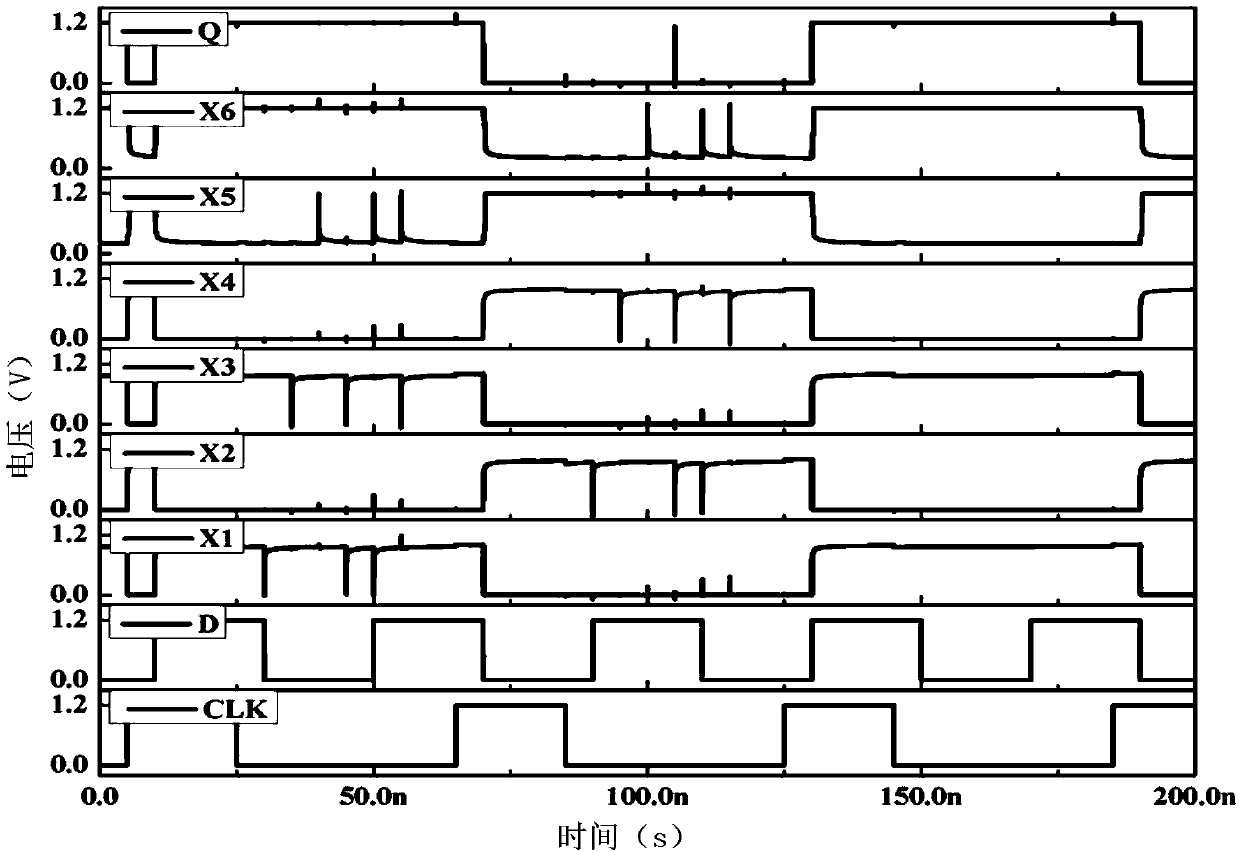

Anti-radiation D latch

ActiveCN109547006AReduce power consumptionReduce overheadReliability increasing modificationsFault toleranceTransmission gate

The invention discloses an anti-radiation D latch, belongs to the field of anti-nuclear reinforcement in integrated circuit reliability, and solves the problems that the traditional anti-radiation D latch needs more hardware and is high in power consumption and long in delay time, the double-node upset can be resisted, but the double-node upset resistance is poor, and even the fault tolerance of the double-node upset cannot be achieved. The anti-radiation D latch comprises NMOS transistors N1 to N16, PMOS transistors P1 to P16 and two inverters I1 and I2. The anti-radiation D latch is few in used devices, small in size and simple in structure, so that the power consumption of the whole latch is reduced and the latch has low hardware expenditure. A signal at the input end of the latch can be transmitted to an output port only through one transmission gate, the data transmission time is short, and the fault tolerance for upset of any single node and the two nodes can be achieved, and thus the fault-tolerant protection of the single-node upset resistance and the double-node upset resistance is achieved. The anti-radiation D latch can provide protection for application of an integratedcircuit chip in a high-radiation environment (such as aerospace and ground nuclear power stations).

Owner:ZHONGBEI UNIV

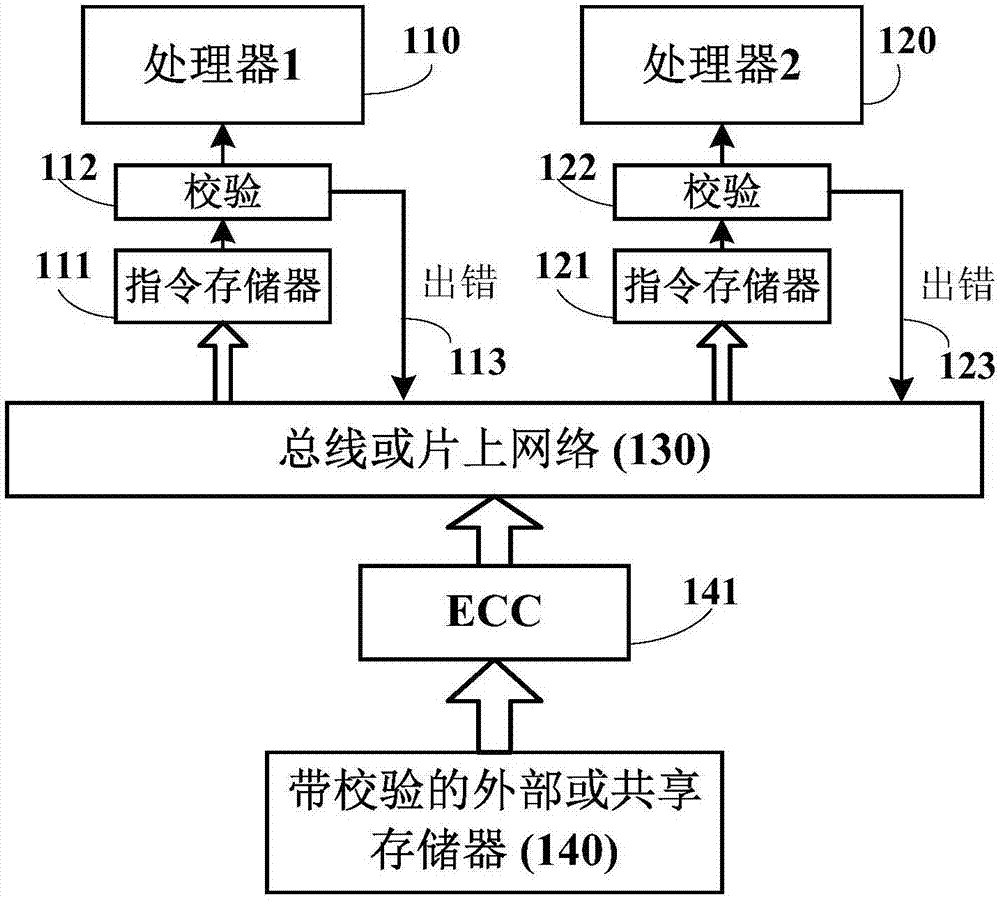

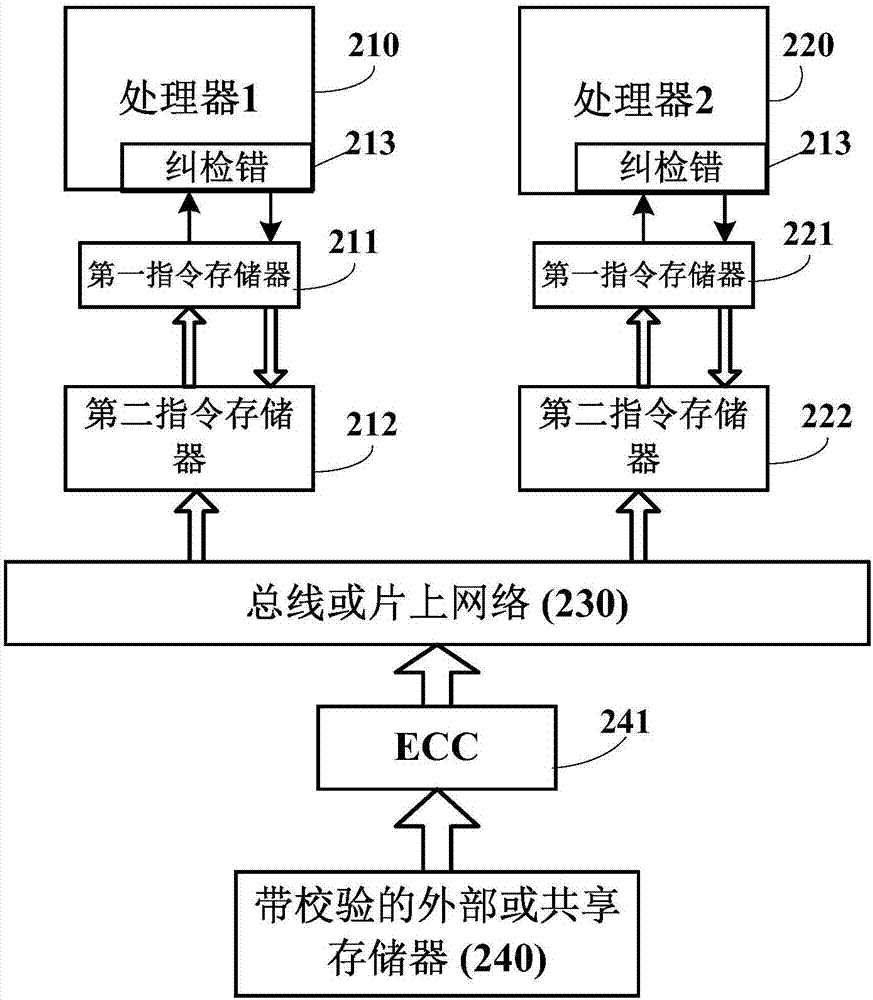

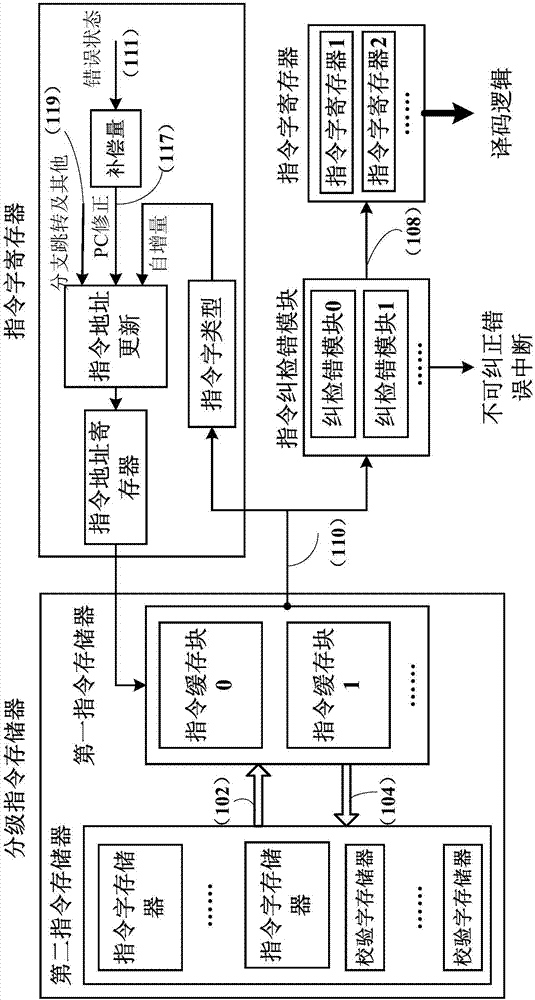

Method and device for fault tolerance of grading instruction memory structure capable of actively writing back

ActiveCN107885611AGuaranteed reliabilityImprove reliabilityNon-redundant fault processingInstruction memoryFault tolerance

The invention provides a method and a device for fault tolerance of a grading instruction memory structure capable of actively writing back. The device comprises a grading instruction memory, an instruction fault correcting and checking module, an instruction character register, and an instruction address register. The method comprises: 1, starting and operating a processor; 2, taking out instruction character data from the grading instruction memory; 3, sending the instruction character data to the instruction fault correcting and checking module; 4, determining a fault correcting and checking result to have no fault or have a correctable fault; if yes, continuing to perform a step 5; if no, jumping to step 10; 5, writing an instruction character to the instruction character register; 6,updating the instruction address register; 7, determining whether a correctable fault occurs; if yes, continuing to perform a step 8; if no, jumping to a step 9; 8, writing the instruction character data back to the grading instruction memory; 9, ending processing; jumping to the step 2, processing the address of the next instruction; 10, when the instruction character data has uncorrectable fault, suspending the processor. The method and the device realize fault tolerance of instructions and the instruction memory, and have relatively low hardware cost.

Owner:XIAN MICROELECTRONICS TECH INST

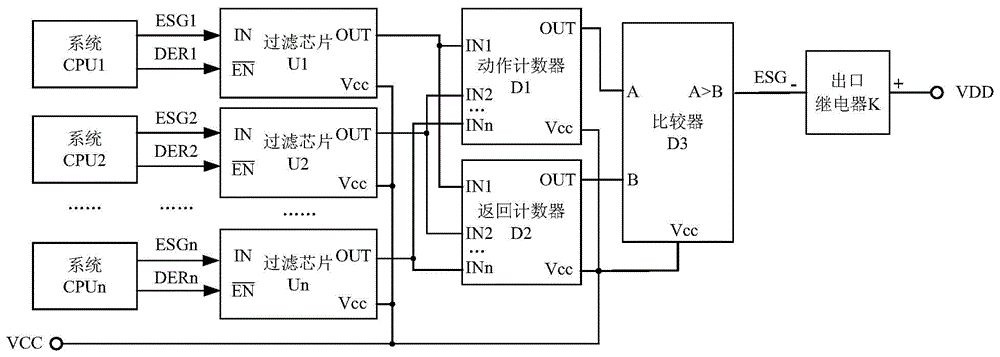

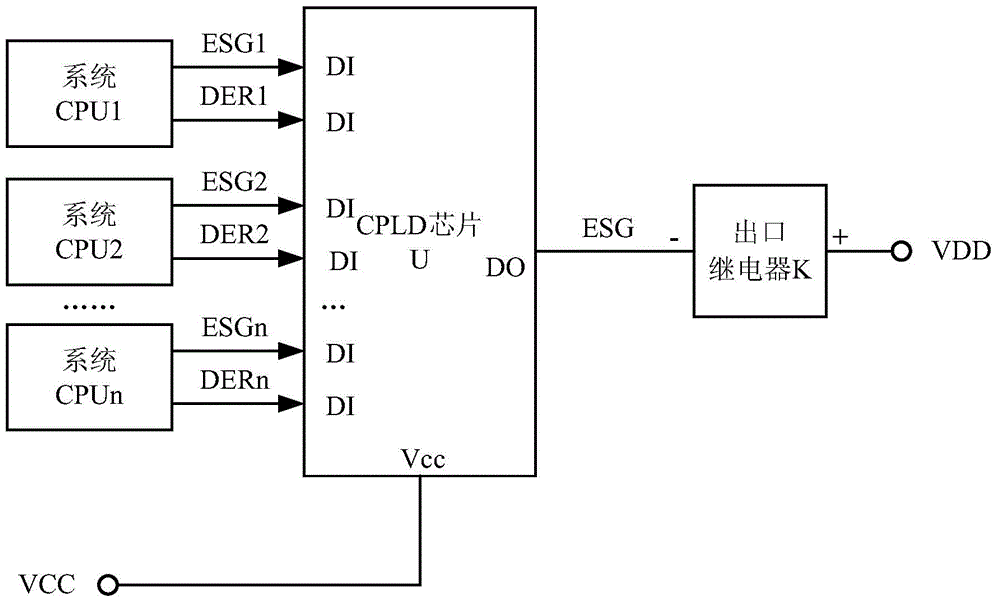

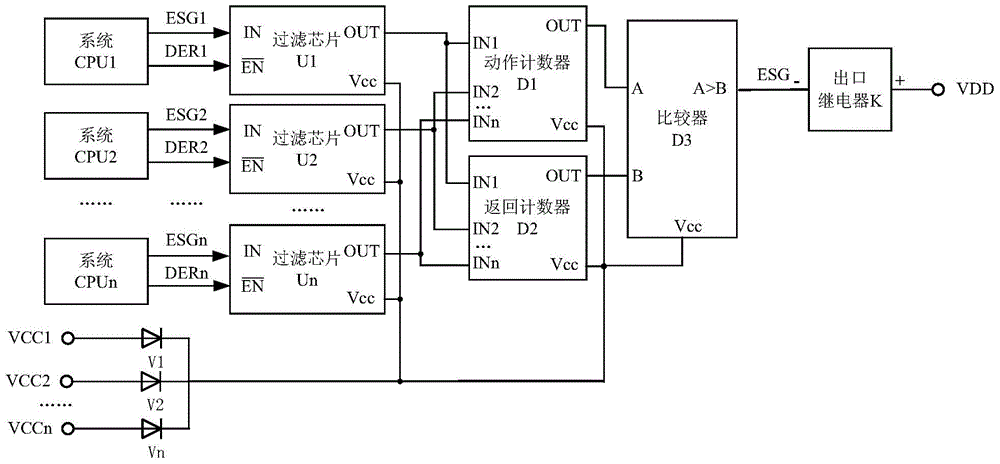

Multi-bus protection outlet arbitration fault tolerance system and method

ActiveCN104810808AGuaranteed reliabilityPrevent impact on reliabilityEmergency protective circuit arrangementsFault toleranceError prevention

The invention discloses a multi-bus protection outlet arbitration fault tolerance system which comprises a first power supply, a second power supply, a plurality of CPUs (central processing unit), a plurality of filtering chips, an action counter, a return counter, a comparator and an outlet relay. Each CPU is connected with the corresponding filtering chip, the action counter and the return counter are connected with the filtering chips, output ends of the action counter and the return counter are connected with an input end of the comparator, an output end of the comparator is connected with a negative electrode of an input end of the outlet relay, a positive electrode of an input end of the outlet relay is connected with the second power supply, and the first power supply is connected with the filtering chips, the action counter, the return counter and the comparator. Redundancy and fault tolerance design principles are simultaneously considered, and act-refused prevention and act-error prevention of the CPUs in a protection device are organically integrated.

Owner:NANJING GUODIAN NANZI POWER GRID AUTOMATION CO LTD

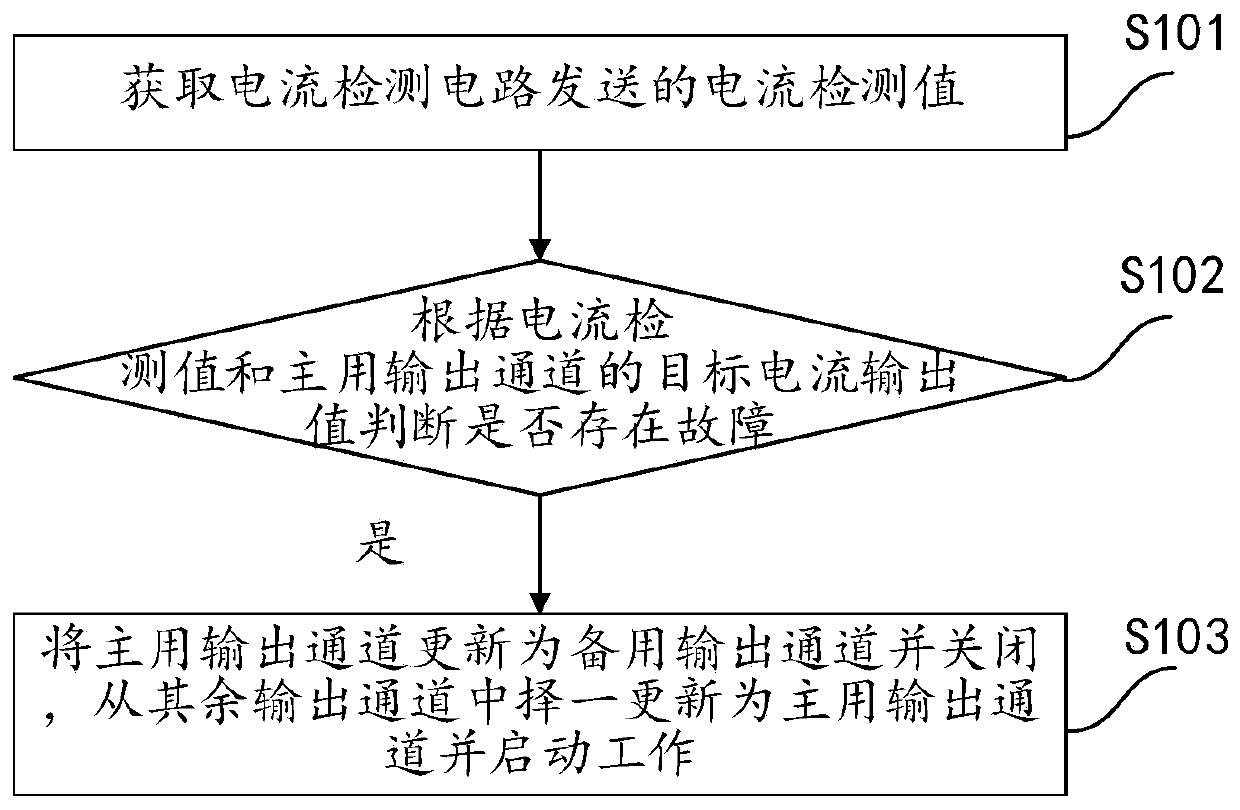

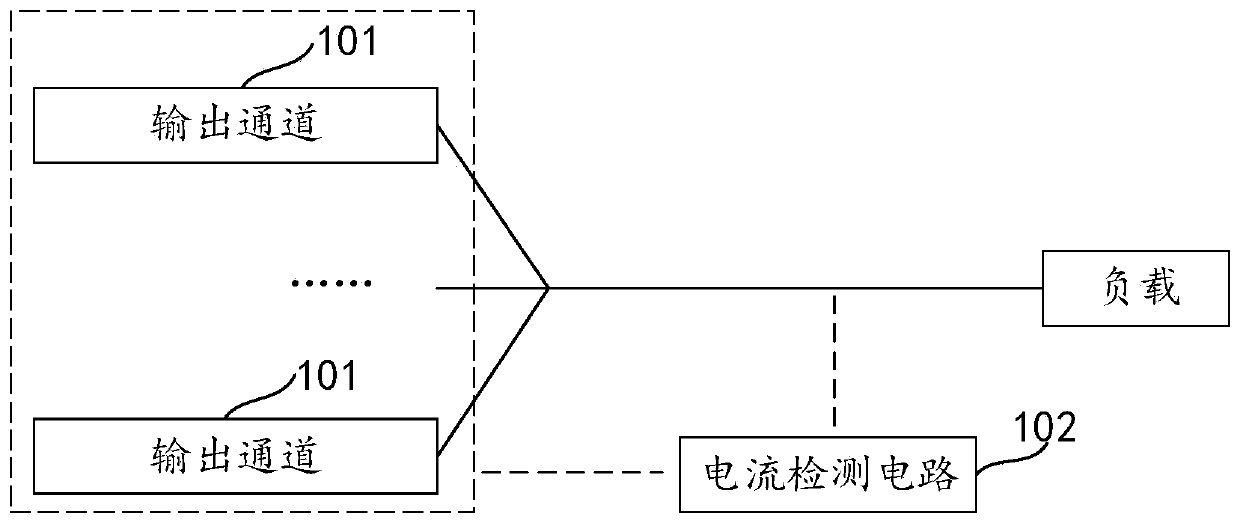

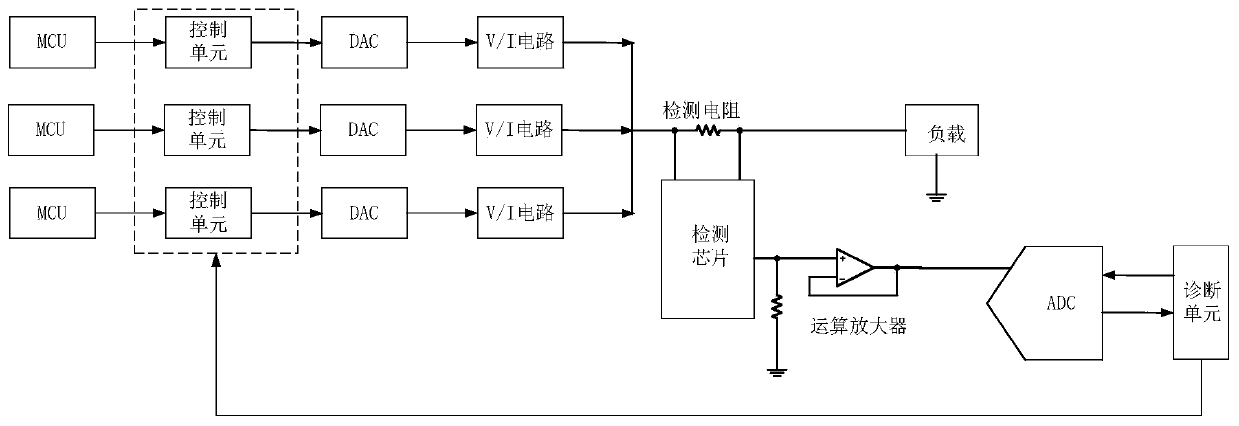

Current type analog quantity output module and control method thereof

ActiveCN110780111ATimely detection of faultsTo achieve fault toleranceMeasurement using digital techniquesFault toleranceControl engineering

The application discloses a current type analog quantity output module and a control method thereof, which are suitable for a current type analog quantity output module comprising a plurality of output channels with output terminals connected in parallel and a current detection circuit. The current detection circuit is coupled to a combined circuit formed after parallel connection of the pluralityof output channels and is sued for detecting the output current in the combined circuit. In addition, the control method includes: acquiring current detection value sent by the current detection circuit; determining whether a fault exists or not according to a current detection value and a target current output value of a main output channel being current unique one in a working state; and if so,updating the main output channel to be a standby output channel and closing the standby output channel, and selecting one from the rest of output channels to update the selected one to be a main output channel and starting the main output channel to work. Therefore, a fault problem can be detected in time and the standby output channel can be selected to replace the current main output channel tooutput currents continuously, thereby realizing fault tolerance and thus improving the safety and usability of the product effectively.

Owner:HANGZHOU HOLLYSYS AUTOMATION

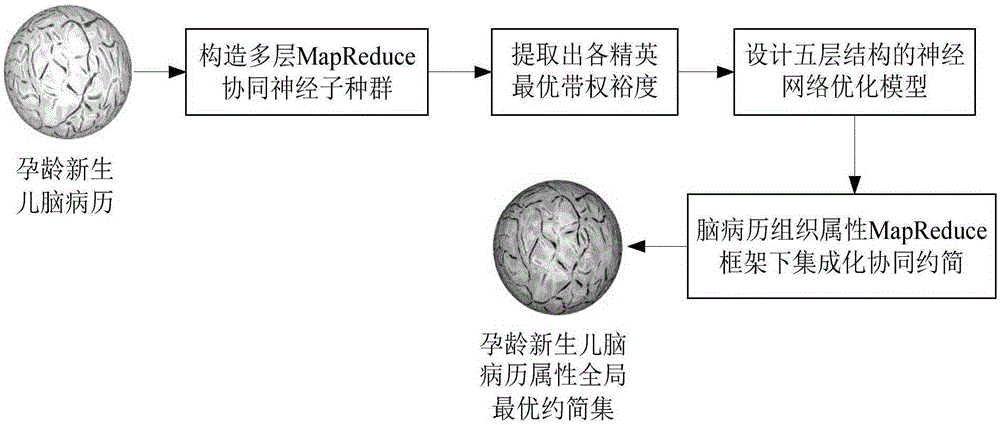

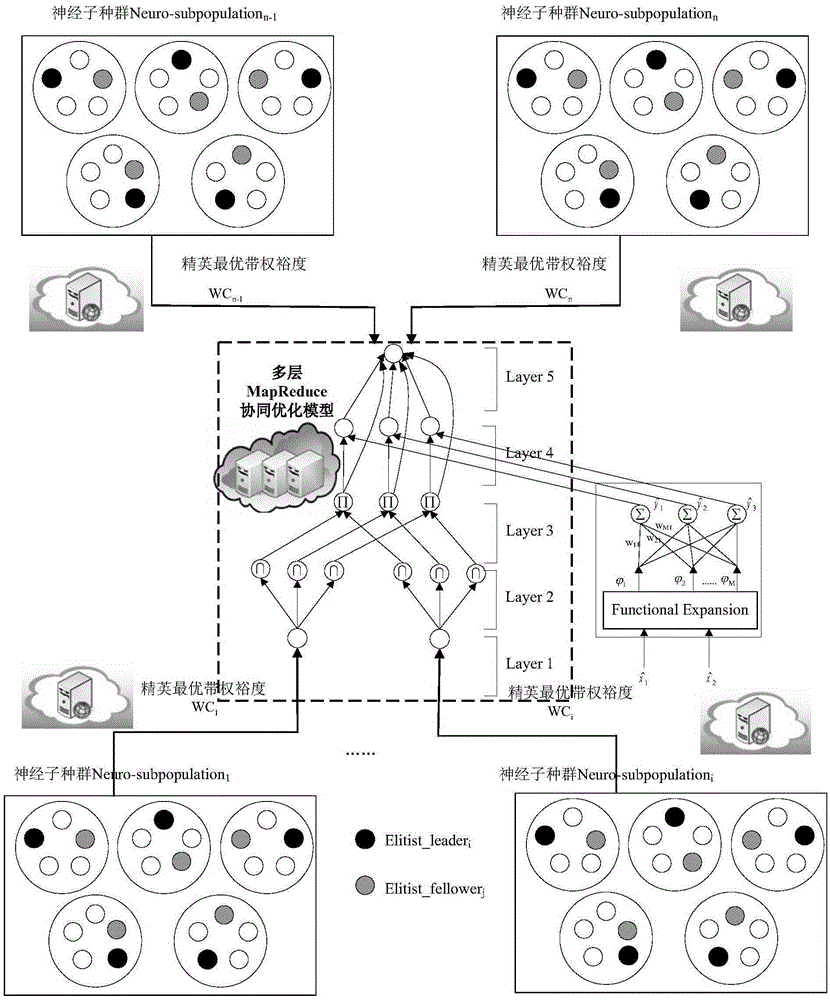

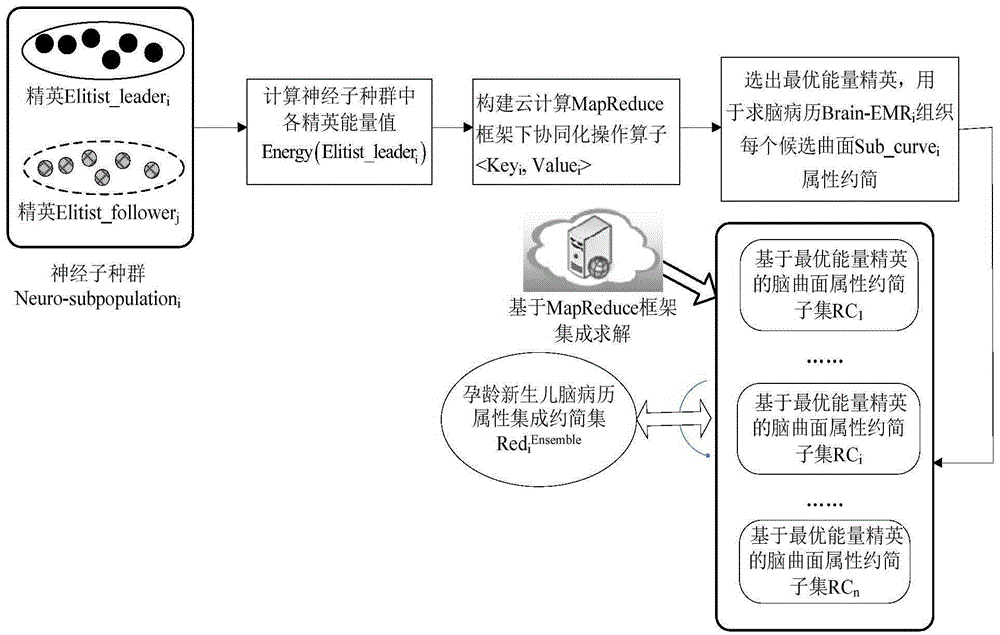

Multilayer cloud computing framework coordinated integrated reduction method for gestational-age newborn brain medical records

ActiveCN105279388AImprove stabilityImprove consistencyBiological neural network modelsSpecial data processing applicationsPopulationNetwork model

The invention discloses a multilayer cloud computing framework coordinated integrated reduction method for gestational-age newborn brain medical records. The multilayer cloud computing framework coordinated integrated reduction method comprises the steps of firstly constructing a multilayer MapReduce coordinated neuro-subpopulational structure, extracting each neuro-subpopulational elite optimal weighted margin WCi, adaptively dividing a large-scale brain medical record tissue attribute to n neuro-subpopulations which co-evolute through the MapReduce, and acquiring optimal dividing curved surfaces of different brain medical record tissues; and designing a neural network model with a five-layer structure, constructing an elite energy matrix NSMP, performing integrated coordinated reduction of a brain medical record curved surface Sub-curvei by each neuro-subpopulation optimal energy elite Elitist-leaderi, obtaining the optimal reduced set Redi<Ensemble> of a respective divided curved surface, and finally extracting a global optimal attribute reduced set Red<Ensemble> of the brain medical record tissue. According to the multilayer cloud computing framework coordinated integrated reduction method, the reduction efficiency and the reduction efficiency for the gestational-age newborn brain medical records in a big data environment are quickly improved through the multilayer MapReduce frame and coordinating with the neuro-subpopulational elite in a cloud computing environment. Furthermore the multilayer cloud computing framework coordinated integrated reduction method for the gestational-age newborn brain medical records has an important meaning for brain medical record selection, role extraction, clinical decision supporting service, etc.

Owner:NANTONG UNIVERSITY

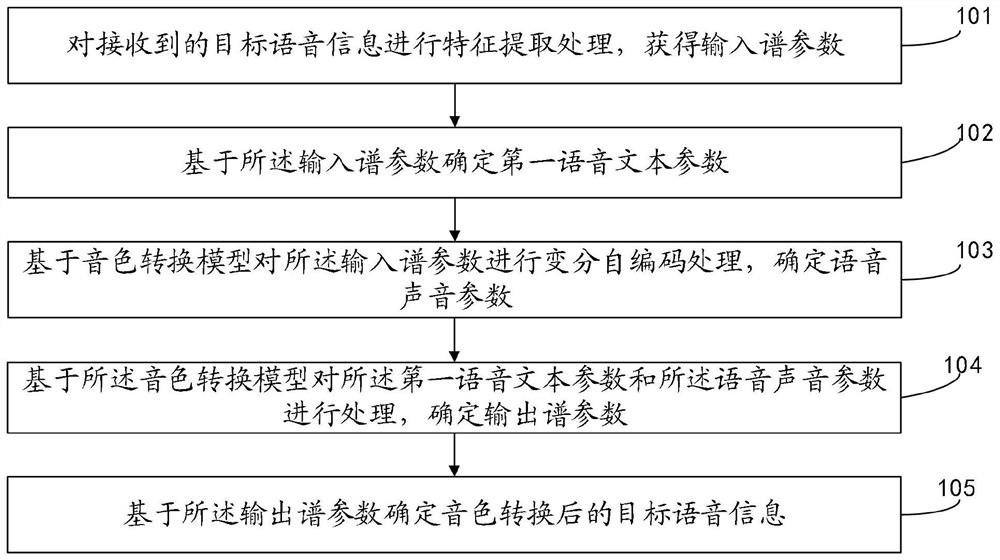

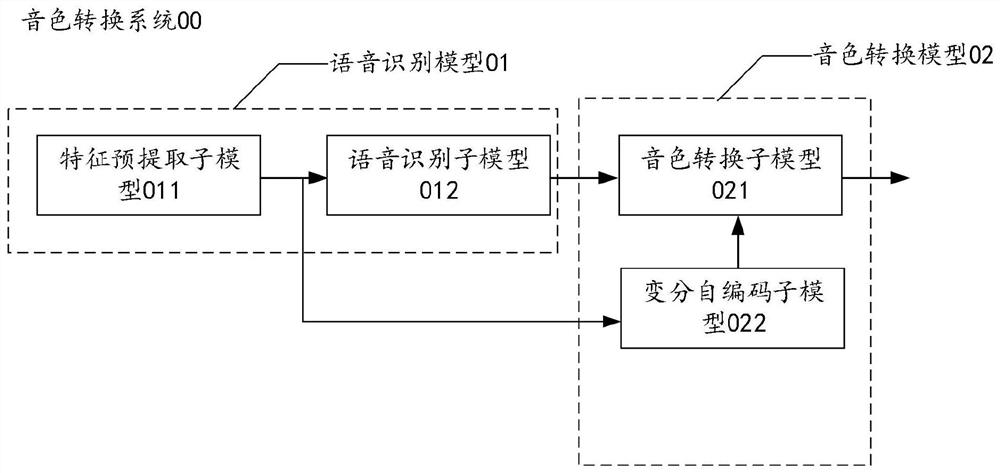

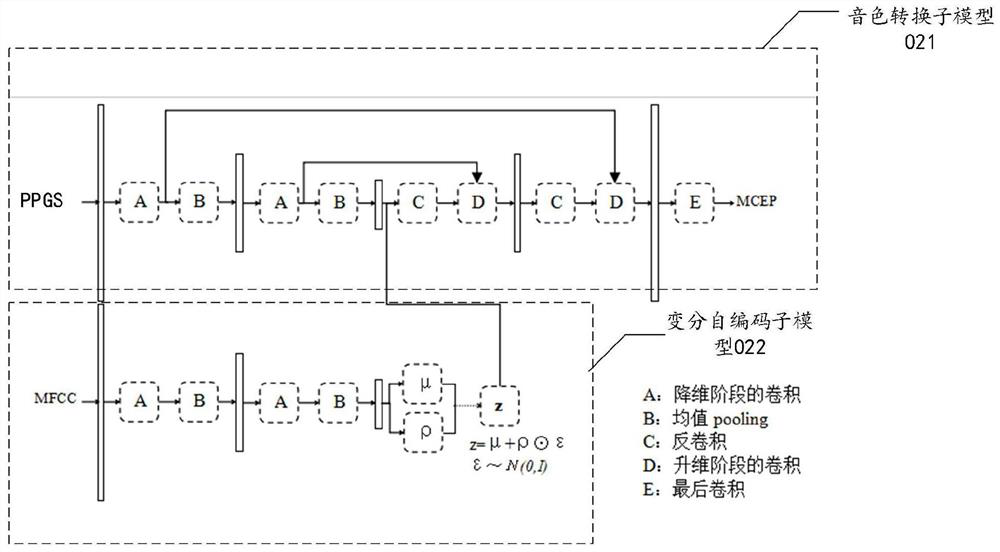

Timbre conversion method and device and electronic equipment

PendingCN112652318AGuaranteed conversion effectImprove reliabilitySpeech analysisFeature extractionEngineering

The invention discloses a timbre conversion method and device and electronic equipment, and belongs to the technical field of audio processing. The method comprises the following steps: carrying out feature extraction processing on received target voice information to obtain input spectrum parameters; determining first voice text parameters based on the input spectrum parameters; performing variational self-encoding processing on the input spectrum parameters based on a tone conversion model, and determining voice parameters; processing the first voice text parameters and the voice sound parameters based on the tone conversion model, and determining output spectrum parameters; and determining target voice information after tone conversion based on the output spectrum parameters. According to the embodiment of the invention, by determining the voice sound parameters, false recognition of tone conversion based on the output spectrum parameters determined by the first voice text parameters is reduced, error correction and fault tolerance of false recognition are realized, the conversion effect of tone conversion is ensured, and the reliability of tone conversion is improved.

Owner:BEIJING SINOVOICE TECH CO LTD

Anti-double-node-upset D latch

ActiveCN109525236ASensitive area reducedReduce areaDelay compensationFault toleranceNuclear radiation

The invention provides an anti-double-node-upset D latch and belongs to the field of nuclear hardening in integrated circuit reliability. The problems that according to an existing latch, required hardware is much, an area is large, power consumption is high, propagation delay time is long, anti-double-node-upset capability is poor, and fault tolerance to double-node-upset cannot be realized are solved. The D latch comprises 20 NMOS transistors N1 to N20 and 12 PMOS transistors P1-P12. Employed devices are few. A size is small. A structure is simple. The employed devices are few, so power consumption of the whole latch is reduced, and relatively low hardware cost is realized. A signal at an input end of the latch can be transmitted to an output port through a transmission gate. Data transmission time is short. The fault tolerance to any single-node and double-node-upset can be realized, so anti-single-node and anti-double-node-upset fault tolerance protection is realized. The D latch is particularly applicable to aerospace, space flight and a nuclear power plant with nuclear radiation effect.

Owner:ZHONGBEI UNIV +1

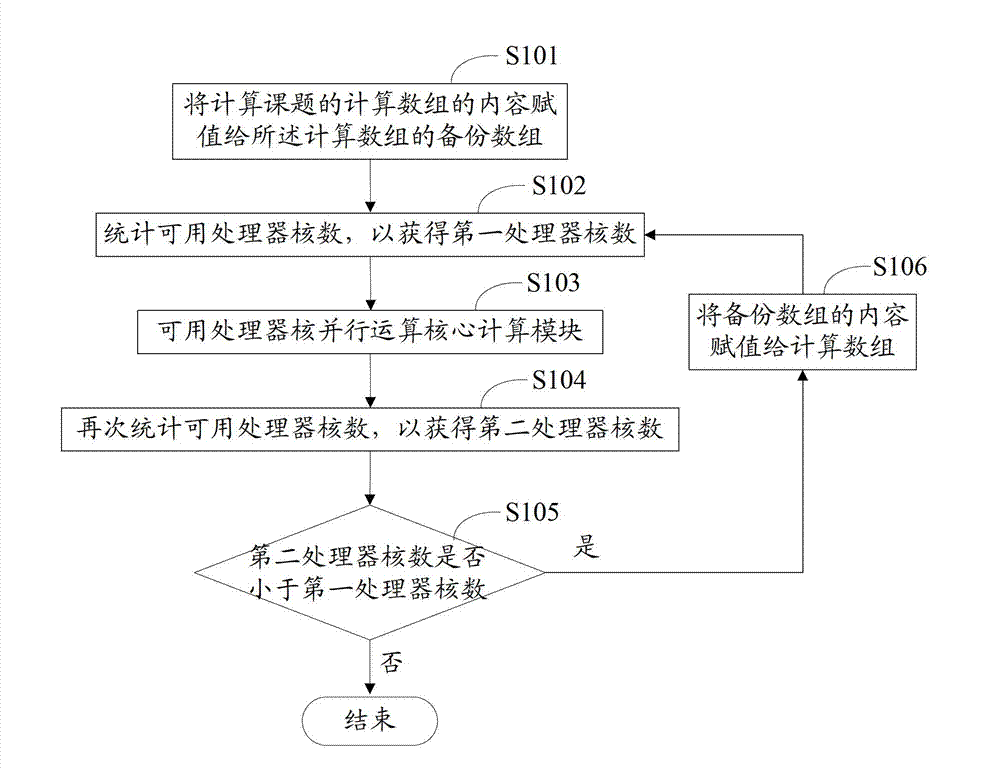

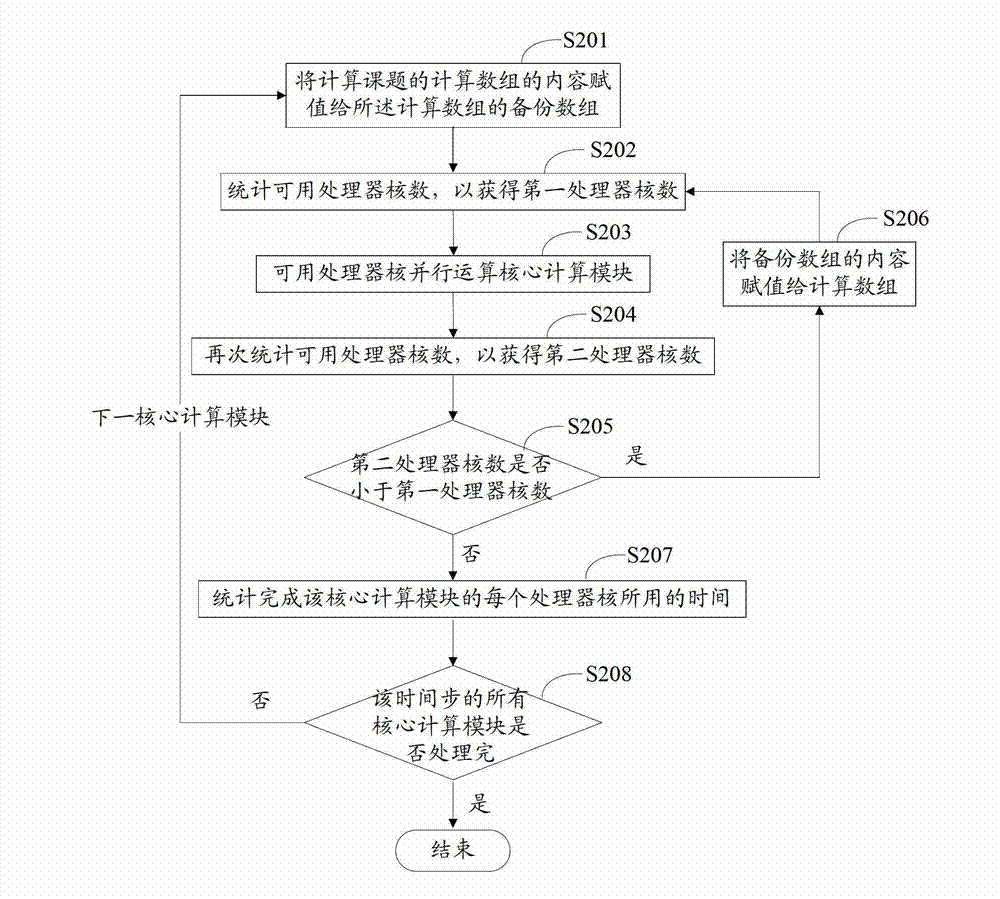

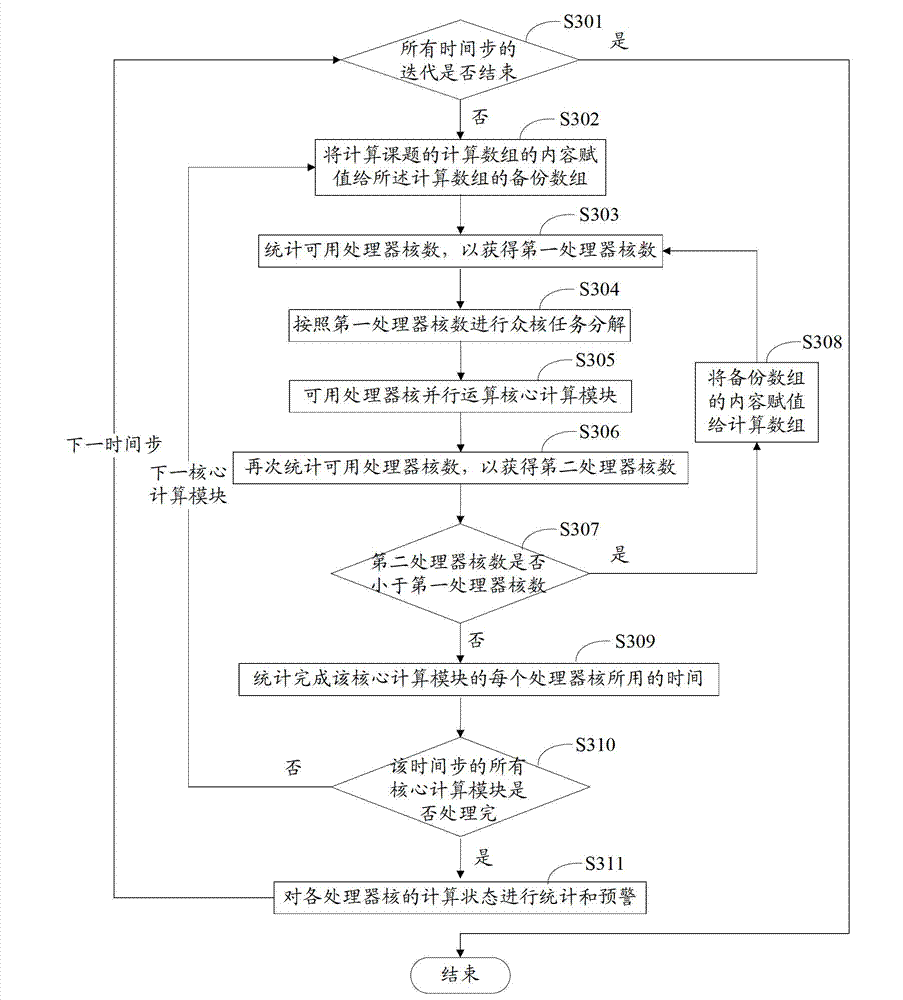

Fault-tolerance method of large-scale heterogeneous parallel computing

ActiveCN102929738AReduce failure recovery timeGuaranteed reliabilityFault responseFault toleranceArray data structure

The invention provides a fault-tolerance method of large-scale heterogeneous parallel computing. The method includes treating each core computing module of each time step as follows: contents in computing digit groups of a computing subject are assigned to backup digit groups and computing for completing the core computing modules is performed; wherein the computing for completing the core computing modules includes that the number of available processor cores is computed to obtain the number of a first processor cores; the available processor cores perform parallel computing on the core computing modules; the number of the available processor cores is computed for a second time to obtain the number of a second processor cores; and the number of the first processor cores and the number of the second processor cores are compared, if the number of the first processor cores is smaller than that of the second processor cores, contents of backup digit groups are assigned to the computing digit groups, and computing for completing the core computing modules is completed for a second time until the number of the first processor cores is consistent with that of the second processor cores. According to the fault-tolerance method of large-scale heterogeneous parallel computing, computing resources can be fully used, fault recovery time is reduced, and the reliability of parallel computing is improved.

Owner:JIANGNAN INST OF COMPUTING TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com