Parallel scheduling method for satellite-borne multi-core SoC (System on a Chip) task-level load balance

A technology of task scheduling and load balancing, applied in the direction of multi-program device, resource allocation, program control design, etc., to achieve the effect of avoiding failure, avoiding inconsistency, and realizing software fault tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

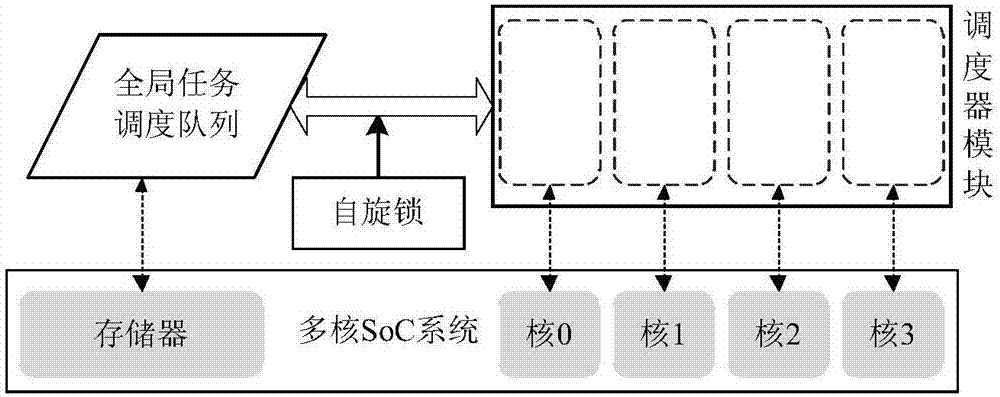

[0024] In order to give full play to the computing performance of the on-board multi-core SoC and realize the task scheduling of the on-board multi-core parallel and fault-tolerant embedded operating system, the present invention proposes a task-level load-balanced parallel scheduling method for the on-board multi-core SoC.

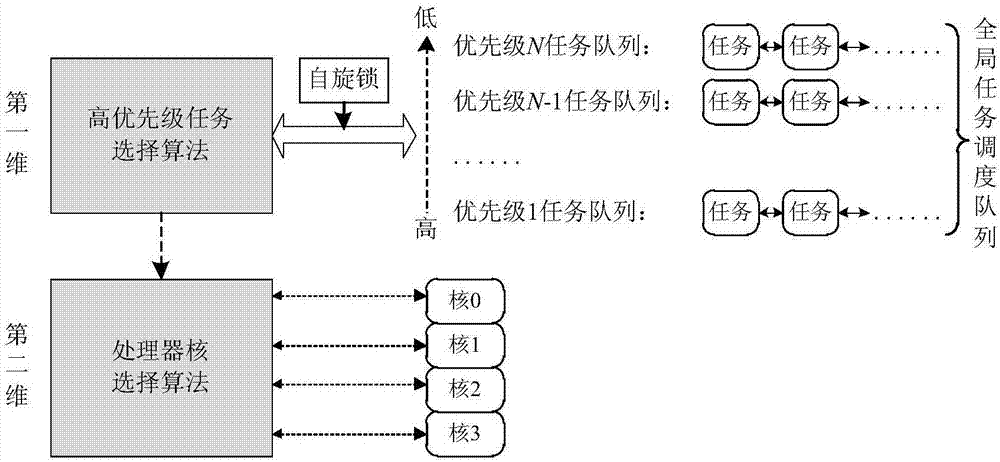

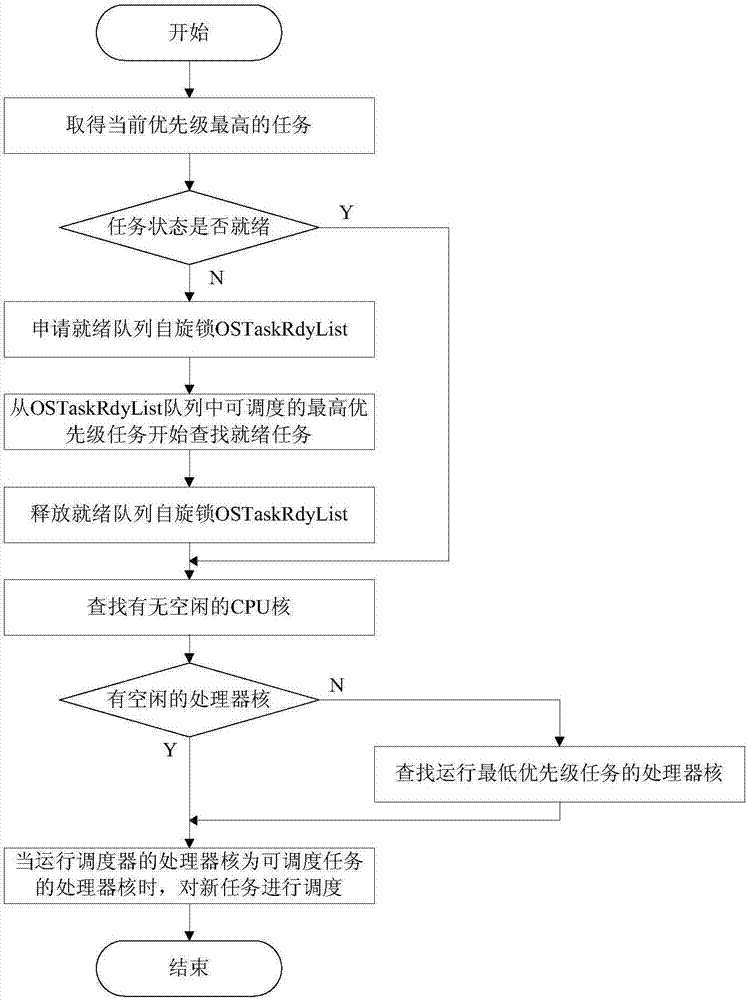

[0025] This embodiment adopts the global task scheduling queue, and the multi-processor core runs the scheduling algorithm independently; in the scheduling process, each processor core uses a spin lock to perform mutually exclusive access to the global task scheduling queue, thereby ensuring that the global task scheduling queue data Consistency and integrity; the scheduling algorithm adopts a two-dimensional scheduling model, that is, firstly select the highest priority task as the task to be scheduled, and then select the idle or lowest priority processor core as the processor core to run the scheduled task processor core.

[0026] Due to the separate s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More