Method and device for fault tolerance of grading instruction memory structure capable of actively writing back

A technology of instruction memory and memory, which is applied in the direction of instruments, response error generation, error detection/correction, etc., can solve the problems of increasing the vulnerability of digital signal processor instructions, simple instruction functions, abnormal program execution, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0072] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

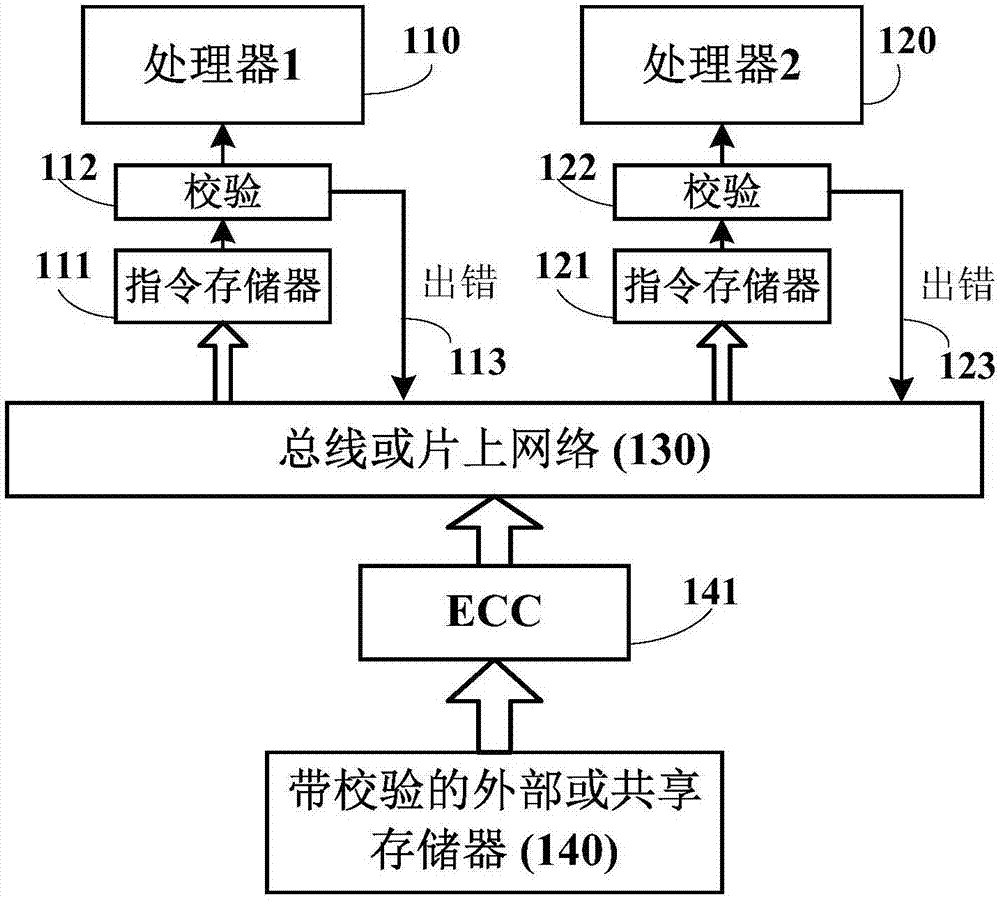

[0073] At present, the fault-tolerant hardening of memory by most processors is a "passive" method, as shown in the attached figure 1As shown, it illustrates the fault-tolerant process of "passive" loading of instruction memory. The system integrates two processors 110 and 120 . Each processor integrates independent instruction memory 111 and 121. Instruction word verification logic 112 and 122 is integrated between the processor and the instruction memory. Processors 110 and 120 are connected to external memory or shared memory 140 through on-chip bus or on-chip network 130 . The output instruction data of the external memory or the shared memory is passed through the error checking and correction logic ECC 141, and after the parity code, it is written into the instruction memory 111 and 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More