Patents

Literature

52results about How to "Low execution efficiency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

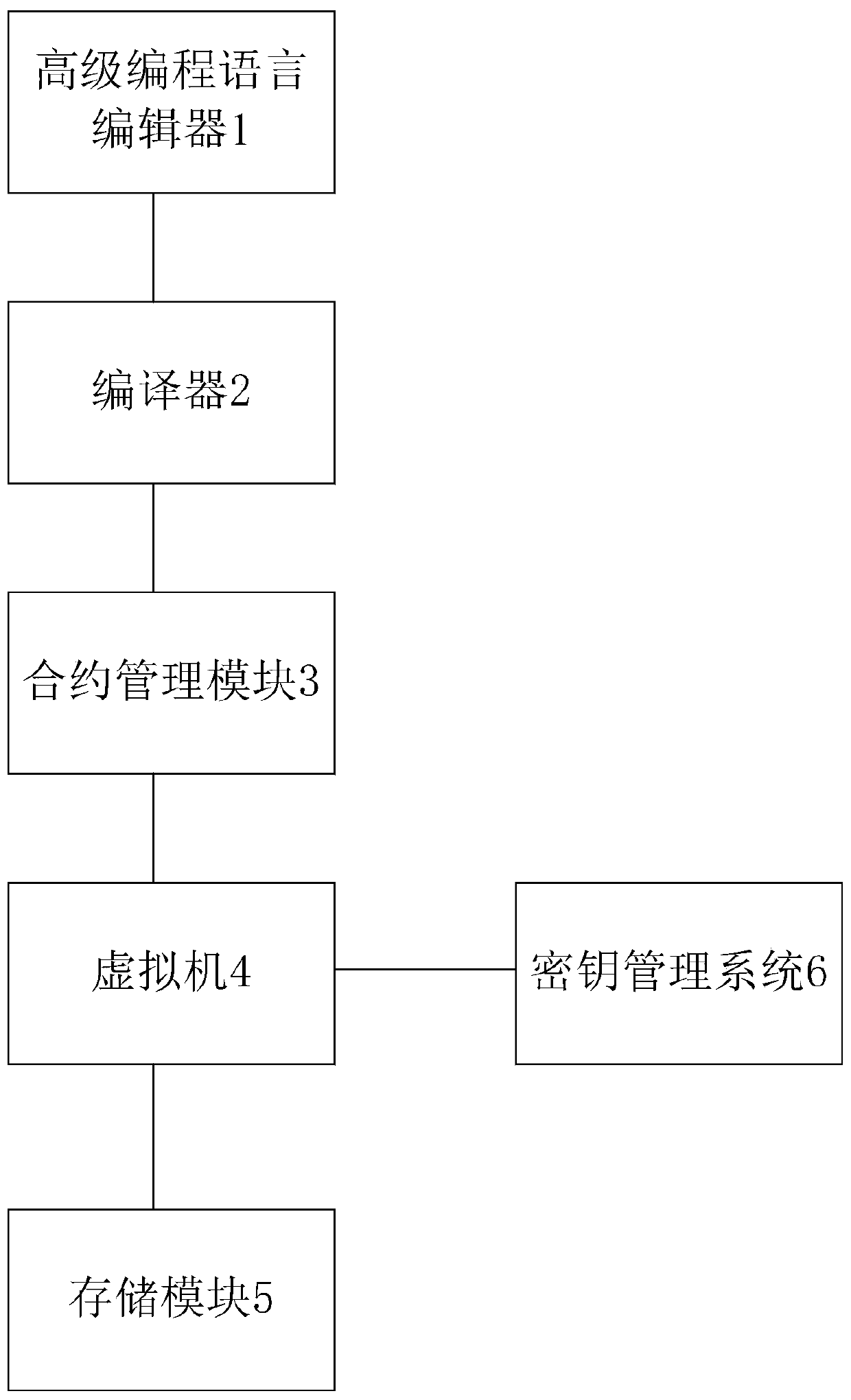

Method and a system for constructing a smart contract in a block chain

ActiveCN109766722APerformance bottleneckLow execution efficiencyDigital data protectionCode compilationData privacy protectionSmart contract

The invention relates to a method and a system for constructing an intelligent contract in a block chain. The method comprises the steps of 1, constructing an intelligent contract core system in the block chain; Step 2, contract upgrading based on the intelligent contract core system; Step 3, contract execution based on the intelligent contract core system; And step 4, performing data privacy protection based on the intelligent contract core system. The characteristics of data isolation, contract upgradable and data privacy protection are provided, and the requirements of enterprise organizations for service iterative upgrade, data governance and data security are better met.

Owner:梧桐链数字科技研究院(苏州)有限公司

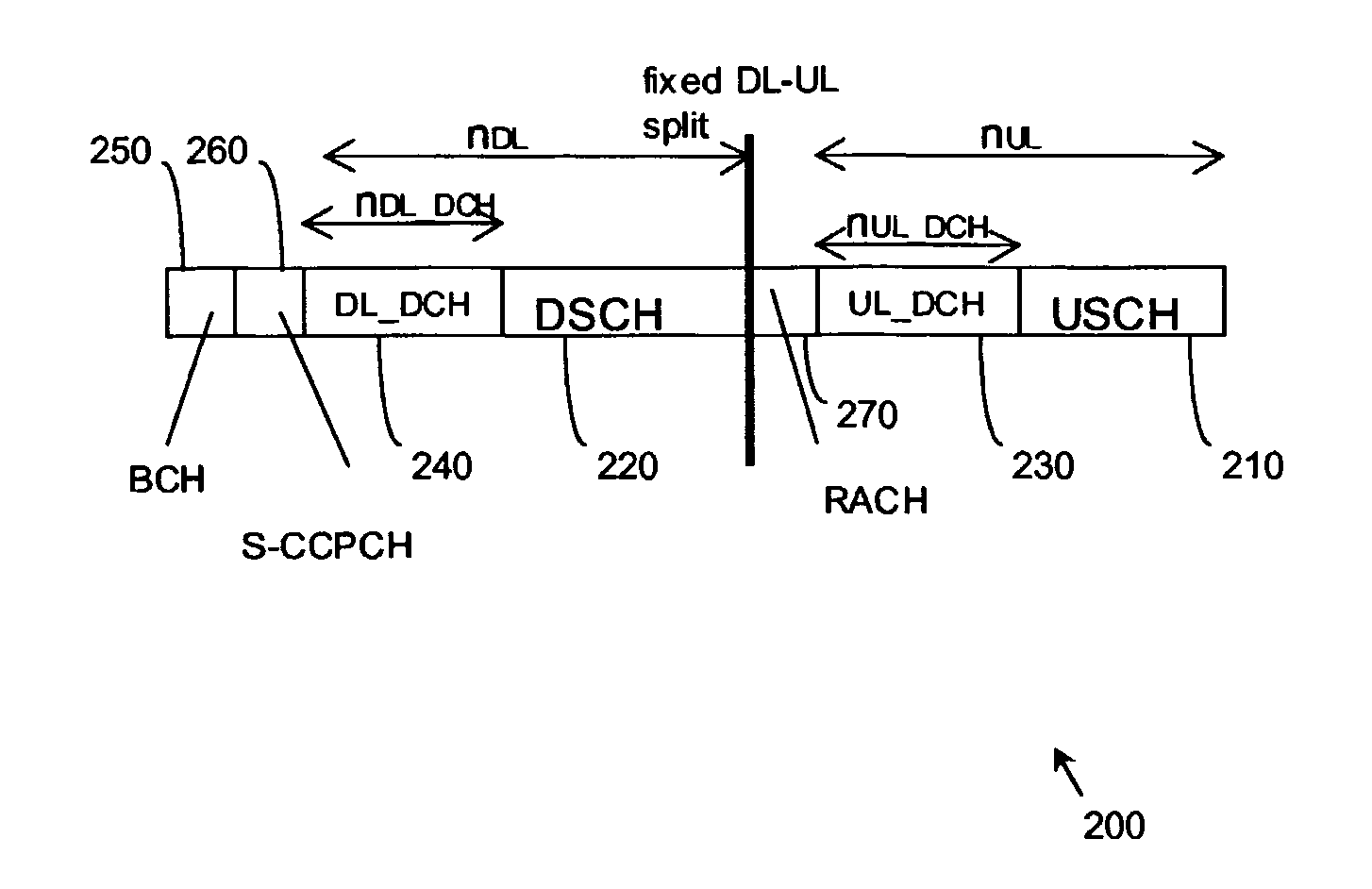

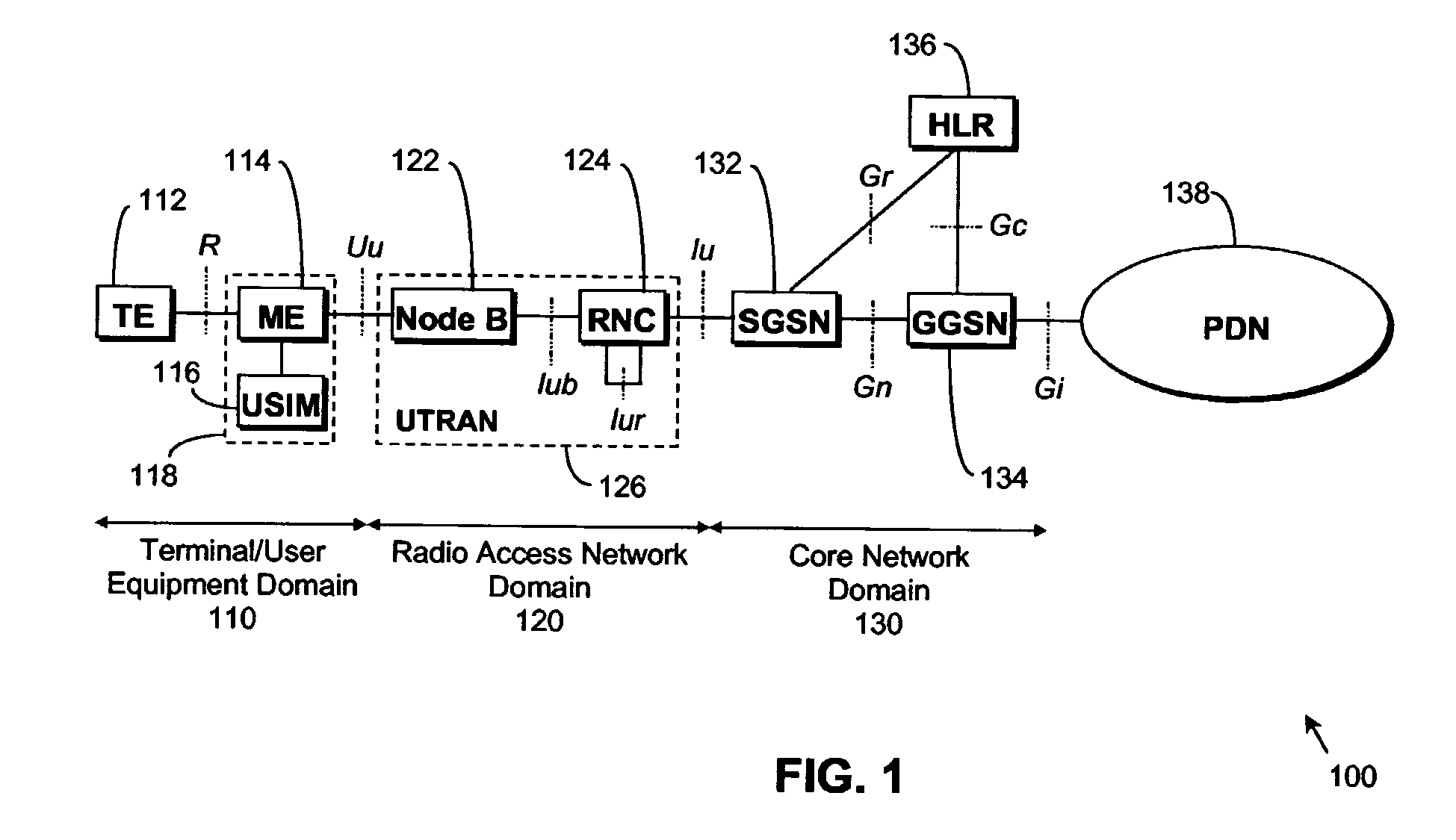

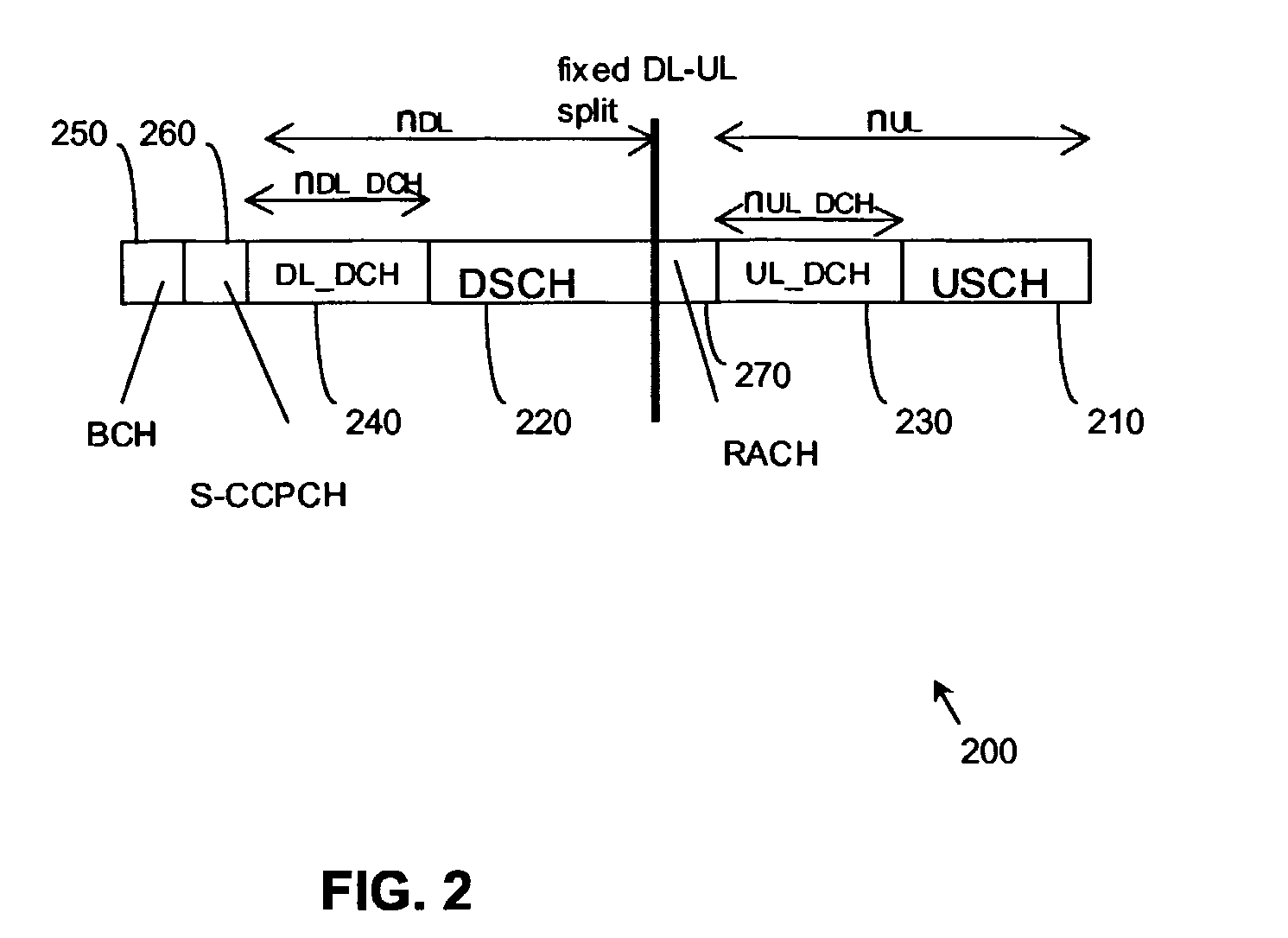

Method and Arrangement for Allocating a Dedicated Channel in a Cellular Communication System

ActiveUS20070259668A1Increase flexibilityImprove performanceRadio/inductive link selection arrangementsRadio transmission for post communicationQuality of serviceCommunications system

A dynamic channel assignment scheme for a TDD radio communication system (100) with coexisting dedicated (230; 240) and shared (210; 220) channels has segregated dedicated and shared channel mechanisms. Up to nDL<sub2>—< / sub2>DCH<sub2>—< / sub2>MAX / nUL<sub2>—< / sub2>DCH<sub2>—< / sub2>MAX dedicated downlink / uplink channel slots are granted, with the remainder of slots for shared channels. These maximum numbers accommodate the needs of conversational and streaming class traffic carried on shared channels. New slots can be claimed for dedicated channels (subject to this maximum) as required, taking the shared channel slot with the smallest timeslot. If the last DCH allocation in a slot is ended, the slot is freed for DSCH / USCH usage. This provides the following advantage(s): uplink algorithm metrics account for intercell interference, the most significant interference source in TDD mode systems, leading to greater capacity; midcall reallocation allows coverage and quality of service to a user to be maintained when a user moves from the centre of the cell to the cell edge; dynamic split between dedicated channel timeslots and shared channel timeslots allows the network to optimise radio resources according to traffic type, leading to an overall higher capacity when the network supports both dedicated channels and shared channels; alignment of the DCH slots across many cells improves the usefulness of measurements for DCA / CAC.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

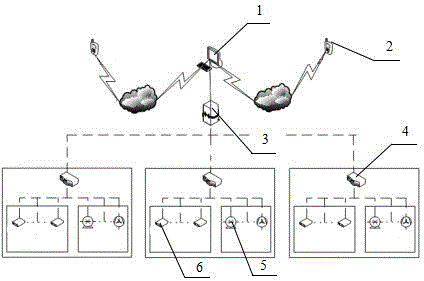

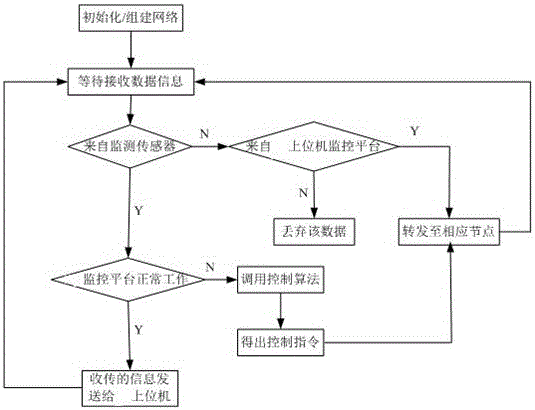

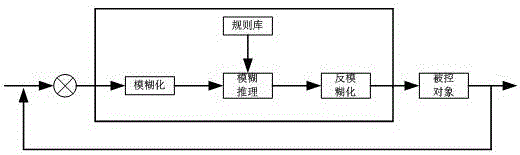

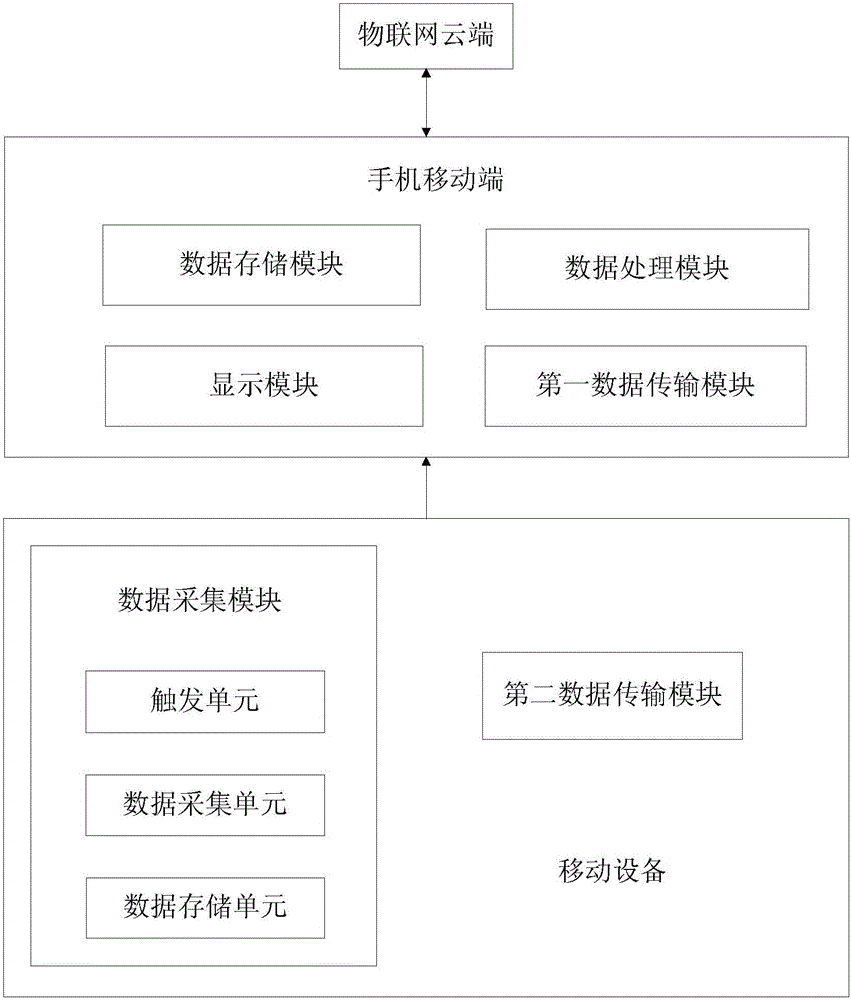

Livestock and poultry house environment monitoring system based on Internet of Things technology and working method thereof

InactiveCN106444925ARealize remote monitoringAchieve accessSimultaneous control of multiple variablesComputer monitoringThe Internet

The invention relates to a livestock and poultry house environment monitoring system based on the Internet of Things technology and a working method thereof. The system comprises a monitoring and executing module, a data transmission module, an upper computer monitoring platform 1 and a mobile terminal. The monitoring and executing module is arranged in a livestock and poultry house and comprises a monitoring module 6 and an executing module. The data transmission module is a ZigBee wireless sensing module. The upper computer monitoring platform 1 comprises a real-time display module, a data storage module, a control module and an alarm module. The working method of the system includes the steps of information acquisition, data fusion, fuzzy control and instruction output. An optimal weighted data fusion algorithm is adopted for the data fusion step. The system and the working method thereof have the advantages that the system is supported by the Internet of Things technology and the fuzzy control technology, a ZigBee wireless sensing network, a TCP / IP network and a mobile communication network are fully utilized, and the intelligent livestock and poultry house environment monitoring system is provided. The system achieves access of the mobile phone terminal to ZigBee network monitoring data through an SIM900A module and the upper computer monitoring platform 1.

Owner:NANTONG UNIVERSITY

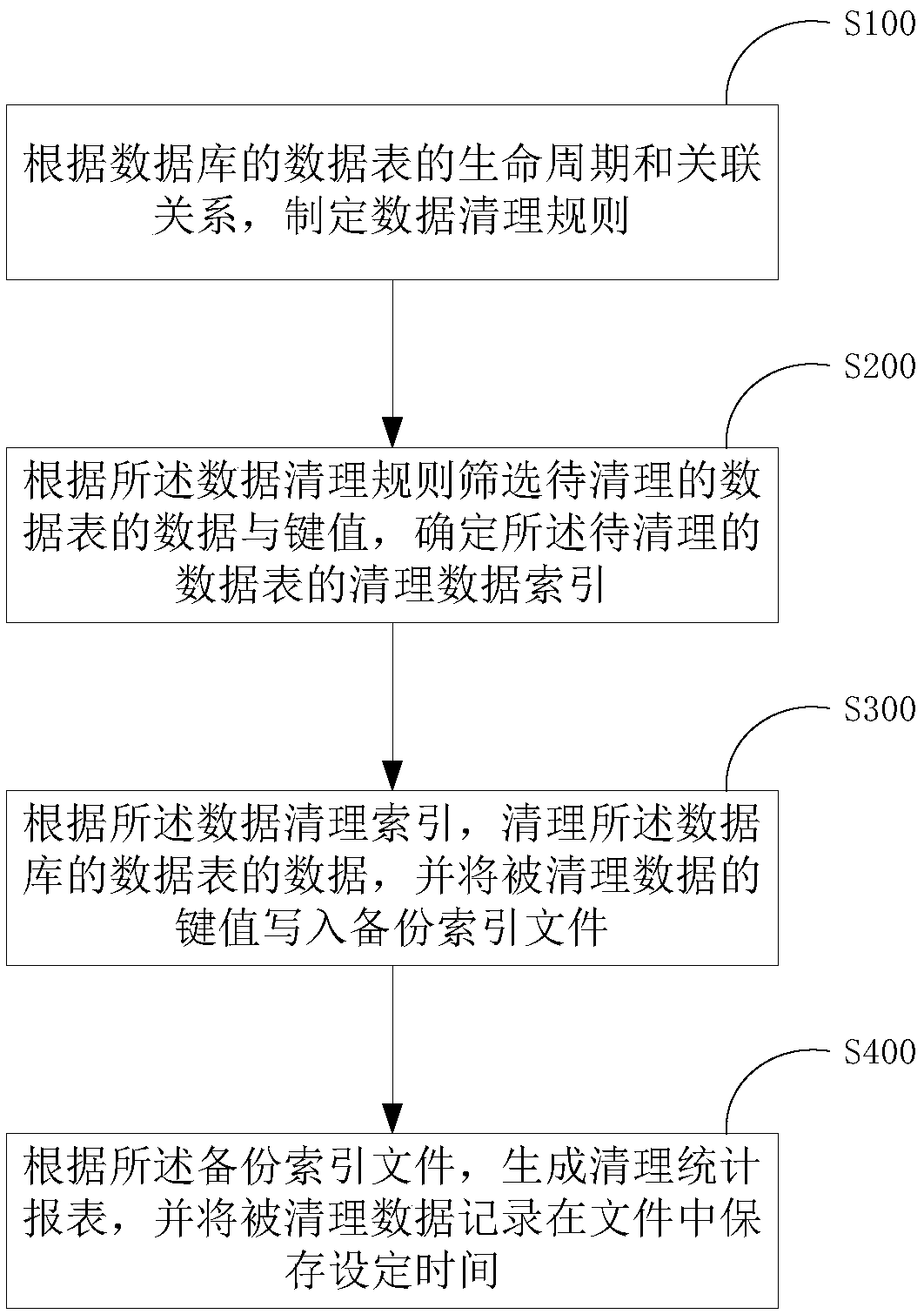

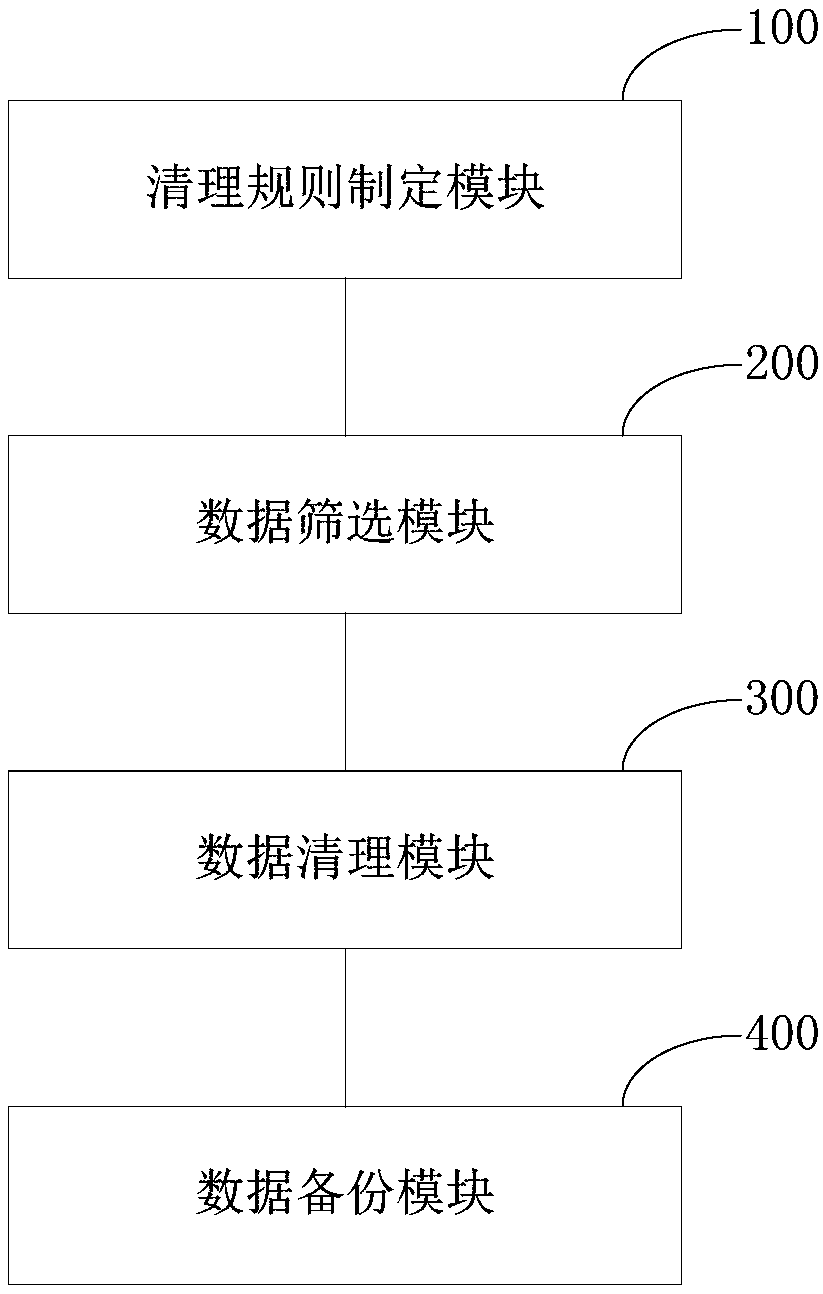

Bank system historical data cleaning method and device

ActiveCN108959400AGuaranteed uptimeGuaranteed safe operationFinanceSpecial data processing applicationsEnvironmental systemsSafe operation

The invention provides a bank system historical data cleaning method and device, used for cleaning historical data of a database data table. The bank system historical data cleaning method comprises the following steps: formulating a data cleaning rule according to the life cycle and association relationship of the data table of the database; screening data and key values of the data table to be cleaned according to the data cleaning rule, and determining the cleaned data index of the data table to be cleaned; cleaning the data of the data table of the database according to the data cleaning index, and writing the key values of the cleaned data into a backup index file; and generating a cleaning statistics report and recording the cleaned data in the file to save for a set time according to the backup index file, so as to support recovering the file from the file as needed. Through the bank system historical data method and device disclosed by the invention, the cleaning of the historical data can be realized, and efficient and safe operation of the production environment system can be ensured; therefore, the impact of the historical data cleaning process on normal business applications is avoided to the greatest extent, and the probability of affecting the normal applications in the normal production environment after the data cleaning is reduced.

Owner:BANK OF CHINA

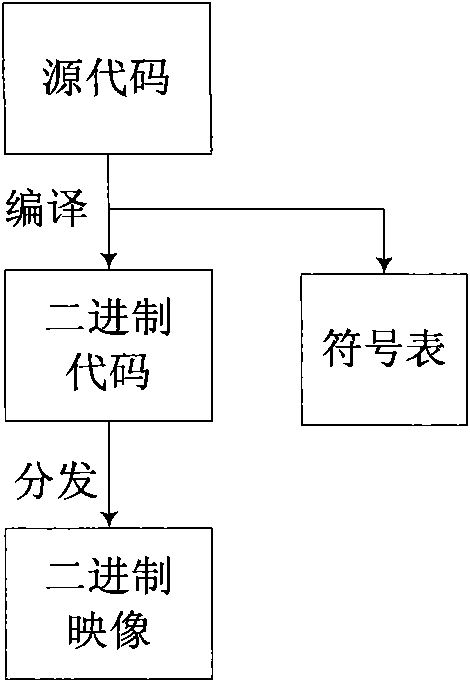

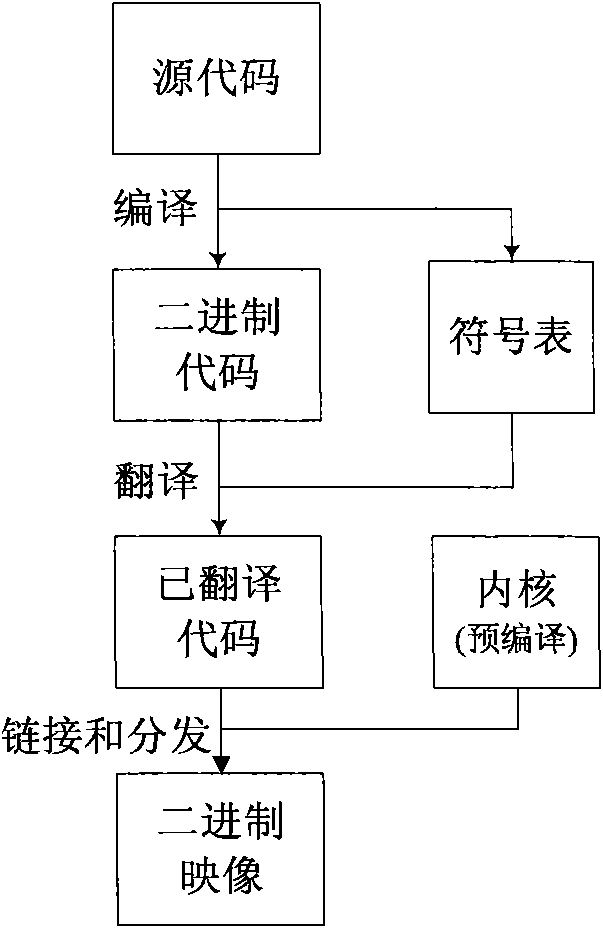

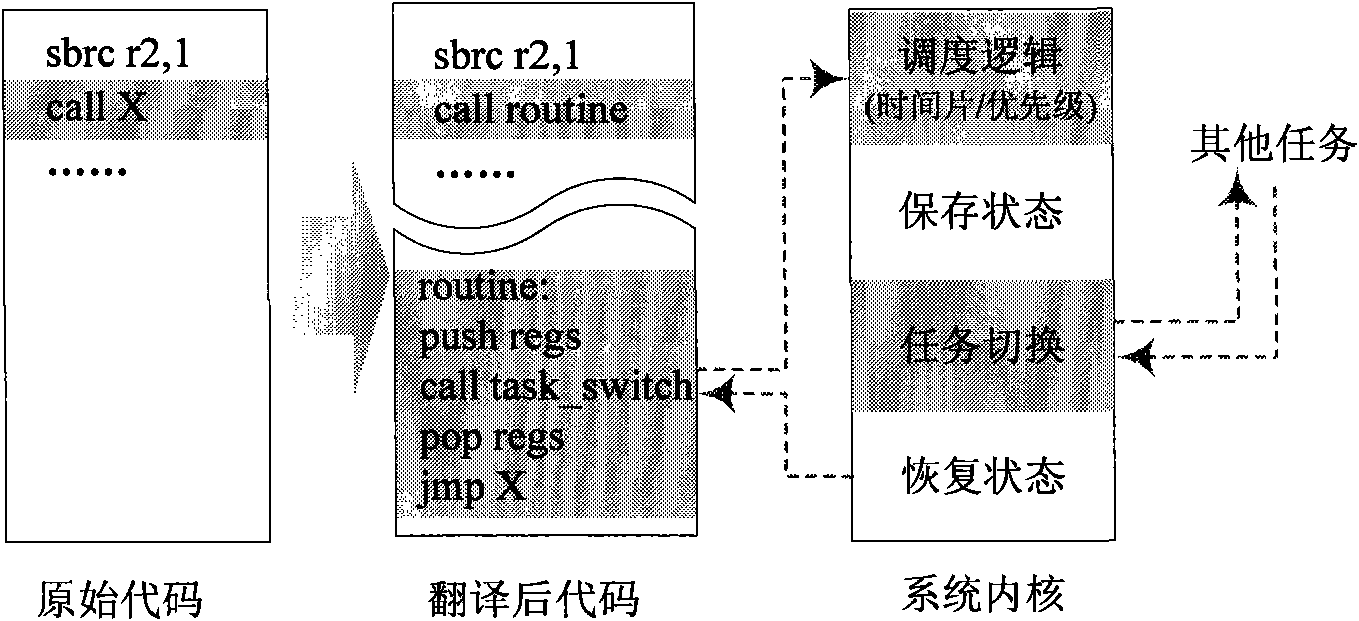

Task scheduling method for wireless sensor network node

InactiveCN101848549AEfficient translationSmall timeNetwork topologiesCode TranslationOperational system

The invention relates to a task scheduling method for a wireless sensor network node. The method is realized based on a special operating system based on a wireless sensor network, wherein the special operating system comprises a binary code translation tool and an operating system kernel, the binary code translation tool runs on a base station node and provides a pretreatment for an application program; the operating system kernel runs on a sensor node and provides a series of kernel services; and the binary code translation tool and the operating system kernel act together to realize preemptive multi-task scheduling in the sensor node. The task scheduling method overcomes defects in the prior art, and realizes functions similar to the time-sharing, concurrent and preemptive multi-task scheduling functions of the traditional operating system. Each task has an independent time slice in the execution process, the information of the time slice is maintained by the operating system, the task does not need to concede the execution right, and the operating system can automatically suspend the task used by the time slice and switch to another task, thereby meeting the multi-task requirement of the application program.

Owner:NAT UNIV OF DEFENSE TECH

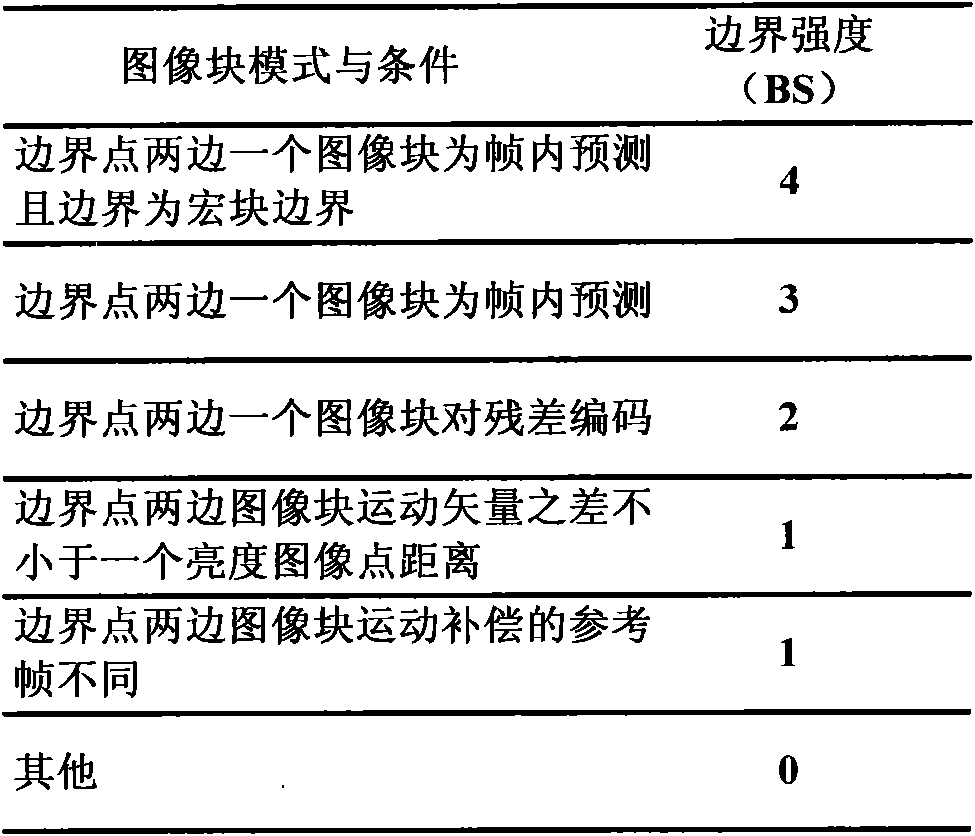

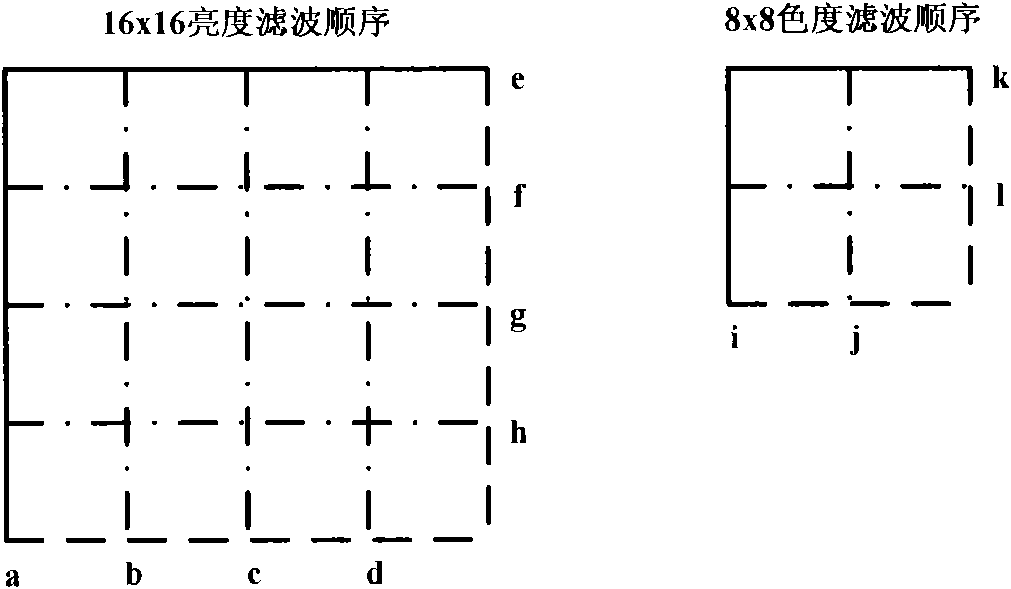

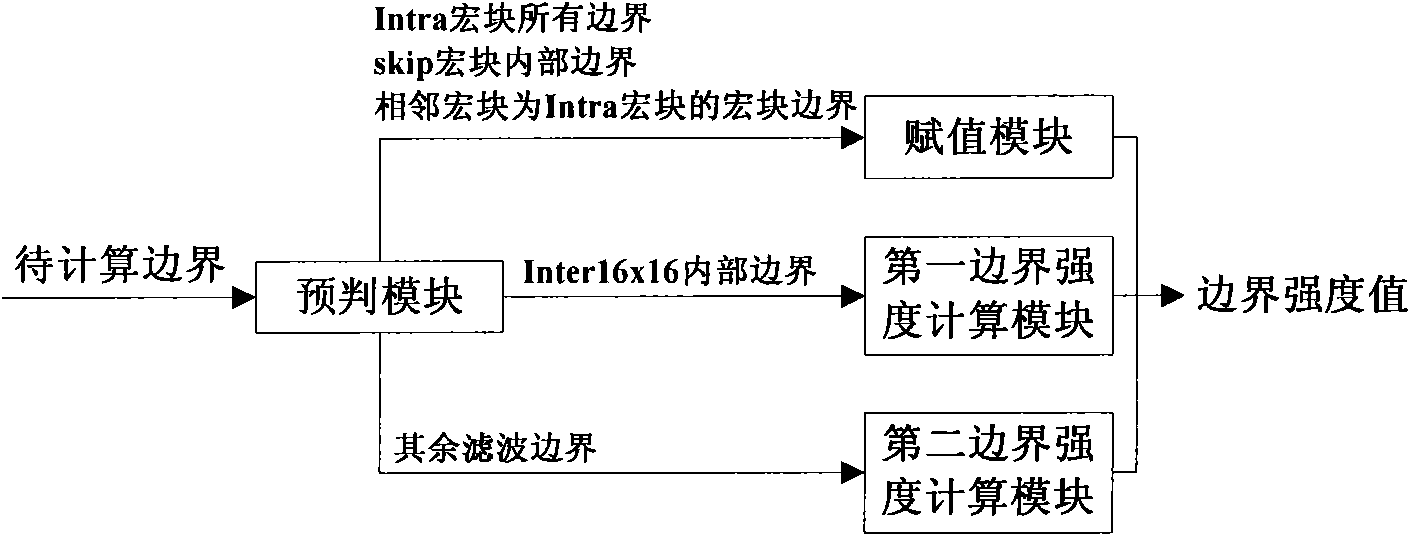

H.264 standard-based deblocking filter boundary strength computing device and method

ActiveCN102316318ALow execution efficiencyReduce the number of conditional judgmentsTelevision systemsDigital video signal modificationUltimate tensile strengthComputer science

The invention discloses a H.264 standard-based deblocking filter boundary strength computing device and method, which are used for computing boundary strength of boundary points during H.264 deblocking filtering. According to the invention, the boundary point with same modes are pre-judged according to a coding mode of current macroblocks and a coding mode of adjacent macroblocks and according tothe condition that boundaries of the macroblocks exist, and can be directly assigned. For the boundaries which can not be directly assigned, logic operation and arithmetic operation are adopted for replacing skip judgment when the boundary strength is computed. The invention has the advantages of being capable of remarkably reducing a large quantity of repetitive computation and complex conditionjudgment of a deblocking filtering link of the H.264 standard and increasing program execution efficiency, and is especially suitable for embedded processors such as a DSP (Digital Signal Processor).

Owner:SOI MICRO CO LTD

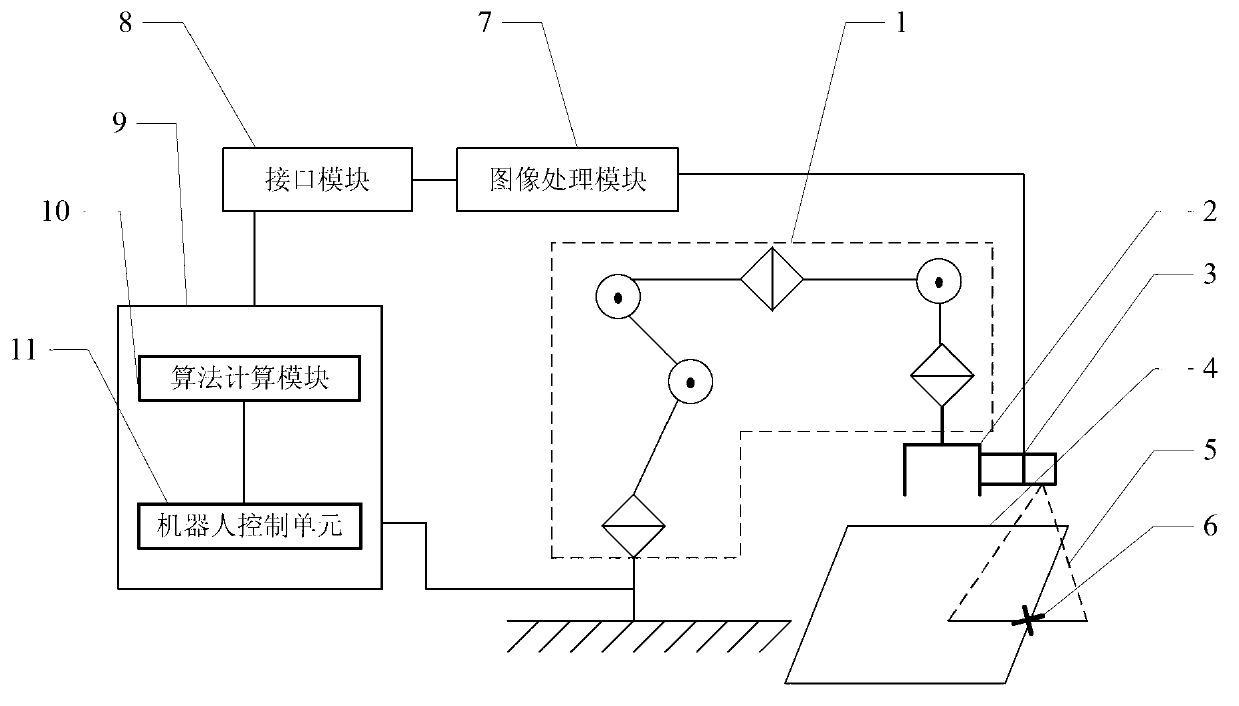

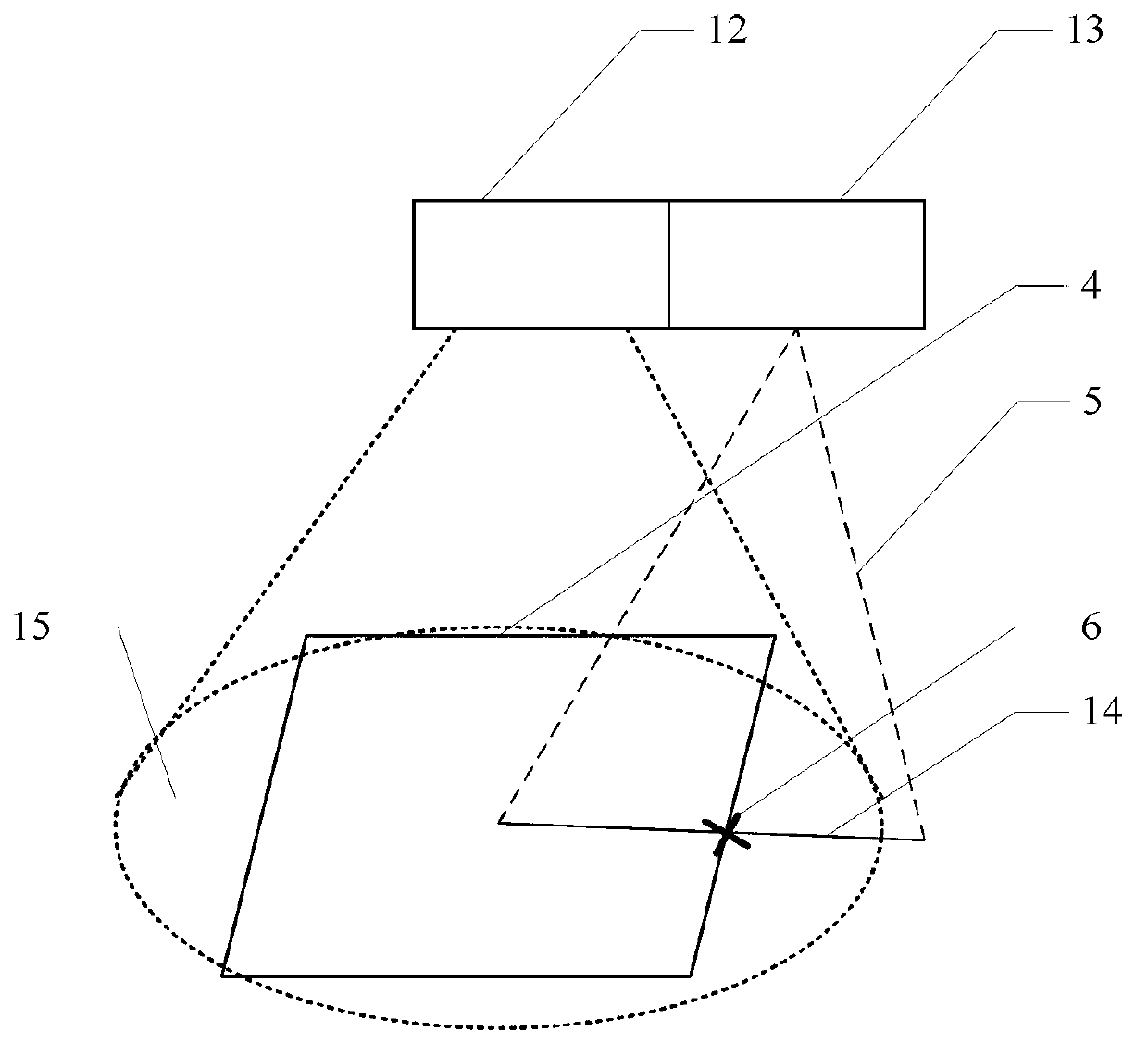

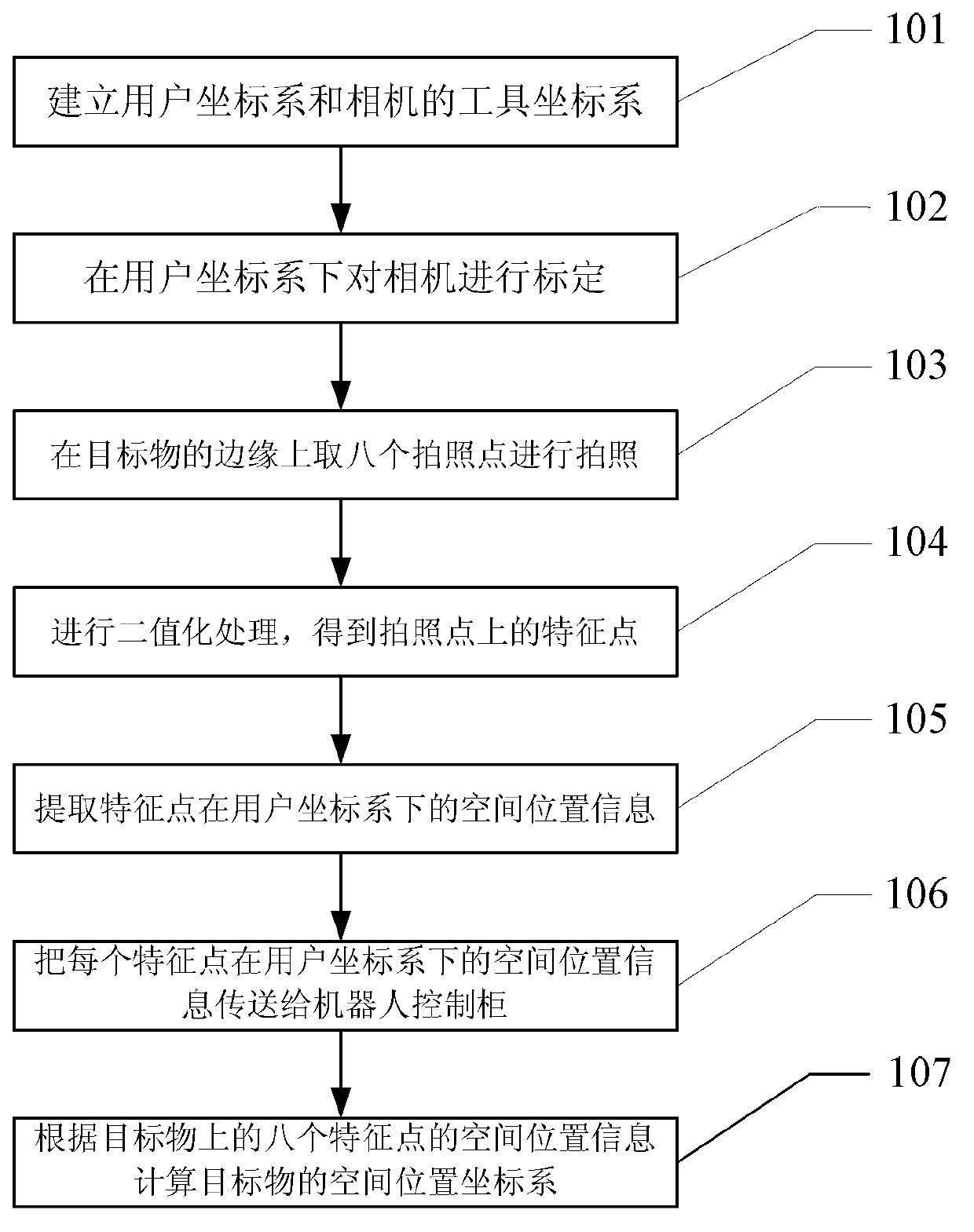

Space positioning system for intelligent assembly and space positioning method for intelligent assembly

ActiveCN103278091AAchieve positioningHigh precisionUsing optical meansSpatial positioningPattern recognition

The invention discloses a space positioning system for intelligent assembly. The space positioning system for intelligent assembly can carry out space positioning on target objects which are complex in shape. The space positioning system for intelligent assembly comprises a robot control cabinet, a robot module, a 3DL camera, an image processing module, an algorithm calculating module and a positioned target object. The invention further discloses a space positioning method for intelligent assembly. The space positioning method for intelligent assembly comprises the steps of (1) building a user coordinate system and a tool coordinate system of the 3DL camera, (2) calibrating the 3DL camera in the user coordinate system, (3) taking eight photograph points in the edge of the target object to photograph, (4) carrying out binarization processing on photographed images of each point, and obtaining feature points of each photograph point, (5) extracting space position information of each feature point in the user coordinate system, (6) transmitting the space position information of each feature point in the user coordinate system to the robot control cabinet, and (7) calculating a space position coordinate system of the target object according to the space position information of the eight feature points on the target object.

Owner:SHANGHAI FANUC ROBOTICS

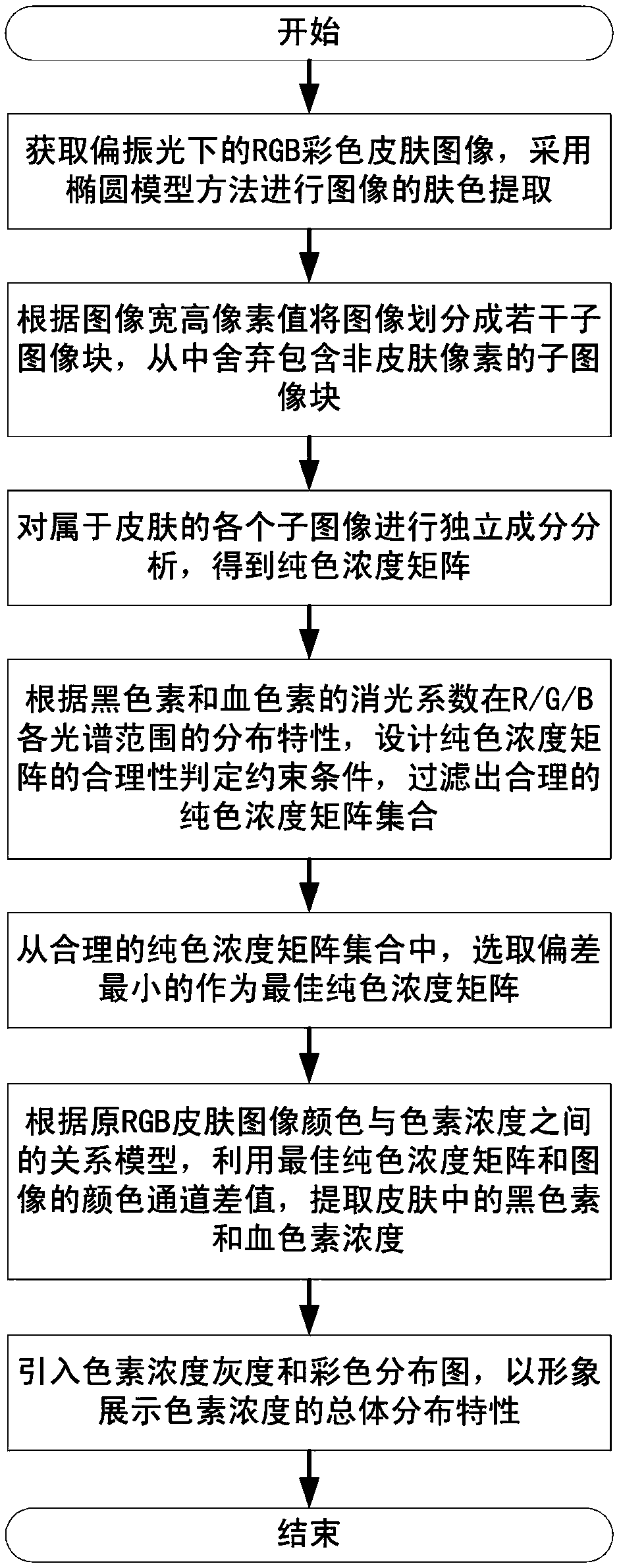

A pigment separation method of centralized image channel difference based on optical density space

ActiveCN109325938AEliminate distractionsResolve inaccuraciesImage enhancementImage analysisPrincipal component analysisSkin color

The invention discloses a pigment separation method of centralized image channel difference based on optical density space, which comprises the following steps of acquiring an RGB color skin image under polarized light and extracting skin color; dividing the image into a plurality of sub-image blocks and discarding the sub-image blocks containing non-skin pixels; obtaining the pure color density of each sub-image block; obtaining a matrix optimum solid color concentration matrix; calculating the concentrations of melanin and hemoglobin in the image, and introducing the gray distribution and color distribution of the pigment concentration. According to the present invention, a light source interference term in a conventional pigment separation model is eliminated without principal componentanalysis, and a simple and efficient constraint condition for judging the rationality of the pure color concentration matrix is designed, thereby avoiding, in the existing pigment separation algorithm, the inaccuracy and robustness of the pigment concentration extraction result due to the interference of light source intensity and the data loss in the principal component analysis process, as wellas the low efficiency of the algorithm due to the complexity of the determination process of the pure color concentration matrix.

Owner:武汉嫦娥医学抗衰机器人股份有限公司

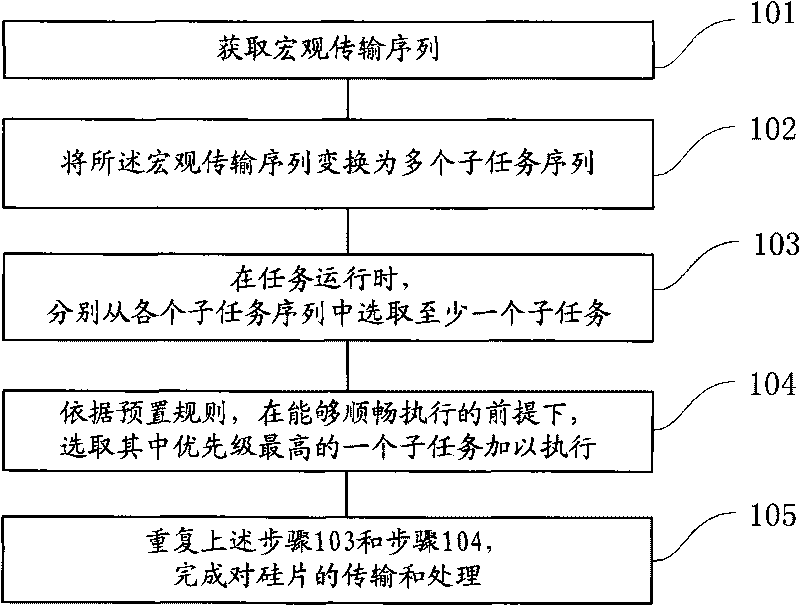

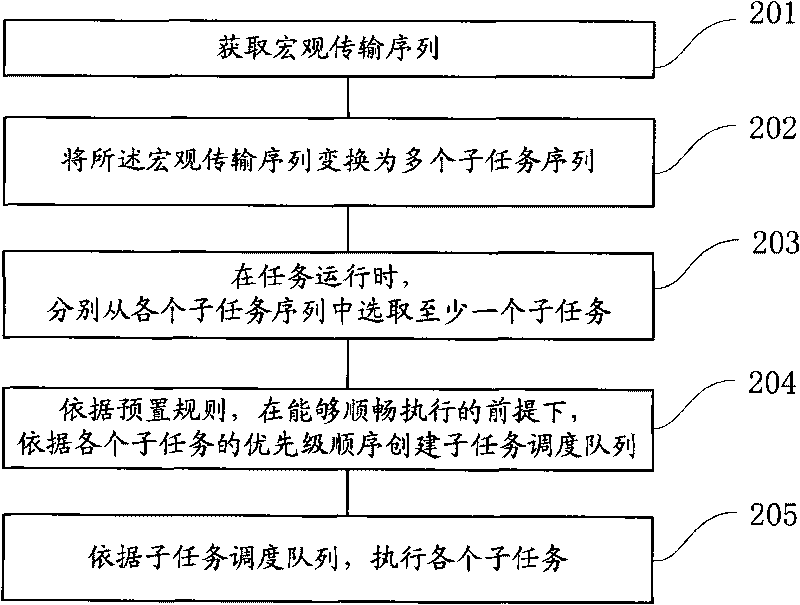

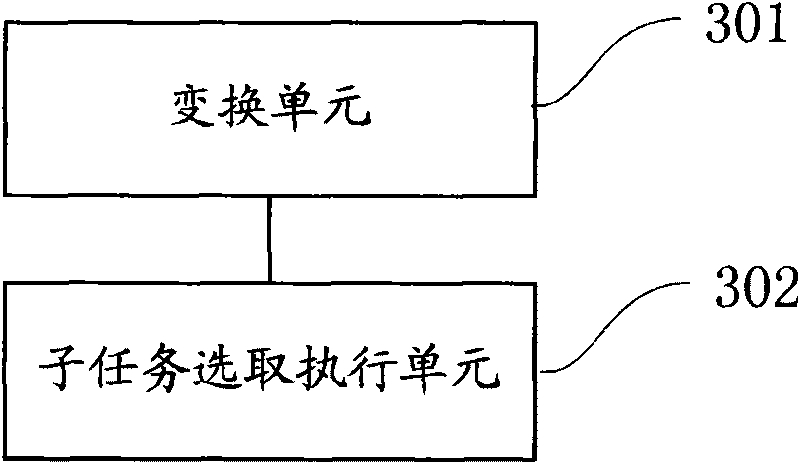

Silicon slice optimal scheduling method and device

ActiveCN101751025AImprove concurrencyImprove execution efficiencyTotal factory controlProgramme total factory controlSequence transformationOptimal scheduling

The invention discloses a silicon slice optimal scheduling method, which comprises the following steps: a, acquiring a macro transmission sequence; b, converting the macro transmission sequence into a plurality of sub task sequences; c, when a task is run, selecting at least one sub task from each sub task subsequence; d, according to preset rules, on the premise of smooth execution, executing a sub task with the highest priority; and e, repeating the steps c and d and completing the transmission and processing of silicon slices. In the invention, on the basis of the macro transmission sequence, a lower layer micro transmission sequence execution policy is optimized, so the concurrency of the execution of the sub tasks is improved, the execution efficiency of Job is improved and consequently yield of a machine is increased.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

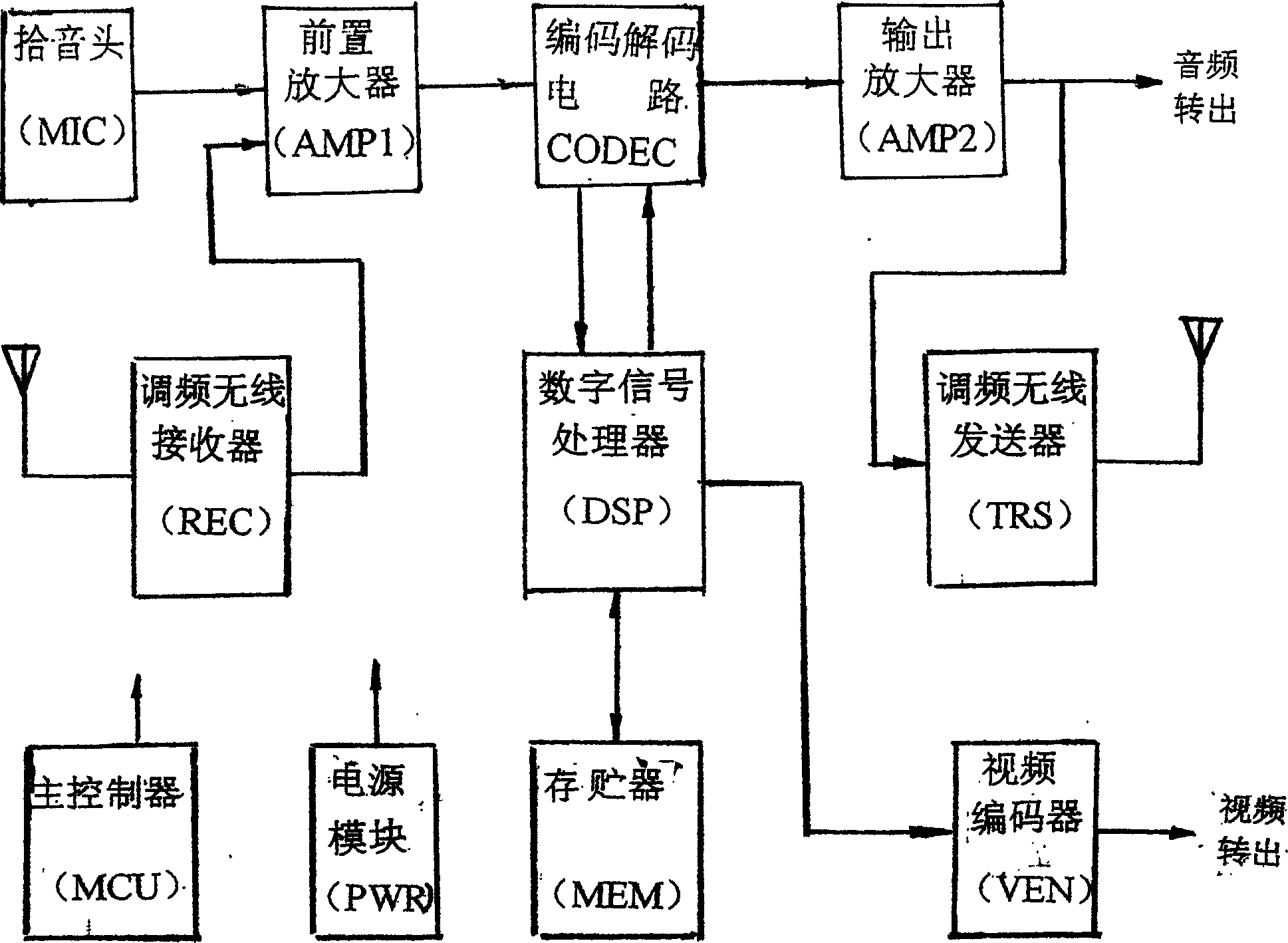

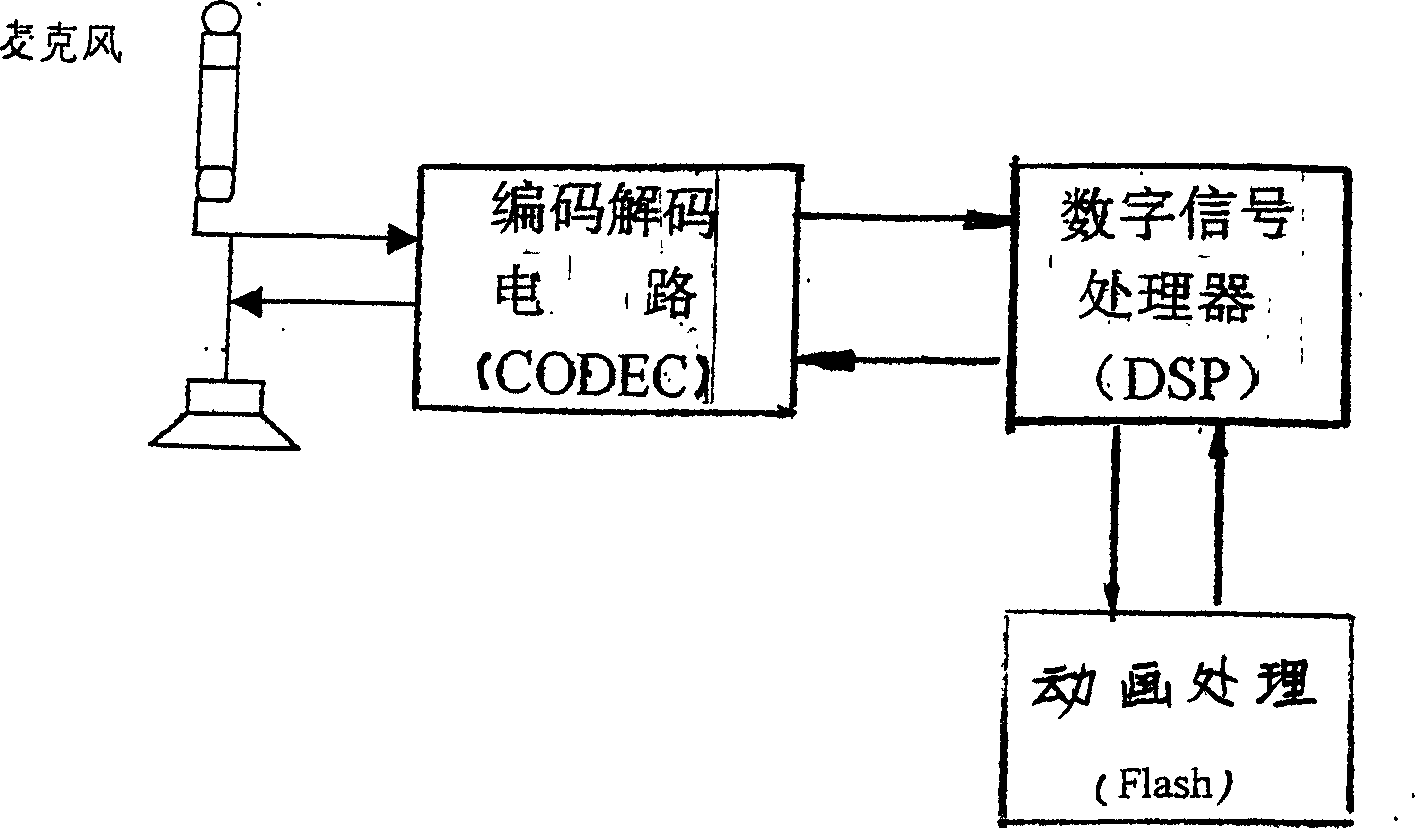

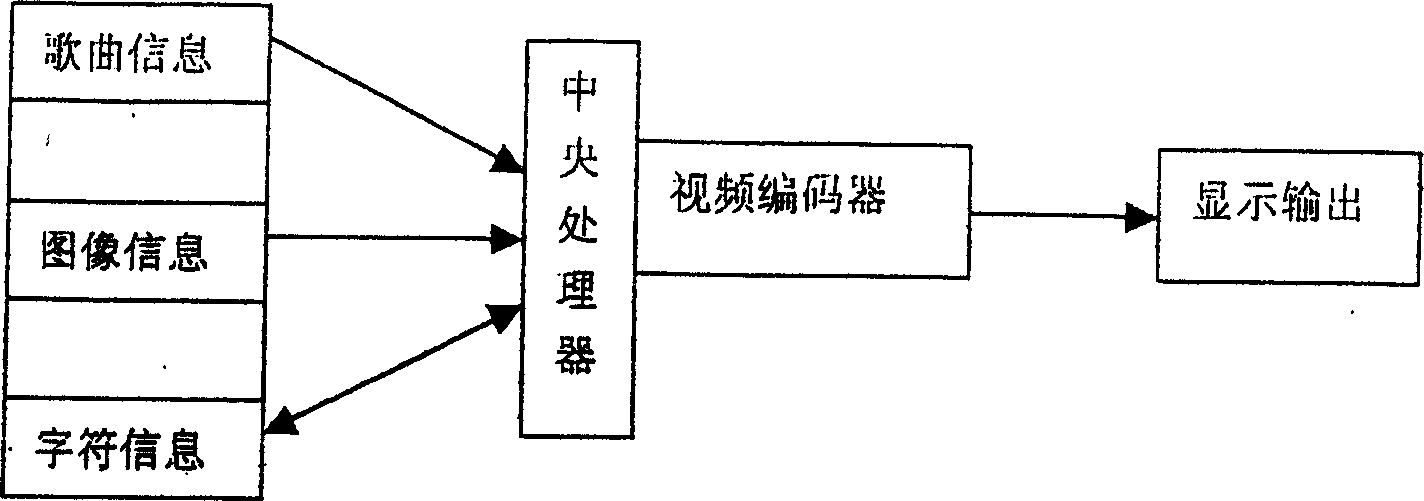

Portable (recordable) karaoke apparatus

InactiveCN1489148ASave storage spaceFast operationRecord information storagePackagingComputer hardwareImaging processing

The invention relates to Karaoke device, particular to device integrating the functions of storing, ordering, playing, singing and recording songs, and using Adaptive Differential Pulse Code Modulation (ADPCM algorithm) as well as MIDI format and special image processing method. Connecting to video and audio of TV set in any format system, user can enjoy Karaoke amusement at any moment and place at one's pleasure. The device possesses functional features of light and handy, large capacity, recordable and easy of operation.

Owner:上海歌升音像科技有限公司

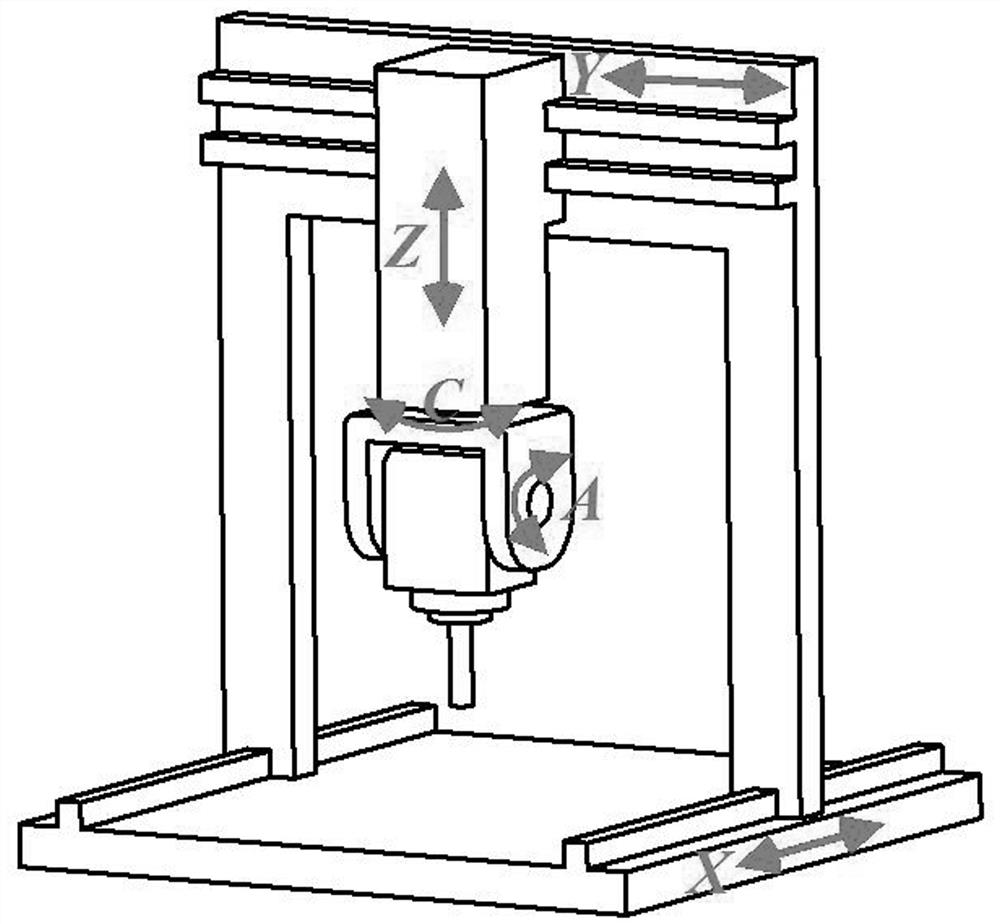

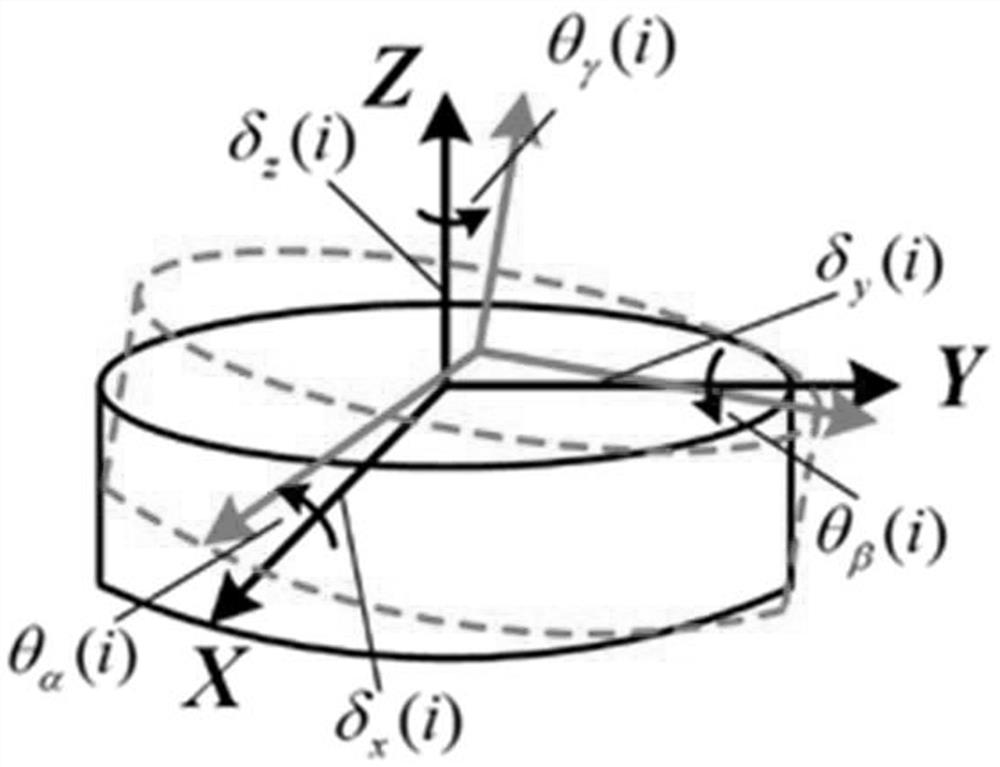

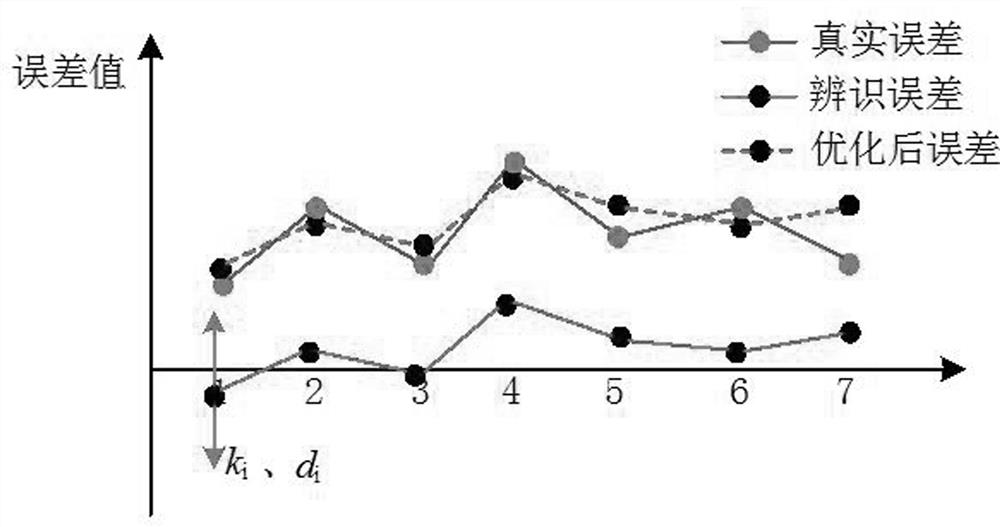

Method for quickly optimizing and compensating spatial positioning errors of rotating shaft of five-axis numerical control machine tool

ActiveCN112526927AImprove operational convenienceImprove detection efficiencyProgramme controlComputer controlTechnical supportRotational axis

The invention discloses a method for quickly optimizing and compensating spatial positioning errors of a rotating shaft of a five-axis numerical control machine tool. The method comprises the following steps: 1) establishing a spatial positioning error model; (2) forming an error database containing 12 geometric error vectors of the rotating shaft; 3) constructing a numerical control system rotating shaft space positioning error compensation table; 4) establishing a compensation data optimization model; 5) completing iterative optimization of the compensation data, and realizing optimal selection of a correction coefficient; 6) completing compensation for the geometric errors of the rotating shaft of the five-axis numerical control machine tool; and 7) updating geometric error correction data to an error database, detecting a linkage track of the rotating shaft, setting a positioning error threshold of the linkage track, and circularly implementing three steps of operations of detection, optimization and compensation to realize precision guarantee. According to the optimization compensation method, iteration of the machine tool space positioning error compensation value can be efficiently and conveniently completed, the automation degree is high, the adaptability of optimization compensation is good, and technical support is provided for machine tool machining precision.

Owner:CHENGDU AIRCRAFT INDUSTRY GROUP

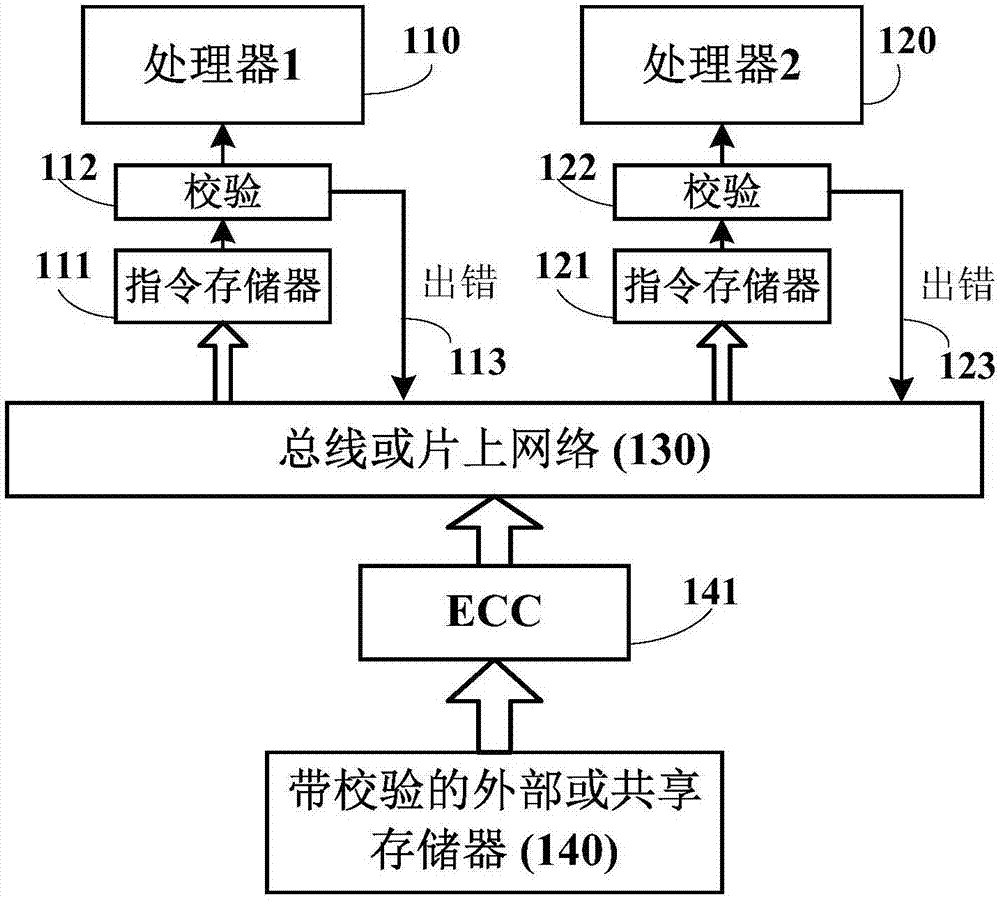

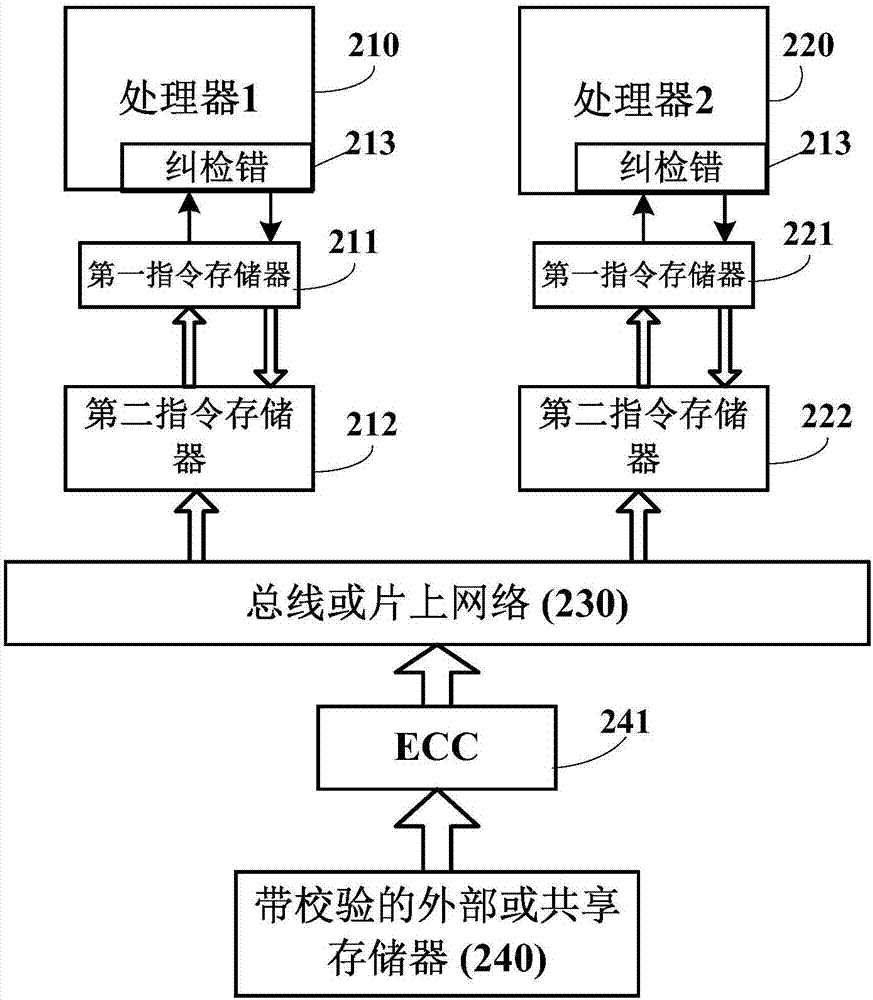

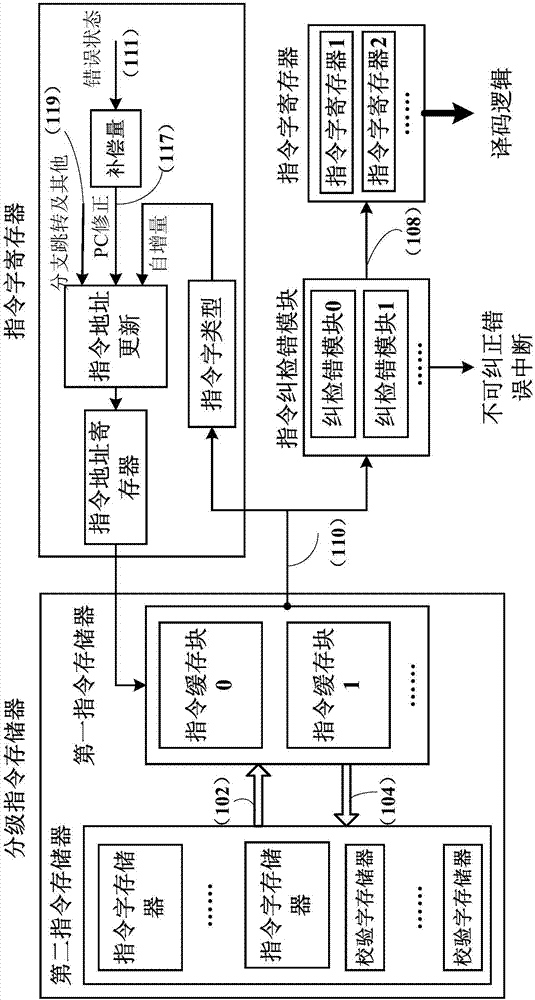

Method and device for fault tolerance of grading instruction memory structure capable of actively writing back

ActiveCN107885611AGuaranteed reliabilityImprove reliabilityNon-redundant fault processingInstruction memoryFault tolerance

The invention provides a method and a device for fault tolerance of a grading instruction memory structure capable of actively writing back. The device comprises a grading instruction memory, an instruction fault correcting and checking module, an instruction character register, and an instruction address register. The method comprises: 1, starting and operating a processor; 2, taking out instruction character data from the grading instruction memory; 3, sending the instruction character data to the instruction fault correcting and checking module; 4, determining a fault correcting and checking result to have no fault or have a correctable fault; if yes, continuing to perform a step 5; if no, jumping to step 10; 5, writing an instruction character to the instruction character register; 6,updating the instruction address register; 7, determining whether a correctable fault occurs; if yes, continuing to perform a step 8; if no, jumping to a step 9; 8, writing the instruction character data back to the grading instruction memory; 9, ending processing; jumping to the step 2, processing the address of the next instruction; 10, when the instruction character data has uncorrectable fault, suspending the processor. The method and the device realize fault tolerance of instructions and the instruction memory, and have relatively low hardware cost.

Owner:XIAN MICROELECTRONICS TECH INST

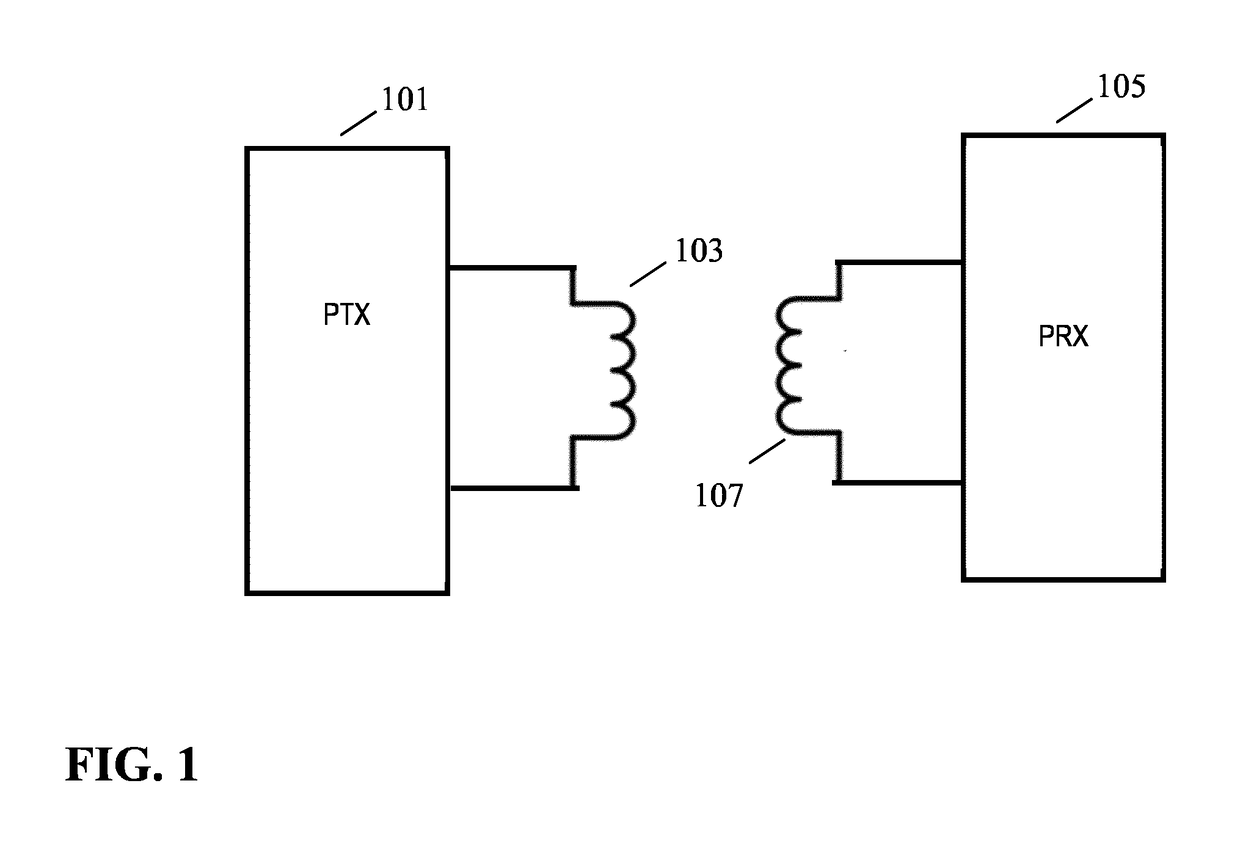

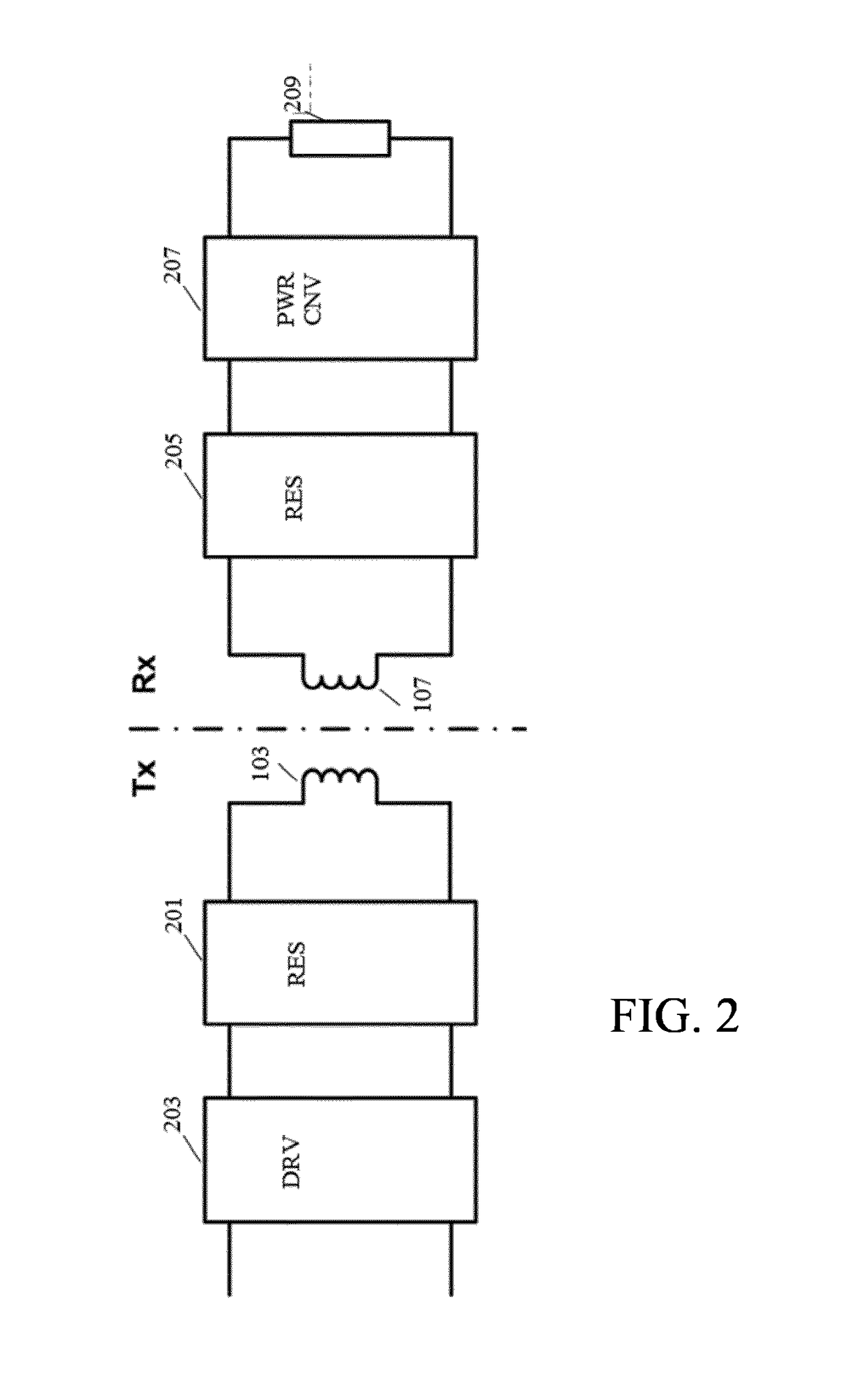

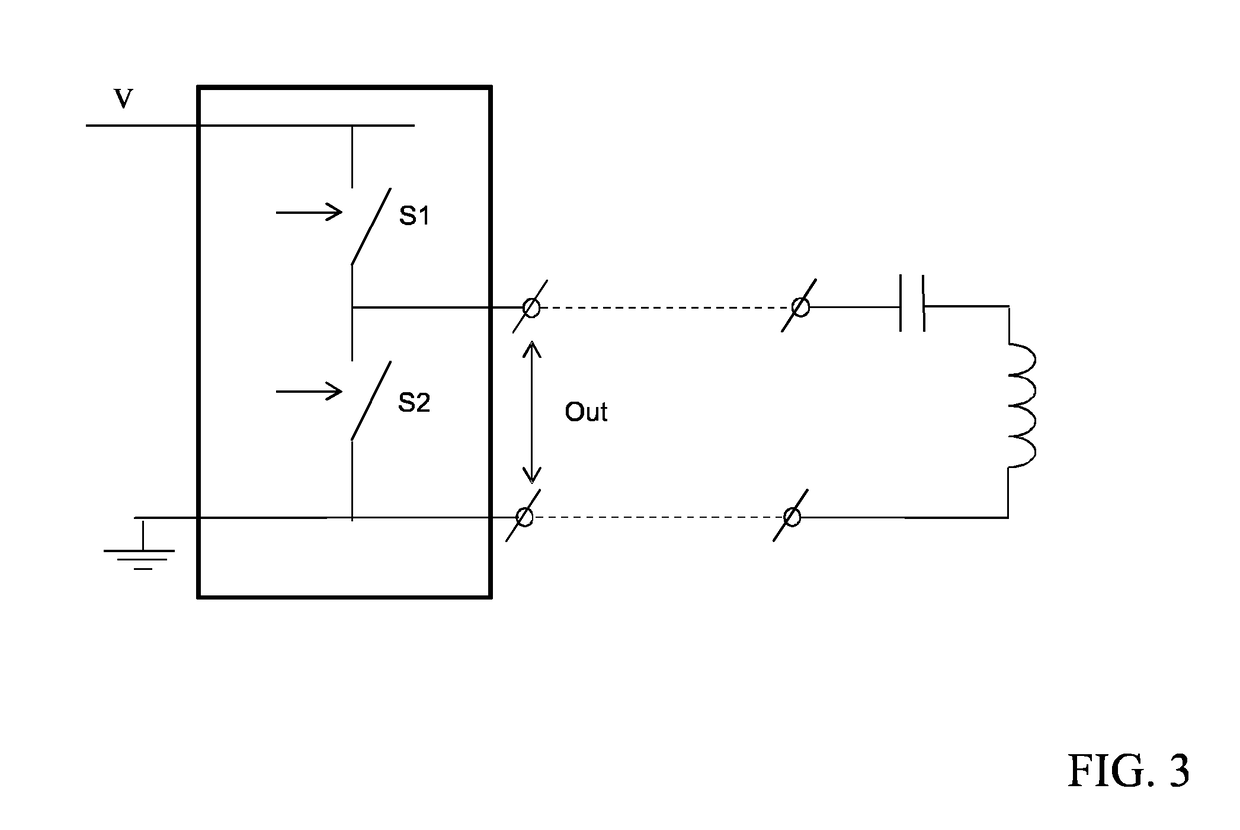

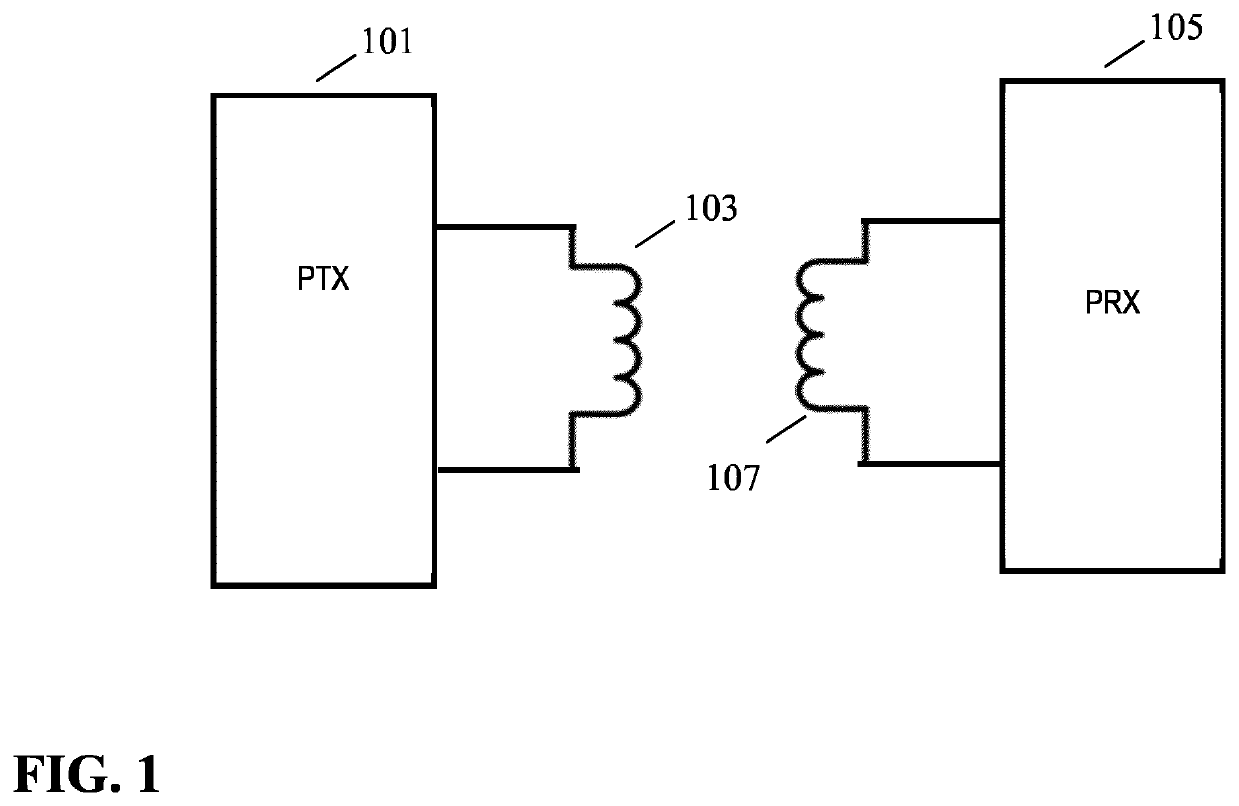

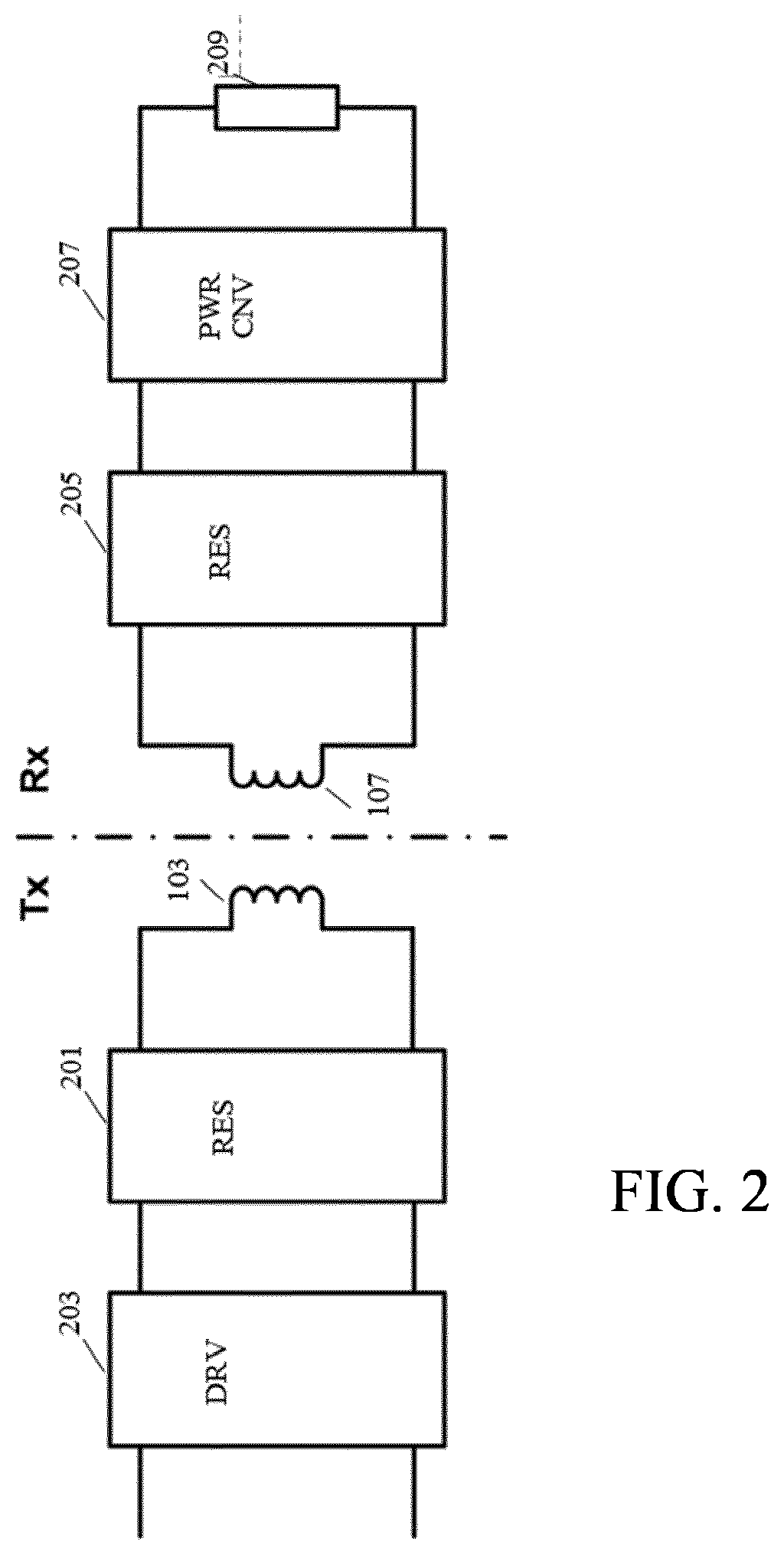

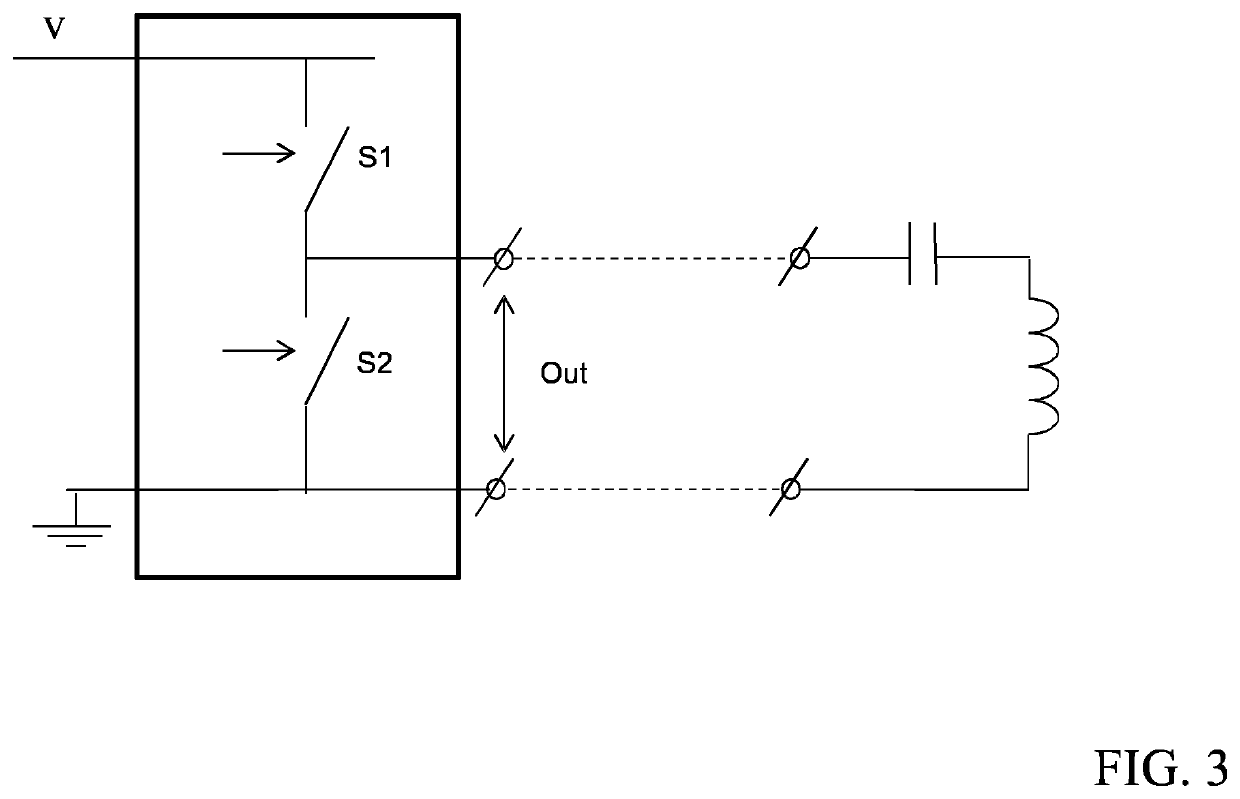

Wireless inductive power transfer

ActiveUS20180342899A1Improve performanceEffective regulationCircuit arrangementsElectric power transmissionTransmitter coil

A power transmitter (101) for inductively transferring power to a power receiver (105) comprises a resonance circuit (201) comprising a transmitter coil (103) for generating a power transfer signal. A sampler (511) samples a current through, or voltage over, the transmitter coil (103). A message receiver (509) receives messages load modulated onto the power transfer signal based on the samples. A driver (203) generates a drive signal for the resonance circuit (201) and a resonance modification circuit (505) reduces the resonance frequency of the resonance circuit (201) by slowing a state change for a resonating component of the resonance circuit (201) for a fractional time interval of the cycles of the drive signal. A sample time controller (513) controls the sample times in response to at least one of start-times and end-times of the fractional time intervals, and specifically may set the sample times to be within the fractional time intervals.

Owner:KONINKLJIJKE PHILIPS NV

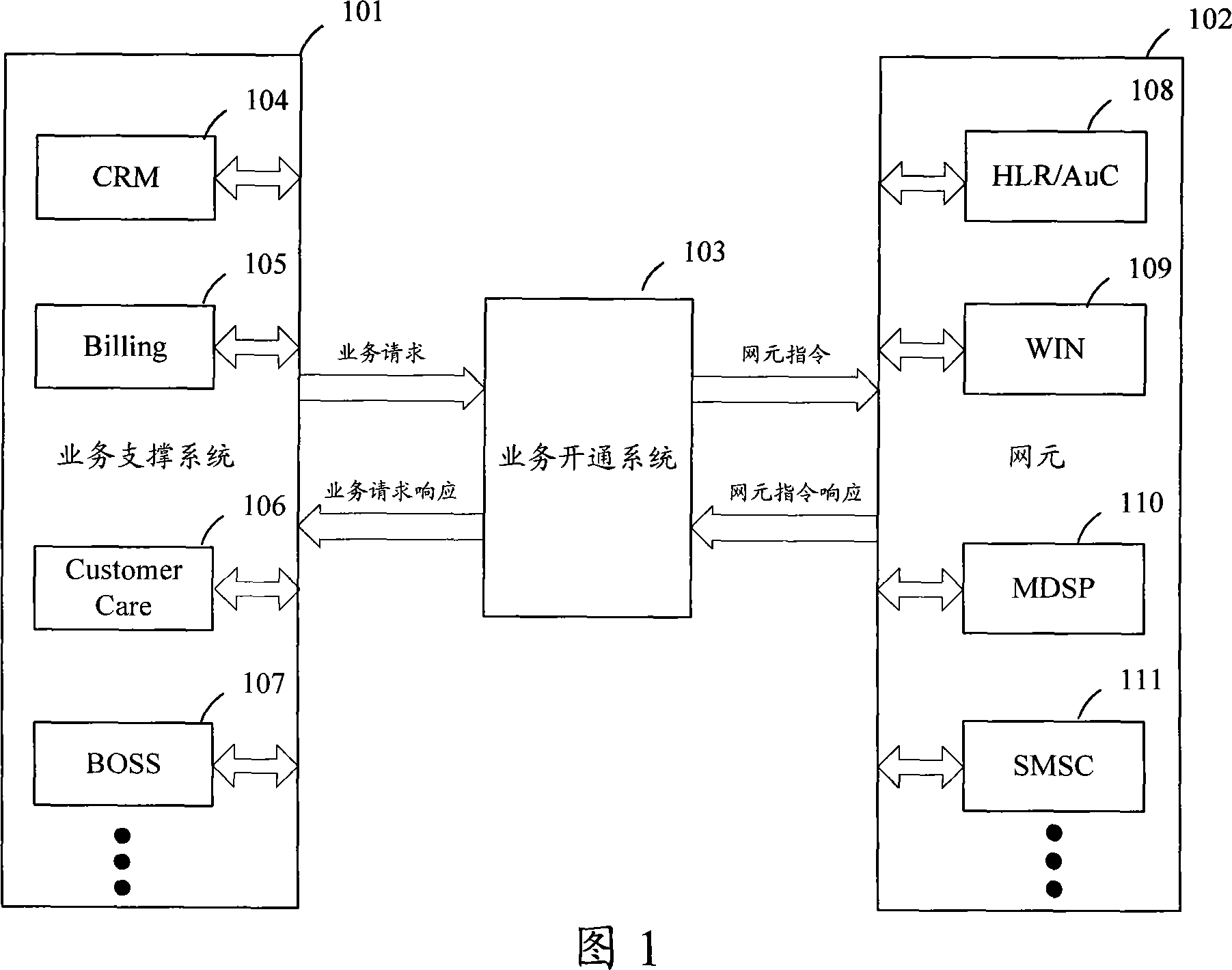

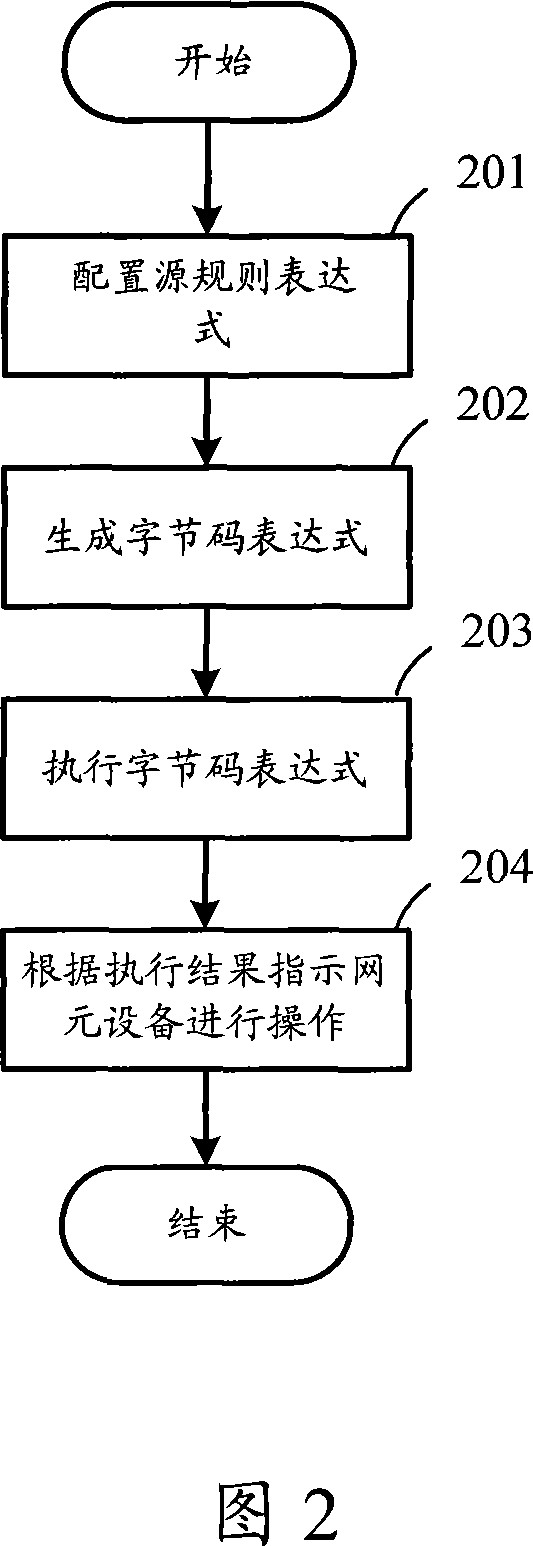

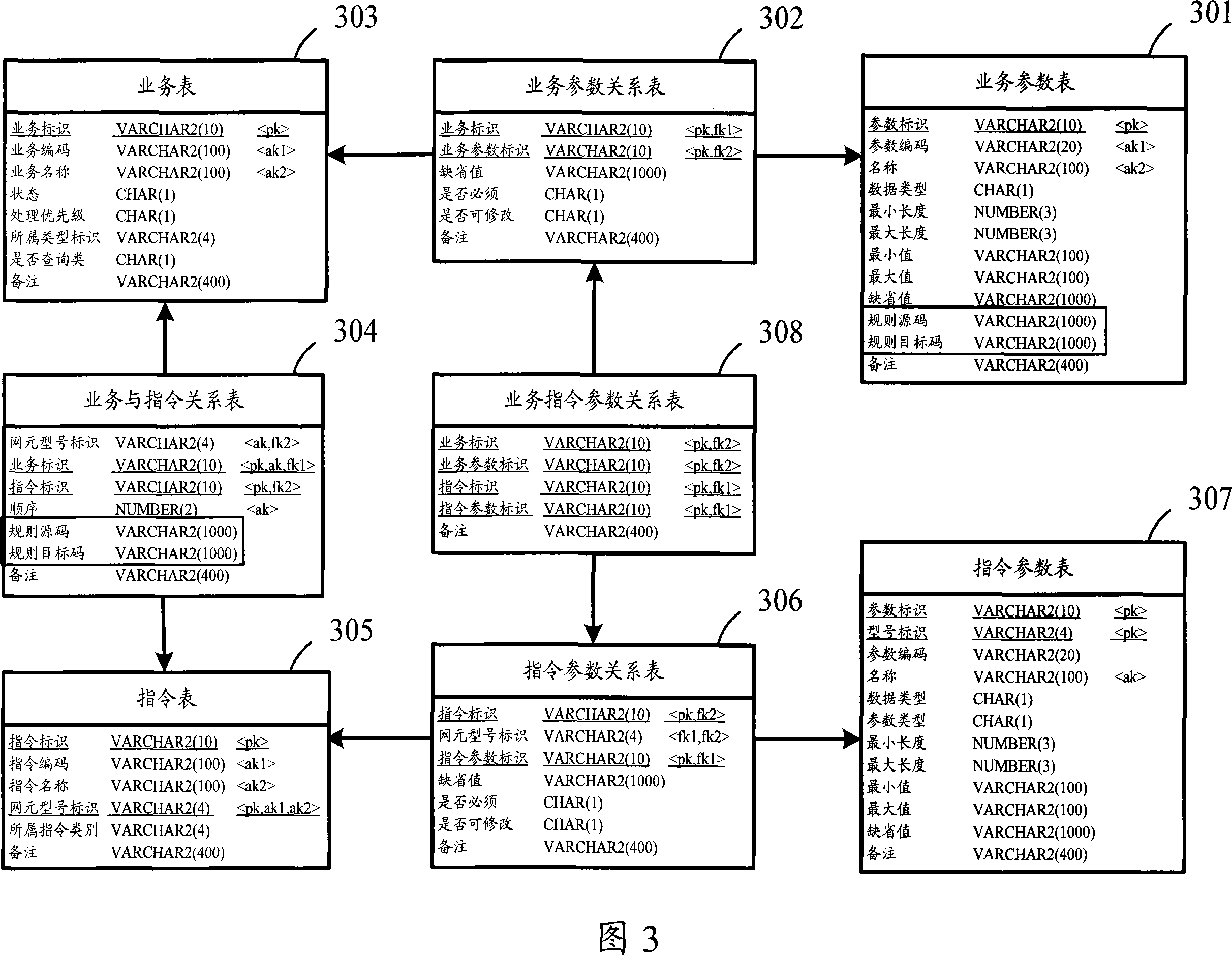

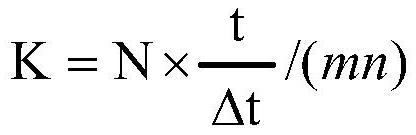

Method and apparatus for service fulfillment

InactiveCN101179772AImprove stability and scalabilityImprove service activation efficiencyRadio/inductive link selection arrangementsData switching networksByte

The invention provides a method of service opening, which includes the following steps: configuring source rule expressions based on service rules; transforming source rule expressions to expressions of bytes; implementing expressions of the bytes; indicating the network cell equipment required by service opening to be operated according to the implementation result of the expressions for the bytes. At the same time, the invention also provides a device for service opening corresponding to the method. Through the technical proposal of the invention, configuration of the new service can be flexibly and conveniently carried out in the service-opening system, thus greatly increasing the efficiency and stability of service opening.

Owner:HUAWEI TECH CO LTD

Space debris collision early warning method

PendingCN111861859AMeet timeliness requirementsLow costResource allocationToolsEarly warning systemRelative motion

The invention discloses a space debris collision early warning method, which is characterized by comprising a space debris positioning system and an early warning system; the early warning system is used for calculating the relative motion trail of space debris under a spacecraft orbit coordinate system by utilizing spacecraft orbit information through space debris observation information detectedby a microwave radar on a spacecraft, calculating the minimum distance of the space debris relative to the spacecraft in the future T time, giving early warning information by judging the minimum distance for multiple times, and starting an orbit avoidance program for avoiding collision. Compared with the prior art, the invention aims to provide the space debris collision early warning method, which is provided for the collision harm of the space debris to the satellite, has a good actual processing effect, and can be widely applied to space debris monitoring.

Owner:昆宇蓝程(北京)科技有限责任公司 +1

A template selection and accelerated matching method for nonlinear color space classification

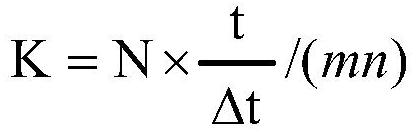

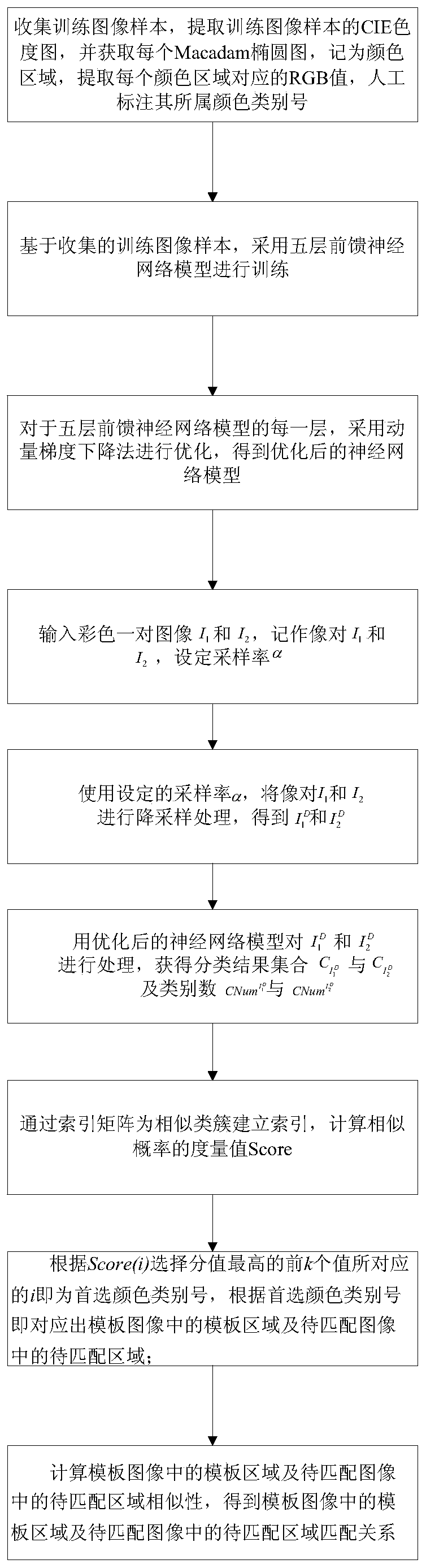

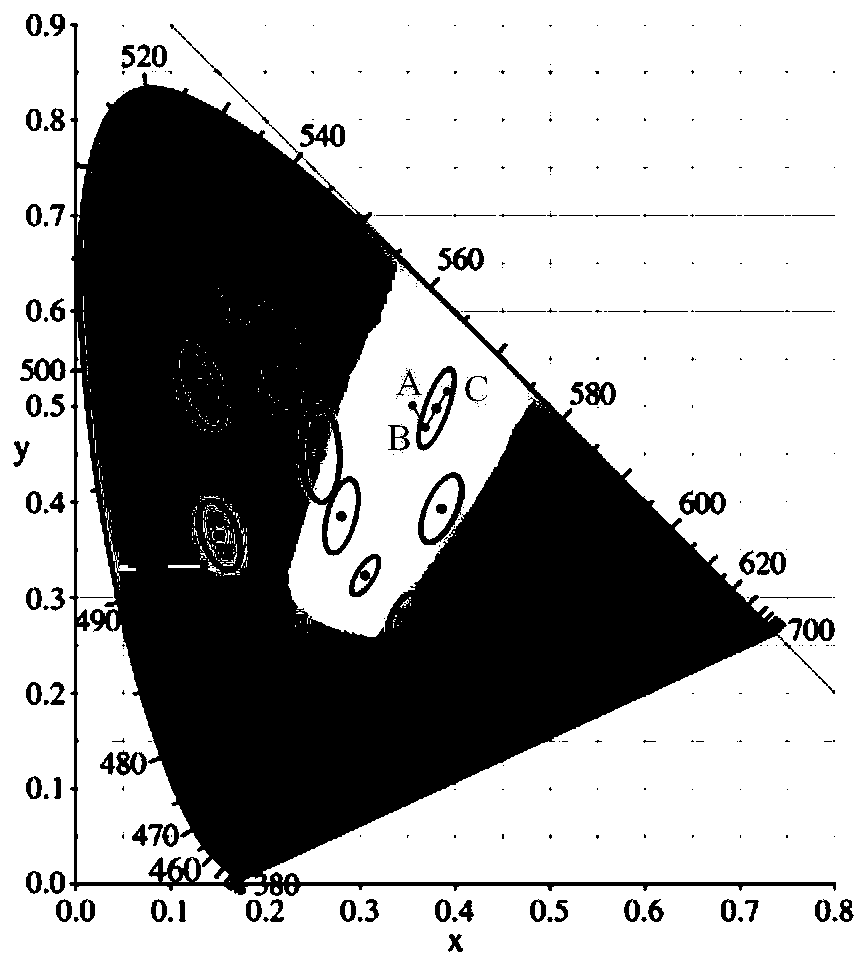

ActiveCN109886325AImprove registration rateImprove execution speedCharacter and pattern recognitionNeural architecturesLinear modelHuman eye

The invention provides a template selection and accelerated matching method for nonlinear color space classification, and the method comprises the processes of the model training and the image matching, wherein the model training comprises the steps of collecting a training image sample, extracting a CIE chromaticity diagram of the training image sample, and carrying out the manual marking of a color category number to which the CIE chromaticity diagram belongs; and obtaining a five-layer feedforward neural network model; and the image matching process comprises the following steps of inputting a pair of color images, and setting a sampling rate; carrying out isolated point downsampling processing; obtaining a classification result set; calculating a metric value of the similarity probability; selecting i corresponding to the first k values with the highest scores as a preferred color category number, and correspondingly obtaining a template area in the template image and an area to bematched in the image to be matched according to the preferred color category number; and matching the template area in the template image with the to-be-matched area in the to-be-matched image. Experimental results show that the method has the higher registration rate and execution speed, and the problem that color space color distance measured by a linear model is inconsistent with human eye vision judgment in an existing matching method is solved.

Owner:LIAONING TECHNICAL UNIVERSITY

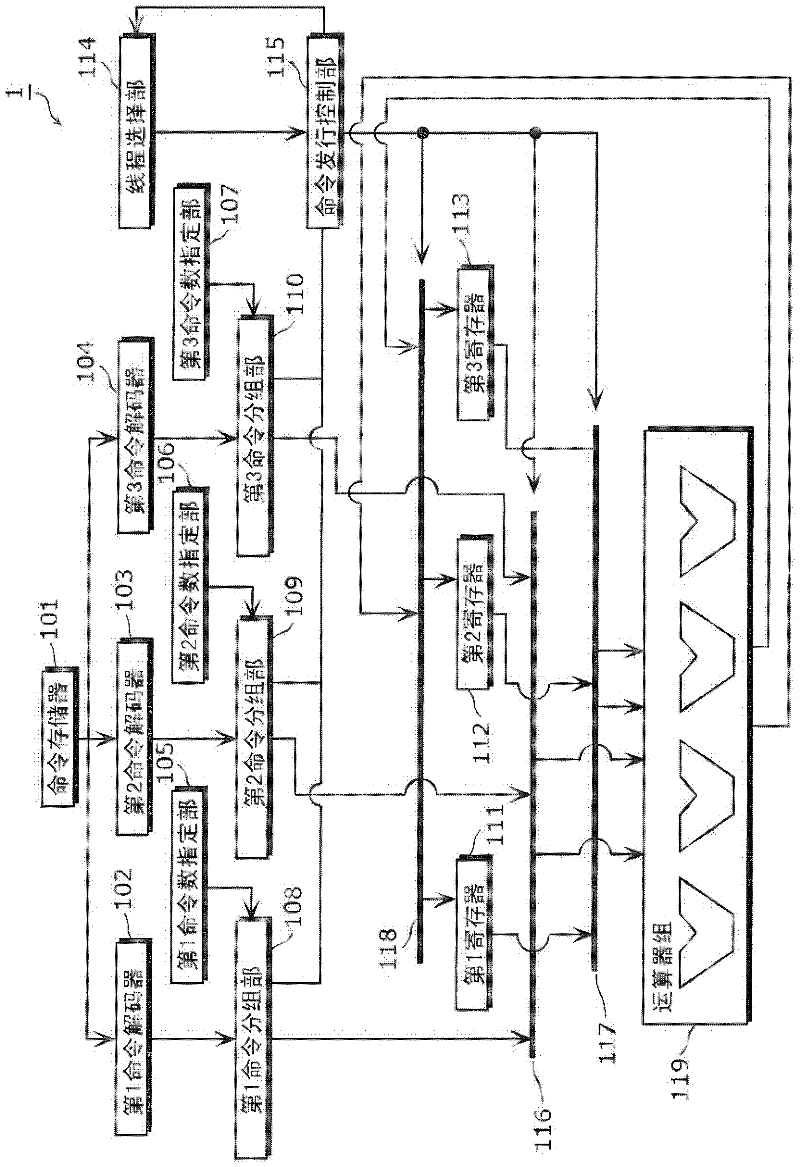

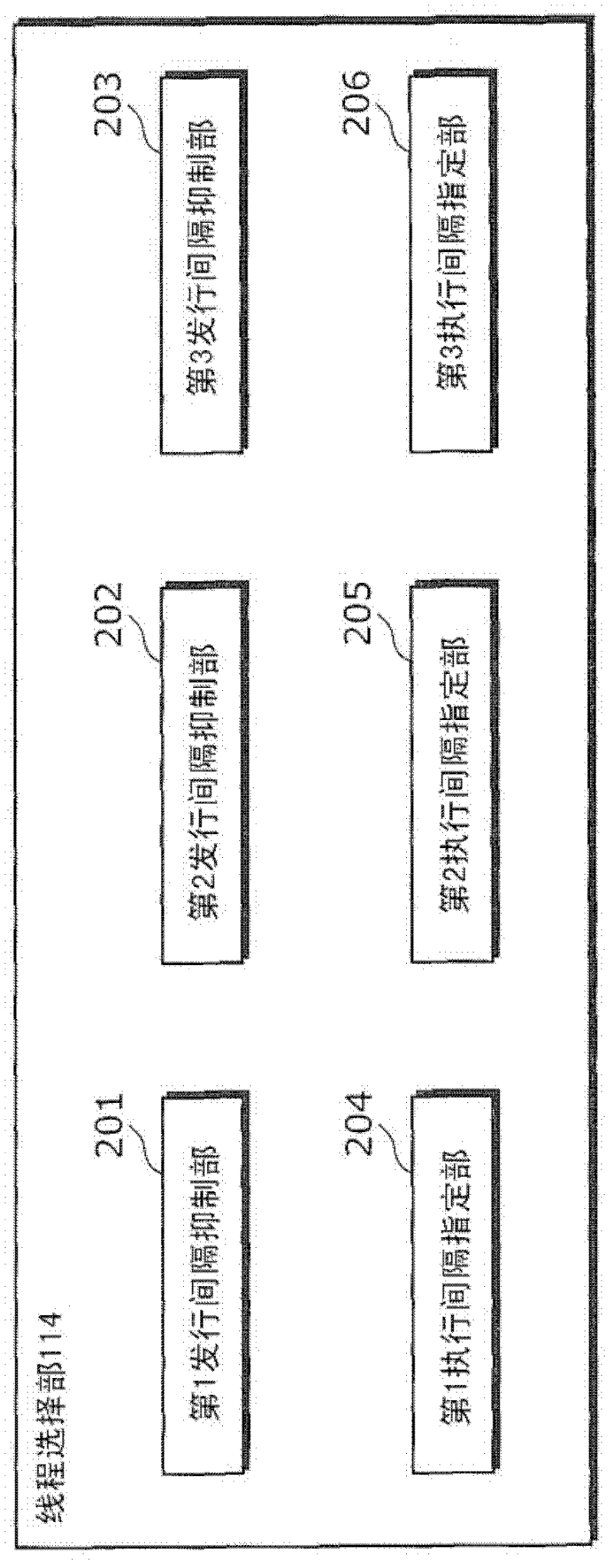

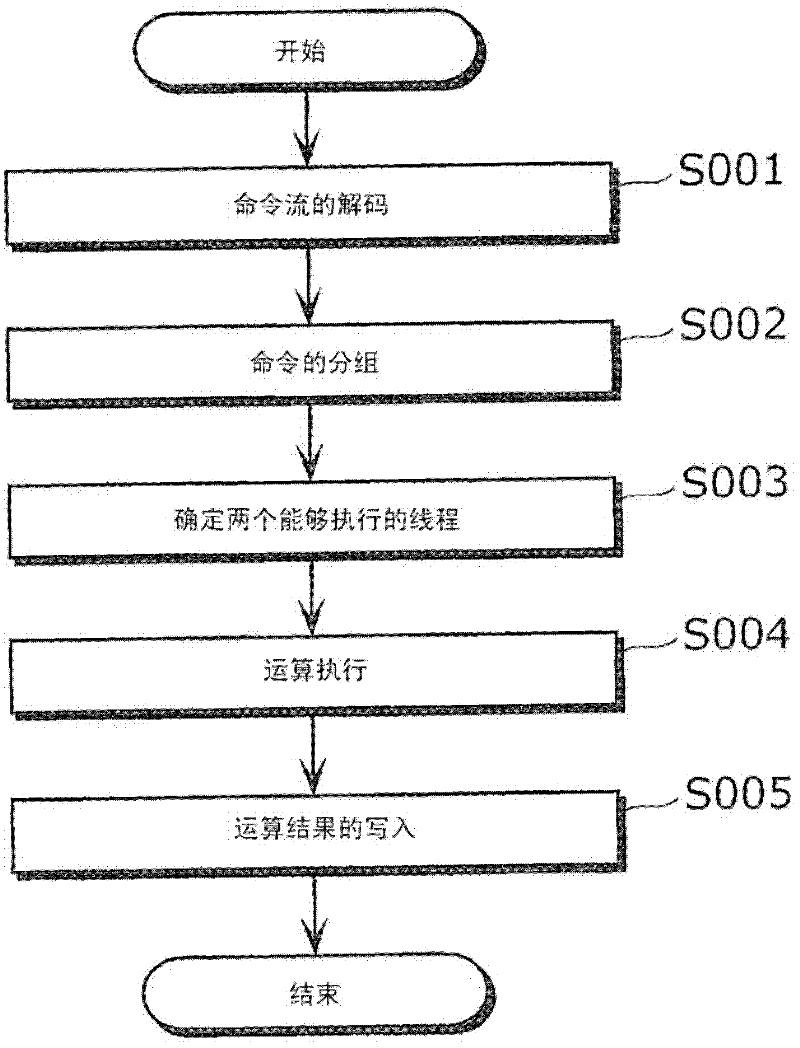

Multi-thread processor, compiler device and operating system device

ActiveCN102334094ALow execution efficiencyEasy to useMultiprogramming arrangementsConcurrent instruction executionOperational systemUnit group

A multi-thread processor (1) which executes instructions in multiple threads in parallel is provided with a computing unit group (119) comprising multiple computing units each for executing an instruction, a first instruction grouping unit (108) to a third instruction grouping unit (110) each for, in each thread, grouping instructions included in the thread into a group comprising instructions concurrently executable by the multiple computing units, a thread selection unit (114) for selecting, from among the multiple threads, a thread including instructions to be issued to the multiple computing units at every execution cycle of the multi-thread processor (1) by controlling the frequency of execution of the instructions in the multiple threads, and an instruction issuance control unit (115); for issuing the instructions of the grouped group among instructions included in the thread selected by the thread selection unit (114) to the multiple computing units at every execution cycle of the multi-thread processor (1).

Owner:SOCIONEXT INC

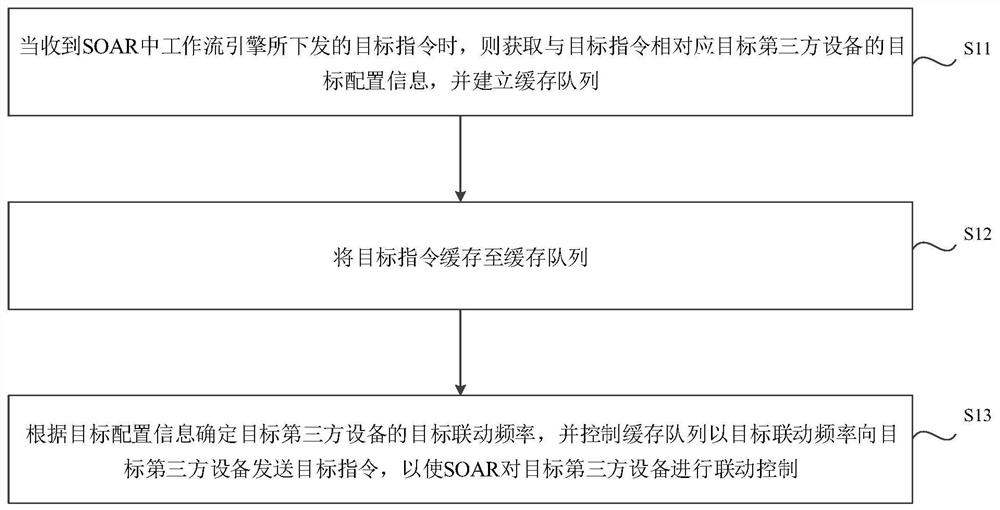

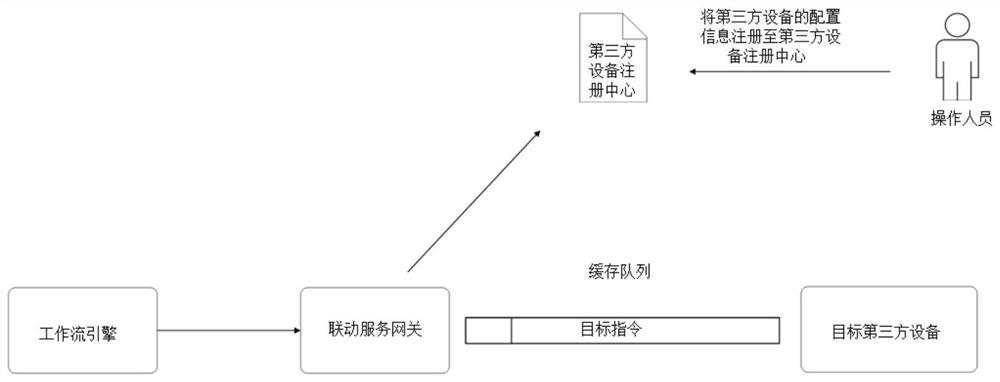

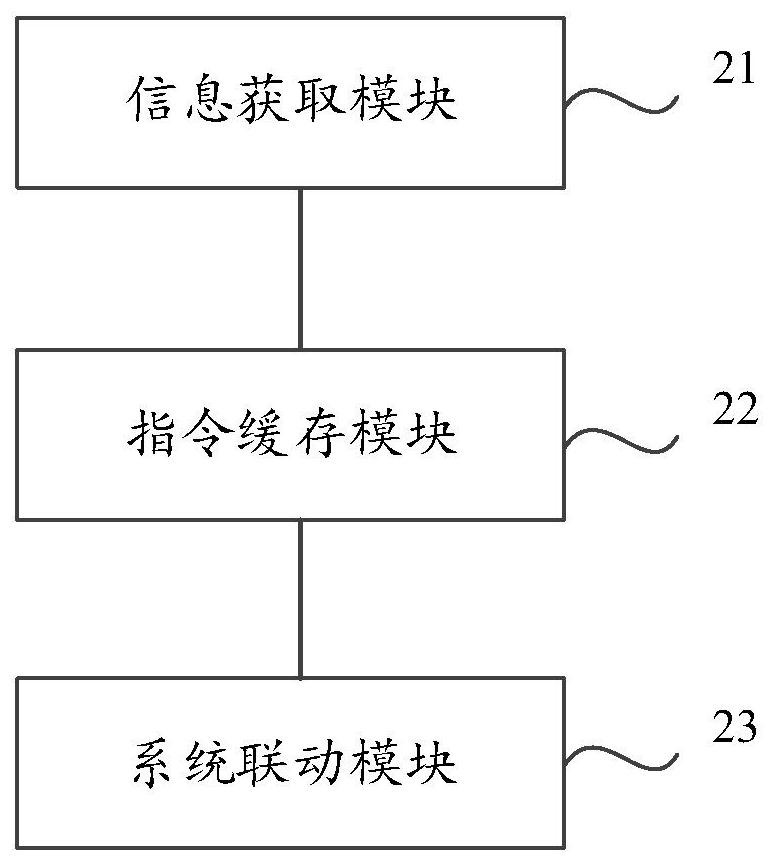

SOAR linkage equipment control method, device, equipment and medium

ActiveCN113691627ALow execution efficiencyOrderly controlData switching networksThird partyWorkflow engine

The invention discloses an SOAR linkage equipment control method, a device, equipment and a medium. The method comprises the following steps: obtaining target configuration information of target third-party equipment corresponding to a target instruction when the target instruction issued by a workflow engine in SOAR is received, and building a cache queue; caching the target instruction to a cache queue; and determining a target linkage frequency of the target third-party device according to the target configuration information, and controlling the cache queue to send a target instruction to the target third-party device at the target linkage frequency, so that the SOAR performs linkage control on the target third-party device. Due to the fact that the cache queue can orderly and effectively issue the target instruction to the target third-party device according to the actual processing capacity of the target third-party device through the method, in the setting mode, even if the execution efficiency of the target third-party device is low, the SOAR can be successfully linked to the target third-party device.

Owner:HANGZHOU ANHENG INFORMATION TECH CO LTD

Tourism system platform

InactiveCN105931149ASolve travel problemsImprove reading efficiencyData processing applicationsTransmissionData accessData library

The present invention relates to a tourism system platform which comprises a communication module, a packet analysis module, a monitoring module, a task execution module, a service start module, and a data access module. Through providing a shared, common, fast, convenient and safe transportation query system with a scale economy, the travel problem of people is solved, through using a database of a master-slave mode, the efficiency of reading and writing is greatly improved, and the system availability is improved.

Owner:HAINAN SMART CITY TECH DEV CO LTD

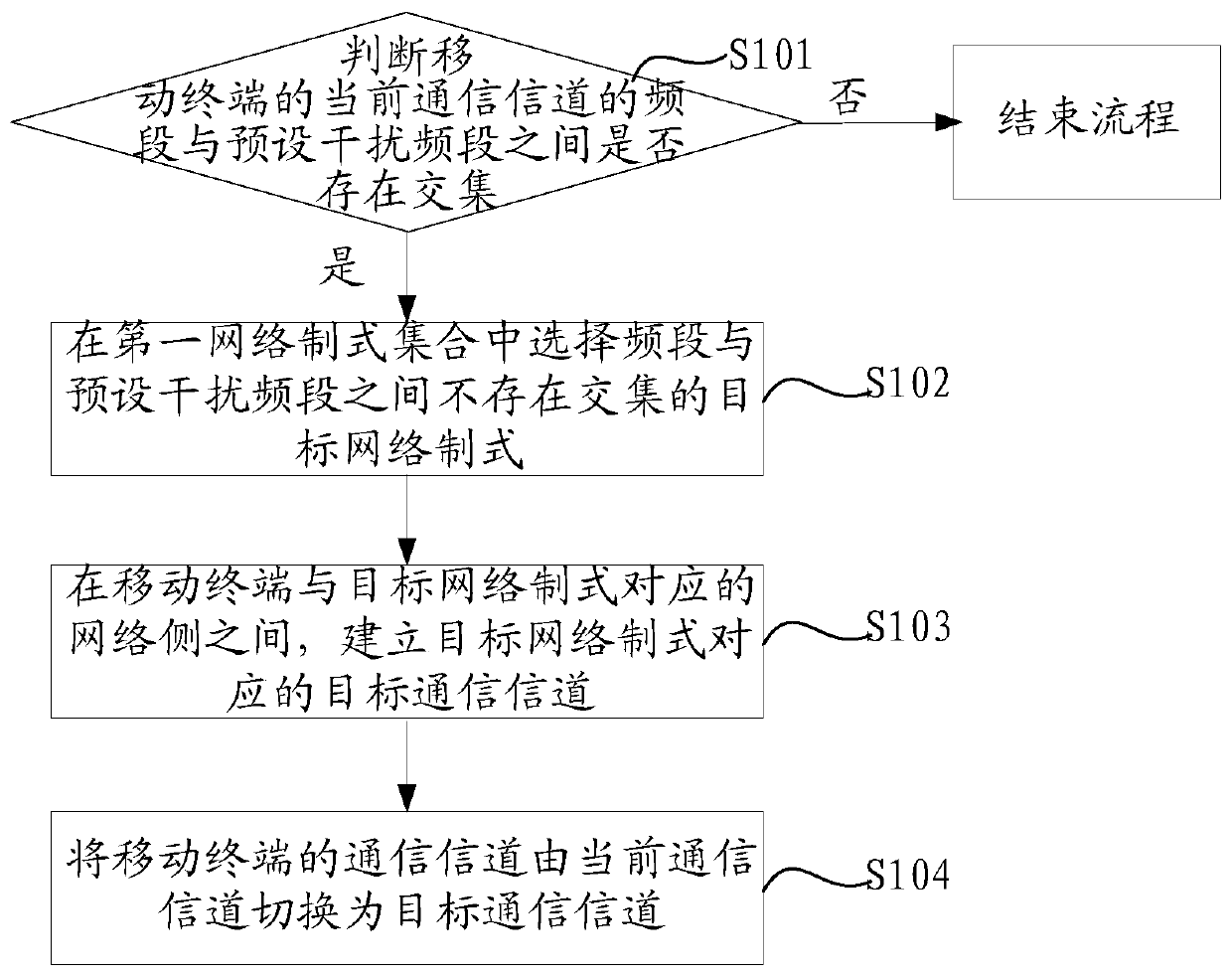

Channel switching method and mobile terminal

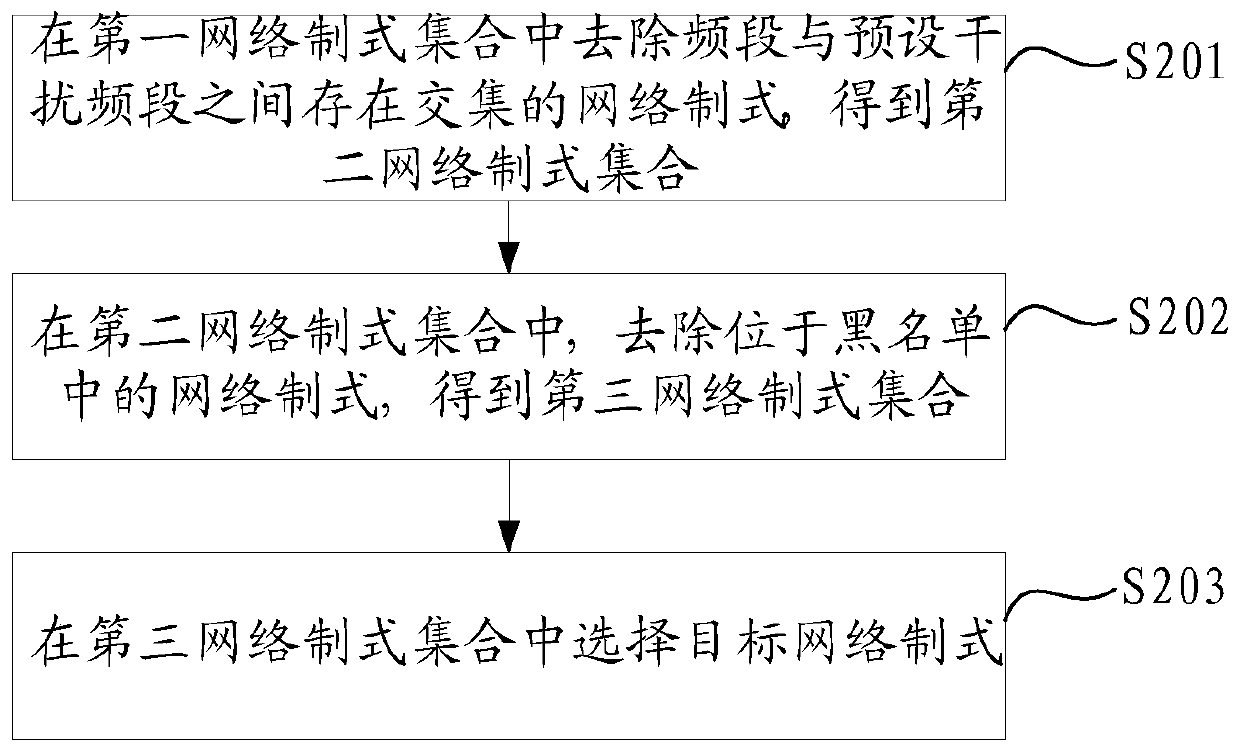

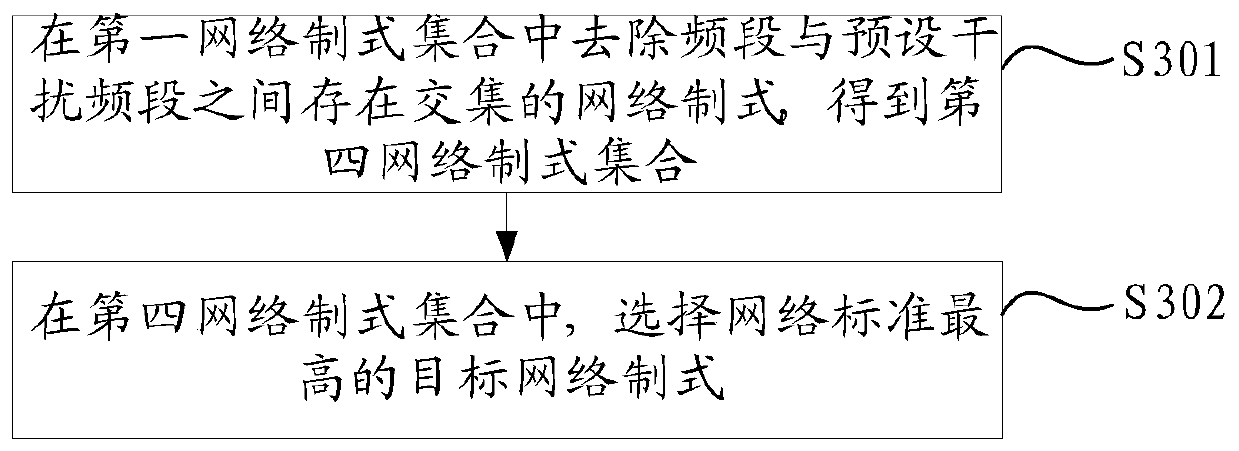

InactiveCN110493839AReduce complexityLow execution efficiencyTelephone set constructionsWireless communicationClock rateComputer terminal

The invention provides a channel switching method and a mobile terminal. Therefore, the mobile terminal does not need to execute the service needing to use the network based on the current communication channel any more; the service needing to use the network can be executed based on the target communication channel; because no intersection exists between the target network type of the target communication channel and the preset interference frequency band, the target communication channel is not interfered by the clock frequency of the mobile terminal, so that the mobile terminal can normallyexecute the service needing to use the network. The clock frequency can be set only by one clock frequency, so that the complexity of the mobile terminal can be reduced, the situation that the clockfrequency is switched between the main clock frequency and the standby clock frequency does not exist due to the fact that only one clock frequency exists, the situation that the clock frequency is frequently switched does not exist, and therefore the situation that the mobile terminal cannot normally operate can be avoided.

Owner:VIVO MOBILE COMM CO LTD

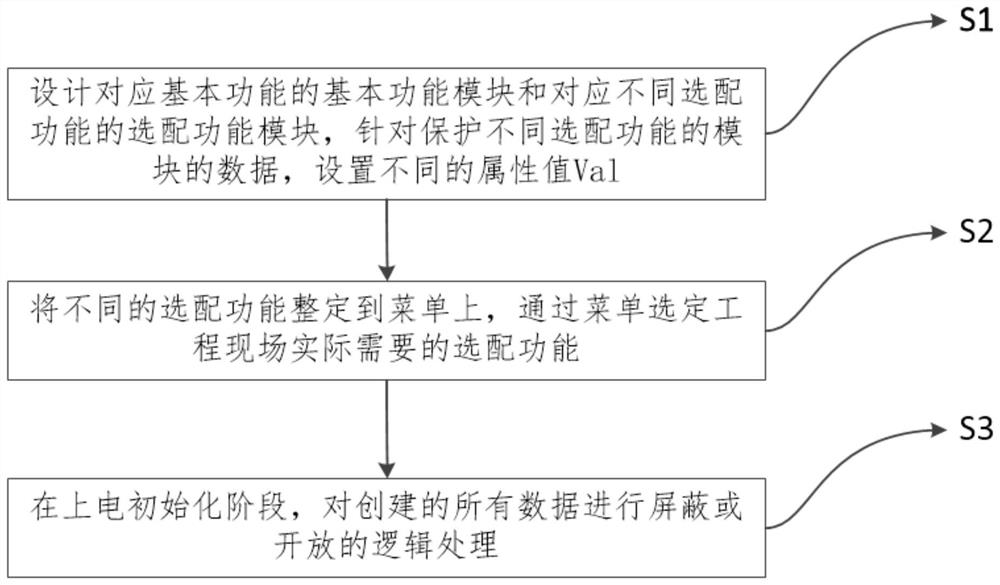

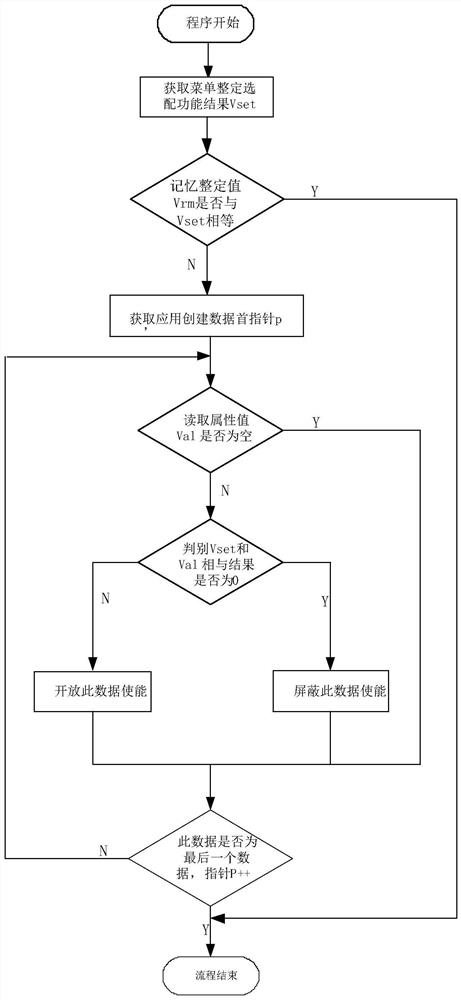

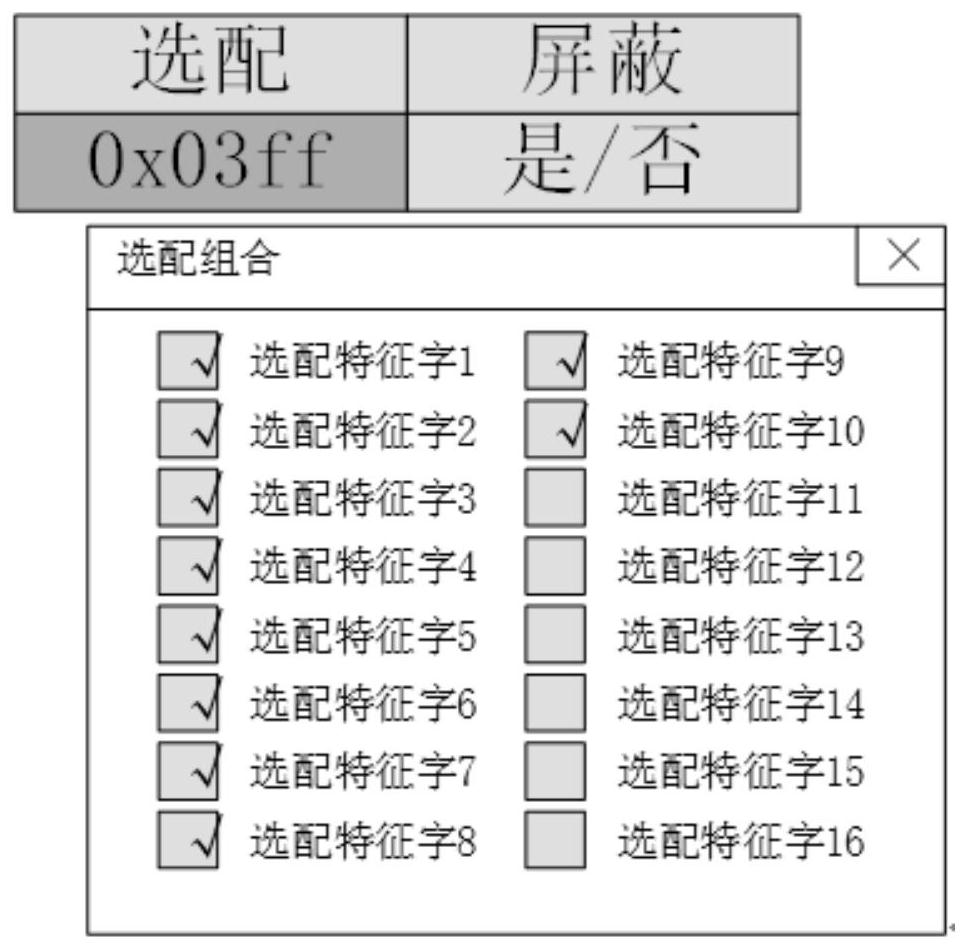

Method and system for setting relay protection device function selection by adopting menu interface

InactiveCN111966263AReduce complexityImprove work efficiencyInput/output processes for data processingElectrical and Electronics engineeringMatch function

The invention discloses a method and a system for setting function selection of a relay protection device by adopting a menu interface. The method comprises the following steps of designing a basic function module corresponding to a basic function and a matching function module corresponding to different matching functions, and setting different attribute values Val for protecting data of the modules with different matching functions; setting different matching functions on a menu, and selecting the matching function actually required by the engineering field through the menu; and in the power-on initialization stage, shielding or opening logic processing being carried out on all the created data. According to the method, different matching functions can be selected and protected accordingto menus, engineering debugging complexity is reduced, and the risk of man-made uncontrollability caused by the fact that correct configuration needs to be downloaded according to the matching functions due to diversification of the protection matching functions in the prior art is solved.

Owner:XUJI GRP +5

inspection method based on bdd

InactiveCN103886377ALow execution efficiencyAchieve the purpose of screeningInference methodsLogic errorData mining

The invention discloses knowledge database rule generation formula inspection method based on BDD, which is characterized in that the inspection method performing the following inspection steps on each inputted rule when an alpha node network of an inference machine is constructed based on the inference rules: converting a prior rule generation formulation Rp to corresponding BDD and detecting that whether the Rp can be satisfied through traversing the BDD, and converting a prior rule generation rule Rp to corresponding BDD and detecting whether the Rp can be permanently real through traversing the BDD. The invention realizes the rule that the filtering knowledge database has logic errors and realizes automatic inspection on the facts that whether the reference rule can be satisfied or can be permanently real.

Owner:北京神舟航天软件技术股份有限公司

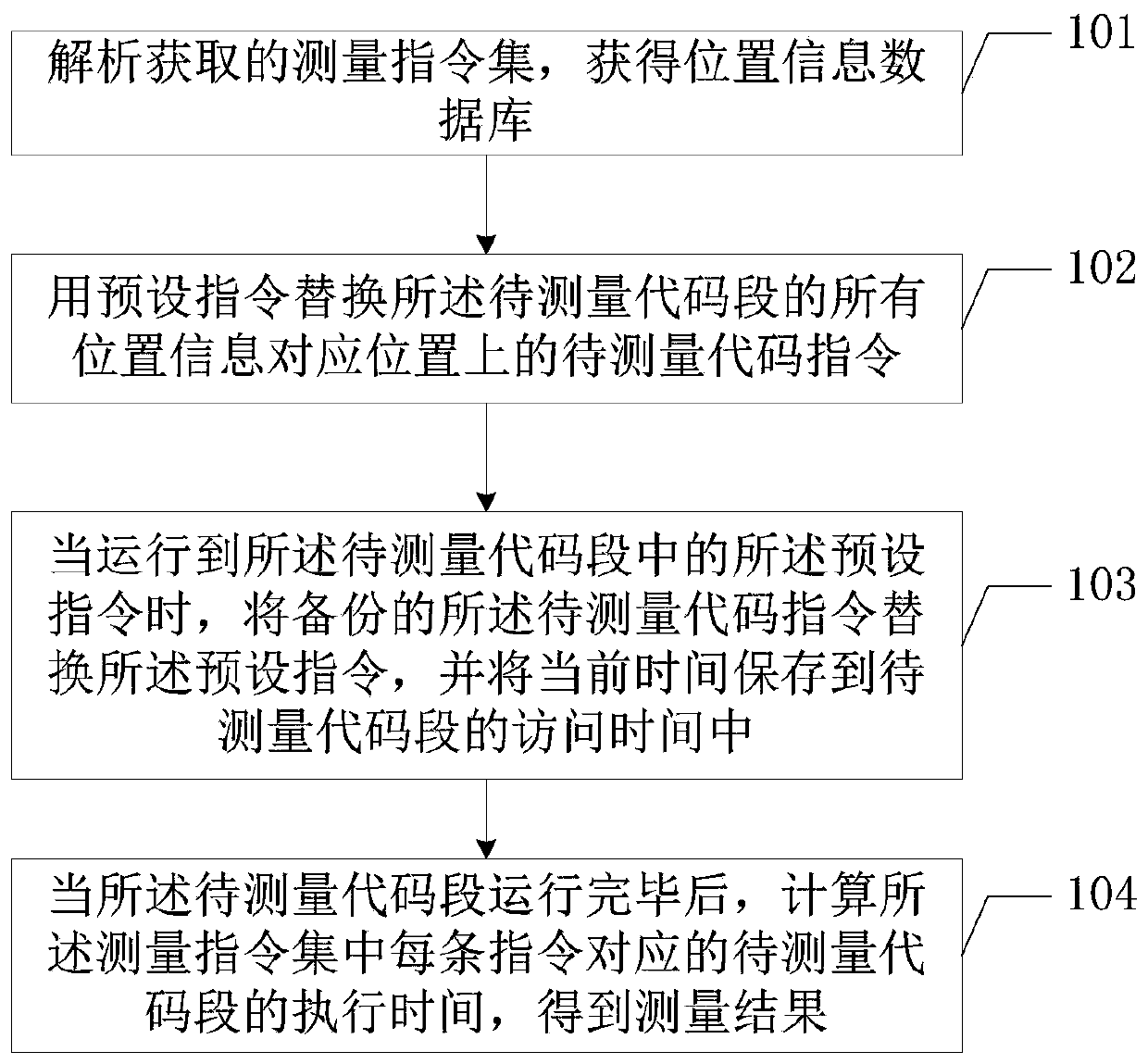

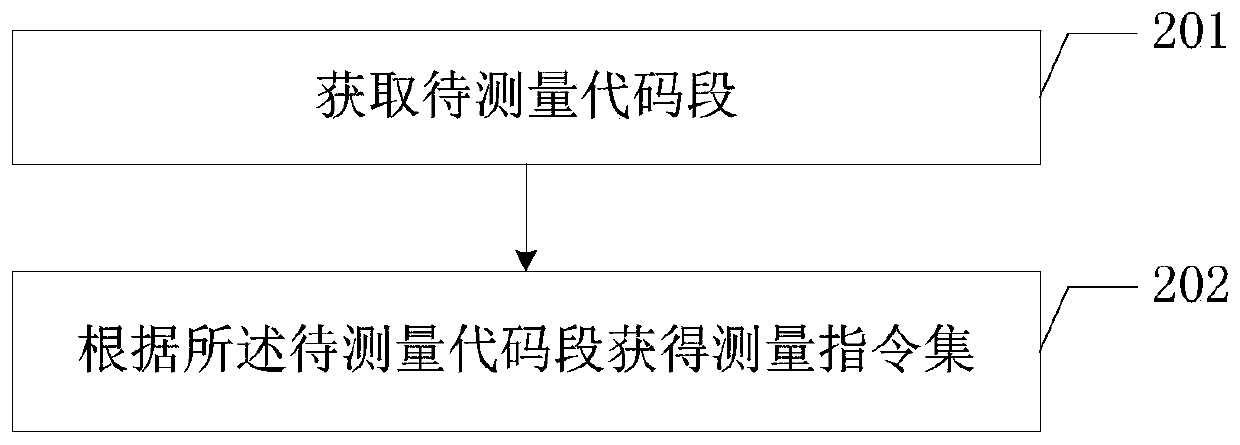

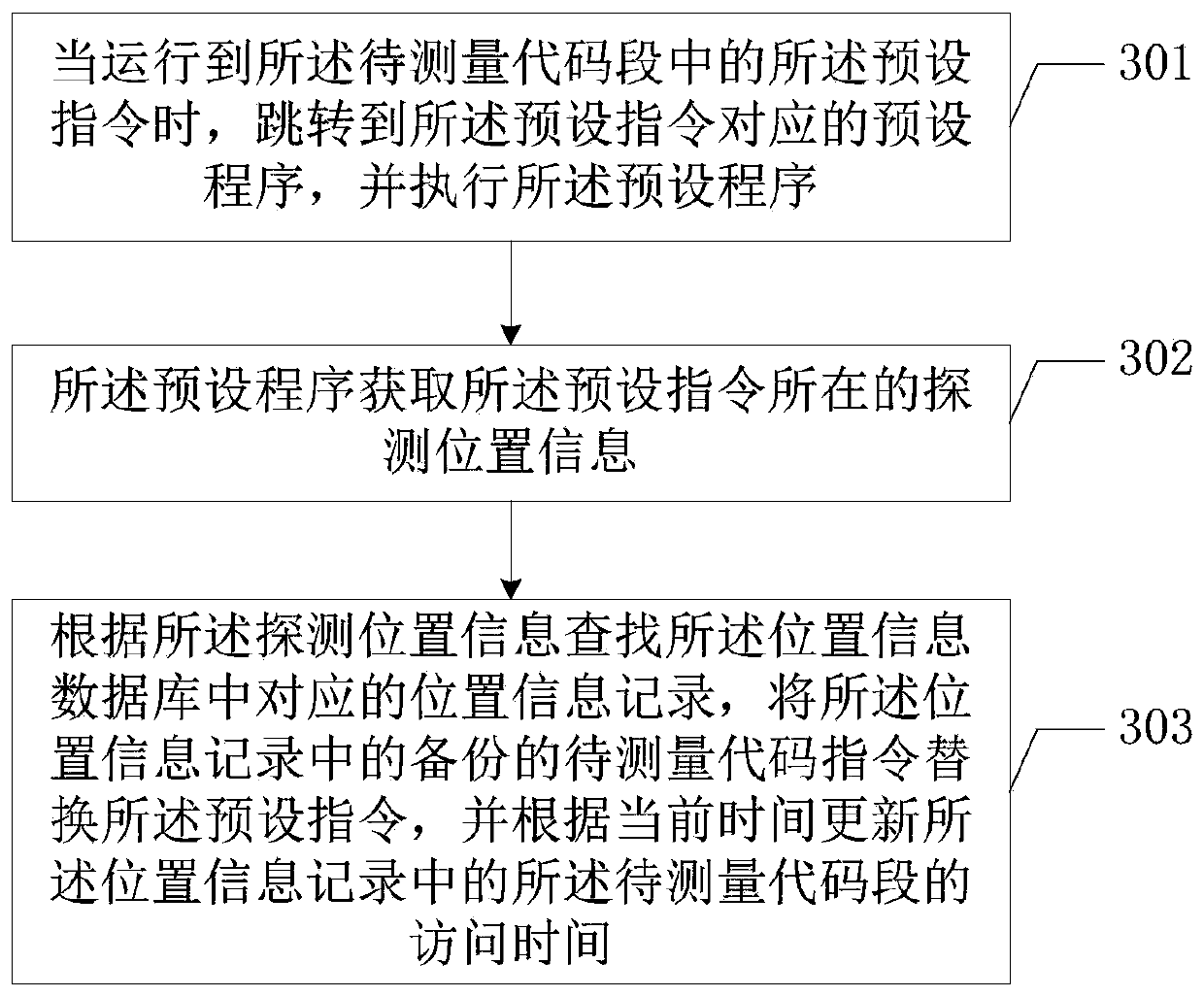

Method for measuring code segment execution time and terminal equipment

ActiveCN110580220AAutomate your measurementsRapid diagnosis execution efficiencySoftware testing/debuggingAccess timeTerminal equipment

The invention is suitable for the technical field of program optimization, and provides a method for measuring the execution time of a code segment and terminal equipment, and the method comprises thesteps: analyzing an obtained measurement instruction set, and obtaining a position information database; replacing the to-be-measured code instructions at the positions corresponding to all the position information of the to-be-measured code segment with a preset instruction; when a preset instruction in the to-be-measured code segment is run, replacing the preset instruction with the backed-up to-be-measured code instruction, and storing the current time in the access time of the to-be-measured code segment; after the operation of the to-be-measured code segment is finished, calculating execution time of a to-be-measured code segment corresponding to each instruction in the measurement instruction set; therefore, the execution time of any code segment of the program can be measured without modifying the condition of the program code, which code segment of the program is not high in execution efficiency can be quickly diagnosed, automatic measurement is realized, a measurement resultis formed, and further analysis is facilitated.

Owner:PAX COMP TECH SHENZHEN

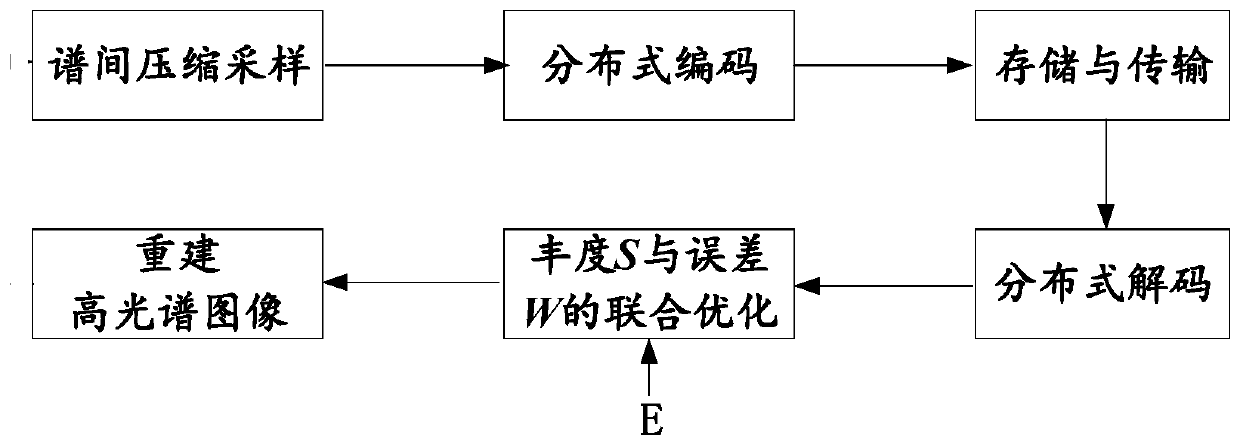

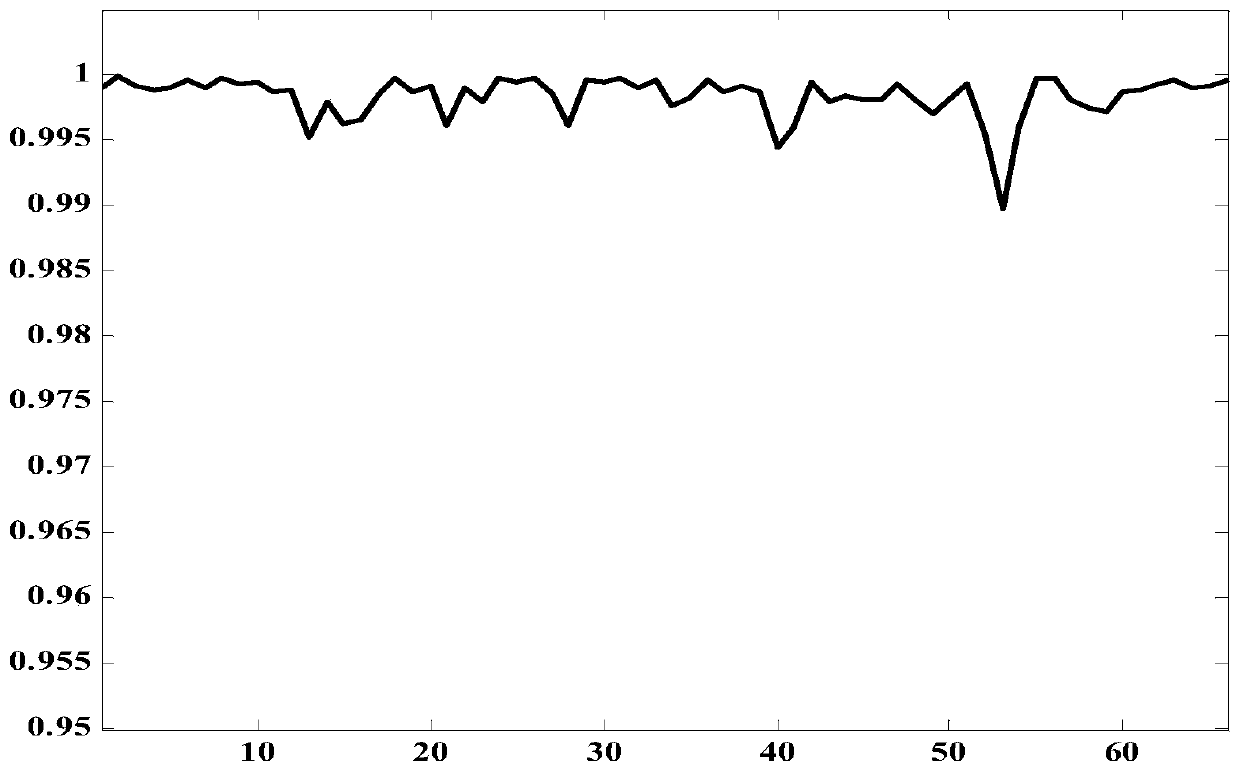

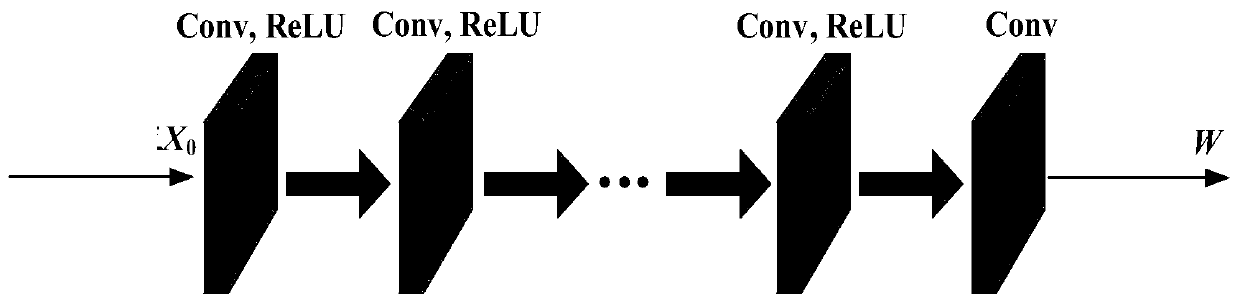

Hyperspectral image distributed compression method and system based on compressed sensing

ActiveCN110390699AEfficient compressionAchieve lossless compressionImage enhancementImage analysisCoding blockLossless compression

Owner:ARMY MEDICAL UNIV

Wireless inductive power transfer

ActiveUS10707698B2Improve performanceFacilitate communicationCircuit arrangementsTransmitter coilResonance

A power transmitter (101) for inductively transferring power to a power receiver (105) comprises a resonance circuit (201) comprising a transmitter coil (103) for generating a power transfer signal. A sampler (511) samples a current through, or voltage over, the transmitter coil (103). A message receiver (509) receives messages load modulated onto the power transfer signal based on the samples. A driver (203) generates a drive signal for the resonance circuit (201) and a resonance modification circuit (505) reduces the resonance frequency of the resonance circuit (201) by slowing a state change for a resonating component of the resonance circuit (201) for a fractional time interval of the cycles of the drive signal. A sample time controller (513) controls the sample times in response to at least one of start-times and end-times of the fractional time intervals, and specifically may set the sample times to be within the fractional time intervals.

Owner:KONINKLJIJKE PHILIPS NV

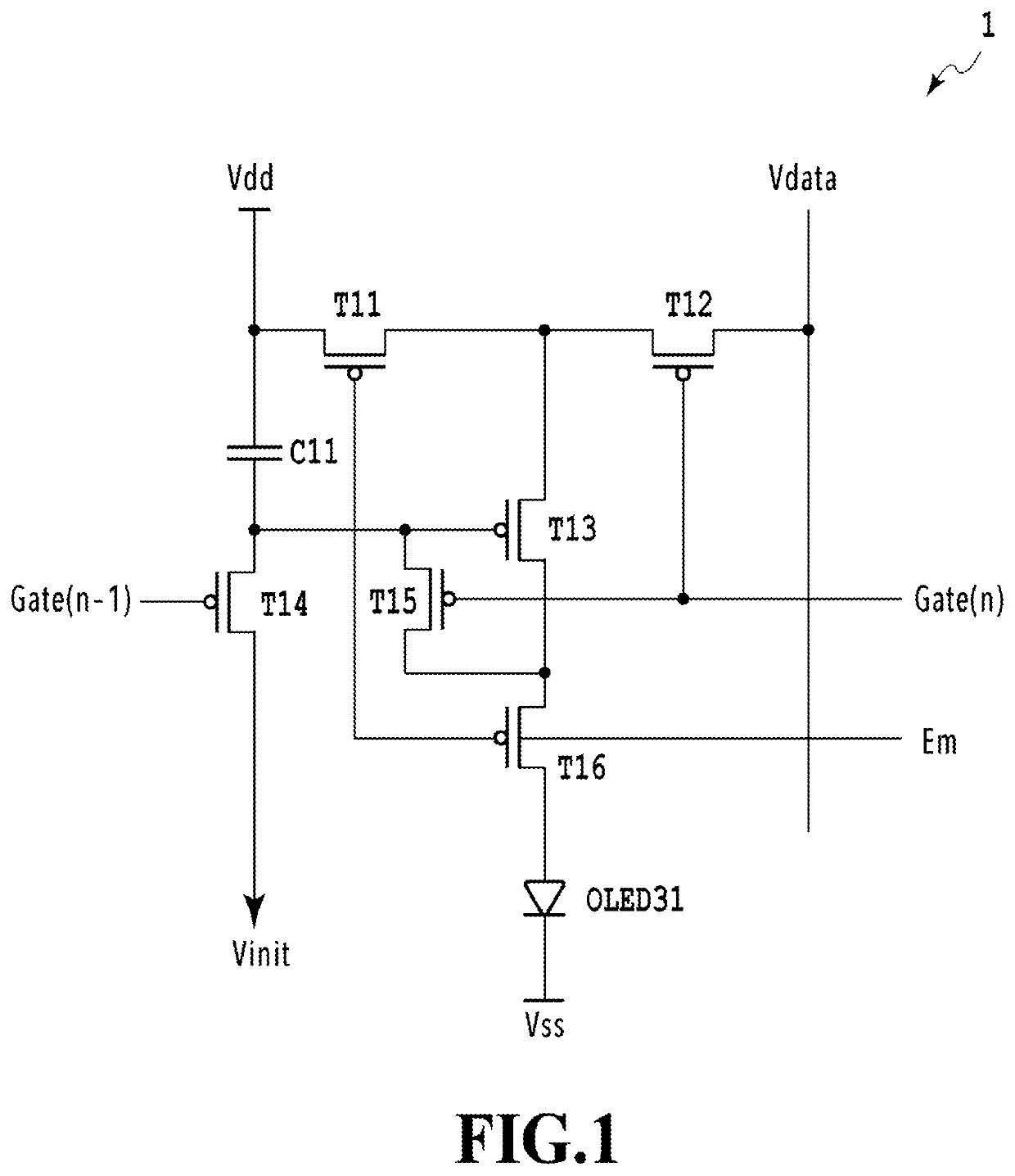

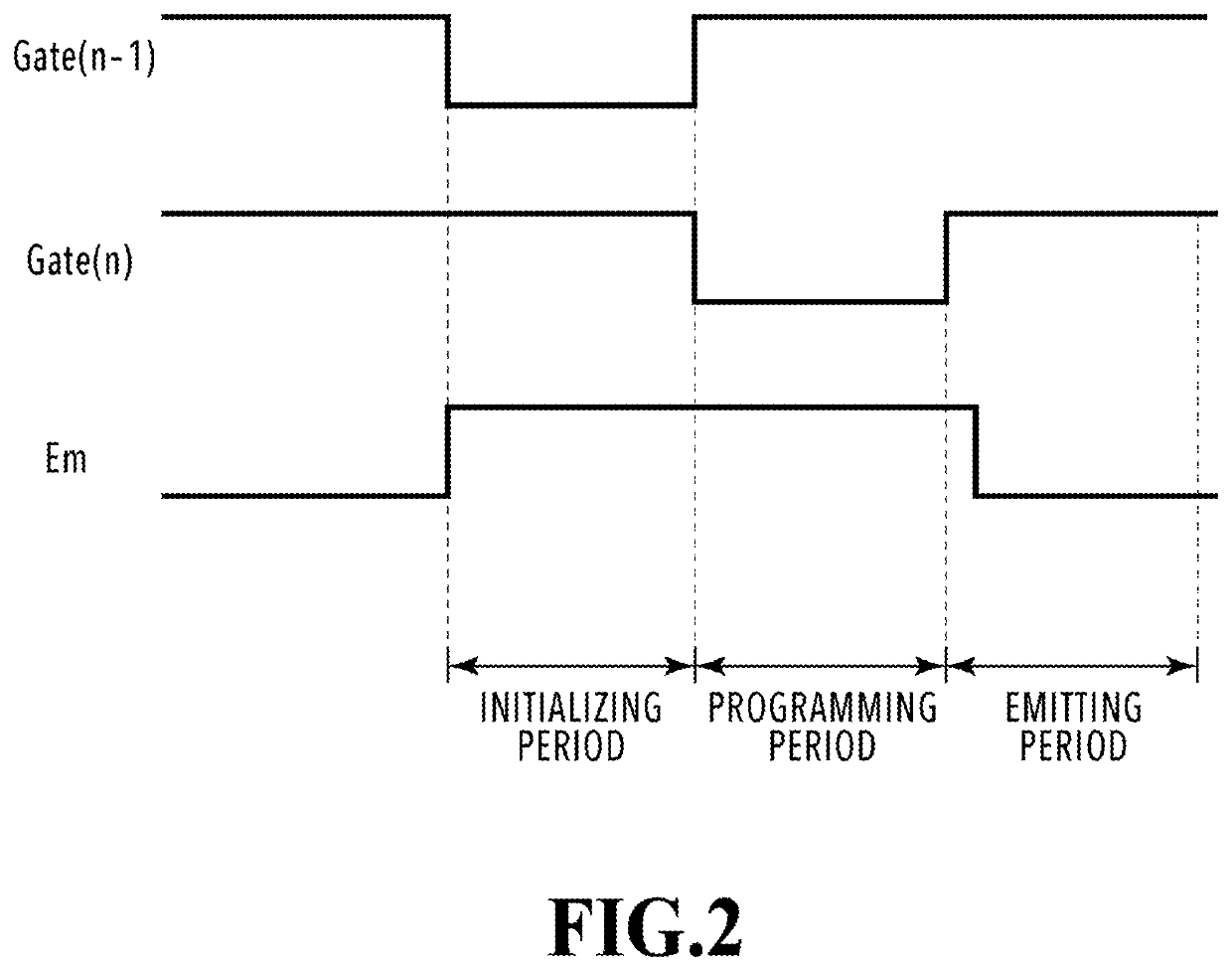

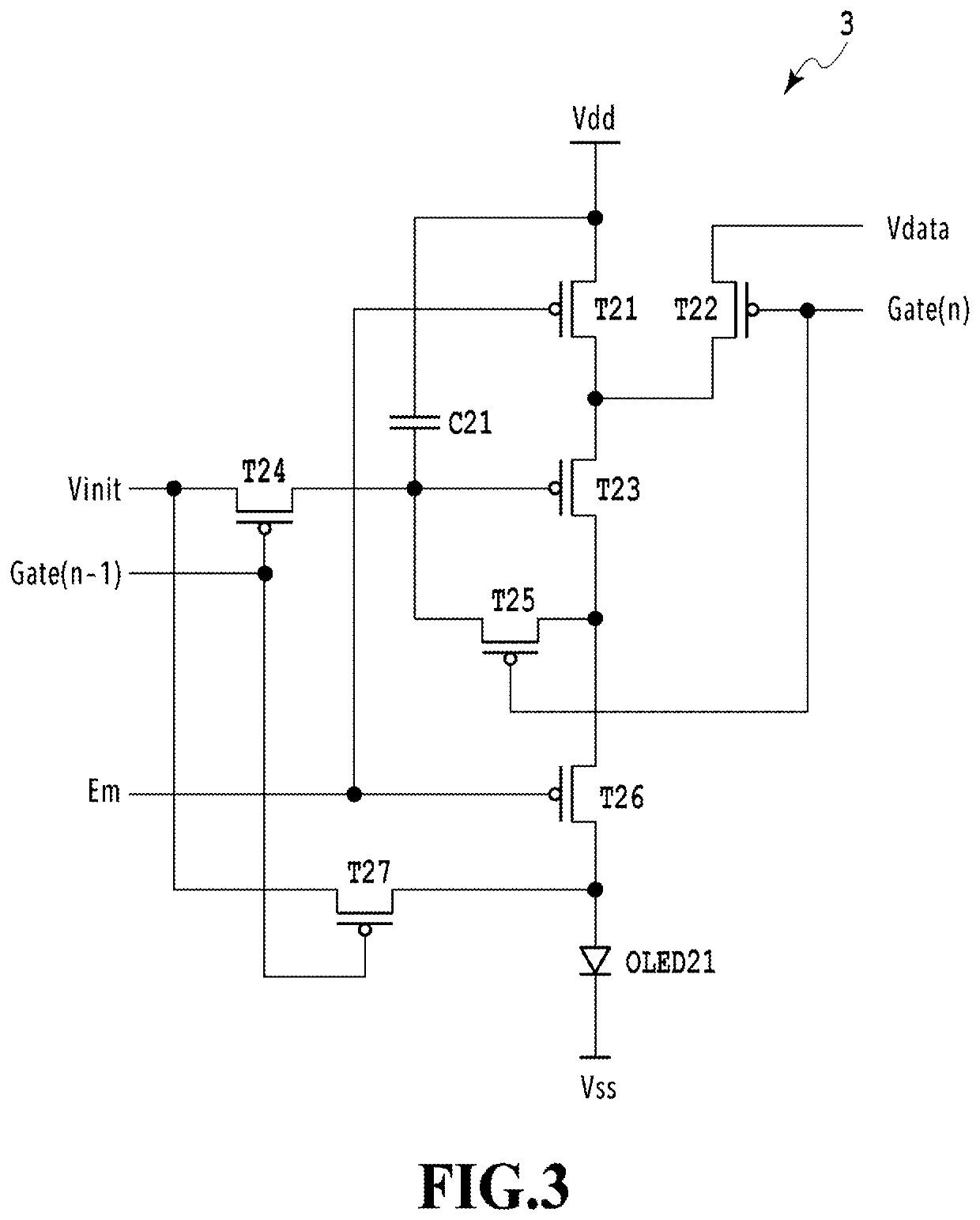

Pixel circuit and pixel control method

PendingUS20220084466A1Simple circuit structureReduce complexityStatic indicating devicesCharge voltageData lines

Provided are a pixel circuit and a pixel control method capable of quickly controlling pixels with a simpler configuration of a combination of a photosensor and a pixel circuit. The pixel circuit includes: a switching transistor for switching a data signal to be applied to a data line; a driving transistor for supplying a drive current to an organic light emitting diode (OLED) according to a charge voltage corresponding to the data signal; a compensation transistor for compensating for a threshold voltage of the driving transistor; and a photosensor having a terminal to which a bias voltage is applied, wherein the switching transistor is a dual gate transistor having a first gate connected to another terminal of the photosensor, and a second gate connected to a gate of the compensation transistor.

Owner:HUAWEI TECH CO LTD

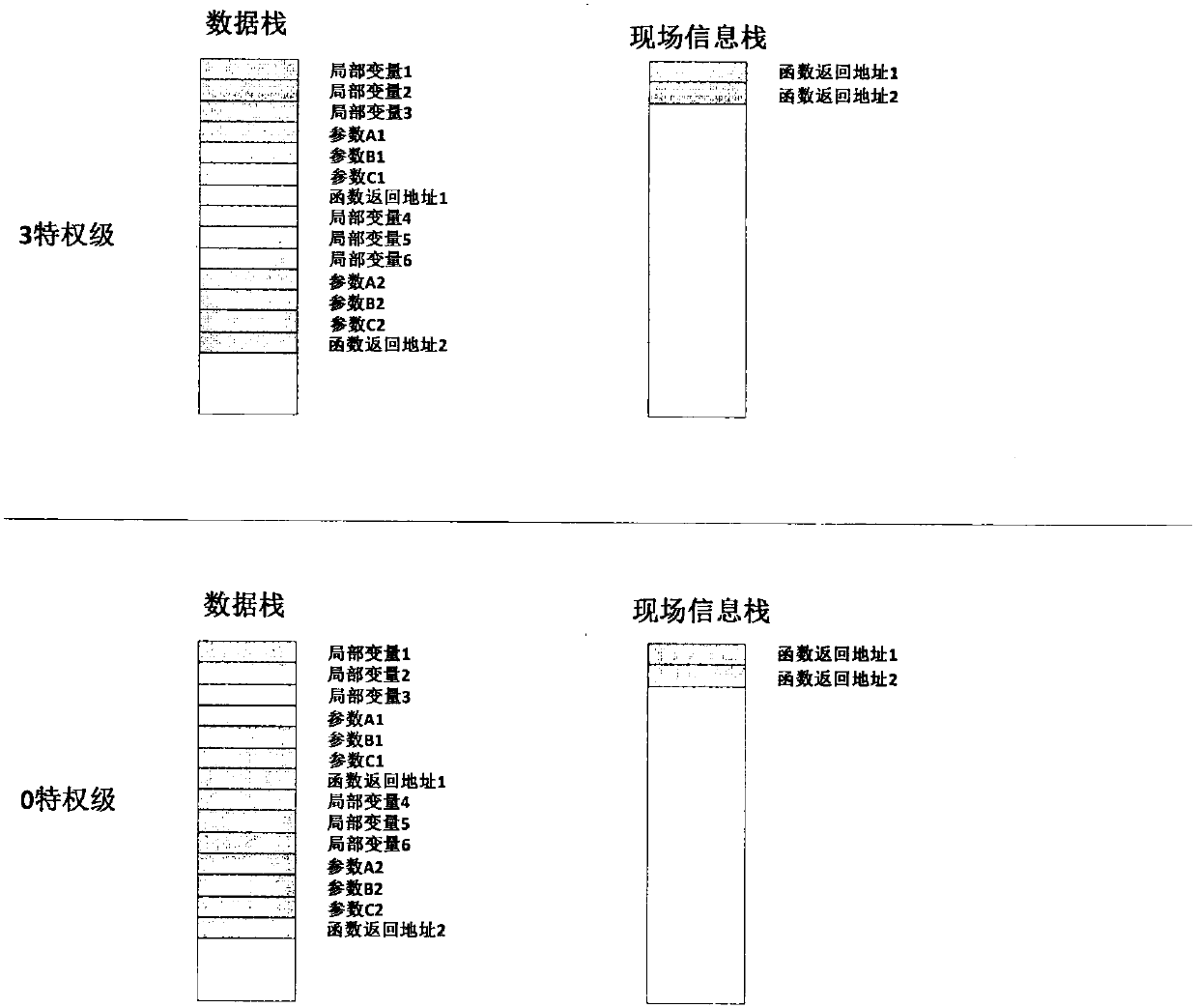

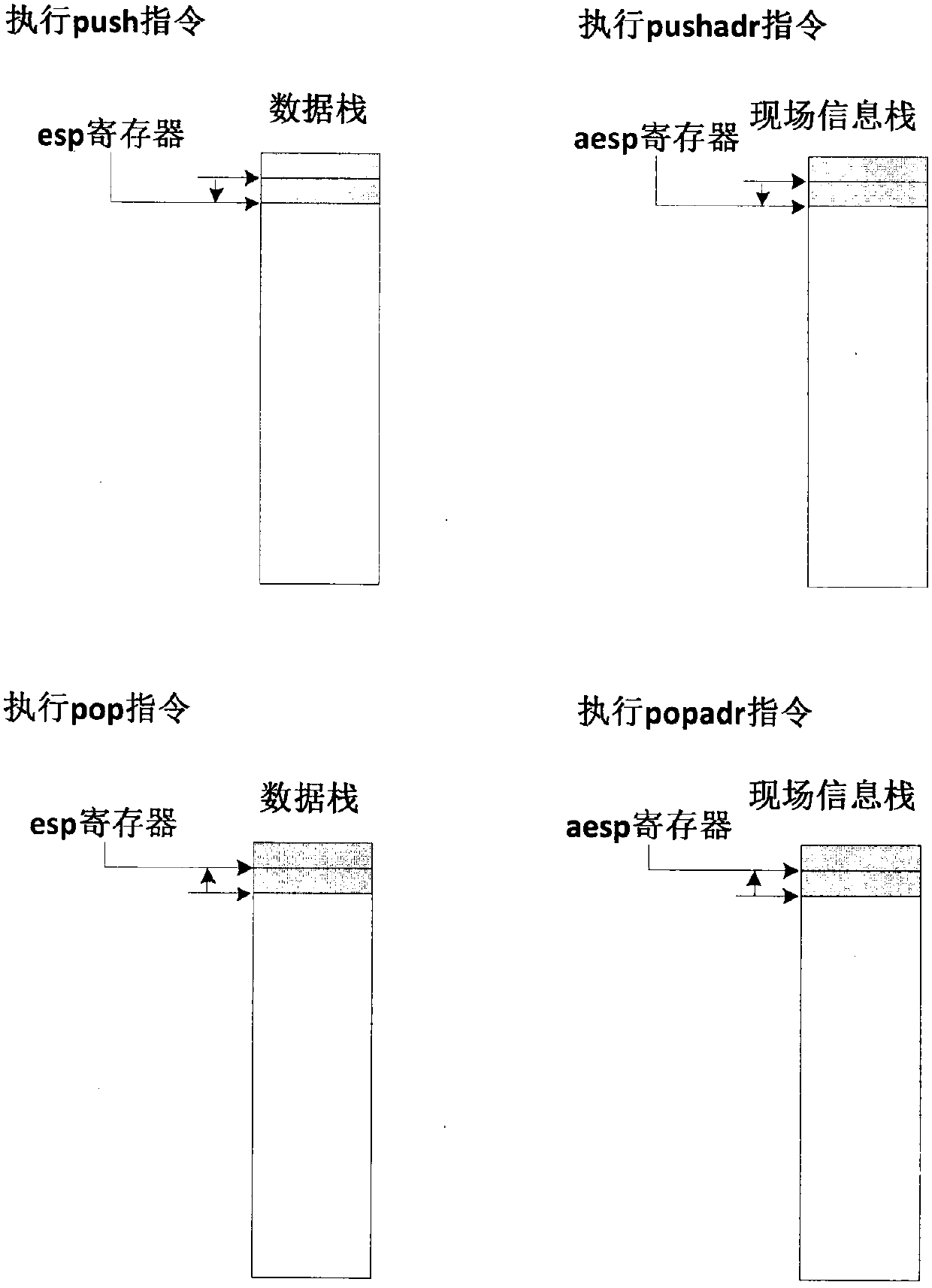

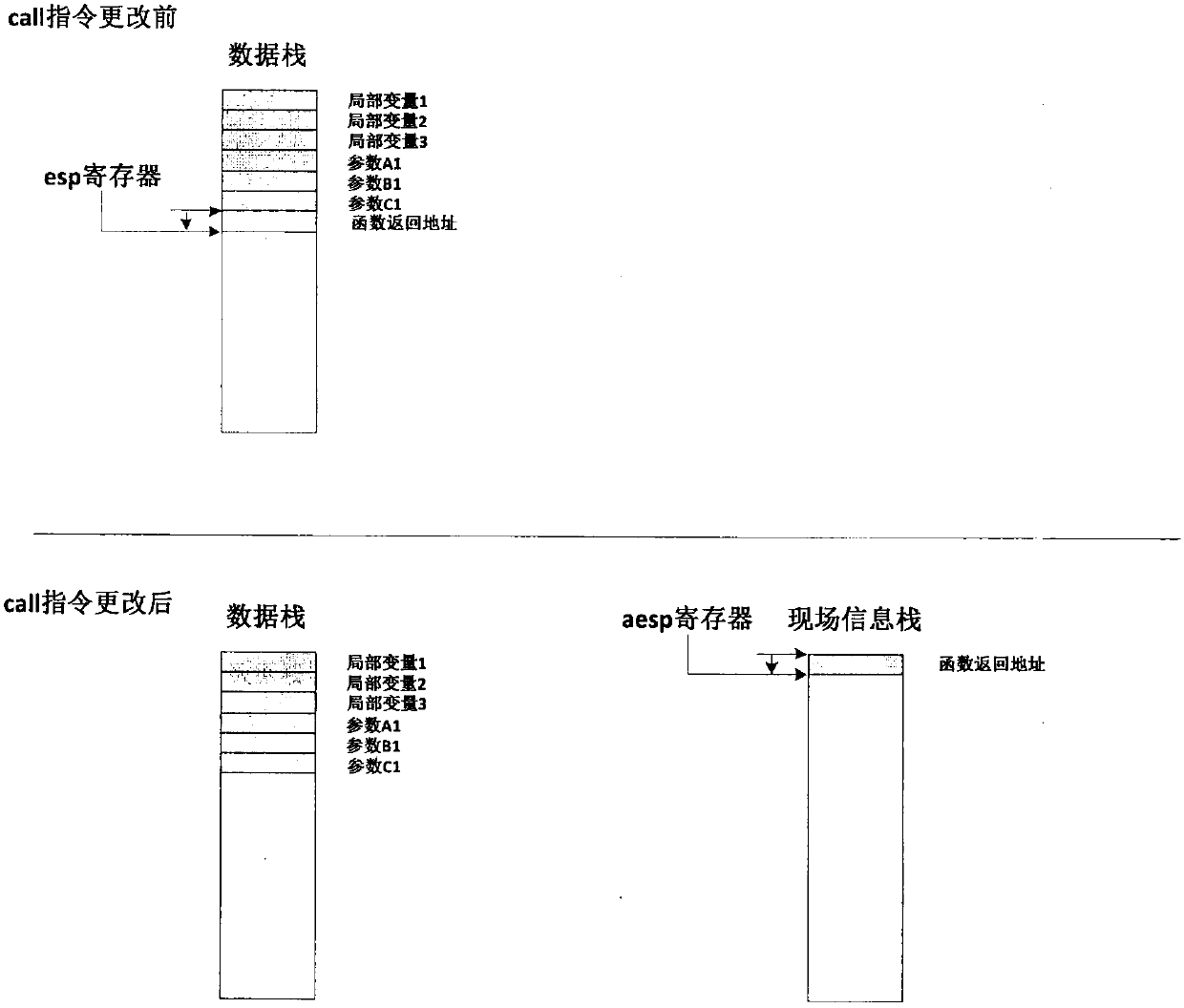

Data protection method and computing device

ActiveCN110598406AAvoid overwritingAvoid attackDigital data protectionPlatform integrity maintainanceParallel computingInformation security

The invention discloses a method for protecting specific data accessed by a central processing unit (CPU), relates to an information technology, in particular to the field of information security, andparticularly relates to a method for protecting a transfer instruction return address, which adopts a field information stack to store data generated by operations needing field protection, such as calling, interrupting and the like; an ass register and an aesp register are added and are respectively used for storing a segment selector of the field information stack and a stack top pointer of thefield information stack; a pushadr and a pushadr instruction are added, the pushadr instruction is used for pressing an address into the field information stack, and the aesp automatically points toa new stack top; the popadr instruction is used for popping up an address from the field information stack, and the aesp automatically points to a new stack top. By applying the scheme provided by theinvention, the condition that a new execution sequence can be generated in a program to further generate an attack due to the fact that a return value of function calling or an address value returnedby interruption is covered is avoided.

Owner:杨力祥

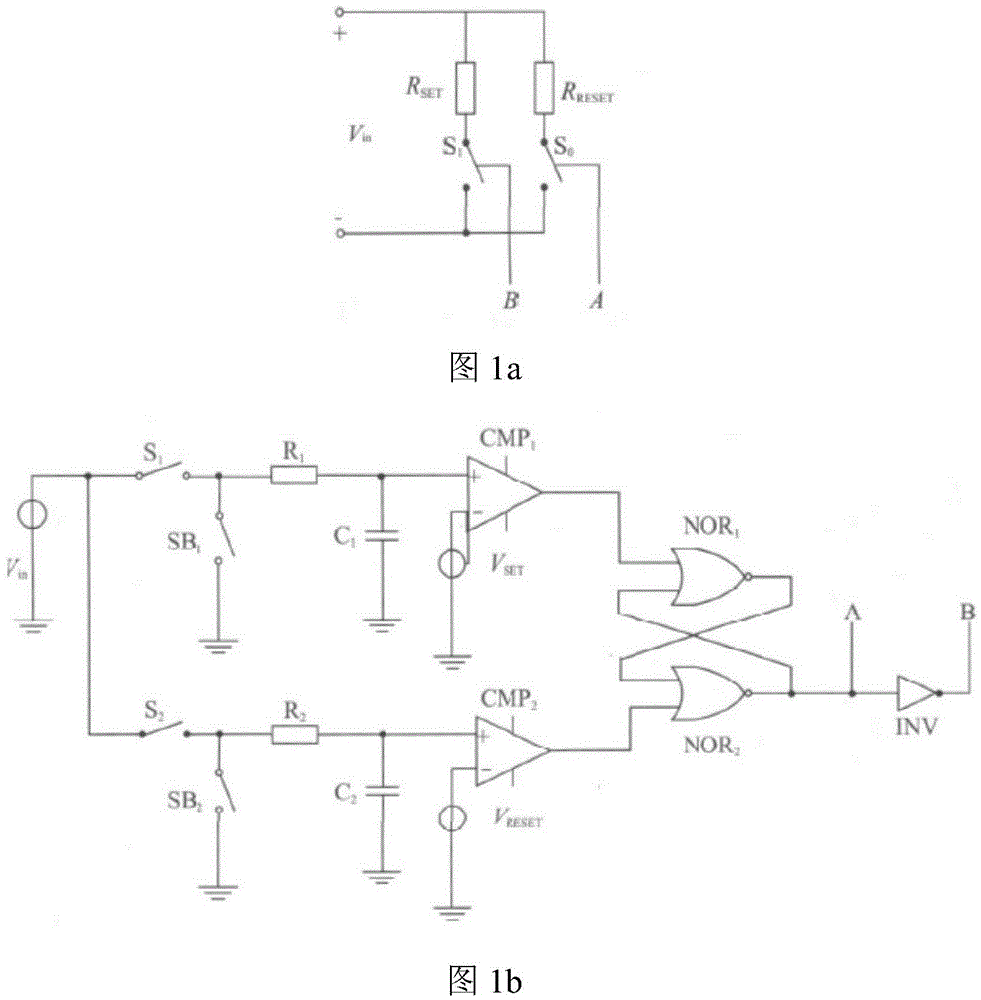

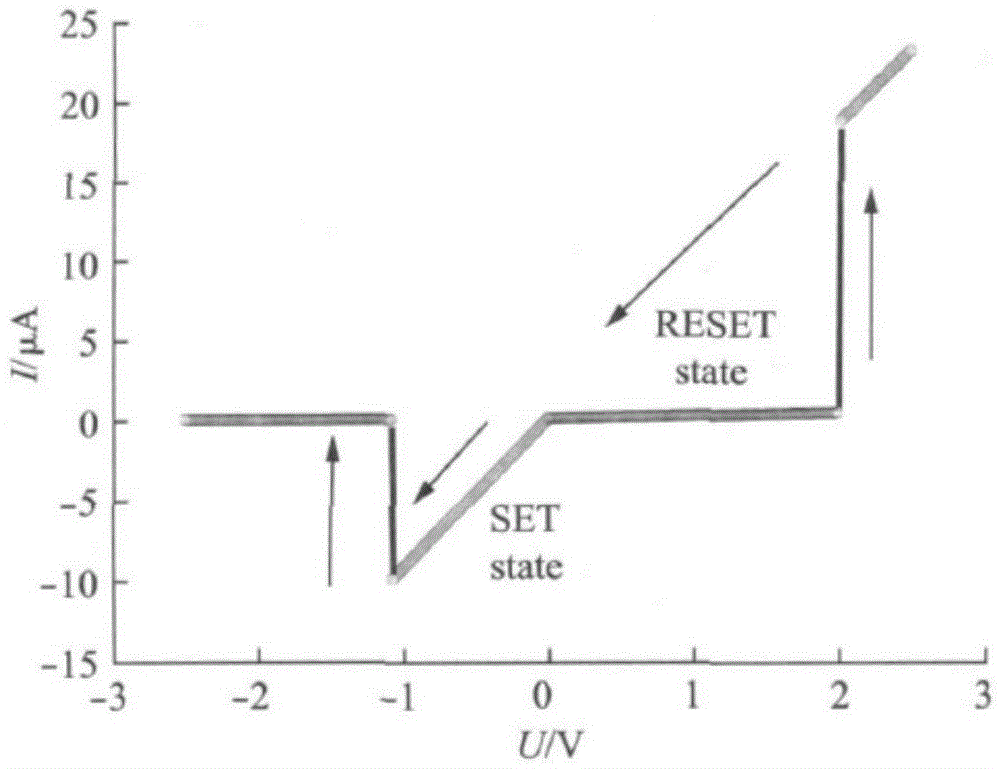

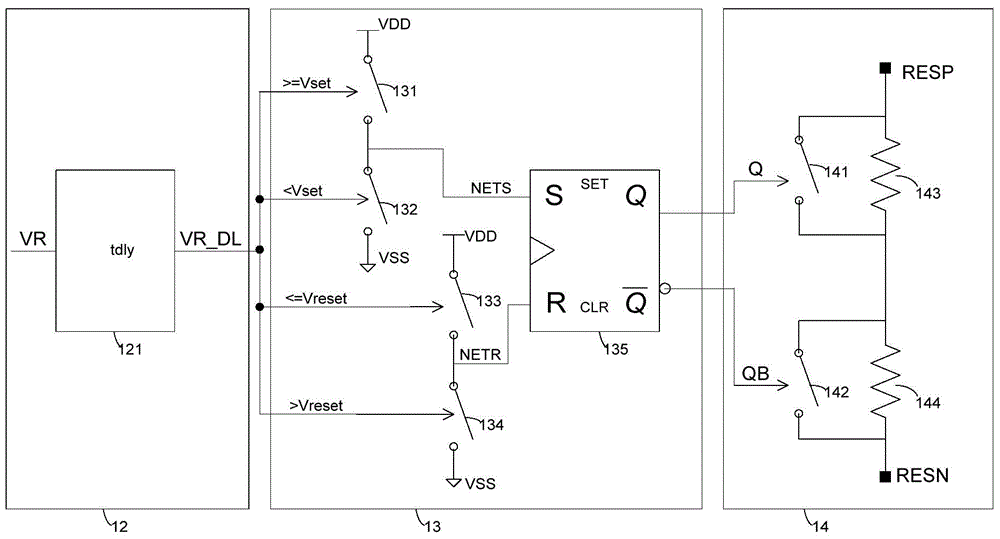

Variable resistor simulation modeling method and circuit in RRAM storage unit

ActiveCN104636548ACharacteristic reflectionReduce the numberSpecial data processing applicationsElectrical resistance and conductanceVoltage pulse

The invention relates to a variable resistor simulation modeling method and circuit in an RRAM storage unit. The circuit comprises a state detection circuit, a state judgment control circuit and a state conversion circuit, wherein the state detection circuit is used for carrying out delayed processing on pure voltage pulse VR at the two ends of a variable resistor to obtain voltage signals VR_DL; the state judgment control circuit is used for comparing the voltage signals VR_DL with state overturning threshold voltage (Vset and Vreset), and the overturning state of the variable resistor is determined; the state conversion circuit is used for determining the equivalent resistance value of the variable resistor according to the determined overturning state of the variable resistor. The variable resistor simulation modeling method and circuit in the RRAM storage unit resolve the technical problems that an existing simulation modeling method is long in simulation time, and a generated simulation file is too large, can relatively actually fit the electric characteristic of the variable resistor, and reflects the characteristics of the memory or storage information under different work conditions of the variable resistor.

Owner:XI AN UNIIC SEMICON CO LTD

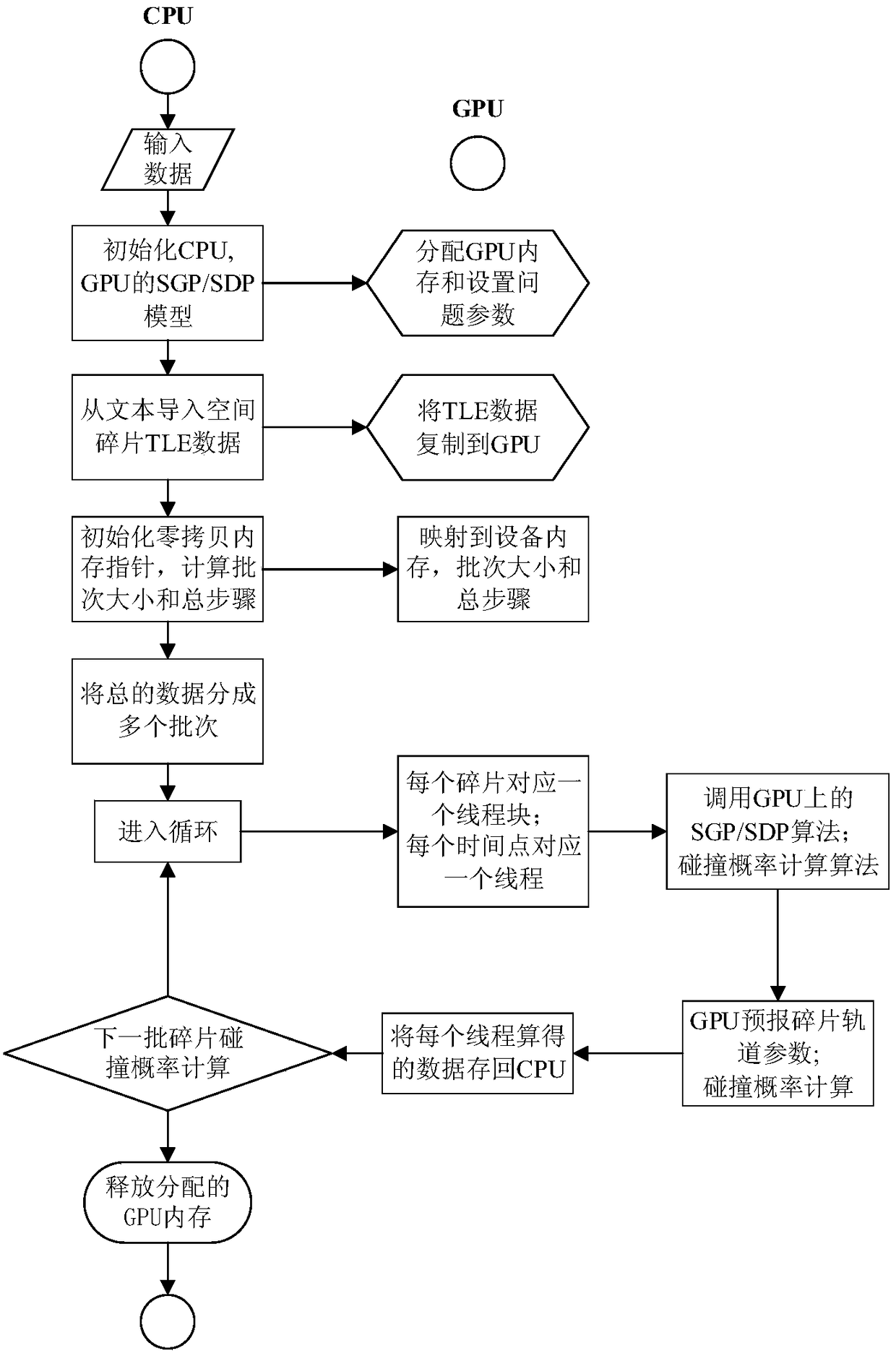

A space debris early warning method based on GPU acceleration

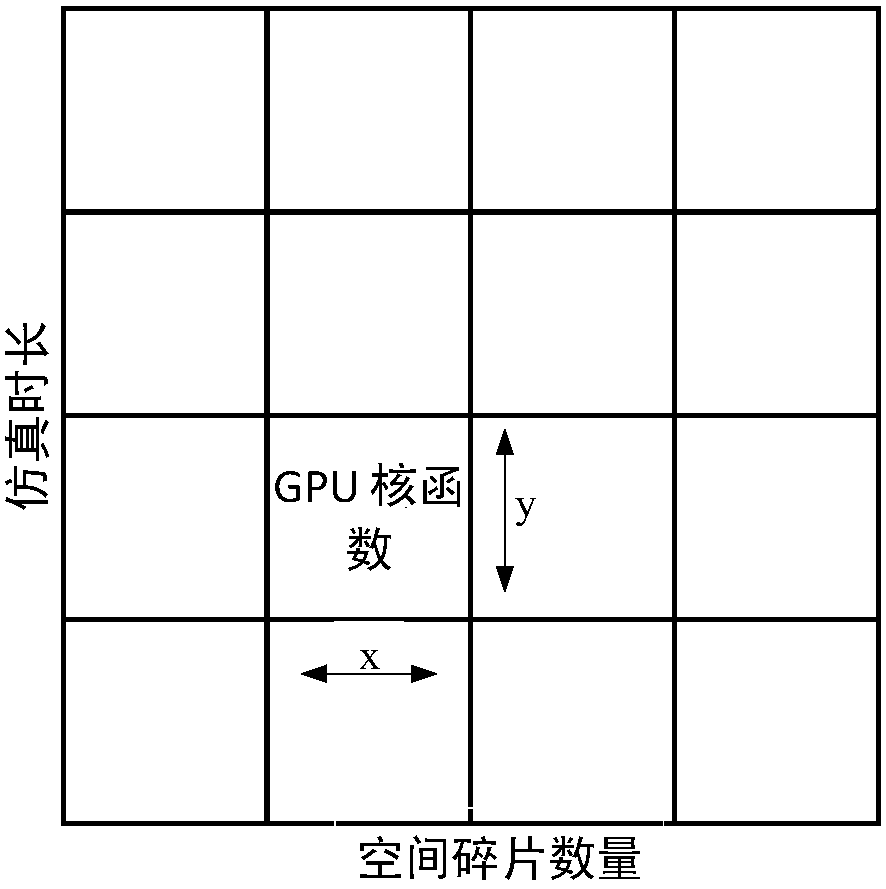

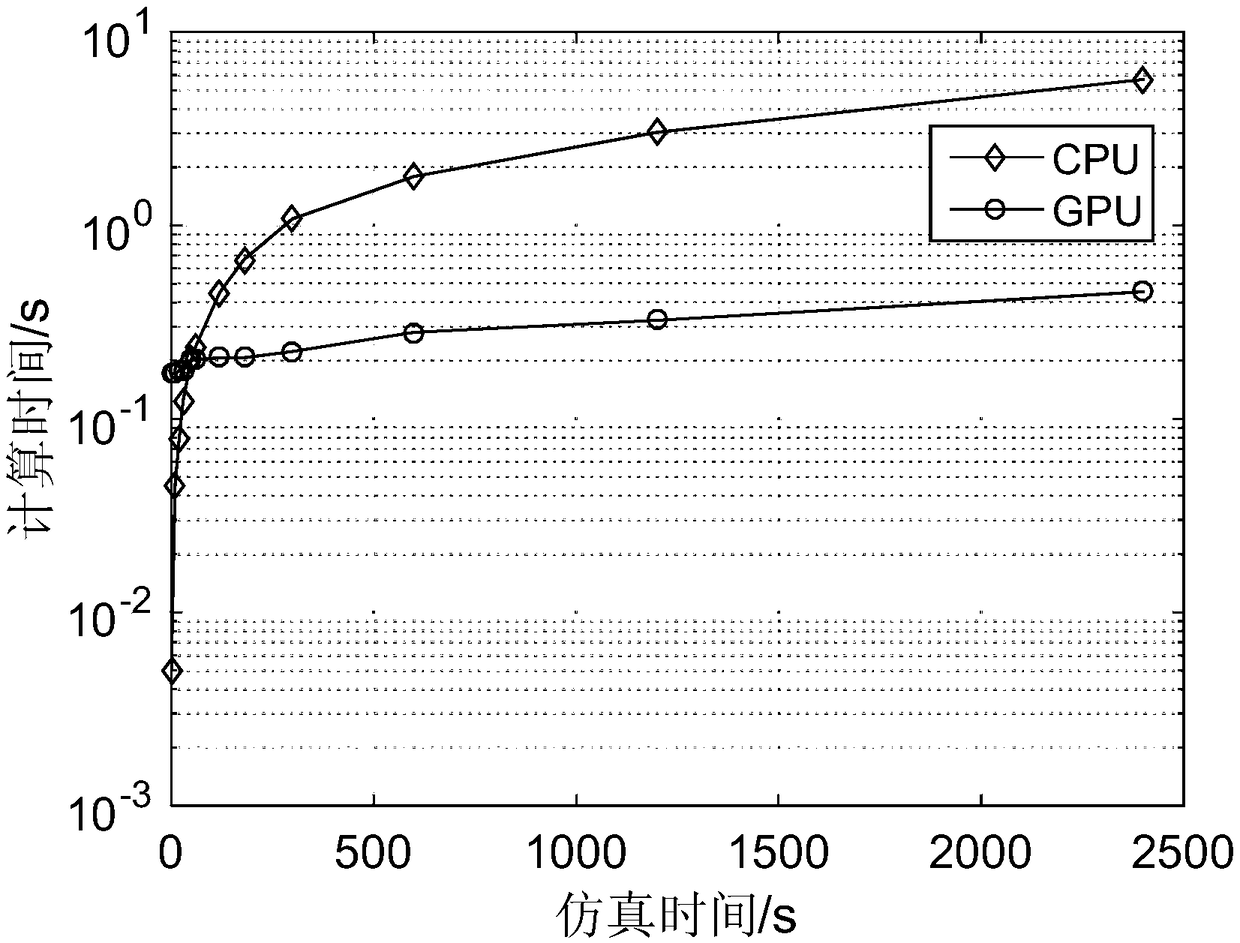

ActiveCN106055780BFast speed ratioMeet timeliness requirementsDigital computer detailsSpecial data processing applicationsZero-copyParallel computing

Provided is a space debris pre-warning method based on GPU acceleration. The method comprises following steps: (1) transplanting an SGP4 / SDP4 model on a GPU, initializing parameters of the SGP4 / SDP4 model on a CPU and setting the number of thread blocks on the GPU and the thread number of each thread block; (2) obtaining TLE data of currently pre-warning space debris on the CPU and copying obtained data to the assigned GPU memory; (3) initializing a zero-copy memory pointer, mapping the pointer to the above GPU memory, combining the available maximum memory and thread number based on the number of currently pre-warning space debris to calculate the batch size of space debris; (4) using zero-copy technology for batching space debris according to the above batch size in order to obtain collision probability of each debris at each time point in the manner of an assembly line and sending back to the CPU for storage; (5) releasing assigned GPU memory after processing space debris.

Owner:BEIHANG UNIV

An intelligent scheduling method for single-threaded multi-priority systems

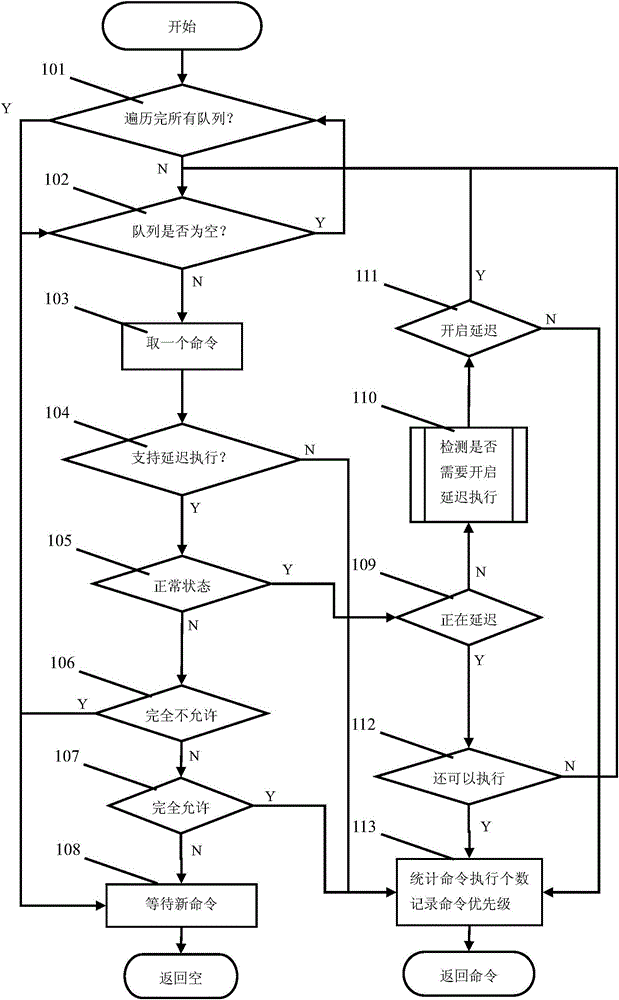

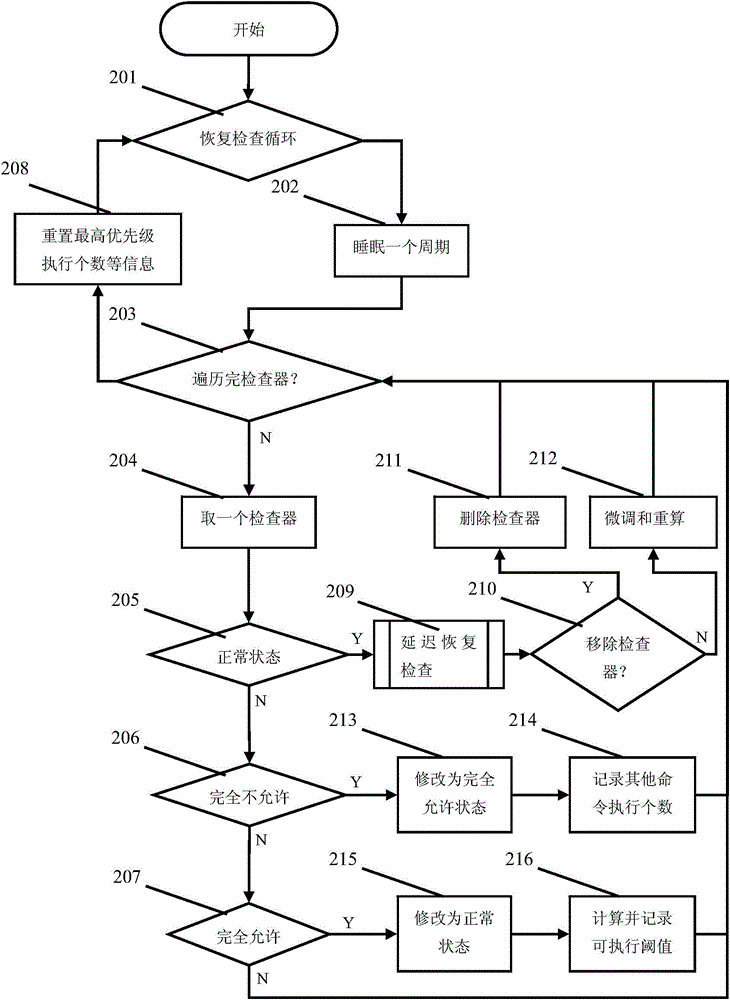

ActiveCN103793207BEasy to controlResolve issues affecting normal business executionConcurrent instruction executionOperating systemLower priority

The invention relates to an intelligent scheduling method of a single-thread and multi-priority system. The intelligent scheduling method of the single-thread and multi-priority system includes the step of deferred execution scheduling and the step of appointed instruction control execution, wherein according to the step of deferred execution scheduling, a deferred execution state identity is added to each kind of instruction, and whether the non-deferred state needs to be recovered or not is detected by a deferring recovery detector; according to the step of appointed instruction control execution, a control cycle is set, an execution threshold value of each appointed instruction is calculated in each control cycle, and the number of executed appointed instructions in each control cycle is controlled according to the execution threshold values. Compared with the prior art, the intelligent scheduling method of the single-thread and multi-priority system improves the instruction execution efficiency, and solves the problem that in the single-thread and multi-priority system, due to insertion of low-priority tasks occupying too much time, execution efficiency of high-priority tasks drops largely.

Owner:EISOO SOFTWARE