Multi-thread processor, compiler device and operating system device

A multi-threaded processor and compiler technology, applied in multi-programming devices, machine execution devices, code compilation, etc., can solve the problems of thread execution efficiency reduction, waste, and inability to execute at the same time, and achieve high execution efficiency and high efficiency The effect of using

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

[0056] In this embodiment, a multi-threaded processor that improves command execution efficiency through command execution control, limitation of the number of commands, designation of the limited number of commands by registers, designation of the limited number of commands by commands, and the number of execution cycles will be described. Designation of intervals, designation of execution cycle intervals by registers, command-based designation of execution cycle intervals, and suppression of issue intervals of commands with resource constraints.

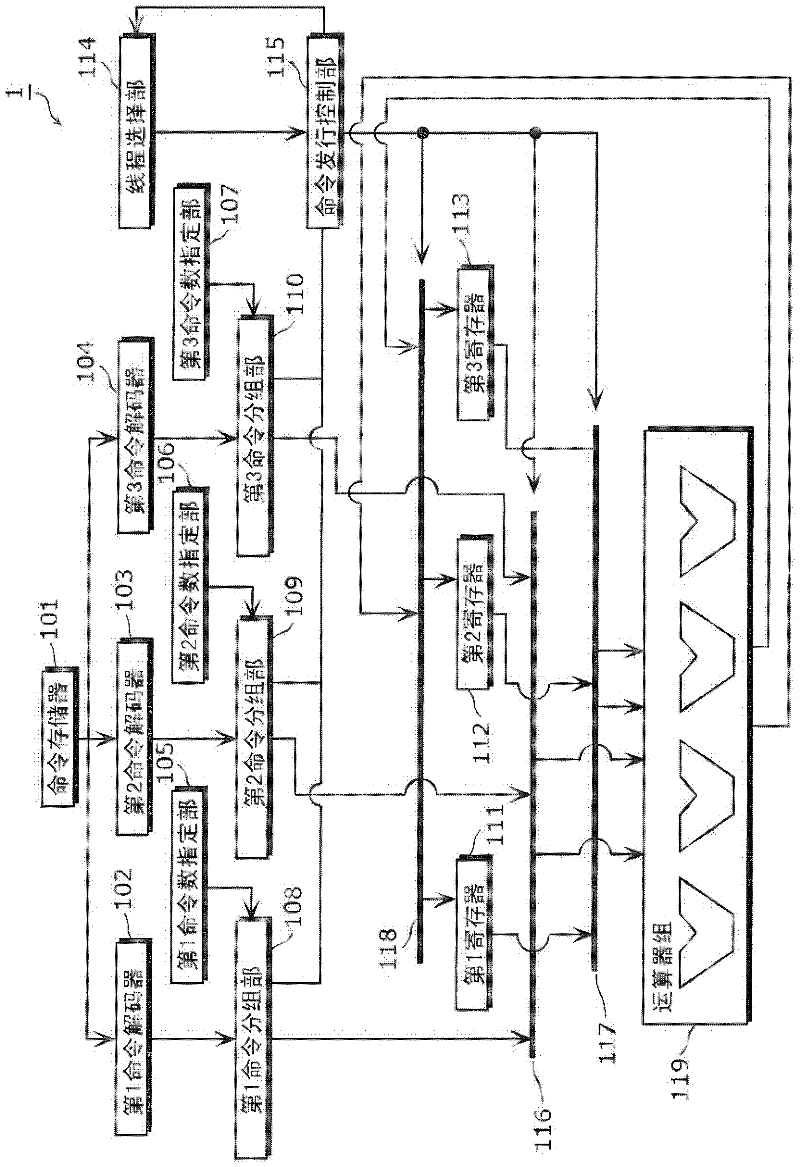

[0057] figure 1 It is a block diagram showing the structure of the multi-thread processor of this embodiment. In addition, in this embodiment, it is assumed that it is a multi-threaded processor capable of executing three threads in parallel.

[0058] The multithreaded processor 1 includes: an instruction memory 101, a first instruction decoder 102, a second instruction decoder 103, a third instruction decoder 104, a first instru...

Embodiment approach 2

[0109] Next, a compiler and an operating system according to Embodiment 2 of the present invention will be described with reference to the drawings.

[0110] Figure 5 It is a block diagram showing the configuration of the compiler 3 according to Embodiment 2 of the present invention.

[0111]Compiler 3 accepts source program 301 described by a programmer in C language as input, converts it into an internal intermediate representation (intermediate code), performs optimization and resource allocation, and generates executable code 302 suitable for the target processor. The processor targeted by the compiler 3 is the multithreaded processor 1 described in the first embodiment.

[0112] Next, the detailed structure and operation of each component of the compiler 3 of the present invention will be described. In addition, the compiler 3 is a program, and its function is realized by executing the program for realizing each component of the compiler 3 on a computer having a proces...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More